# **Experiment 3**

# Open Loop Boost Converter Construction and Testing ECE 482

The objectives of this experiment are:

- To design and realize a power inductor

- To construct and test a boost converter power stage operating in open-loop

- To become familiar with basic layout of power electronics circuits

- To create an accurate loss breakdown which models the efficiency of the boost converter

In this experiment, use a voltage source at all times to simulate the battery. Do not test with the battery in this experiment. For this implementation of the prototype boost converter, the maximum power  $P_{max}$  tested should be at least 100W, and no larger than 250W.

Coordinate with your group and compare converter designs from the prelab. Select one design that your group will build and test for this, and the next experiment. There will be opportunity to revise your design in Experiment 5.

### I. Inductor Design and Construction

The magnetics library available in this lab has several cores and copper wire of various gauge, as well as copper foil available of use. Datasheets describing the important parameters of each core are linked to the course website. Shim stock is available in the lab for gapping the cores. Confer with your lab partner and decide on an inductor design to implement: select the wire gauge, wind the required number of turns on the bobbin, insert the proper air gaps, and assemble the core. Check the inductance value L on the RLC meter, and iterate if necessary.

#### **II.** Boost Power Stage Construction

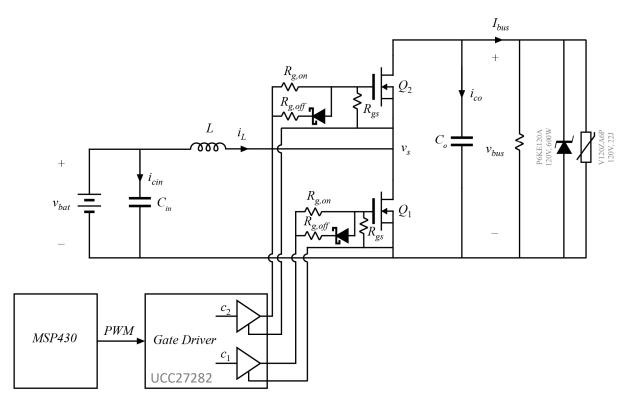

Based on the analysis in your prelab and any additional discussion within your group, select the power transistor and diode you would like to use to implement the Boost converter switches. Mount the power transistor and diode on the heat-sinks from your lab kit. Use the (electrically isolating, thermally conducting) thermal interface material in your kit to insulate the transistor cases from the heatsinks. Using a drill, mount standoffs and binding posts to your perf board. Construct the power stage as shown in Fig. 1 on the perf board. Note the following as you construct the circuit:

- Use lower gauge wire to make interconnections in the *power stage*. Smaller cross-section wire can be used to make signal connections.

- For the inductor, leave loops of wire long enough to insert a clip-on AC current probe to measure the current

- Aside from the previously mentioned locations, keep the wiring short for connections having pulsating currents.

- Use twisted pairs to make the signal and return connections for any signals which must run a significant distance

- Insert 10  $\Omega$  and 2  $\Omega$  gate resistors  $R_{g,on}$  and  $R_{g,off}$  between the UCC27282 outputs and the gates of the transistor to prevent excessive dv/dt at the switched node.

- Insert  $10k\Omega$  resistors between gate and source  $R_{gs}$  of all power transistors to ensure that, when not driven, the devices default to cutoff operation

- Use decoupling capacitors to minimize the size of any loop around which any high frequency component will flow. Make sure the power loop and gate drive loops are well decoupled.

- Note the datasheets for all integrated circuits used and be aware of additional components required for proper operation

Figure 1: Boost converter open-loop power stage schematic

As you construct the circuit, test and debug each component to ensure proper and expected operation is achieved. Do not build the entire converter at once!

#### **III.** Boost Power Stage Testing

Add the zener diode (F5624C) and MOV (F3074-ND) to the output of your boost converter. These are protection devices meant to ensure that the bus voltage is never allowed to rise above

75 V. Per operation constraints, this voltage should never go above 50 V during proper operation. Before you begin any power conversion, answer the following questions

- Is the load connected? In an unloaded asynchronous boost converter, the output voltage will increase unbounded.

- What are the rated voltages and currents of all components including power semiconductors, capacitors, and ICs and is your expected operation well within these limits?

- What are the rated voltages and currents of all test equipment and is your expected operation well within these limits?

With all power supplies turned off, connect the input port of your converter to the high power B&K (or Extech) power supply, which will emulate the battery for testing. Note that the B&K supplies are limited to 5 A output current, whereas the Extech supplies can produce up to 20 A of current *from their rear terminals*. Connect the electronic load across the output port of your converter. You may use independent laboratory voltage sources to generate the supply voltages for the ICs. Use your MSP430 controller to generate the PWM signal. Use a voltage probe to measure  $v_s$  and use multimeters to measure the input and output currents. If available, use a current probe to measure the current through the inductor.

Set the electronic load to constant resistance at 250  $\Omega$ , set the input supply to zero, then turn on all auxiliary power supplies. Increase  $V_{bat}$  to a few volts, and verify that the converter waveforms are correct. Slowly increase  $V_{bat}$  to 25 V, adjust the converter duty cycle to obtain an output of 50 V. Record the DC voltage and current of the source and the load, and calculate the efficiency. If these readings match expectations, proceed.

Gradually decrease the load resistance to obtain full power at the output of the converter. Again measure and record the efficiency; additionally, measure the following waveforms for inclusion in your report:

- Drain currents of  $Q_1$  and  $Q_2$

- Inductor current  $i_l(t)$

- Switched node voltage  $v_s(t)$

- Bus voltage  $v_{bus}(t)$

- Input voltage *v<sub>batt</sub>*(*t*)

Label the waveform names and scales. Label salient features. Measure the inductor current ripple  $\Delta i_L$ , and compare with the value you designed for in your prelab assignment. Include these values in your report.

## IV. Converter Efficiency Sweep

Generate plots of converter efficiency and duty cycle with respect to output power for  $V_{bus} = 50 \text{ V}$ . At this voltage, take at least five measurements at differing power levels which span the range of 0 to  $P_{max}$ . Additionally, take measurements at  $P_{max}$  with the output voltage  $V_{bus} = 30 \text{ V}$  and  $V_{bus} = 40 \text{ V}$ . For each measurement, record the voltages, power level, converter efficiency, and converter duty cycle D. In all cases, ensure that neither input nor output currents exceed the 20 A limit of the B&K multimeters. Turn in plots of the duty cycle and efficiency with respect to output power, with a single curve for each bus voltage.

# V. Efficiency Analysis and Simulation

For the original full-power operating point when  $V_{bat} = 25 \text{ V}$  and  $V_{bus} = 50 \text{ V}$ , analytically solve the expected power loss in each component of the circuit and each loss mechanism you find to be significant. Explain and justify which losses you have selected to neglect, and at what level you model the losses you have chosen to include. Compare your predicted loss budget with the experimental efficiencies obtained. Note and explain any discrepancies.

Using LTSpice, generate a model, including losses, of your converter. You may use averaged, or switching models. Using this model, generate the same efficiency sweeps as were measured experimentally in Section IV. Compare the results to your experimental data from Section IV, as well as the analytical model just developed, again noting and explaining any discrepancies. Speculate on the source of any unaccounted for losses in the converter. In your lab report, discuss any modifications which could be made to the converter which you believe would help improve performance, including any changes in devices used, converter characteristics, inductor design, layout, etc.