# ALGORITHM ANALYSIS AND MAPPING ENVIRONMENT FOR ADAPTIVE COMPUTING SYSTEMS

FINAL TECHNICAL REPORT

# 25 September 2001

| Submitted by:   | BAE Systems, Information and Electronic Warfare<br>Systems<br>P.O. Box 868<br>Nashua, NH 03061-0868                                       |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Under Contract: | F33615-97-C-1174                                                                                                                          |

| As:             | CLIN 0001, Data Item A001                                                                                                                 |

| For:            | <b>Air Force Research Laboratory/SNAS, Building 23</b><br>2010 Fifth Street<br>Wright Patterson Air Force Base, OH 45433-7301             |

|                 | <b>Defense Advanced Research Projects Agency</b><br>Information Technology Office<br>3701 North Fairfax Drive<br>Arlington, VA 22209-2308 |

Approved for public release; distribution is unlimited.

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                    |                                                                                                                                                                                                                          |                                                                                                                                                                                     | Form Approved<br>OMB No. 0704-0188                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pastic reporting burden for this collection of informa<br>gathering and maintaining the data needed, and com<br>collection of information, including suggestions for in<br>Dava highway, Suite 1264, Antilegon, VA 22202-333 | tion is estimated to average 1 hour per m<br>pleting and reviewing the collection of in<br>educing this ourden, to Washington Head<br>2, and to the Office of Management and 8                                           | sponse, including the time for revi<br>formation. Send comments regard<br>quarters Services, Directorate for is<br>udget, Paperwork Reduction Projec                                | ewing instructions, searching existing data sources,<br>ing this burden estimate or any other aspect of this<br>information Operations and Reports, 1215 Jefferson<br>t (0704-0188), Washington, DC 20503. |

| 1. AGENCY USE ONLY (Leave blank)                                                                                                                                                                                             | 2. REPORT DATE<br>April 2, 2001                                                                                                                                                                                          | 3. REPORT TYPE AND                                                                                                                                                                  |                                                                                                                                                                                                            |

| <ul> <li><b>4. TITLE AND SUBTITLE</b><br/>Algorithm Analysis and Mapping<br/>Systems, Final Technical Report</li> <li><b>6. AUTHOR(5)</b><br/>Jphn C. Zaino</li> </ul>                                                       |                                                                                                                                                                                                                          | 1                                                                                                                                                                                   | 5. FUNDING NUMBERS<br>Program Funding,<br>Contract Number:<br>F33615-97-C-1174                                                                                                                             |

| 7. PERFORMING ORGANIZATION NAME                                                                                                                                                                                              | (S) AND ADDRESS(ES)                                                                                                                                                                                                      |                                                                                                                                                                                     | B. PERFORMING ORGANIZATION                                                                                                                                                                                 |

| BAE SYSTEMS (Formerly Sande<br>PO Box 868<br>Nashua NH<br>03061-0868                                                                                                                                                         | ers, A Lockheed Martin Co)                                                                                                                                                                                               |                                                                                                                                                                                     | REPORT NUMBER<br>CLIN 0001, CDRL A001                                                                                                                                                                      |

| 9. SPONSORING / MONITORING AGENCE<br>Air Force Research<br>Laboratory / SNAS<br>28 Electronics Parkway<br>Rome NY, 13441-4514                                                                                                | Y NAME(S) AND ADDRESS(ES)<br>Defense Advanced Rese<br>Information Technology<br>3701 North Fairfax Drive<br>Arlington, VA 22209-230                                                                                      | <b>arch Projects Agency</b><br>Office                                                                                                                                               | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER<br>CLIN 0001, CDRL A001                                                                                                                                  |

| 11. SUPPLEMENTARY NOTES                                                                                                                                                                                                      | - · · · · · ·                                                                                                                                                                                                            | 1 .<br>• • •                                                                                                                                                                        |                                                                                                                                                                                                            |

| 12. DISTRIBUTION AVAILABILITY STA<br>DOD<br>The views and conclusions contain<br>should not be interpreted as repres<br>implied, of the Defense Advanced                                                                     | ned in this document are the senting the official policies,                                                                                                                                                              | ose of the authors and<br>either expressed or                                                                                                                                       | 12b. DISTRIBUTION CODE                                                                                                                                                                                     |

| developed an integrated algorithm<br>signal processing algorithm into a<br>(FPGAs) devices. This environme                                                                                                                   | analysis and mapping envi<br>n Adaptive Computing Syst<br>ent allows designers to trans<br>aster than is currently possil<br>computing: algorithm analy<br>special characteristics of sig<br>nplemented as extensions to | ronment for translating<br>em (ACS) consisting o<br>sform signal processing<br>ole. Our approach was<br>sis, algorithm mapping<br>gnal processing algorith<br>the Ptolemy design en | f field programmable gate array<br>algorithms into FPGA-based<br>to focus on three areas of capability<br>, and smart generators. These<br>ums to reduce the time to field the<br>vironment                |

|                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                                                                                                                                                                     |                                                                                                                                                                                                            |

| 14. SUBJECT TERMS                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                    |                                                                                                                                                                                     | 15. NUMBER OF PAGES                                                                                                                                                                                        |

| Adaptive Computing, FPGA, Rec<br>Modeling, Simulation, Ptolemy, A                                                                                                                                                            |                                                                                                                                                                                                                          | pping, Algorithm Analy                                                                                                                                                              | ISIS, 16. PRICE CODE                                                                                                                                                                                       |

| 17. SECURITY CLASSIFICATION 18.<br>OF REPORT<br>UNCLASSIFIED                                                                                                                                                                 | SECURITY CLASSIFICATION<br>OF THIS PAGE<br>UNCLASSIFIED                                                                                                                                                                  | 19. SECURITY CLASSIFIC<br>OF ABSTRACT<br>UNCLASSIFIED                                                                                                                               |                                                                                                                                                                                                            |

| NSN 7540-01-280-5500                                                                                                                                                                                                         |                                                                                                                                                                                                                          |                                                                                                                                                                                     | Standard Form 298 (Rev. 2-89)<br>Prescribed by ANSI Sol. 239-18<br>298-102                                                                                                                                 |

| A | bstract            |                                                             | 1  |

|---|--------------------|-------------------------------------------------------------|----|

| 1 | The Need           |                                                             |    |

| 2 | <b>Objective</b>   |                                                             |    |

| 3 | Approach.          |                                                             | 6  |

| 4 | Progress           |                                                             | 9  |

|   | 4.1 Algorit        | hm Analysis and Mapping                                     | 12 |

|   |                    | gorithm Analysis                                            |    |

|   |                    | goritm Mapping                                              |    |

|   | 4.2 Smart          | Generators                                                  |    |

|   |                    | y Integration and the ACS Domain                            |    |

|   |                    | strations                                                   |    |

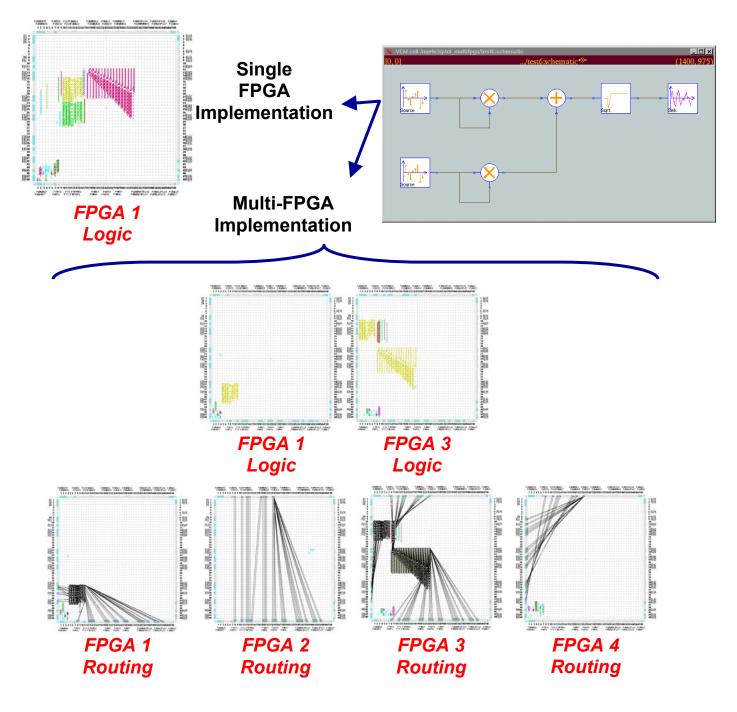

|   |                    | monstration: Design Generation for Single or Multiple FPC   |    |

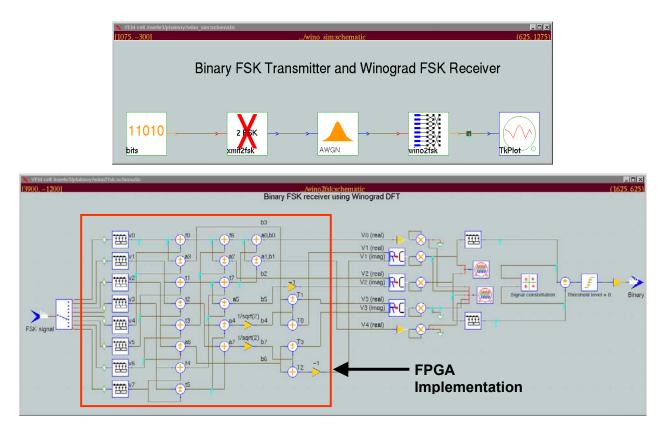

|   |                    | monstration No. 1: Wnigrad DFT-Based FSK Communicat         |    |

|   |                    | ceiver                                                      |    |

|   |                    | monstration No. 2: Signal Detection using FFT-Based Corr    |    |

|   |                    | monstrations No. 3 and 4: Acceleration of a High Resolution |    |

|   |                    | mplate-matching Application (System-Oriented High Rang      |    |

|   |                    | solution Automatic Recognition Program (SHARP))             |    |

|   | 4.4.4.1<br>4.4.4.2 | SHARP Algorithm                                             |    |

|   | 4.4.4.2            | Hardware Analysis                                           |    |

|   |                    | U U                                                         |    |

| 5 | Summary            |                                                             |    |

| 6 | References         |                                                             |    |

| 7 | Acronyms           |                                                             |    |

## **Table of Contents**

## List of Figures

| 1  | Use of Capabilities to Develop an Adaptive Computing System        | 8    |

|----|--------------------------------------------------------------------|------|

| 2  | Design Time and Run Time Environments for an Adaptive Computing Sy | stem |

|    | Implementation Using the AAME Tools                                | 9    |

| 3  | Algorithm Trade-Offs                                               |      |

| 4  | Complex Multiply                                                   | 14   |

| 5  | Cost vs. Variance for Complex Multiply Designs                     |      |

| 6  | Variance Estimates.                                                |      |

| 7  | Cost Estimates                                                     | 17   |

| 8  | Cost and Variance Estimates for a Magnitude Calculation            | 18   |

| 9  | Results of Naïve Monte Carlo Algorithm and Monte Carlo Wordlengths | 19   |

| 10 | Comparisn: Prediction vs. Actual Performance                       |      |

| 11 | Markov Chain Sampling                                              | 20   |

| 12 | Lower Bound for Optimization                                       | 21   |

| 13 | ACS Tools User Interface                                           | 22   |

| 14 | Target Architectures                                               | 23   |

| 15 | Pipeline Alignmnet and Schedule Determination Required for Logic   |      |

|    | Synthesis                                                          | 26   |

| 16 | Wordlength Optimization Analysis                                   | 27   |

| 17 | Ptolemy Project                                                    |      |

| 18 | ACS Domain, Ptolemy Project                                        |      |

| 19 | ACS Domain, Corona/Core and Targets                                |      |

| 20 | Design Generation for Single or Multiple FPGAs                     | 35   |

| 21 | Winograd DFT-Based FSK Communications Receiver                     |      |

| 22 | Winograd DFT-Based FSK Communications receiver – VHDL, Schedule    |      |

|    | and HW Design                                                      |      |

| 23 | Winograd DFT-Based FSK Communications Receiver – Processing        |      |

|    | Results                                                            | . 38 |

| 24 | Signal Detection Using FFT-Based Correlator                        | 39   |

| 25 | SHARP Approach to ATR                                              |      |

| 26 | SHARP Approach Using Minimum Error                                 | . 41 |

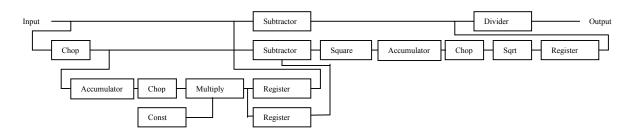

| 27 | Block Calculations for Bias Removal and Normalization              |      |

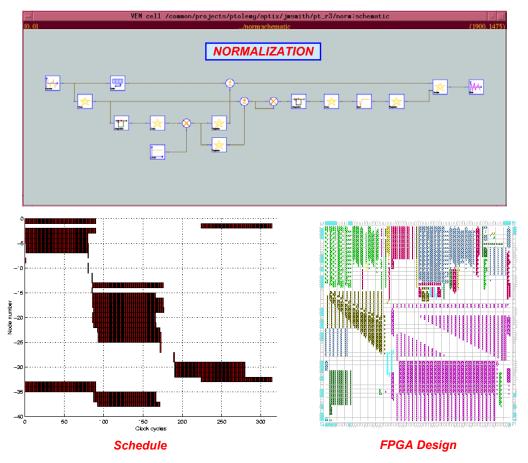

| 28 | Normalization Routine                                              | 49   |

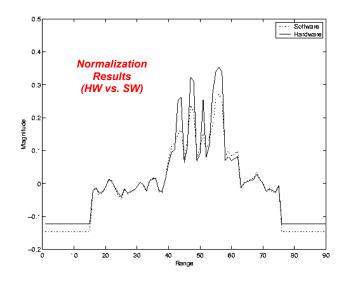

| 29 | Normalization Results – HW vs. SW                                  |      |

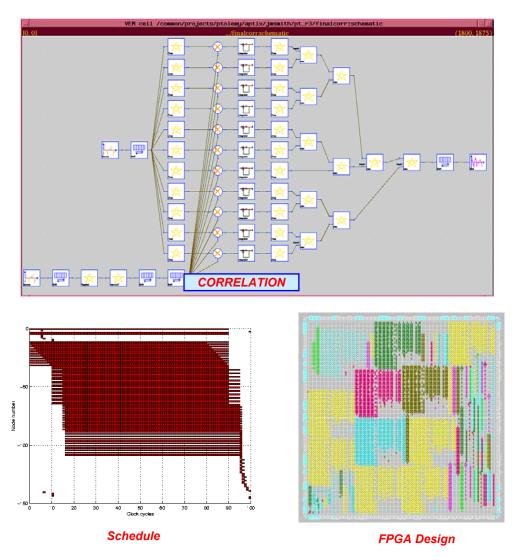

| 30 | Correlation Routine                                                |      |

# List of Tables

| 1.0 | Performance Benefits and Development Limitations of Adaptive |    |  |

|-----|--------------------------------------------------------------|----|--|

|     | Computing System Implementations                             | 3  |  |

| 4.1 | Confusion Matrix by Vehicle Using Original AFRL Code         | 43 |  |

| 4.2 | Confusion Matrix by Vehicle Type Using Original AFRL Code    | 43 |  |

| 4.3 | Timing Analysis of Original Software                         |    |  |

| 4.4 | Timing Analysis of Optimized Software                        |    |  |

#### Abstract

Over the past four years, a team at BAE SYSTEMS has developed an integrated algorithm analysis and mapping environment for translating a dataflow representation of a signal processing algorithm into an Adaptive Computing System (ACS) consisting of field programmable gate array (FPGAs) devices. This environment allows designers to transform signal processing algorithms into FPGA-based hardware an order of magnitude faster than is currently possible. Our approach has been to focus on three areas of capability critical to the success of adaptive computing: algorithm analysis, algorithm mapping, and smart generators. These capabilities take advantage of the special characteristics of signal processing algorithms to reduce the time to field the ACS implementation, and were implemented as extensions to the Ptolemy design environment (http://ptolemy.eecs.berkeley.edu) developed at the University of California, Berkeley.

Algorithm implementation for ACS requires careful consideration of the appropriate signal representation and the costs of operations. The algorithm analysis capabilities developed on this program reduce the effort required to find good ACS implementation choices for a signal processing algorithm. The environment provides algorithm designers with information about operation counts, including adds, multiplies, and memory accesses, and with analyses of quantization effects related to ACS implementations. For many DSP problems, reduced precision arithmetic will maintain acceptable system performance. A mapping of an algorithm to an FPGA architecture will be successful if the designer can limit wordlength growth without sacrificing algorithm performance. Wordlength reduction introduces noise into the data stream, so the designer must balance the need for an efficient implementation with output quality. Designing optimal wordlength combinations that must be considered. Naive random sampling approaches are ineffective for large flowgraphs, because most of the samples do not correspond to feasible or useful designs.

In our work, we use a Markov chain Monte Carlo (MCMC) sampling approach [1,2] to finding good wordlength combinations for DSP flowgraphs. We define a feasible region of wordlengths that consists of designs near the Pareto-optimal cost/quality boundary which also satisfy any feasibility constraints. The MCMC sampler is used to generate uniform samples from this feasible region by performing a random walk on a specially constructed Markov chain; this approach solves a problem that can be very difficult using only naive sampling approaches. Additionally, the MCMC method offers extreme simplicity in the software coding of the algorithm, in contrast with dynamic programming approaches. With these techniques and capabilities, an algorithm designer can quickly determine the appropriate number of bits for signal representations at all points in the design and quantify the performance of various implementation choices.

Signal processing algorithm mapping for ACS also involves assigning functions to different processing elements. On this program we have developed mapping techniques

for ACS tailored to signal processing. These capabilities include performance analysis, multi-device partitioning assistance, and automatic scheduling. The scheduling and partitioning functions use the coarse-grain nature of signal processing dataflow graphs to help optimize partitioning for ACS. Our tools automatically generate the VHDL code needed to translate data paths across different FPGA devices.

Current methods for logic generation for ACS are either built around libraries of functions or around general-purpose logic synthesis. As part of this effort, we implemented "smart generators" that are extensions of the concept of a parameterized library. These generators are tailored to signal processing functions and include rules that capture specific implementation techniques and trade-offs. For example, a smart generator for a complex multiplier is able to trade between a three-multiplier implementation and a four-multiplier implementation according to area and latency constraints. Additionally, we have provided mechanisms to automatically generate both hardware and software interfaces for the resultant ACS. Our initial target system was a Xilinx XC4062XL-based Wildforce™ board from Annapolis Micro Systems http://www.annapmicro.com. Additional efforts were also expended towards augmenting our tools to support a Xilinx Virtex™ XCV1000-based Wildstar™ board, also from Annapolis Micro Systems.

The algorithm analysis, mapping, and logic generation capabilities have been developed as extensions to Ptolemy. Ptolemy provides a well documented, object-oriented, open software architecture with implementations in C++ and Java. Our extensions to Ptolemy have been captured in a new ACS domain that separates the interface specification from implementation for each signal processing functional block. The algorithms of interest to this project are represented by dataflow graphs comprised of these functional blocks, following a synchronous dataflow model of computation. We have used a Corona/Core architecture, where each block has a common interface known as the Corona, and one or more implementations, known as the Cores. A retargeting mechanism allows the users to change Cores and hence implementation, which moves the dataflow graph between various simulation models (floating point, fixed point) and implementations (C code, VHDL code).

These ACS tools have been used to automatically implement several applications. The first was a Winograd Discrete Fourier Transform (DFT) as part of a channelized frequency shift-keyed (FSK) receiver in ACS. The Winograd algorithmic structure has the minimum number of multiplications for any DFT approach, and is thus ideal for FPGA implementation. The tools have also been used to develop an FPGA implementation of a high speed linear FM detector. We used our tools to also implement a FFT-based complex correlator, requiring the use of two 16-point complex FFT cores in series with a cornerturn to obtain a 256-point spectrum. Most recently, we utilized our tools to accelerate a high resolution radar template-matching application. In all cases, our ACS tools were used to simulate the algorithm, select appropriate fixed point representations, and generate the VHDL implementations. The final FPGA designs were obtained by synthesizing the VHDL and performing place and route with commercial

tools. The ACS domain is part of Ptolemy Classic and includes these ACS capabilities and selected demonstrations.

## 1 The Need

The "Algorithm Analysis and Mapping Environment for Adaptive Computing Systems" is a DARPA ITO/Wright Labs effort to develop tools and a software environment that significantly enhances the ability of a designer to develop adaptive computing systems. Adaptive computing systems, e.g. systems which use reconfigurable logic for computation, have the potential for leap ahead improvement in performance, measured in operations per watt or operations per cubic inch, for a range of signal processing applications. However, the current tools and environments for developing such systems are not sufficient to allow the full power of adaptive computing technology to be developed. Typically, hardware design expertise is required to get any working adaptive computing system implementation. Generation of a good implementation requires many time-consuming iterations between an algorithm designer and a hardware developer. Table 1.0 illustrates both the potential of adaptive computing technology as well as the development time issue.

| Application               | Performance Benefit                                                                                                                          | Development Limitations                                                                                |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| COTS Midband<br>Algorithm | Reconfigurable implementation performed 25 x more frames per second for same hardware area.                                                  | Implementation was twice as long as software implementation. Total development time measured in weeks. |  |

| Communications            |                                                                                                                                              |                                                                                                        |  |

| Digital Receiver          | Sixteen channel filter bank on 320<br>MHz data implemented on two MCMs. Weeks to implement. Required knowledge of specialized FFT structure. |                                                                                                        |  |

Table 1.0. Performance benefits and development limitations of adaptive computing system implementations.

# 2 Objective

Our objective in this program was to dramatically reduce the time required to implement an adaptive computing system. Our goal was to reduce the time to develop an initial working design from days to minutes and the time to implement an optimized solution from weeks to days. Our goal was to make this capability available to the algorithm designer who lacks significant hardware development background. It was our objective to demonstrate an order of magnitude reduction in the time required to map a military signal processing algorithm onto an adaptive computing system. The objective was to work towards these goals by developing new algorithm analysis and mapping capabilities and by implementing these capabilities in an integrated development environment. These development efforts were to include the following capabilities: a) capabilities that allow a signal processing algorithm designer to analyze their algorithm for characteristics specifically suited, or ill-suited, for implementation in adaptive computing systems; b) capabilities that take advantage of the special structure of many signal processing algorithms to ease mapping algorithms to adaptive computing devices; and c) capabilities that enable device specific and function-specific implementation generators. These capabilities and the environment were demonstrated throughout the program on signal processing algorithms with military applications.

The objective was to implement the capabilities and environment for this program in a form that is readily accessible to the adaptive computing system community. Our work was to make adaptive computing systems more readily accessible to algorithm developers and to speed the development of military signal processing applications. The environment developed was to be an extensible environment to which other researchers would be able to add to.

Specifically, the AAME program objectives (from Statement of Work) were to:

## Algorithm Analysis

- Develop capabilities that assist a signal processing algorithm developer in analyzing a signal processing algorithm for implementation in an adaptive computing system. These capabilities shall be implemented as a set of software tools that operate on signal flow graphs. Capabilities shall include at least the following:

- Develop the capability to propagate derived information about algorithm wordlengths and formats based on wordlengths and formats of input data and coefficients.

- Develop the capability to track statistical information through an algorithm. This capability shall support comparison of a conventional implementation with reduced complexity implementations.

- Develop the capability to both simulate and test real and synthetic data sets in complicated algorithms. This capability shall enable algorithm performance analysis and trade-off analyses.

- Develop the capability to explore alternative algorithmic rearrangements. This capability will allow multiple algorithmic implementations to be tested automatically by the system to find the most efficient rearrangement for a given application and technology.

## Algorithm Mapping

• Develop a capability to represent a synchronous data-flow algorithm in a model that captures the mapping of that algorithm to hardware components. Through an iterative process, the user shall be able to find efficient mappings of algorithms to components, both in space and time. These capabilities shall include the following:

- Design and populate a hierarchical library of hardware components. Representations for device-specific components shall be developed and a mechanism for building architectures from these components shall be provided.

- A graphical user interface shall be used to group components of the algorithm and assign them to hardware devices. The designer shall be given feedback on the performance of the partitioning in terms of utilization, throughput, and efficiency, among other metrics. The capability to recommend efficient mappings shall be developed.

- Extend the concepts of multi-processor scheduling to include scheduling of hardware contexts for dynamically reconfigurable devices.

## **Smart Generators**

- Develop the capability to generate device and function-specific implementations. These capabilities shall include the following:

- Develop and integrate generators for basic digital signal processing (DSP) operations applicable to at least two distinct reconfigurable logic target technologies. Enough basic building blocks shall be provide to produce usable hardware for the demonstrations.

- Develop and integrate recursive hierarchical generators which allow for multiple algorithmic implementations to be compared for optimality in the targeted technology.

- Develop and integrate hardware/software interfaces that de-couple the interface from implementation. Large data sets and flow control shall be considered.

- Incorporate general purpose logic synthesis as a mechanism for extending capabilities to new devices.

#### Software Architecture and Integration

• Integrate algorithm analysis, algorithm mapping, and smart generators technology into the software environment. All software developed on this program shall be designed to interface standards consistent with the software environment and shall be distributed according to existing procedures, which make the software, as is, available freely to all interested parties. Incremental software releases shall be provided on a regular basis. Software documentation shall be provided.

#### Demonstrations

- Demonstrate the capabilities and software developed on this program after each software release. Libraries shall be populated and generators developed as appropriate for each demonstration. Capabilities shall be demonstrated in each of the three areas of algorithm analysis, mapping, and smart generators for each demonstration. These demonstrations shall include the following signal processing applications:

- Demonstrate the ability to support common communication structures including basic mathematics, filtering, and quantization

- Demonstrate multiple kinds of signal processing operations, including filtering, Constant False Alarm Rate (CFAR) detection, parameter matching and decision processing at different rates. The hierarchical generation capability of the smart generators task shall be used to create implementations of critical operations.

- Demonstrate processing of large multidimensional data sets using image processing or ATR algorithms developed under the MSTAR program.

- Demonstrate the retargetability of its approach through a multi-function demonstration of MSTAR modules. The demonstration shall include multiple functions mapped to the same hardware and the demonstration shall include high level symbolic rearrangement, partitioning, and automatic scheduling of algorithms.

## **Technical Reports/Reviews**

• Exercise good management practices to monitor the technical progress of the AAME program by reviewing monthly progress against cost and schedule plans. Prompt communication of any issues affecting progress shall be made. Periodic program reviews shall be conducted. Results of this effort shall be described in papers and conference presentations. Periodic reports summarizing the technical progress as well as a final report shall be delivered.

## 3 Approach

Our approach to meeting the challenging objectives of this program consisted of four major thrusts:

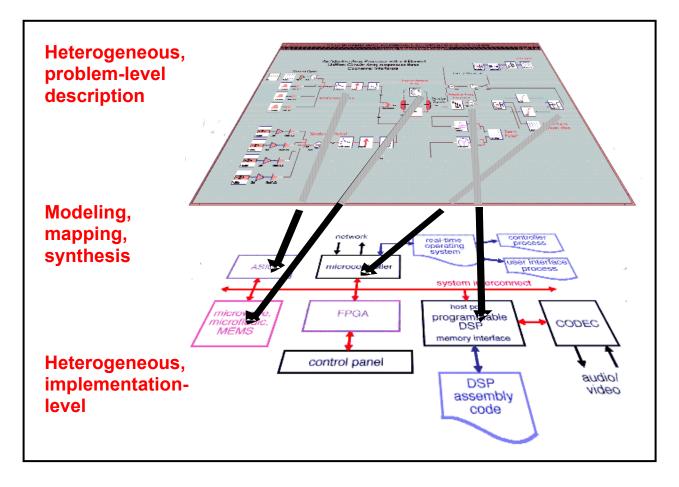

The first was to focus on a system that starts with a high level language input and restrict ourselves to a limited application domain. In our case we chose the domain of dataflow signal processing algorithms. We used a high level system, the Ptolemy system, from the University of California, Berkeley as our algorithm representation and manipulation environment. The second thrust was to support algorithm development at the bit level by combining analytical and simulation methods to help the algorithm developer optimize performance. This included development of methods for providing the algorithm designer with feedback about the implications of algorithm implementation decisions. We included in this capability provisions to rearrange algorithms as required by implementation requirements.

The third thrust was to leverage the structure of signal processing algorithms to improve algorithm mapping. We took advantage of the coarse-grain nature of signal processing dataflow graphs to improve partitioning of algorithms in space and time. We also investigated the use of scheduling tools, developed for mapping signal processing dataflows onto programmable processors, to develop hardware schedulers that are used in adaptive computing system implementation.

The fourth thrust included providing a library of signal processing building blocks, with their hardware implementations, and the ability to rapidly compose these blocks as well as the ability to automatically generate the software to drive the hardware.

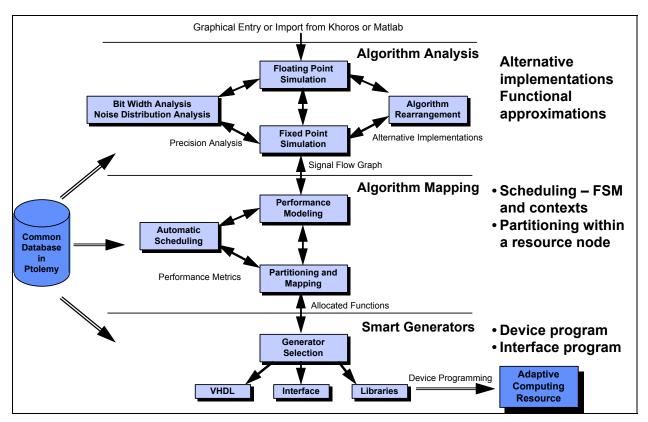

Figure 1 shows how the capabilities that this program have provided are used to develop an adaptive computing system. In our approach an algorithm is entered into the system. Our approach represents signal processing dataflow graphs within the Ptolemy system. We support direct entry of algorithms within that environment. The system supports floating point simulations to set a performance baseline of an algorithm. Bit width analysis and noise distribution analysis are performed and a fixed point version of the algorithm can be simulated. The results of fixed point simulation can be compared to the floating point simulation and the process iterated until a good tradeoff between precision and performance is realized. This iteration can be augmented by the manual rearrangement of the algorithm to provide alternative implementations. For example, multiple implementations of an FIR filter can be investigated.

Following algorithm analysis the resulting signal processing algorithm dataflow graph is mapped to an adaptive computing resource node. We have considered adaptive computing resource nodes with multiple reconfigurable devices and with the capability to be dynamically reconfigured. The first step of the mapping work is to predict performance of the algorithm on the target hardware. This prediction can flow back up into algorithm analysis and cause alternative algorithms to be explored. Automatic scheduling tools are used in the mapping phase to assist in the partitioning of the signal processing dataflow graph and the mapping of those partitions in space and time over multiple dynamically reconfigurable devices.

The final step in the process is the generation of the detailed programming, both for the reconfigurable devices as well as for the programmable processor that is controlling the adaptive computing resource. The entire process is driven by a set of libraries that provide a common database to present signal processing elements. Included in this approach is the idea that logic generators can be "smart," e.g. changing their

Figure 1. Use of Capabilities to Develop an Adaptive Computing System.

implementation according to desired design characteristics such as maximum throughput or minimum power.

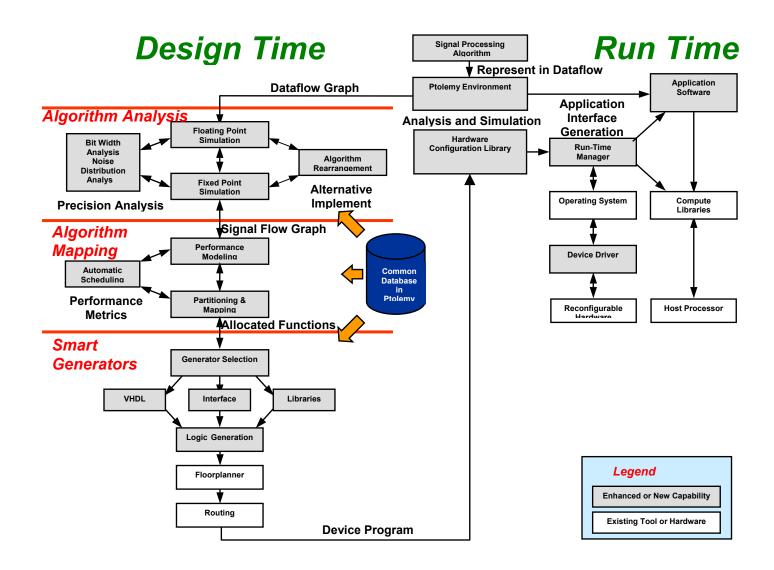

Figure 2 below expands the above design process to include how the designed system flows into run time execution. As can be seen, once the logic generation is complete from the use of the smart generators, commercial tools are used for the place and routing and hardware bitstream configuration file generation. In the run time environment, the hardware configuration is used (loaded to the device) in conjunction with the application software, host operating system and actual device to run the application.

Figure 2. Design Time and Run Time Environments for an Adaptive Computing System Implementation Using the AAME Tools.

#### 4 **Progress**

Over the past four years, the BAE Systems team members involved in this program have successfully developed an integrated algorithm analysis and mapping environment for translating a dataflow representation of a signal processing algorithm into an Adaptive Computing System (ACS) consisting of field programmable gate array (FPGAs) devices. This environment now allows designers to transform signal processing algorithms into FPGA-based hardware an order of magnitude faster than is currently possible. Our approach was to focus on three areas of capability critical to the success of adaptive computing: algorithm analysis, algorithm mapping, and smart generators. These capabilities take advantage of the special characteristics of signal processing algorithms to reduce the time to field the ACS implementation, and are being implemented as

extensions to the Ptolemy design environment (<u>http://ptolemy.eecs.berkeley.edu</u>) developed at the University of California, Berkeley.

The algorithm analysis capabilities developed on this program significantly reduce the effort required to find good ACS implementation choices for a signal processing algorithm. The environment provides algorithm designers with information about operation counts, including adds, multiplies, and memory accesses, and with analysis of quantization effects related to ACS implementations. The tools produced under this program help ensure mappings of an algorithm to an FPGA architecture are successful with regards to limiting wordlength growth without sacrificing algorithm performance. Optimal wordlength combinations for dataflow graphs can be determined quickly using the tools developed. In our work, we use a Markov Chain Monte Carlo (MCMC) sampling approach [1,2] to finding good wordlength combinations for DSP flowgraphs. We define a feasible region of wordlengths that consists of designs near the Paretooptimal cost/quality boundary which also satisfy any feasibility constraints. The MCMC sampler is used to generate uniform samples from this feasible region by performing a random walk on a specially constructed Markov chain; this approach solves a problem that can be very difficult using only naive sampling approaches. Additionally, the MCMC method offers extreme simplicity in the software coding of the algorithm, in contrast with dynamic programming approaches. With these techniques and capabilities, an algorithm designer can quickly determine the appropriate number of bits for signal representations at all points in the design and quantify the performance of various implementation choices.

On this program we have successfully developed mapping techniques for ACS tailored to signal processing. These capabilities include performance analysis, multi-device partitioning assistance, and automatic scheduling. The scheduling and partitioning functions use the coarse-grain nature of signal processing dataflow graphs to help optimize partitioning for ACS. Our tools automatically generate the VHDL code needed to translate data paths across different FPGA devices.

To augment the normal methods of logic generation for ACS, i.e. either built around libraries of functions or around general-purpose logic synthesis, we successfully implemented "smart generators". The smart-generators exist now as extensions to the concept of a parameterized library. These generators are tailored to signal processing functions and will include rules that capture specific implementation techniques and trade-offs. For example, a smart generator for a complex multiplier is able to trade between a three-multiplier implementation and a four-multiplier implementation according to area and latency constraints. Additionally, we have provided mechanisms to automatically generate both hardware and software interfaces for the resultant ACS. Our initial and primary target system has been a Xilinx XC4062XL-based Wildforce<sup>™</sup> board from Annapolis Micro Systems http://www.annapmicro.com. We also augmented our tools to provide limited Virtex technology support, such as that used with a Xilinx Virtex<sup>™</sup> XCV1000-based Wildstar<sup>™</sup> board, also from Annapolis Micro Systems.

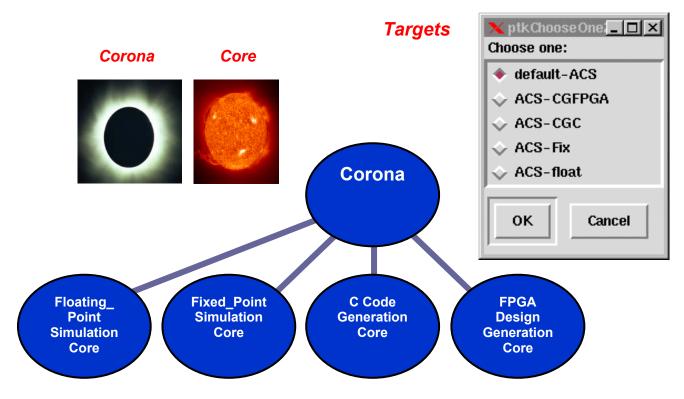

The algorithm analysis, mapping, and logic generation capabilities have been developed as extensions to Ptolemy. Ptolemy provides a well documented, object-oriented, open software architecture with implementations in C++ and Java. Our extensions to Ptolemy have been captured in a new ACS domain that separates the interface specification from implementation for each signal processing functional block. The algorithms of interest to this project are represented by dataflow graphs comprised of these functional blocks, following a synchronous dataflow model of computation. We have used a Corona/Core architecture, where each block has a common interface known as the Corona, and one or more implementations, known as the Cores. A retargeting mechanism allows the users to change Cores and hence implementation, which moves the dataflow graph between various simulation models (floating point, fixed point) and implementations (C code, VHDL code).

The ACS tools have been used to automatically implement several applications along the various stages of development of the tools capabilities. These have included four main demonstrations and several others. The four main demonstrations included:

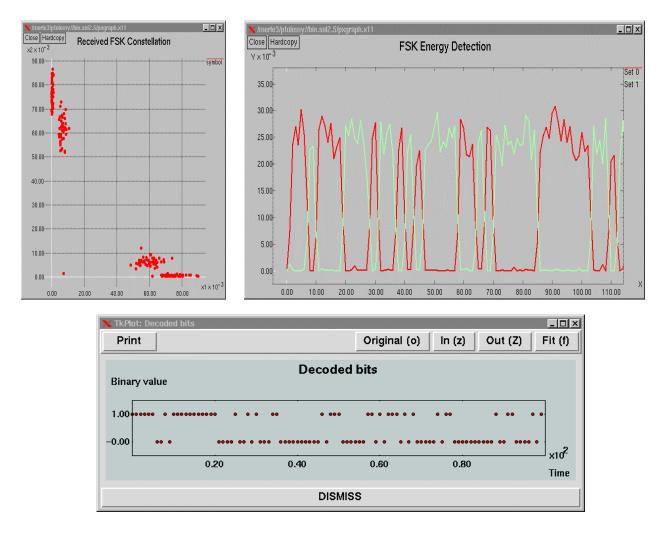

- A Winograd Discrete Fourier Transform (DFT) as part of a channelized frequency shift-keyed (FSK) receiver in ACS. The Winograd algorithm structure has the minimum number of multiplications for any DFT approach, and was thus ideal for FPGA implementation. This demonstration was shown at the April 1999 DARPA ACS PI meeting.

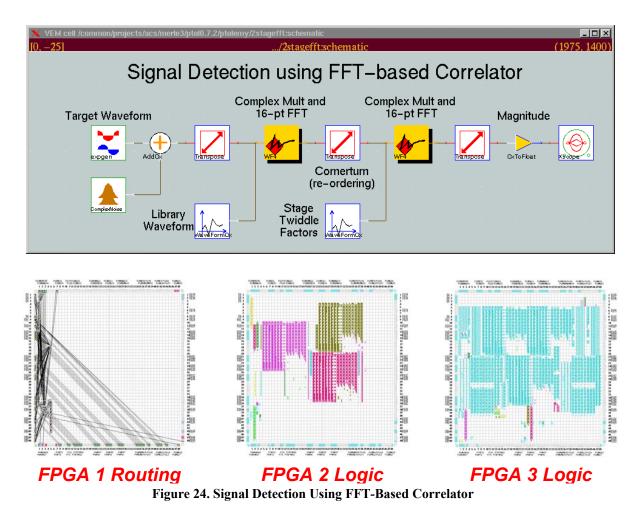

- A signal detection scheme (template matching) using an FFT-based correlator. This implementation involved an FFT-based complex correlator, requiring the use of two 16-point complex FFT cores in series with a cornerturn to obtain a 256-point spectrum. This demonstration was shown at the April 2000 DARPA ACS PI meeting.

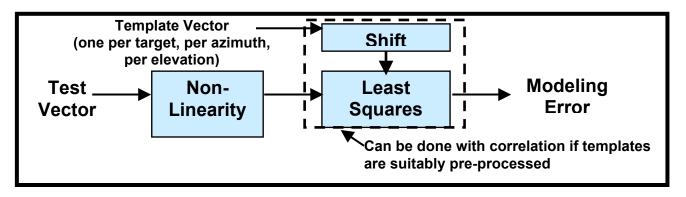

- Initial workings/progress towards accelerating a high resolution radar templatematching application (System-Oriented High Range Resolution Automatic Recognition Program (SHARP)). This demonstration was shown at the October 2000 DARPA ACS PI meeting.

- Full implementation of the accelerated SHARP algorithm on multiple FPGA devices.

Additional demonstrations developed using the ACS tools as the program and tools capabilities progressed included comparison of fixed point vs floating point implementation/results for smaller algorithms (e.g. a "Butterfly" generation algorithm), the first demonstration of the tools automatic implementation of multi-FPGA use (for a magnitude calculation), and the development of an FPGA implementation of a high speed linear FM detector (for the Reconfigurable Algorithms for Adaptive Computing (RAAC) program).

In all cases above, the ACS tools were used to simulate the algorithm, select appropriate fixed-point representations, and generate the VHDL implementations. The final FPGA

designs were obtained synthesizing the VHDL and performing place and route with commercial tools.

Along with the above applications/demonstrations, there have been four software releases of the ACS tools that incorporated enhanced tools capabilities developed up to the point of the software release. The first release was in June 1998, the second in April 1999, the third in August 2000 and the fourth in July 2001. Each was released as an update to the ACS domain of the UC Berkeley Ptolemy Classic project (delivered to UCB for incorporation into Ptolemy source code).

The sections that follow describe in detail the progress achieved for each development effort under the AAME program.

## 4.1 Algorithm Analysis and Mapping

The two development areas of algorithm analysis and mapping can be distinctive in areas of theoretical usage in the implementation of an algorithm to an ACS system. For example, the areas associated with algorithm analysis can be categorized as SNR analysis, alternative implementations and functional approximations. Algorithm mapping can be considered related to timing and sizing estimation, scheduling, and partitioning of the algorithm pieces across multiple FPGAs. This is generally what was expected during the initial development work. However, as development progressed, it was apparent that the two are much more closely related, one affecting the outcome or iteration of the other. For this reason, this section discusses the development efforts and results of the algorithm analysis portion along with the mapping efforts.

As a result of the efforts in these areas, design space exploration has been automated. In this regard, we have developed and applied bit width optimization theory (Markovian modeling) for algorithm analysis and implemented a bit width optimization tool to trade signal to noise ratio (SNR) versus hardware complexity. In addition, we have implemented pipeline alignment and scheduling algorithms for signal processing dataflow graphs. These latter capabilities automatically generate "algorithm-specific" sequencer and memory control logic, handle uni-rate and multi-rate signal processing, and allow for single and multi-FPGA implementations.

## 4.1.1 Algorithm Analysis

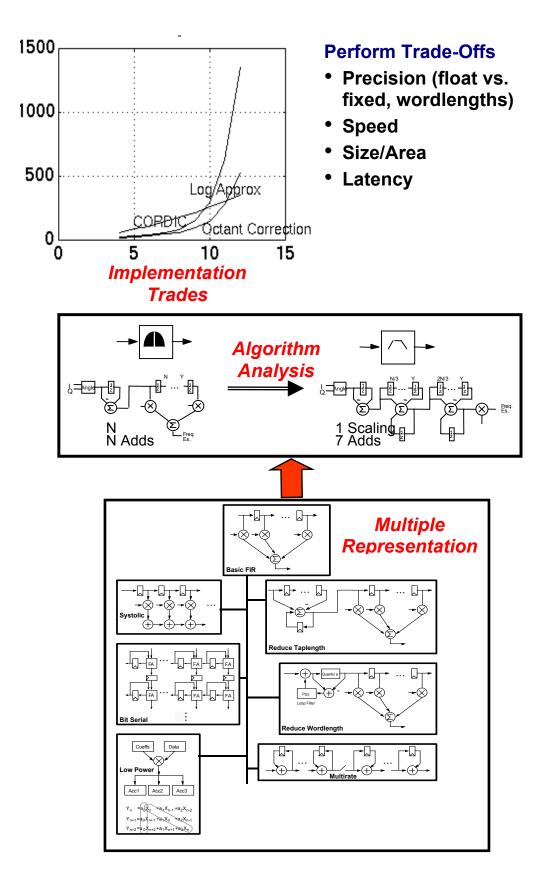

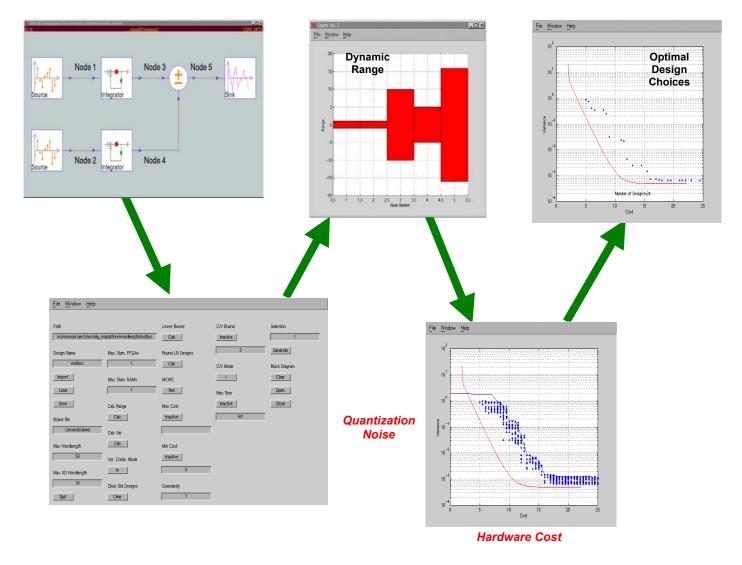

There are often approximations that can be made in order to improve the efficiency of an algorithm. These could include variable wordlengths and data representation, and approximations to functions in order to reduce system complexity. Figure 3 below shows some of the trade-offs that should be considered, such as precision, speed, size/area and latency.

Figure 3. Algorithm Trade-Offs

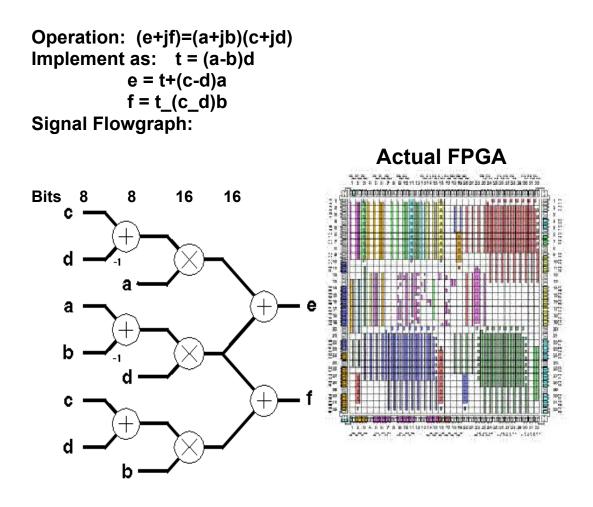

Although custom wordlengths reduce HW requirements for a given algorithm and reduces unecessary switching and power dissipation. However, a DSP system now becomes an approximation yieldig degraded results. Therefore, the goal was to find good wordlength combinations satisfying the criteria that 1) the design fits in an FPGA and 2) acceptable performance is maintained. The following example in Figure 4 for a complex multiply demonstrates factors that were considered in developing the wordlength analysis tools.

Figure 4. Complex Multiply

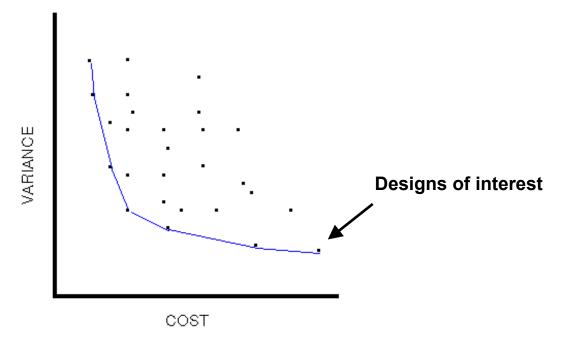

For the above example, we would like for both the HW cost and the rounding noise variance to be low. However, since you cannot have both, interesting combinations must be considered as shown in Figure 5 (cost vs. variance).

Figure 5. Cost vs. Variance for Complex Multiply Designs

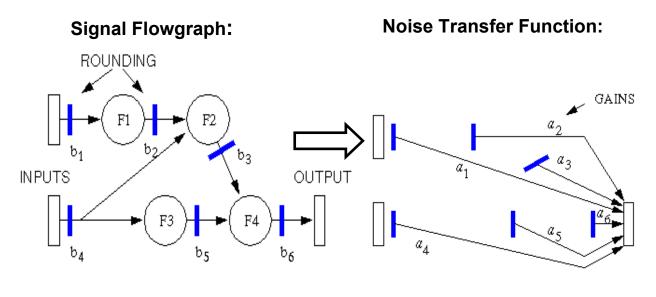

Based on the above, cost and variance estimate functions had to be developed/employed. Figures 6 and 7 below show variance and cost estimates respectively.

B<sub>2</sub> Noise Gain Calculation:

Figure 6. Variance Estimates

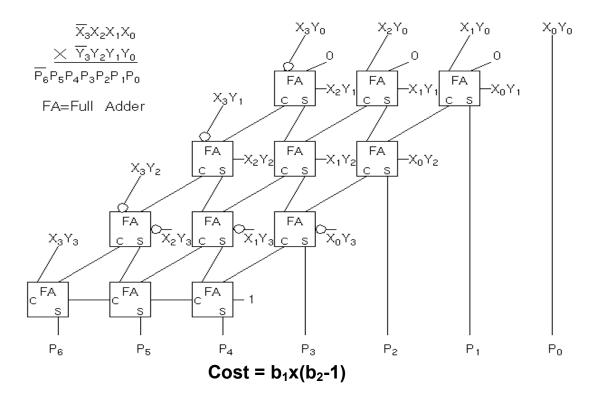

## **b**<sub>1</sub>x **b**<sub>2</sub> Multiplier Array Example

**Figure 7. Cost Estimates**

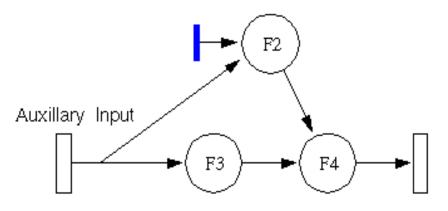

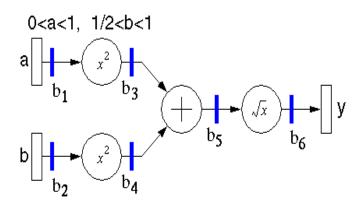

The following example of a magnitude calculation is an example that provided insight into our development of the tools for algorithm analysis. Figure 8 shows the data flow graph and the associated cost and variance calculations.

Cost= $b_1^2 + b_2^2 + \max(b_3, b_4) + 1 + b_5 b_6$ Variance= $2^{-2b1}/15 + (2^{-2b2} + 2^{-2b3} + 2^{-2b4})/12$ + $(2^{-2b5} + 2^{-2b6})/3$

Constraints:

$$b_3 \le 2b_1$$

$b_4 \le 2b_2$

$b_5 \le \max(b_3, b_4)+1$

$1 \le b_i \le 32$

#### Figure 8. Cost and Variance Estimates for a Magnitude Calculation

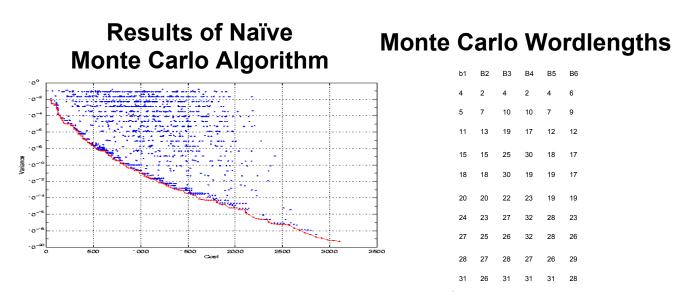

Figure 9 shows the results if a "naïve" monte carlo calculation were used to explore the cost vs. variance of different designs within the design space and the resultant Monte Carlo wordlengths.

Figure 9. Results of Naïve Monte Carlo Algorithm and Monte Carlo Wordlengths

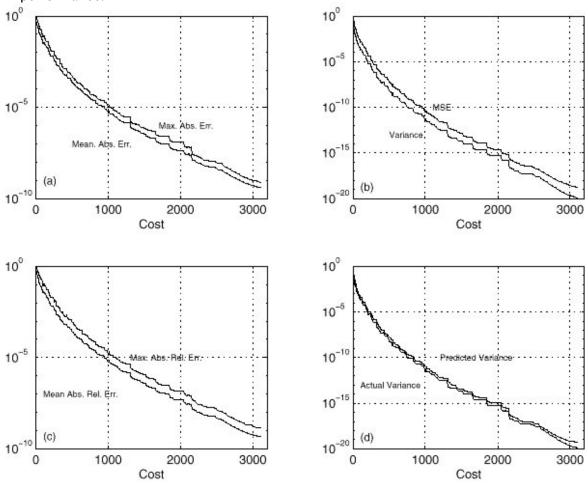

The following charts of Figure 10 show a comparison of predicted versus actual performance.

Figure 10. Comparison: Prediction vs. Actual Performance

It could be seen that the Naïve sampling approach with the Monte Carlo algorithm wasted samples due to exploration of inefficient regions in the cost/variance plane. Also, when a violation of the constraints occurs, the sample is discarded. Since the design space is exponential in the number of design parameters, it is essentially infeasible to exhaustively test all combinations. This problem only gets worse in multiple dimensions which can include multiple outputs sharing HW building blocks. A better solution was needed.

The improved solution was the use of Markov Chains. A Markov Chain can be described as follows:

- Current state is a vector of wordlengths b

- Transitions involve +/- 1 one of the b elements

- Possible transitions are chosen randomly with equal probability

- If a transition would cross from feasible to infeasible, the current state is maintained

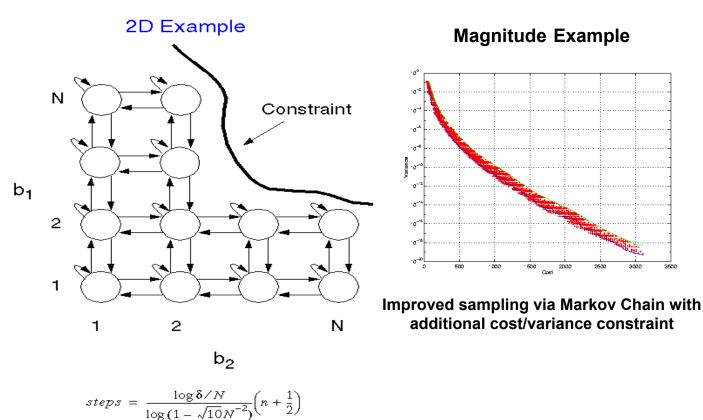

In this manner, a random walk is performed on the Markov Chain, testing b along the way. It can be shown that each feasible stae has equal probability of being sampled (after some number of steps). Figure 11 below shows an example of improved sampling using Markov Chain sampling.

# 20

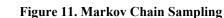

An additional modified approach that we took provided an iterative approach to the Markov Chain sampling. This was done to overcome the fact that the cost/variance constraints are not usually known. In this fashion, each iteration uses only a small number of samples. The first time through, no constraints are applied. After each iteration, a curve is passed through the best lower bound. As the curve moves up, the curve becomes the next constraint. To determine the lower bound for optimization, and referring to Figure 12 below, the following steps are taken:

- Given C(b) and V(b) (cost and variance as a function of wordlength b)

- Start with a=0

- Minimize C(b) + aV(b) through choice of b

- Slightly increase a, and repeat

Figure 12. Lower Bound for Optimization

The code uses several optimizations to enhance speed. This procedure can be used for initializing the Monte Carlo method.

The resultant user interface for the analysis tools was developed in Matlab and is shown in Figure 13. As stated earlier, this user interface evolved into a tool deeply integrated in both the algorithm analysis and algorithm mapping phases. Specific details of the tools uses is described in the procedure at the end of this section.

| <u>File Window H</u> elp                               |                   |                  |           |               |

|--------------------------------------------------------|-------------------|------------------|-----------|---------------|

|                                                        |                   |                  |           |               |

| Path                                                   |                   | Lower Bound      | C/V Bound | Selection     |

| /common/projects/acs/alg_map/pfiore/wordlength/multacc |                   | Calc             | Inactive  | 1             |

| Design Name                                            | Max. Num. FPGAs   | Round LB Designs | 2         | Generate      |

| multacc                                                | 1                 | Calc             | C/V Mode  | Block Diagram |

| Import                                                 | Max. Num. RAMs    | МСМС             | 1         | Clear         |

| Load                                                   | 1                 | Bun              | Max Time  | Open          |

| Save                                                   | Calc Range        | Max Cost         | Inactive  | Close         |

| Board File                                             | Calc              | Inactive         | Inf       |               |

| Unconstrained                                          | Calc Var          |                  |           |               |

| Max Wordlength                                         | Calc              | Min Cost         |           |               |

| 32                                                     | Var. Comb. Mode   | Inactive         |           |               |

| Max I/O Wordlength                                     | m                 | 0                |           |               |

| 16                                                     | Clear Old Designs | Granularity      |           |               |

| Quit                                                   | Clear             | 1                |           |               |

Figure 13. ACS Tools User Interface

Based on the development stages of the algorithm analysis capabilities of the tools, we determined the following general conclusions regarding algorithm analysis:

- There is a great demand for custom DSP implementations

- New devices match well with DSP requirements

- Optimizing DSP designs can be difficult

- Random sampling methods fail for large problems

- The Markov Chain for uniform sampling solves this problem

- Lower bounding calculation is useful and easy to calculate

#### 4.1.2 Algorithm Mapping

The objectives of algorithm mapping were three-fold:

- Performance Modeling provide feedback on utilization, throughput, efficiency, etc... The feedback should be used by the algorithm analysis capabilities.

- Partitioning and Mapping break large data flow graphs into groups and map those groups across multiple devices and across time.

• Automatic Scheduling - automatically determine the firing sequence, optimal mappings and sequence of configurations.

As a result of the development efforts related to algorithm mapping, the tools capabilities matured to include cost analysis as part of the wordlength analysis, the capability for automated uni-rate and multi-rate pipeline alignment and scheduling through developed algorithms, and support for memory allocation.

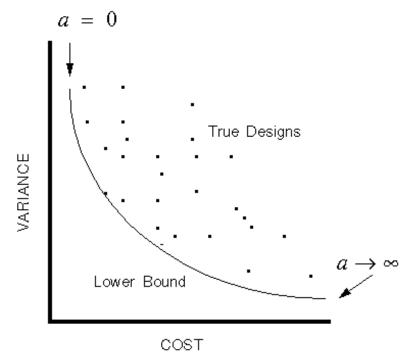

For algorithm mapping, it is appropriate to first describe criteria related to the target architecture associated with our tools environment (see Figure 14 below). The number of reprogrammable devices was targeted initially for a single FPGA device. The final target supported evolved to multiple devices on a board. Device interconnections were defined as fixed interconnect with predicable delays. The I/O interfaces included shared memory attached to the reconfigurable devices. The dataflow model used was one of Synchronous dataflow, supporting first uni-rate and then multi-rate dataflow. Modes of operation included uni-rate, pipelined, synchronous operations. Two target architectures were used on this program. These included the Annapolis Micro Systems Wildforce<sup>TM</sup> (Xilinx 4000 series) and Wildstar<sup>TM</sup> (Xilinx Virtex<sup>TM</sup>). The primary support provided under this program was for the Wildforce<sup>TM</sup>.

Figure 14. Target Architectures

The processing model used was well-matched to the Ptolemy Synchronous Dataflow (SDF) Domain in the following manner:

- The use of unit and block token produce and consume amounts

- The Netlist structure determines the execution order constraints

- Pipeline delay information is required to determine absolute timing

- Delays are set to align pipelines for the maximum throughput

- Delay can be automatically determined from block parameters

The processing model is a combination of a fully synchronous model and tagged synchronous models in that no handshaking or tags are used but data is not always valid. Data validity is implicit in the timing of latch signals. In addition, Memory access fits the same model in that data from a common memory is demuxed into separate streams running at lower rates and data to the common memory is multiplexed to a single port.

Another characteristic of the processing model is that multiple FPGAs introduce additional pipeline delays. The last feature of the processing model which was successfully developed and integrated into the tools environment was support for multirate parameterized execution, allowing for the significant achievement of supporting multiple data streams through the same FPGA device at different rates.

To begin the process of algorithm mapping, a method of creating the appropriate netlist had to be developed. A Macro Level Netlist Generator was developed that translates the algorithm blocks into a high-level netlist. This netlist is different from HDL approaches because the netlist at this level is more abstract than a wire-accurate low-level netlist. In this mode, where the hardware memory is a variable and the correct design is not already in a library, the Macro Level Netlist Generator compiles information about the hardware design.

With a macro netlist generated, additional functionality and coordination is then needed to actually produce a low-level netlist and hardware design. To assist in these functions a function called the Stitcher was developed. The Stitcher uses the data produced by the Macro Level Netlist Generator to coordinate the production of an actual low-level netlist and hardware design. This is done by properly accessing information produced by or contained in the Smart Generators (Smart Generators to be discussed in the next section), information regarding the optimal design choice determined through the use of the wordlength analysis tool and scheduling information, and then augmenting the netlist with this information, commanding the Smart Generators to actually create their associated hardware, and then linking all the hardware designs together.

Scheduling is performed by uni-rate and multi-rate sequencers developed on this project. Scheduling of the algorithm onto the FPGA hardware involved pipeline rearrangemnet and data port conflict resolution. To perform these functions, elements need to be added into the netlist. These include, for example, delays, multiplexers, address generators, tristates, and latches, each of which has its own Smart Generator. At this point, the detailed low-level design can be created.

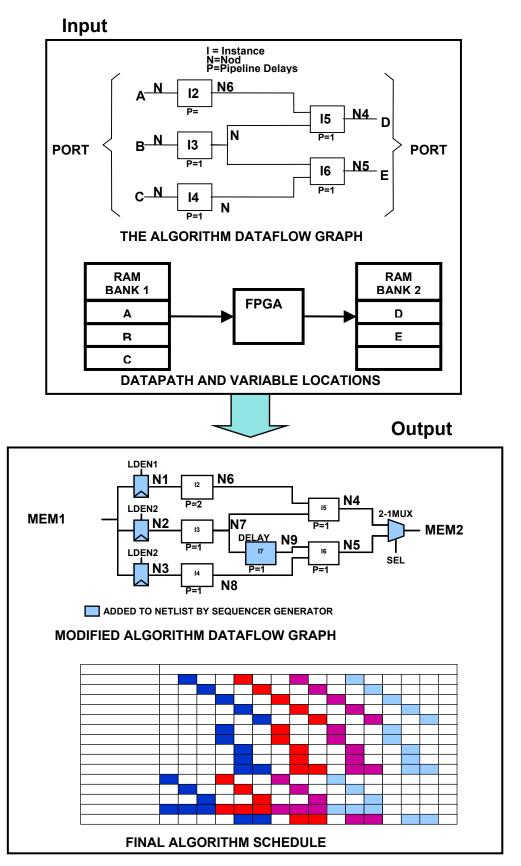

The scheduling algorithms of the sequencers that were developed can be described through an example. Figure 15 shows a conceptual algorithm data flow graph with three inputs, two outputs and five operations or "instances". The three input vector streams A,B and C all reside in one bank of RAM (also called a Port). The two output vectors D and E reside in a second port. All data vectors are assumed to be of the same size. All the instances in the design will be created with a pipeline delay of one, except 12, which requires a pipeline delay of two. Because of the unequal amount of pipeline delays, extra delays must be appropriately added to the netlist to correctly align the pipelines.

In addition to this pipeline alignment problem, the usage of the data ports must be correctly scheduled. For example, we cannot schedule D and E to be written at the same time. Our approach is to add multiplexers to the netlist for cases where multiple outputs go to the same port. We also add tristate buffers for cases both reads and writes to the same port can occur. Latches for input data can also be provided. These are not strictly necessary, but can provide for improved timing.

Figure 15 shows the results of this scheduling operation. Note the addition of the input latches, the internal delay, and the output multiplexer into the netlist by the sequencer. The Stitcher also connects all logic ports to the appropriate physical port. The timing chart in the figure shows the activation sequence of the internal nodes of the algorithm as well as the activity of the multiplexer control signal, latch load enable signal, and port activity. Several consecutive launches are shown in the chart. Note that the maximum launch rate of three cycles is attained.

Figure 15. Pipeline Alignment and Schedule Determination Required for Logic Synthesis

In order to provide proper sequencing of data vectors, each bank of hardware memory requires an Address Generator. In our approach, the parameters needed by the Address Generators associated with a computation are automatically derived by the Macro Level Netlist Generator. This information is used by the stitcher to calculate needed address offsets. During the scheduling, the stitcher derives an Address Generator for each data port. This approach frees the algorithm designer from the task of writing code or developing hardware fro this purpose. Also, we found that generating custom address generators for each algorithm substantially reduces the required amount of logic from what would be required for general purpose address generators.

The following, along with Figure 16, depicts the final evolved state of the wordlength analysis tools and the interrelation and capabilities among the algorithm analysis and mapping design spaces:

Figure 16. Wordlength Optimization Analysis

- The wordlength analysis tools starts by importing the macro level netlist and associated smart generator files from Ptolemy. These files are the rangecalc, natcon, numsim, cost, and schedgen files, whose functions will be described below.

- The wordlength tool next calculates the numerical range of each arc of the flowgraph. The rangecalc files from each hardware instance in the graph are used for this purpose. Essentially, the numerical range at the inputs of a particular instance is propagated to the outputs. The process is iterated until all numerical ranges are known. The manner in which a particular rangecalc file determines its output range is dependent on the mathematical function implemented by the instance.

- Once the ranges are calculated, we must now calculate the variances scale factors for every arc in the flowgraph. These determine the effect of rounding on the outputs of the graph. The various numsim files from each hardware instance in the graph are used for this purpose. These numsim files simply mimic the numerical properties of their corresponding mathematical function. They are used by exercising the flowgraph with random data, and then sligthly perturbing various graph points, so that an approximation to the gradient of the output of the graph can be obtained. This in turns determines the variance scale factors to be used in the subsequent optimization.

- With the variance scale factors now known, we are ready to find actual good designs, using the Markov Chain Monte Carlo (MCMC) method. The tool performs a random walk, keeping the best designs, as determined by the variance of a particular wordlength combination, as well as its cost. The costs are calculated by using the cost smart generator files.

- The random walk is modified by use of the natcon smart generator files. These files place constraints on allowable wordlength combinations. For example, many of the Coregen library elements nly allow certain input and output wordlength combinations; this knowledge is captured in the natcon files. If the random walk violates a natcon contraint, that particular design is discarded.

- The algorithm scheduling is also performed during the random walk. This is necessary because most hardware instances have schedules and latencies that change as a functions of the wordlengths. The individual schedgen smart generator files provide local information about the behavior of each instance. During the random walk, when a particular wordlength combination is proposed, the individual schedules are fitted together so that an efficient overall schedule results. Note that instances with differing data rates and latencies are easily handled by this approach.

- The user typically performs multiple random walks; the tool remembers the best designs from all the walks. As the design exploration progress, the user has the ability to control the regions of the design space that the tools visits. This is done by setting bounds on the minimum or maximum cost that will be tolerated, the maximum total latency of the design, and most importantly, an upper bound on cost/variance combinations to allow in the random walks.

- This last constraint greatly improves the efficiency of the random walks. As the set of optimal designs improves (approaches the theoretical lower bound), the tool can place a reasonable upper bound on cost/variance combinations to consider. When the random walk would violate this constraint, the step is simply not taken. It can be shown that the resulting feasible region will be uniformly covered by a random walk (in the limit). By gradually moving the upper bound closer to the set of optimal designs so far discovered, we shrink the feasible region so that it approaches only the truly optimal set of feasible designs.

- Once the user has a set of designs that are good enough, the tool allows the user to check the schedule of various designs, and to then select one to actually build. The selected design is translated into a macro level netlist, with the actual wordlengths and schedule information. This data is then used by the sticher to construct the VHDL for the design.

#### 4.2 Smart Generators

Smart generators provide a systematic way to capture design information about specialized arithmetic structures. Smart generators allow for rapid population of libraries with new components by capturing algorithm-specific implementations, from the bit-level up to the coarse grain function level, and by making information about the implementation available for the hardware design and implementation process and tools. An algorithm designer specifying a mathematical operation may not be aware of many of the ingenious implementations that have been developed. Even simple structures such as adders, multipliers, and filters have an enormous array of implementation alternatives, many of which have been finely tuned by computer architects and VLSI designers. A Smart Generator can choose the correct implementation considering the user's specification and the target technology. This approach is different and more powerful than a simple parameterized building block.

A novel feature of the Smart Generator is the ability to utilize other Smart Generators in constructing its hardware implementation. Very useful higher-order functions can be constructed in this manner using hierarchical and normal Smart Generators, with a minimum of effort. For example, filters, FFTs, and linear algebraic operations such as matrix multiplication can be constructed out of simpler building blocks such as additions, subtractions, multiplications, and divisions. A Smart Generator may actually choose among multiple implementation strategies that are known to the designer, and may even call itself with different design parameters.

To actually write a Smart Generator, we had to invoke basic element building blocks which were appropriate to the FPGA technology we used. The basic building blocks for the Xilinx 4000 series FPGA logic family, the primary FPGA technology used on our program, is described as:

• AND, NAND, OR, NOR – Simple combinatorial logic

- NOT, XOR, XNOR Simple combinatorial logic

- 16ROM Generic 4-input 1-output combinatorial logic element

- FD Positive edge triggered flip-flop

- FDCE Positive edge triggered flip-flop with clock enable and clear

- VCC,GND Used to tie off an input to a fixed high or low voltage

- FA Full adder

- FA2 Two bits of a fast ripple carry adder string

- CONNECT Connect two signals together

The objectives associated with the development and use of Smart Generators included:

- Parameterized libraries generate node implementations for specified bit widths and parameter values

- Hierarchical representations provide generators that can recursively call other generators

- Interface generation automatically generate software to move data between generalpurpose processor and the reconfigurable platform and to manage sequences of configurations

- General synthesis provide device independent representation of implementation

The above objectives were accomplished. We were successful in implementing a portable logic synthesis methodology for VHDL. We integrated Xilinx Core Generators (4000 Series) capability within the VHDL code generation. In addition, we implemented smart generators for state machine and memory control requirements. Lastly, Smart Generators that can call other Smart Generators (hierarchical generation) were developed and implemented.

During development of the multirate sequencer for scheduling, it was discovered that for multirate operation, each input and each output of each instance Smart Generator must have a corresponding "enable" control point. This represented a change from the unirate approach, where one enable control for the entire star (function) was sufficient. It is acceptable for the enable control to be internally unconnected, if the Smart Generator does not depend on its operation. In this case, the synthesizer will prune any control logic associated with this unconnected input. If the enable is connected internally, the understanding is that any storage elements driven by that enable signal only change state when the enable signal is active. This mechanism is necessary so that state can be saved between initializations.

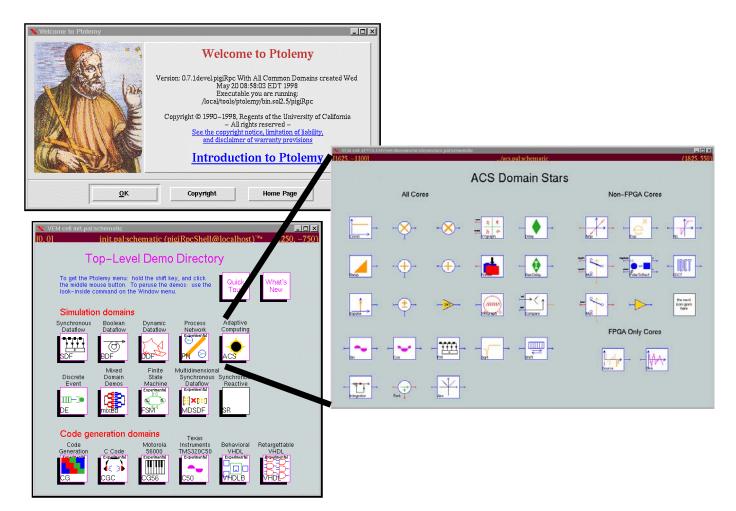

## 4.3 Ptolemy Integration and the ACS Domain

Other than the Matlab specific wordlength analysis tools, the new capabilities developed under this program were developed and integrated with the Ptolemy signal processing algorithm and implementation environment from the University of California (UC), Berkeley (Figure 17). Ptolemy supports heterogeneous system simulation and design using several different models of computation, each implemented in a separate domain. The class of application problems addressed by our work falls into Ptolemy's synchronous dataflow (SDF) domain, where the flow of data is predictable and does not change. In addition to its well-defined models of computation, Ptolemy provides an open software architectue with standard interfaces among its functional areas. Our choice of Ptolemy allowed both rapid insertions of our new capabilities as well as the ability for additional researchers to build their own extensions and libraries, an approach that has been successful in the past.

Figure 17. Ptolemy Project, University of California, Berkeley<http://ptolemy.eecs.berkeley.edu>

Within Ptolemy, there has traditionally been a distinction between simulation and implementation (code generation), and separate domains were created for each purpose. No implementations (code or hardware designs) could be generated from the simulation domains and simulation was not possible from the code generation domains. Also, it was not possible to move among different types of simulation (e.g. floating-point to fixed-point) or among code generation (e.g. C code, assembly code, hardware designs) without recreating graphs with different models.

Together with UC Berkeley, we extended Ptolemy by developing a new Adaptive Computing System (ACS) domain (Figure 18) that separates the interface specification from the implementation for each signal processing functional block, allowing simulation and design/code generation to exist in the same domain.

Figure 18. ACS Domain, Ptolemy Project

In the ACS Domain, algorithms are still represented by SDF graphs. We have used a "Corona/Core" architecture (Figure 19), where each block has a common interface known as the Corona, and one or more implementations, known as the Cores. A retargeting mechanism allows the user to change Cores and hence implementations. The Implementation of a data flowgraph between various simulation models (floating-point, fixed-point) and implementations (C code, VHDL code) is accomplished by simply selecting a different target.

Figure 19. ACS Domain, Corona/Core and Targets

During January, 2000, in the process of integrating the multirate tool, we decided on several multirate blocks to add to the palette of Ptolemy ACS stars/core. These were as follows:

- "Commutator": This block sends one input to N outputs in a round robin fashion. Input and outputs same numerical format.

- "Mux": This multiplexer is actually a unirate block. Every input and every output is valid every clock cycle. One input is propagated to output, chosen by "select" input. Data formats on input and output must be identical. Select lines format must be internally locked. Note that a demultiplexer cannot be incorporated into the current system because the output activation times would be data dependent and therefore not deterministic (i.e. not synchronous).

- "Interleaver": This block is the reverse operation of the commutator, with N inputs and a single output. The output is valid every clock cycle, inputs selected in a round robin fashion. A starting phase field in the edit box will be implemented.

- "Downsampler": The input to this block is valid every clock cycle, and it produces a valid output every Nth clock cycle. Data formats on input and output must be identical. A starting phase field in the edit box will be implemented.