#### Graphical Design Tutorial for HDL Author - Graphics, HDL Designer - Graphics HDL Author - Pro and HDL Designer - Pro

Software Version 2001.3

7 June 2001

Copyright © Mentor Graphics Corporation 1996-2001. All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

Contractor/manufacturer is: Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

> Web site: http://www.hdldesigner.com Email: hdldesigner\_support@mentor.com

This is an unpublished work of Mentor Graphics Corporation.

#### **Trademark Information**

The following names which appear in this documentation set are trademarks, registered trademarks or service marks of Mentor Graphics Corporation:

HDL Designer Series<sup>™</sup>, HDL Designer<sup>™</sup>, HDL Pilot<sup>™</sup>, HDL Detective<sup>™</sup>, HDL Author<sup>™</sup>, HDL2Graphics<sup>™</sup>, FPGA Advantage<sup>™</sup>, Interconnect Table<sup>™</sup>, Interface-Based Design<sup>™</sup>, IBD<sup>™</sup>, Inventra<sup>™</sup>, LeonardoInsight<sup>™</sup>, LeonardoSpectrum<sup>™</sup>, Mentor<sup>™</sup>, Mentor Graphics<sup>®</sup>, Model*Sim*<sup>®</sup>, ModuleWare<sup>™</sup>, Renoir<sup>™</sup>, Seamless<sup>®</sup> and Seamless CVE<sup>™</sup>.

The following names which appear in this documentation set are trademarks, registered trademarks or service marks of other companies:

Adobe, the Adobe logo, Acrobat, the Acrobat logo, Exchange, FrameMaker and PostScript are registered trademarks of Adobe Systems Incorporated.

Altera, MegaWizard and MAX+PLUS are registered trademarks and Quartus a trademark of Altera Corporation.

ClearCase Attache is a trademark and ClearCase is a registered trademark of Rational Software Corporation.

DesignSync is a registered trademark of Synchronicity Incorporated.

FLEXIm is a trademark of Globetrotter Software, Incorporated.

Hewlett-Packard (HP), HP-UX and PA-RISC are registered trademarks of Hewlett-Packard Company.

Leapfrog, NC-Verilog, Verilog and Verilog-XL are trademarks and registered trademarks of Cadence Design Systems Incorporated.

Netscape is a trademark of Netscape Communications Corporation.

Quartus and APEX are trademarks of Altera Corporation.

SPARC is a registered trademark and SPARC station is a trademark of SPARC International Incorporated.

SpyGlass is a trademark of Interra Inc.

Sun Microsystems and Sun Workstation are registered trademarks of Sun Microsystems Incorporated. Sun and SunOS are trademarks of Sun Microsystems Incorporated.

Synopsys, Design Analyzer, Design Compiler, FPGA Express, VCS, VCSi and VSS are trademarks of Synopsys Incorporated.

Synplify is a registered trademark of Synplicity Incorporated.

The Graphics Connection is a trademark of Square One.

Visual SourceSafe and Windows are trademarks of Microsoft Corporation.

UNIX is a registered trademark of UNIX System Laboratories, Incorporated.

Xilinx is a registered trademark and Core Generator a trademark of Xilinx, Incorporated.

Other brand or product names that appear in the documentation are trademarks or registered trademarks of their respective holders.

#### TABLE OF CONTENTS

| About This Manual                       | X    |

|-----------------------------------------|------|

| Introduction                            | X    |

| Copying Text From the Acrobat Viewer    |      |

| Example Designs                         |      |

| Chapter 1                               |      |

| VHDL Timer Exercise                     | 1-1  |

| Specification                           | 1-1  |

| Set Library Mapping                     | 1-2  |

| Set the Default Language                | 1-4  |

| Create a Block Diagram                  |      |

| Edit the Title Block Template           | 1-6  |

| Add Blocks                              | 1-7  |

| Add Embedded Blocks                     | 1-8  |

| Add Ports and Signals                   | 1-9  |

| Add a Bundle and Global Connector       | 1-11 |

| Save the Block Diagram                  | 1-12 |

| Edit Block and Signal Names             |      |

| Add an Embedded HDL Text View           | 1-18 |

| Add a Panel and Edit the Title Block    |      |

| Set State Machine Preferences           | 1-22 |

| Create a Child State Diagram            | 1-24 |

| Add States and Transitions              |      |

| Save the State Diagram                  |      |

| Edit the States                         |      |

| Edit the Transitions                    | 1-30 |

| Create a Hierarchical State Diagram     |      |

| Complete the Hierarchical State Diagram | 1-34 |

| Editing State Machine Properties        |      |

| Set Generation Properties               |      |

| Set Checks for HDL Generation           |      |

| Generate HDL for the State Machine      |      |

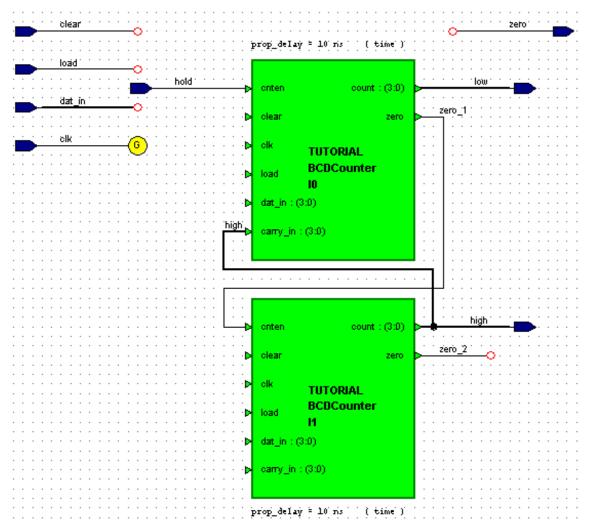

| Import the BCDCounter Design Unit       | 1-44 |

| Create a Child Block Diagram            |      |

| Edit the Generic Mapping            | 1-50 |

|-------------------------------------|------|

| Add ModuleWare Components           | 1-51 |

| Add a User Declaration              | 1-54 |

| Create a Truth Table                | 1-56 |

| Edit the Truth Table                | 1-57 |

| Set Truth Table Properties          |      |

| Browse the Timer Design             |      |

| Generate HDL for the Hierarchy      | 1-61 |

| Edit the Timer Symbol               | 1-63 |

| Create a Test Bench                 | 1-64 |

| Import the Tester Design Unit       | 1-66 |

| Instantiate the Imported Tester     | 1-67 |

| Generate HDL for the Test Bench     | 1-68 |

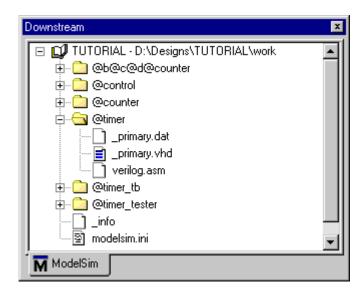

| Browse the Completed Design         | 1-70 |

| Setup the Downstream Tools          | 1-71 |

| Compile the Design                  | 1-74 |

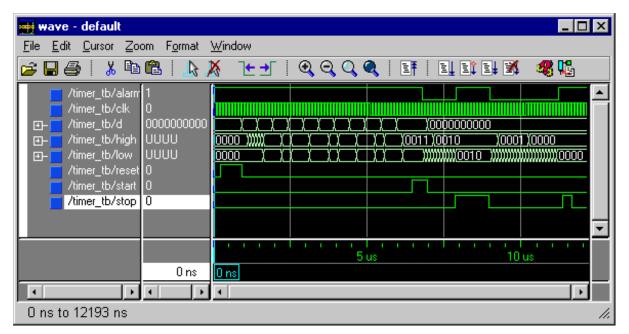

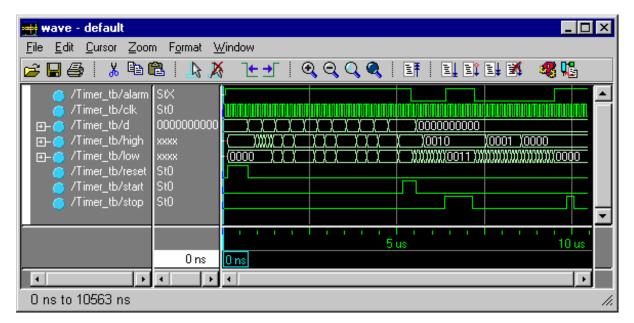

| Invoke the ModelSim Simulator       | 1-76 |

| Setup the Simulator Windows         | 1-77 |

| Enable Animation                    | 1-78 |

| Simulate the Design                 | 1-80 |

| Review the Animation                |      |

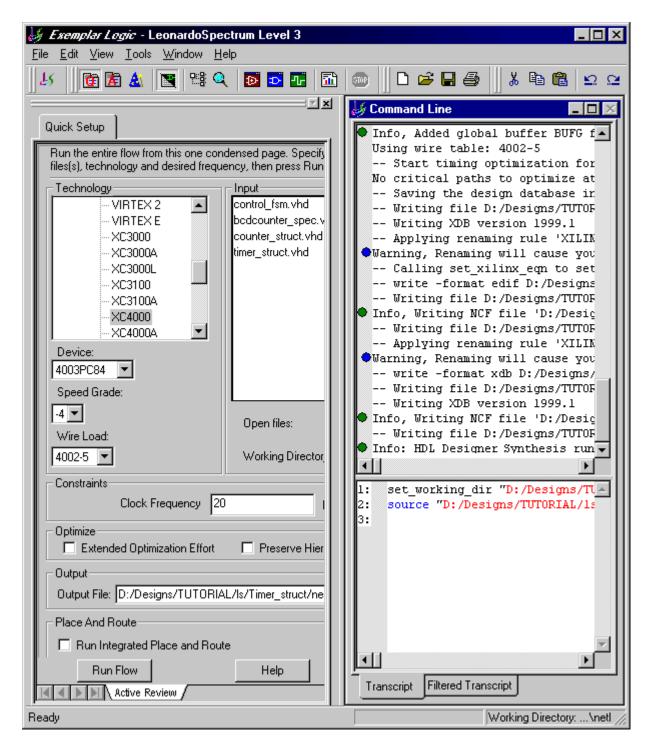

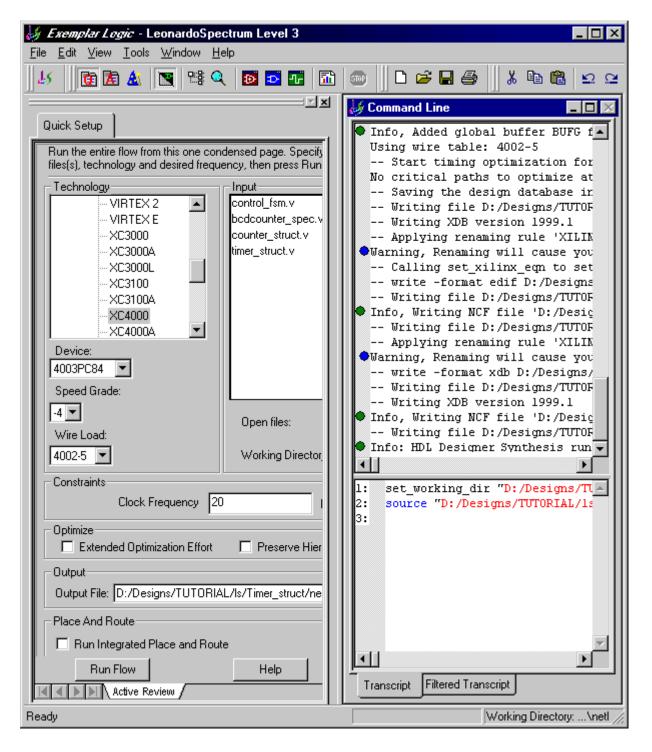

| Setup the Synthesis Tool            | 1-84 |

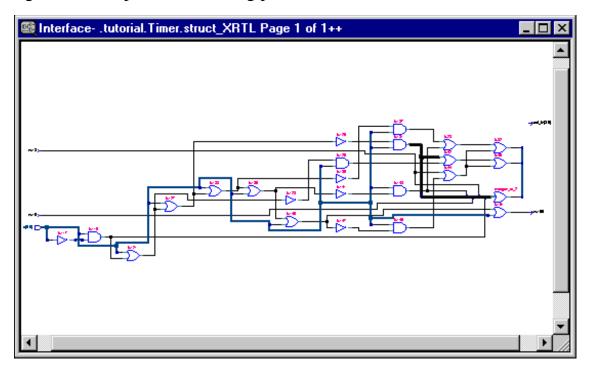

| Run the Synthesis Flow              |      |

| Using the Example VHDL Design       | 1-89 |

| Character 2                         |      |

| Chapter 2<br>Variles Timer Evension | 0.1  |

| Verilog Timer Exercise              |      |

| Specification                       | 2-1  |

| Set Library Mapping                 | 2-2  |

| Set the Default Language            | 2-4  |

| Create a Block Diagram              |      |

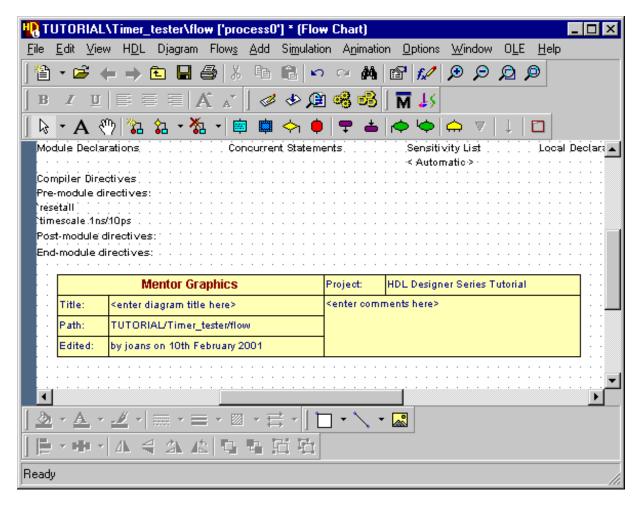

| Edit the Title Block Template       |      |

| Add Blocks                          |      |

| Add Embedded Blocks                 | 2-8  |

| Add Ports and Signals               | 2-9  |

| Add a Bundle and Global Connector       | 2-11 |

|-----------------------------------------|------|

| Save the Block Diagram                  | 2-12 |

| Edit Block and Signal Names             |      |

| Add an Embedded HDL Text View           | 2-18 |

| Add a Panel and Edit the Title Block    | 2-20 |

| Set State Machine Preferences           | 2-22 |

| Create a Child State Diagram            | 2-24 |

| Add States and Transitions              | 2-26 |

| Save the State Diagram                  | 2-27 |

| Edit the States                         | 2-28 |

| Edit the Transitions                    | 2-30 |

| Create a Hierarchical State Diagram     | 2-32 |

| Complete the Hierarchical State Diagram |      |

| Editing State Machine Properties        | 2-36 |

| Set Generation Properties               | 2-39 |

| Set Checks for HDL Generation           |      |

| Generate HDL for the State Machine      | 2-42 |

| Import the BCDCounter Design Unit       | 2-44 |

| Create a Child Block Diagram            | 2-46 |

| Edit the Parameter Mapping              | 2-50 |

| Add ModuleWare Components               |      |

| Add a User Declaration                  | 2-54 |

| Create a Truth Table                    | 2-56 |

| Edit the Truth Table                    | 2-57 |

| Set Truth Table Properties              | 2-58 |

| Add a Module Declaration                | 2-60 |

| Browse the Timer Design                 | 2-61 |

| Generate HDL for the Hierarchy          | 2-62 |

| Edit the Timer Symbol                   | 2-64 |

| Create a Test Bench                     | 2-65 |

| Import the Tester Design Unit           | 2-67 |

| Instantiate the Imported Tester         | 2-68 |

| Generate HDL for the Test Bench         | 2-69 |

| Browse the Completed Design             | 2-71 |

| Setup the Downstream Tools              | 2-72 |

| Compile the Design                    | 2-75 |

|---------------------------------------|------|

| Invoke the ModelSim Simulator         |      |

| Setup the Simulator Windows           |      |

| Enable Animation                      |      |

| Simulate the Design                   |      |

| Review the Animation                  |      |

| Setup the Synthesis Tool              |      |

| Run the Synthesis Flow                |      |

| Using the Example Verilog Design      |      |

| Appendix A                            |      |

| Using Text Design Tools               | A-1  |

|                                       |      |

| Introduction                          |      |

| Create HDL Text for the Control Block |      |

| Create HDL Text for the DtoB Block    |      |

| Importing the Tester Design Unit      | A-12 |

| Generating and Compiling the Design   | A-12 |

| Appendix B                            |      |

| Using Verilog-XL                      | B-1  |

| Introduction                          | B-1  |

| Setup Verilog-XL                      |      |

| Invoke the Verilog-XL Simulator       |      |

| Setup the SimWave Window              |      |

| Enable Animation                      |      |

| Running the Verilog-XL Simulator      |      |

| Review the Animation                  |      |

| Appendix C                            |      |

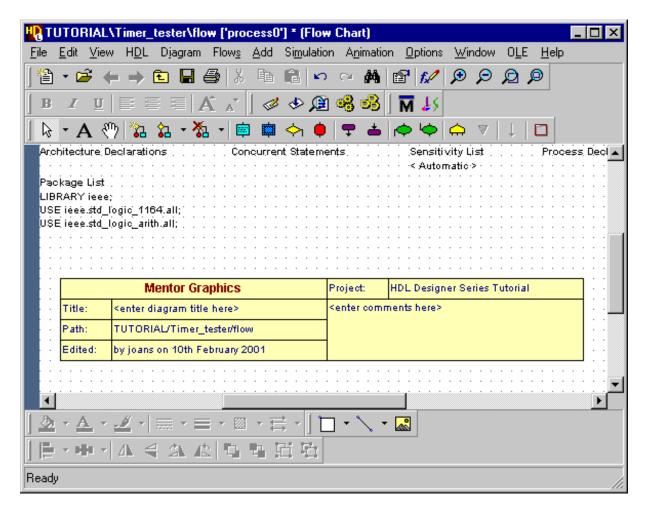

| Creating a VHDL Flow Chart            | C-1  |

| Introduction                          | C-1  |

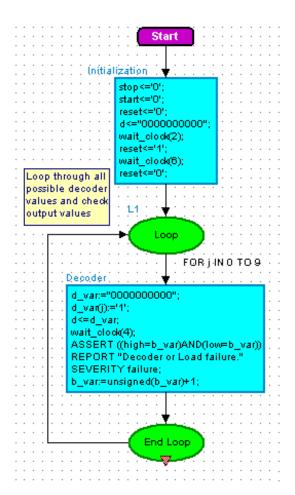

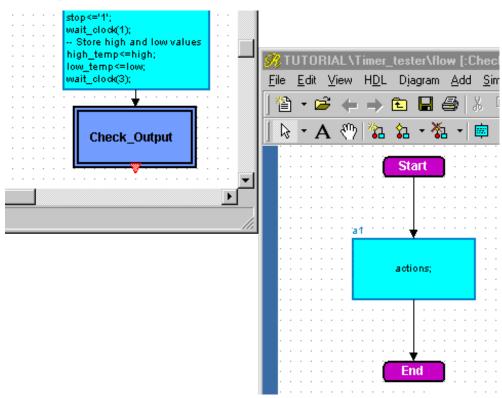

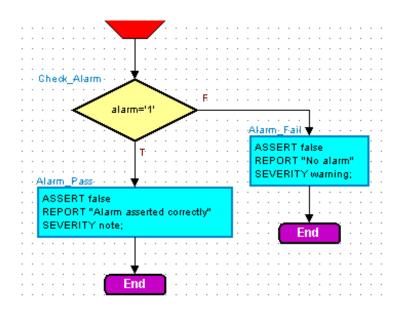

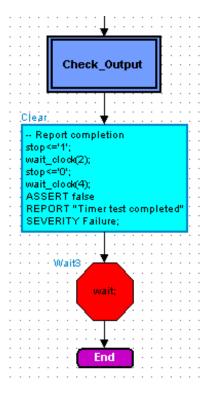

| Create the Tester Flow Chart          |      |

| Set Flow Chart Properties             | C-3  |

| Add a Start Point and Action Box      |      |

|                                       |      |

| Add a Loop and an Associated Comment        | C-7  |

|---------------------------------------------|------|

| Add an Action Box                           | C-11 |

| Add a Hierarchical Action Box               | C-12 |

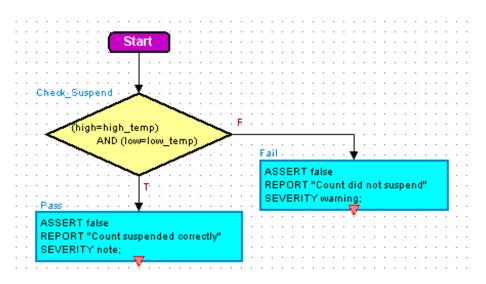

| Add a Decision Box                          | C-13 |

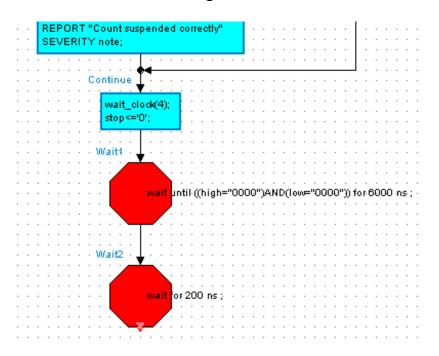

| Add Wait Boxes                              | C-15 |

| Copy the Decision Tree                      | C-17 |

| Completing the Flow Chart                   | C-18 |

| Appendix D<br>Creating a Verilog Flow Chart | D-1  |

| Introduction                                | D-1  |

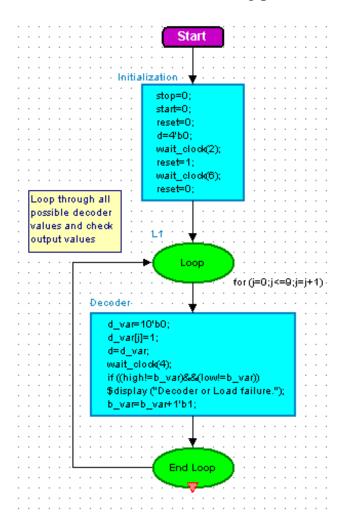

| Create the Tester Flow Chart                | D-2  |

| Set Flow Chart Properties                   | D-3  |

| Add a Start Point and Action Box            | D-6  |

| Add a Loop and an Associated Comment        | D-7  |

| Add an Action Box                           | D-11 |

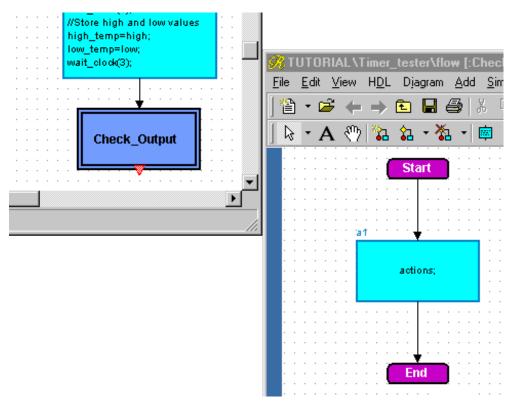

| Add a Hierarchical Action Box               | D-12 |

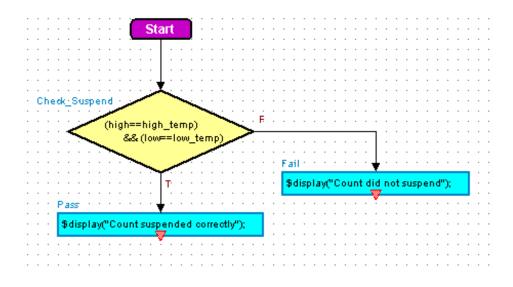

| Add a Decision Box                          | D-13 |

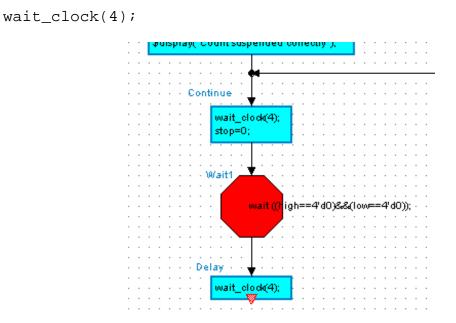

| Add a Wait Box                              |      |

| Copy the Decision Tree                      | D-17 |

| Completing the Flow Chart                   | D-18 |

|                                             |      |

# **About This Manual**

## Introduction

This manual provides a self-paced tutorial with step-by-step procedures for creating a simple timer design and test bench using VHDL or Verilog.

The tutorial covers the basic procedures required to fully define and verify a design using graphical views. The full tutorial can be completed by users of the following HDL Designer Series graphical design tools:

HDL Author - Graphics HDL Author - Pro HDL Designer - Graphics HDL Designer - Pro

The tutorial can also be completed by users of the HDL text design versions of these tools by importing HDL text views instead of creating the graphic editor views.

When new terminology is introduced, the keywords (shown in blue when this document is viewed online) are hyperlinked to a definition in the Glossary. (For example, the keywords test bench, VHDL and Verilog in the first sentence above.)

User and reference information including an online version of the glossary can also be accessed at any time from the **Help Topics** index. The **Help Topics** provide a contents list, keyword index and full text search facility. In addition, many of the dialog boxes are linked to related help topics by Help buttons.

The completed VHDL design can be compiled and simulated if ModelSim is available and the Verilog design can be compiled and simulated using ModelSim or Verilog-XL. Either design can be synthesized if the LeonardoSpectrum tools are available.

A

Although the procedures do not describe the use of other tools, the HDL Designer Series includes support for a range of alternative downstream tool interfaces and it should be possible to use the generated HDL with any of these interfaces. However, you must consider any limitations of your external tool. In particular, some VHDL tools may not support the standard IEEE packages used in the tutorial and you should substitute an appropriate alternative package.

The tutorial assumes that users have some knowledge of the issues for digital hardware design and experience of the VHDL or Verilog language. It is possible to complete the tutorial without this knowledge by carefully copying the language syntax given in the procedures. However, a separate VHDL or Verilog training course is recommended in order to fully appreciate how the power of HDL design can be exploited using graphical design methods.

Procedures for completing the tutorial using VHDL are given in Chapter 1 and procedures for using Verilog in Chapter 2. The alternative procedures for use with the text design tools are described in Appendix A. Procedures for using the Verilog-XL simulator are given in Appendix B.

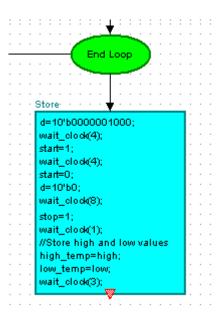

The main tutorial includes a test bench which uses on a flow chart view. The flow chart can be imported from example HDL code or can optionally be created by following the procedures in Appendix C and Appendix D.

When pathnames (or window titles derived from pathnames) are shown in this tutorial, the PC convention ( $\langle \rangle$ ) is used.

The examples shown in the tutorial pages have been laid out for maximum readability in the Acrobat viewer or on the printed page. When you are creating your own design, it is advisable to allow extra space between diagram objects so that you can easily route signals between them.

All user commands in the tutorial procedures are referenced using their menu path (shown in bold text) or toolbar button. However, many commands can also be accessed using keyboard shortcuts. Refer to the shortcut tables in the help pages for full lists of the available shortcuts. These lists can be accessed by choosing **Shortcuts** from the HDL Designer **Help** menu.

## **Copying Text From the Acrobat Viewer**

You can copy text from this document by choosing the (**Text Select**) tool button or  $\bigvee$  shortcut key in the Acrobat viewer and choosing **Copy** from the Acrobat **Edit** menu (or using the shortcut).

The text can be pasted into a text editor (or application dialog box) using the  $\Box + \forall$  shortcut or the **Paste** menu option if one is provided in the destination window. In the graphic editors, you can use the **Paste Special** option to explicitly paste text from the system clipboard.

If you copy HDL text from a tutorial help page, check that punctuation characters are copied correctly. In particular, line feed characters may not be translated on UNIX systems and may need to be re-entered.

## **Example Designs**

Completed examples of the VHDL and Verilog tutorial designs are provided in the HDL Designer Series installation. These can be browsed for reference or can be compiled, simulated and animated directly if you modify their downstream library mapping to use a writable downstream directory.

Refer to the sections "Using the Example VHDL Design" on page 1-89 or "Using the Example Verilog Design" on page 2-90 for more information.

# Chapter 1 VHDL Timer Exercise

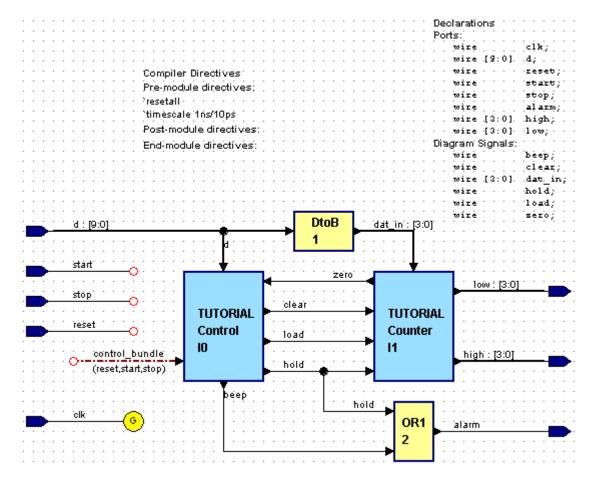

This exercise creates a simple timer using block diagrams and a control block described as a hierarchical state machine. A simple truth table is used to decode four-bit binary codes from the ten-bit input bus. The design is completed using a re-usable component described by a HDL text view.

A test bench is created using a flow chart which can be used as a test harness to simulate the generated VHDL for the timer design. The simulation results can be displayed as animation on the flow chart and state machine to assist in debugging the design. The verified timer design is then synthesized.

The instructions assume that a ModelSim simulator and the LeonardoSpectrum synthesis tools are available. However, the VHDL generated from the diagrams can also be used by other compatible downstream tools that are available on your system.

### **Specification**

The timer outputs time data on two four-bit buses representing low and high values. There is also a logic output signal which triggers an audible alarm. The data input is provided on a ten-bit bus and control is provided by start, stop, reset and clock signals. These signals are summarized in the following table:

#### Inputs

start (logic signal) stop (logic signal) reset (logic signal) clk (logic signal) d (10-bit bus)

#### Outputs

high (4-bit bus) low (4-bit bus) alarm (logic signal)

## **Set Library Mapping**

A library is the logical location of the directories containing your design data. The source design, generated HDL and downstream data can be stored at any writable locations on your available file system but is typically saved below a common root directory.

To set library mapping, choose **New Library** from the **File** menu in the design browser window to display the Add New Library Mapping dialog box.

| 🙀 Add New Library Mapping | ×        |

|---------------------------|----------|

| Library Mappings          |          |

| Library Name:             |          |

| TUTORIAL                  |          |

| Root directory:           |          |

| D:\Designs                | Browse   |

| Open library after add    | Advanced |

| OK Cancel                 | Help     |

Enter a logical library name (for example, *TUTORIAL*) and specify the pathname for the root directory that will contain your library data (for example, *D:\Designs*).

By default, the root directory is set to ..\*hds\_scratch* which is created at *\$HOME/hds\_scratch* on UNIX or *<install\_dir>\examples\hds\_scratch* on Windows.

Library names and pathnames can be entered using upper, lower or mixed case but note that UNIX systems are case sensitive and the case used for pathnames should match the file structure. (On a PC, library names are case sensitive but pathnames are case insensitive.).

Check that the **Open library after add** option is set and use the  $\square K$  button to create and open the new library. Notice that the source design data directory is named  $< root\_directory> \setminus TUTORIAL \setminus src$  and that the generated HDL directory is named  $< root\_directory> \setminus TUTORIAL \setminus hdl$ .

The source design data directory is created (if it does not already exist) when you save a design unit to the *TUTORIAL* library (provided that the parent directory exists and you have write access to create a subdirectory at the specified location). The generated HDL directory is created when you generate HDL for the design. The mapping for the location of compiled data is defined automatically when you set up a downstream tool and the directories created when the design is compiled.

Your library definition is saved in an initialization file which is automatically saved in your user directory with the file name *hds.ini* and is read the next time that the HDL Designer Series tool is invoked.

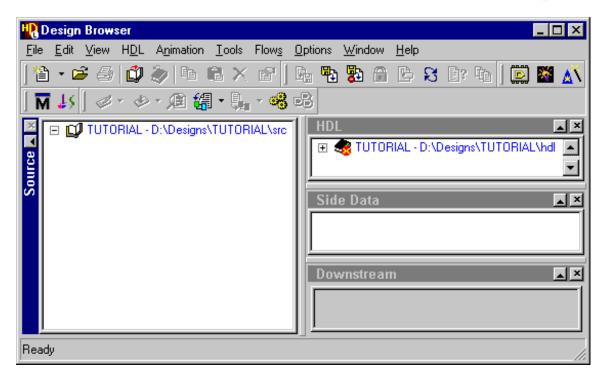

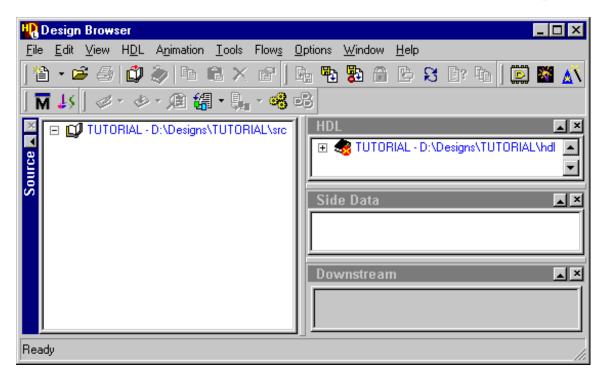

The Source design data directory is displayed in the design browser as an open "book" and the HDL directory as a closed book similar to the following picture:

The Source and HDL pathnames are shown in blue text because the directories do not exist yet but will be updated in the browser when you create them by saving design units and generating HDL for the library. The Side Data and Downstream sub browsers are both empty at this stage unless any other libraries are open.

### Set the Default Language

A set of default preferences are loaded when you invoke a HDL Designer Series tool for the first time. There are separate tabbed dialog boxes for the main settings, VHDL and Verilog options, compile settings, HDL import options, version management settings and master preferences for each type of graphical diagram. The preference dialog boxes can be accessed from the **Options** menu.

Choose **Main** from the **Options** menu to display the Main Settings dialog box, select the **Diagrams** tab and ensure that **VHDL** is set as the default language to be used for new graphic editor views. Use the  $\square K$  button to confirm your choice.

| Main Sett        | lings                                 |        |

|------------------|---------------------------------------|--------|

| General          | Text Diagrams Checks Save             |        |

| -Default Fo      | ont                                   |        |

| Font:            | Arial Normal 10 point                 | Set    |

| L<br>D           | Use scalable fonts                    | ]]     |

| 1                |                                       |        |

| - Title Blocl    | ks                                    |        |

| Template I       | file:                                 |        |

|                  |                                       | _      |

| \$HDS_H          | OME\resources\misc                    | Browse |

| 🔽 Add Ti         | itle Blocks in new diagrams           |        |

| I <b>∙</b> Auu n | die Diocks in new diagrams            |        |

| Default La       | anguage for New Diagrams Graphic Tips |        |

| 2 010001 20      | VHDL     Maximum line length:         | 40     |

|                  | ( VHDL                                |        |

|                  | C Verilog Maximum number of lines:    | 3      |

|                  |                                       | P      |

| Show /           | Anchors for associated objects        |        |

| ■ SHOW P         |                                       |        |

| Units for pri    | inting: Inches                        |        |

|                  |                                       |        |

|                  |                                       |        |

|                  | OK Cancel Apply                       | Help   |

|                  |                                       |        |

All other preferences can be left with their default values for this tutorial.

## **Create a Block Diagram**

Use the *button* in the design browser window and select **Block Diagram**.

A new untitled block diagram is created.

| HDUr | ntitled *  | (Block Diagram)                                |                                                                |                                                          | × |

|------|------------|------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|---|

|      | Edit Vie   |                                                | lation Add                                                     | <u>O</u> ptions <u>W</u> indow O <u>L</u> E <u>H</u> elp |   |

|      | • 🗳        |                                                | <br>∩ ~~                                                       |                                                          |   |

| ] в  | I U        | : ≡≡≡ A`⊾`                                     | - 🔎 🤫                                                          | 3 😼   📴 🎬 <u>۸</u>   🖬 45                                |   |

|      | • A ·      | 🖑 [~~~ 🔀 🖪 🖪 🐼 🥦 🖪                             | <u></u> 。<br>1                                                 | Ļ·≒・S∣► ╼ ╼│○│[                                          | ב |

|      |            |                                                |                                                                |                                                          |   |

|      |            | <company name=""></company>                    | Project:                                                       | <pre><enter here="" name="" project=""></enter></pre>    |   |

|      | Title:     | <enter diagram="" here="" title=""></enter>    | <enter com<="" td=""><td>nments here&gt;</td><td></td></enter> | nments here>                                             |   |

|      | Path:      | <tbd>/<tbd>/<tbd></tbd></tbd></tbd>            | 1                                                              |                                                          |   |

|      | Edited:    | by joans on 08 Feb 2001                        | 1                                                              |                                                          | - |

|      | - <u>)</u> | · A · Z ·   == · = · = · = · = · = · = · = · = | ⇒ v [] `` · · ·                                                | ▼ \ ▼                                                    |   |

|      |            |                                                |                                                                |                                                          |   |

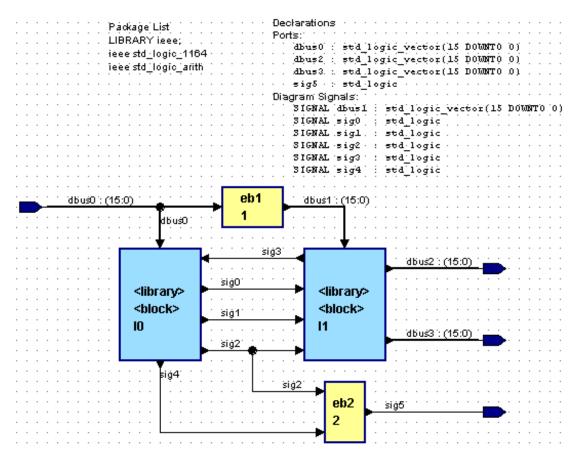

The block diagram is a blank sheet except for a background grid, a package list (with the standard IEEE libraries *std\_logic\_1164* and *std\_logic\_arith* set by default), a copy of the default title block, and empty text fields with labels for Declarations, Ports and Diagram Signals.

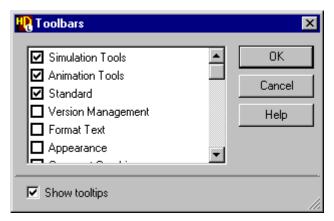

Notice the five toolbars at the top and three toolbars at the bottom of the diagram. The toolbar buttons provide quick access to many of the most frequently used editing and formatting commands.

#### **Edit the Title Block Template**

A title block is automatically added to all new diagrams if the **Add Title Blocks in new diagrams** option is set in your diagram preferences. The default title block is a template with default text for your company name, project name, diagram title and comments. The default title block incorporates internal variables which automatically enter your login name and the current date. Internal variables are also used to enter the logical pathname for the design. This path is initially shown as <TBD>/<TBD> but the internal variables are converted to show the library, design unit and view name when you save the diagram.

Click twice on <company name> in the default title block to display a popup edit box and replace the default text by the name of your company. Click twice on <enter project name here> and enter a name for your project (for example, HDL Designer Tutorial).

Display the **Diagrams** tab of the Main Settings dialog box (as described in "Set the Default Language" on page 1-4) and change the **Template file** pathname to a write-able location such as your working directory or home directory.

Select the title block by clicking with the mouse so that the selection handles are displayed and choose **Save Title Block** from the **File** menu.

| Mentor Graphics |                                             | Project:                                              | HDL Designer Tutorial |

|-----------------|---------------------------------------------|-------------------------------------------------------|-----------------------|

| Title:          | <enter diagram="" here="" title=""></enter> | <enter comm<="" td=""><td>nents here&gt;</td></enter> | nents here>           |

| Path:           | <tbd>/<tbd>/<tbd></tbd></tbd></tbd>         |                                                       |                       |

| Edited:         | by joans on 08 Feb 2001                     |                                                       |                       |

A dialog box is displayed with a warning that saving the title block cannot be undone. Click the Yes button to proceed.

The title block is saved at the new location specified in your preferences and will be used as the default template in new diagrams.

Refer to the online help topics for information about how you can add and modify title blocks.

## **Add Blocks**

Move the title block to the bottom of your block diagram by dragging it with the Left mouse button.

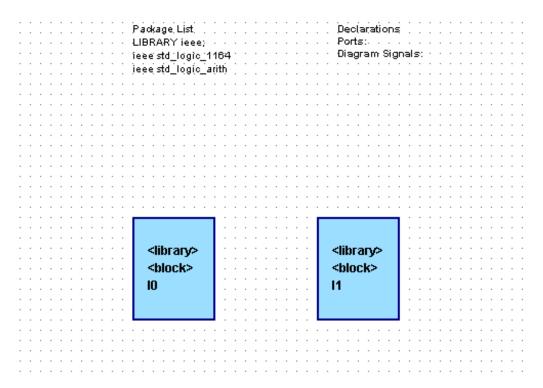

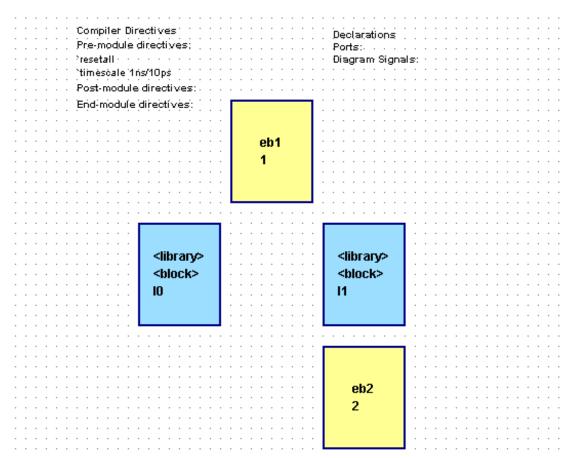

Use the 🔳 button to add two blocks on the diagram as shown in the picture below. The blocks are added with the default library *<library>*, the default name *<block>* and unique instance names (*I0* and *I1*)

The command normally auto-repeats until you select another command or terminate the repeating command by using the right mouse button or  $\boxed{Esc}$  key. However, you can change the behavior of the toolbar buttons by setting the **Activate once only** preference in the **General** tab of the Main Settings dialog box as described on page 1-6.

You can also use the  $\square$  key with any toolbar button to toggle the repeat mode. For example, when **Remain active** is set,  $\square + \blacksquare$  adds a single block on a block diagram.

## **Add Embedded Blocks**

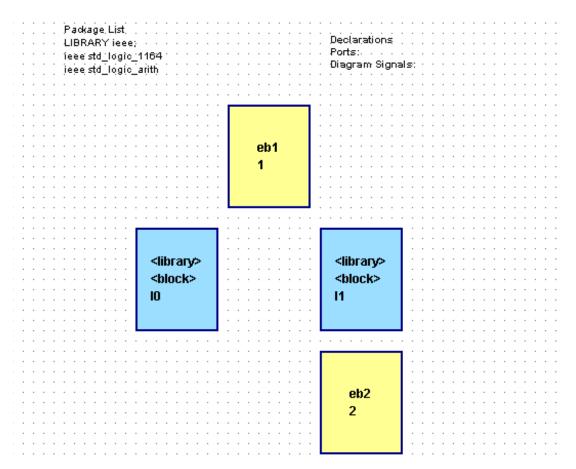

Use the  $\boxed{\Box}$  button to add two embedded blocks on your block diagram as shown in the picture below. The embedded blocks are added with unique default names (*eb1* and *eb2*) and numbers (*1* and *2*)

The view describing a block must be saved as a uniquely named design unit in a library directory. However, the view describing an embedded block is saved as part of the parent block diagram and does not impose hierarchy when HDL is generated for your design. The name of an embedded block must be unique on the diagram and is used as a label in the generated HDL.

The blocks (*I0* and *I1*) will be used to define a child state machine and block diagram view. The embedded blocks (*eb1* and *eb2*) will be defined by concurrent assignment statements on the top level block diagram.

## **Add Ports and Signals**

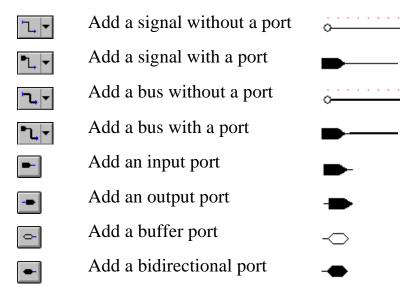

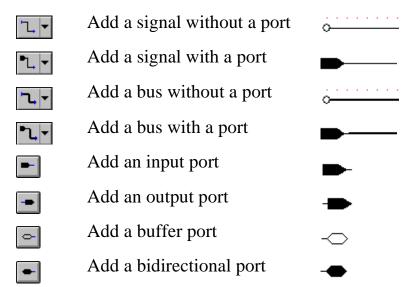

You can use the following buttons to add signals, buses and ports on a block diagram:

Signals or buses can be added between any existing connectable items on the diagram or left unconnected by double-clicking to terminate the net with a dangling net connector. However, you can use the pulldown on the buttons to change the default setting and terminate with a default port at unconnected end points. Notice that the toolbar button changes to show the current setting.

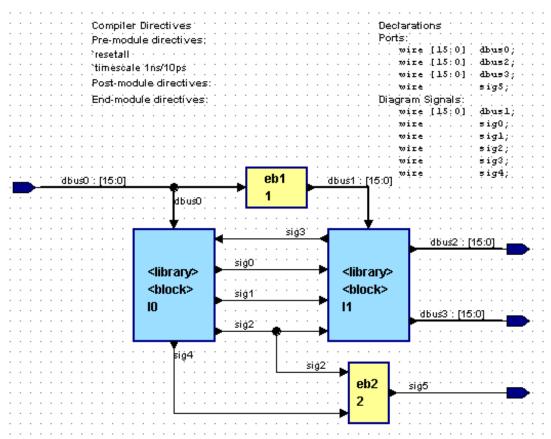

Choose **Signal with Port** and use the button to connect three signals originating from the block on the left (instance *I0* in the picture) to the block on the right (instance *I1*) and one signal returning from *I1* to *I0*. The signals are added with unique names (*sig0*, *sig1*, *sig2* and *sig3*) and the default type *std\_logic*. Notice how declarations are automatically added to the list of Diagram Signals.

Allow two or more grid lines between each port or signal. You can resize objects by selecting a block or embedded block and dragging one of its resize handles. If necessary, you can drag text elements such as the signal name using the Left mouse button.

Add a signal from I0 to the embedded block eb2 and another signal from a point on sig2 terminating on the embedded block.

Add a signal from the embedded block terminating in space on the right side of your diagram. Notice that an output port is automatically added when you doubleclick at the end of the last signal and its declaration is added to the list of ports.

Choose **Bus with Port** and use the **t** button to add a bus from a source on the left side of your diagram with its destination on the upper embedded block *eb1*. A default input port is automatically created at the beginning of the bus. Add another bus starting from this bus and terminating on instance *10*. Notice how both bus segments have the same default name *dbus0* but the default bounds (*15:0*) is shown (in abbreviated format) only on the first bus segment. The full declaration showing the default bus type and bounds *std\_logic\_vector*(*15 DOWNTO 0*) is added to the list of ports. See the online help topic Changing the Display of Signal Properties for information about the format for displaying signals and buses.

Add a bus (*dbus1*) from *eb1* to *I1*. Then add two buses (*dbus2* and *dbus3*) from *I1* terminated with default output ports by double-clicking on the right side of the diagram. Your diagram should now look similar to the picture below:

## Add a Bundle and Global Connector

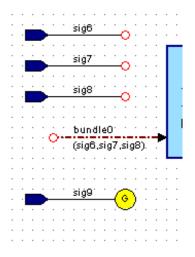

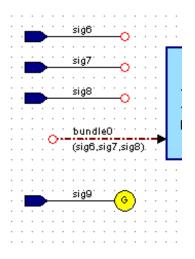

Use the L button to add three signals on the left side of your diagram. Notice that a default input port is created at the source of each signal but a dangling net connector is drawn when you double-click at the end of each signal.

Select the three signals (by dragging a select rectangle with the Left mouse button held down) and use the button to connect a bundle containing these signals to block instance *IO* as shown in the picture below. Notice that the bundle has the default name *bundleO* and the three selected signals are automatically included in the bundle with their names listed under the bundle name.

Use the o button to add a global connector on your diagram below the bundle and use the to add a signal between the global connector and a default input port. (This will be a clock signal which is implicitly connected to every block on the diagram.)

If you make a mistake when editing a diagram, you can use the solution to undo your last edit and the solution to redo an undo operation. You can also use commands from the **Align** cascade of the **Edit** menu to re-align and distribute objects on the diagram.

## Save the Block Diagram

Notice the asterisk (\*) character in the header of the block diagram editor window. This indicates that the diagram has been edited since it was last saved.

Use the 🖬 button to save the block diagram. The Save As dialog box is displayed which allows you to choose from the currently mapped libraries and specify the design unit and design unit view names. Choose the *TUTORIAL* library and enter design unit *Timer*. The dialog box should look similar to the example below:

| 限 Save As Design Uni                                                                                                           | View         |           | ×      |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|--------|

| Library:                                                                                                                       | Design Unit: | View:     |        |

| TUTORIAL SCRATCH_LIB Sequencer_vhd Sequencer_vlg TIMER_Vhdl TIMER_Vlog TUTORIAL UART UART UART_V exemplar Ipm Ipm_v arithmetic | Timer        | struct.bd |        |

| 🔽 Show Standard Librarie:                                                                                                      | \$           |           |        |

| Mappings                                                                                                                       |              | OK Cance  | I Help |

The view name can be entered using any valid HDL identifier but normally defaults as follows:

| struct.bd  | block diagram               |

|------------|-----------------------------|

| struct.ibd | interface-based design view |

| fsm.sm     | state diagram               |

| flow.fc    | flow chart                  |

| tbl.tt     | truth table                 |

| symbol.sb  | symbol                      |

If you omit the two-character extension it is automatically added to identify the type of diagram you are saving. The default leaf names can be changed by setting preferences. However, you should not change the extension (*.bd*, *.ibd*, *.sm*, *.fc*, *.tt* or *.sb*) or the design data file will not be recognized and cannot be reopened.

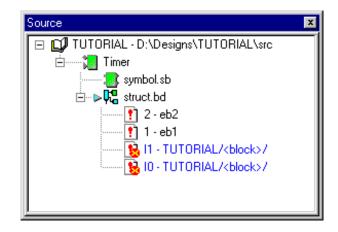

When you click the  $\square K$  button, your diagram is saved and the window title bar is updated to show the diagram pathname *TUTORIAL*\*Timer*\*struct*. This path is also added in the title block replacing the <TBD> used when the diagram was created. Notice that the asterisk (\*) character has been cleared in the block diagram header and the library name used on the blocks in your diagram has been updated to *TUTORIAL*.

1

If the design browser window is obscured, you can pop it to the front by selecting the **Design Browser** window from the **Windows** menu list in the block diagram window.

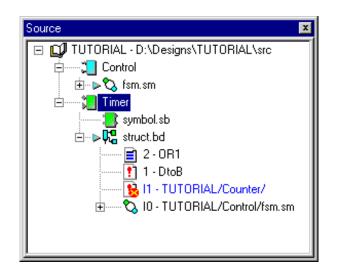

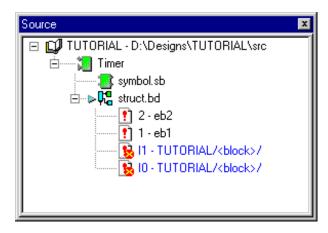

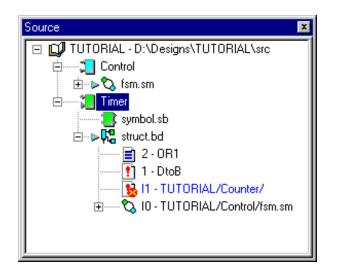

Click on the  $\boxdot$  icon for the *TUTORIAL* library in the source browser and notice that the view is expanded to display the *Timer* design unit. Click on the  $\boxdot$  icon for the *Timer* design unit to reveal that it contains a symbol and block diagram view. Click on the  $\boxdot$  icon for the *struct.bd* view to display the hierarchy of views instantiated as blocks and embedded blocks on the block diagram. The embedded blocks (*eb1* and *eb2*) are shown using the P icon to indicate that no views have been defined. The blocks (*I0* and *I1*) are also shown as undefined but with blue text and an P overlay indicating that no design units exist for their child views.

i

You can change the design browser layout and undock the source browser (shown above), HDL browser, side data browser or downstream browser from the main window. Blue text and an <sup>©</sup> overlay in the source browser indicates that a view is not write-able. (In this case, because design units have not been created for the blocks. This convention is also used to show when you have read-only access.)

#### **Edit Block and Signal Names**

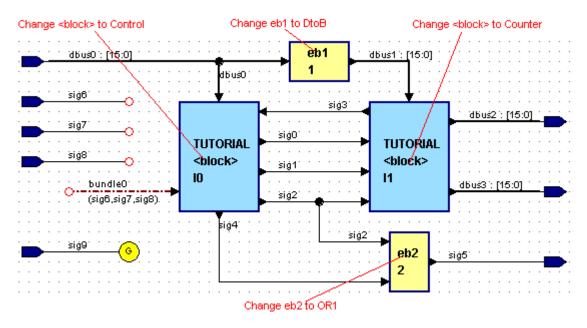

You now have a completed top-level block diagram for the *Timer* design. However, the blocks and signals have default names.

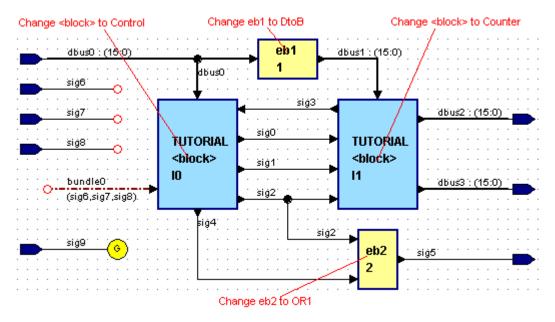

Click on the text <block> in the lower block on the left (instance *I0* in the picture) and notice the small handles which indicate that the text object is selected. Click again and notice that the text is now highlighted and can be directly overwritten. Type the new name *Control* and click outside the text to complete the edit. Repeat this procedure to change the name of block instance *I1* to *Counter*, embedded block *eb1* to *DtoB* and embedded block *eb2* to *OR1*.

The text can be overwritten when it is highlighted. If you click again, the cursor changes to an I-beam which allows you to move the cursor in the text and edit individual characters.

While a text element is selected, an anchor that attaches the text to its associated object is visible and you can move the text independently to improve diagram clarity.

This text editing technique can also be used to edit the signal and bus names.

Alternatively, you can use a dialog box which allows you to edit the properties for a selected object.

Double-click on the existing declarations, use the *button* or choose **Object Properties** from the **Edit** menu to display the Block Diagram Object Properties dialog box and choose the **Declarations** tab.

| 🕄 Object Prope                                                                                                                                                                                                                                | rties                            |                    |          |         |         |              |            | ×    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|----------|---------|---------|--------------|------------|------|

| Blocks Embe                                                                                                                                                                                                                                   | edded Blocks                     | Components         | Generics | Signals | Bundles | Declarations | Frames     | Text |

| dbus0 : std_logi<br>dbus2 : std_logi<br>dbus3 : std_logi<br>sig6 : std_logic<br>sig7 : std_logic<br>sig8 : std_logic<br>sig9 : std_logic<br>sig5 : std_logic<br>dbus1 : std_logic<br>sig0 : std_logic<br>sig1 : std_logic<br>sig2 : std_logic | c_vector(15 DO<br>c_vector(15 DO | WNTO 0)<br>WNTO 0) |          |         |         |              |            |      |

| Declaration<br>Name:                                                                                                                                                                                                                          |                                  |                    |          |         |         |              |            |      |

| iname:                                                                                                                                                                                                                                        | dbus0                            |                    |          |         |         |              | Global Net |      |

| Туре:                                                                                                                                                                                                                                         | std_logic_ve                     | ector              |          |         |         | <b>•</b>     | More >>    |      |

| Constraint:                                                                                                                                                                                                                                   | Index                            | 🔿 Range            | C None   | e       |         |              |            |      |

| Bounds:                                                                                                                                                                                                                                       | 15                               |                    |          | D       | OWNTO   | • 0          |            |      |

| User Declara                                                                                                                                                                                                                                  | tions 🔽 /                        | Align in Columns   |          |         |         |              |            |      |

|                                                                                                                                                                                                                                               |                                  | OK                 | C.       | ancel   | A       | .pply        | Help       |      |

Notice that the port declarations are listed at the top of the dialog box and the other internal diagram signals at the bottom. Input ports are listed before the output ports, otherwise the declarations are listed in alphanumeric order.

You can choose one or more existing declarations in the dialog box and enter new values for any of the declaration fields. For example, choose *dbus1*, *dbus2* and *dbus3*, then enter a new *index* constraint with bounds *3 DOWNTO 0* to update all three buses while all other fields remain AS IS.

The changes are applied to the diagram when you click the OK or Apply button. Notice that all occurrences on the diagram are updated including the declarations list, signals, buses and bundle contents and that the lists of port and signal declarations are sorted alphanumerically when the changes are applied to the diagram.

Use the dialog box to update the port and signal declarations as shown in the following tables.

Ports:

| Old Name | New Name | Туре                        | Constraint | Bounds     |

|----------|----------|-----------------------------|------------|------------|

| dbus0    | d        | std_logic_vector            | index      | 9 downto 0 |

| dbus2    | low      | std_logic_vector            | index      | 3 downto 0 |

| dbus3    | high     | <pre>std_logic_vector</pre> | index      | 3 downto 0 |

| sig6     | start    | std_logic                   | none       | none       |

| sig7     | stop     | std_logic                   | none       | none       |

| sig8     | reset    | std_logic                   | none       | none       |

| sig9     | clk      | std_logic                   | none       | none       |

| sig5     | alarm    | std_logic                   | none       | none       |

**Diagram Signals:**

| Old Name | New Name | Туре             | Constraint | Bounds     |

|----------|----------|------------------|------------|------------|

| dbus1    | dat_in   | std_logic_vector | index      | 3 downto 0 |

| sig0     | clear    | std_logic        | none       | none       |

| sig1     | load     | std_logic        | none       | none       |

| sig2     | hold     | std_logic        | none       | none       |

| sig3     | zero     | std_logic        | none       | none       |

| sig4     | beep     | std_logic        | none       | none       |

All occurrences of each signal name (including the bundle contents) are automatically updated when you use the **Declarations** tab. However, if you use, direct text editing (or the **Signals** tab) to change signal names, it may be necessary to check that all occurrences have been updated. Select the bundle name and use direct text editing or the **Bundles** tab of the Object Properties dialog box to change the default bundle name to *control\_bundle*.

You can change the selection mode to select text or object shapes only by using the v pulldown menu on the v button.

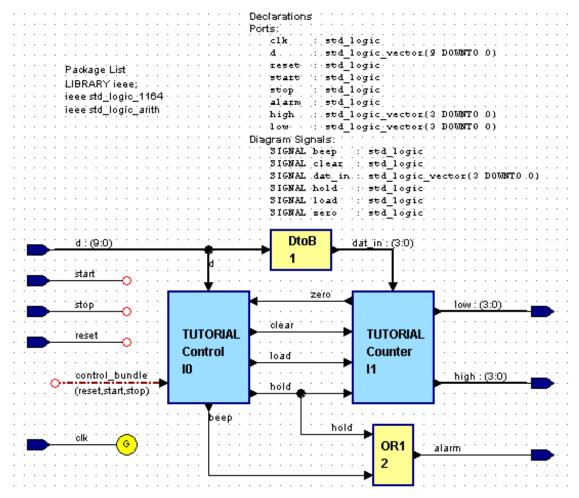

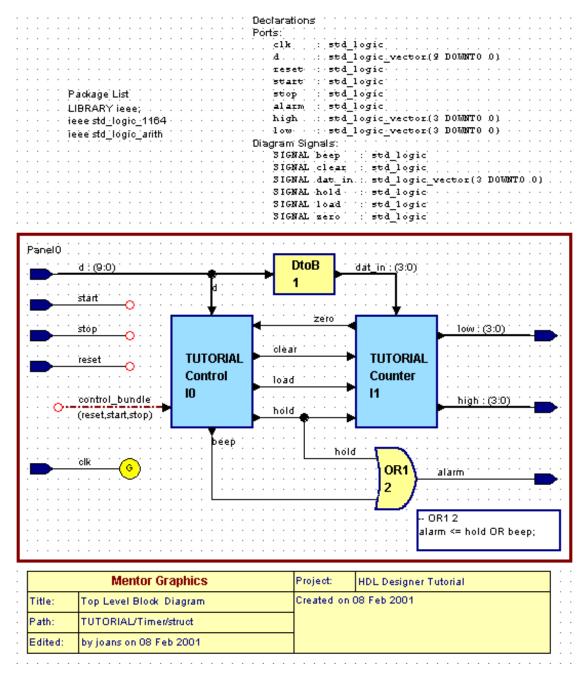

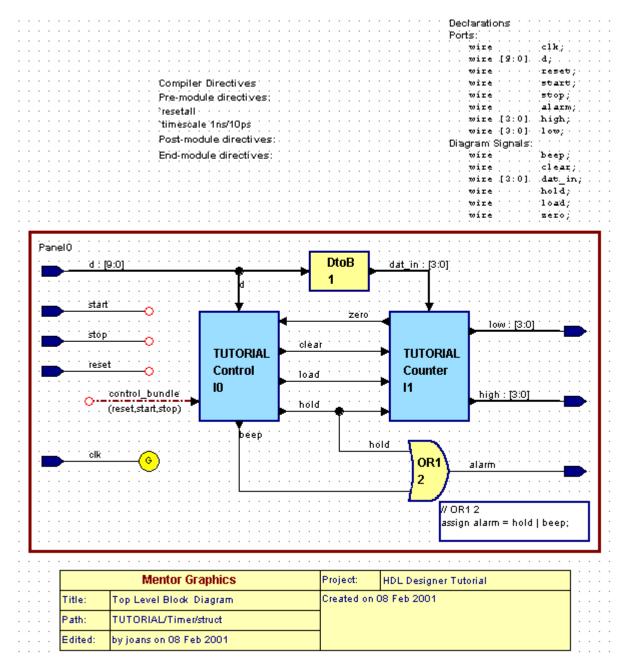

Your block diagram should now look similar to the following picture:

i The fields bound

The More >>> button on the dialog box allows you to disclose additional fields which allow you to modify other signal properties including 2D bounds, initial value, kind, VHDL attributes and synthesis constraints. The User Declarations... button allows you to add additional user-entered architecture declarations to the structural VHDL. Refer to the "Editing VHDL Signal Declarations" help topic for more information about these features which are not used in this tutorial.

### Add an Embedded HDL Text View

Select the *OR1* embedded block and display the popup menu by clicking the route mouse button. Choose **New View** from the **Open** cascade in the popup menu to display the Create Embedded View dialog box. Choose Text from the pulldown list of views in the dialog box.

| 🛺 Create Embedded View         |                                     | ×      |

|--------------------------------|-------------------------------------|--------|

| Create a new view for:         | Embedded Block: OR1 No: 2 (No View) | OK     |

| Select type of view to create: | Text                                | Cancel |

|                                | Text<br>Flow Chart                  |        |

|                                | State Diagram<br>Truth Table        |        |

An embedded HDL text view containing default text is displayed on the block diagram adjacent to the embedded block. Select the text, re-display the Object Properties dialog box if necessary (using the 🖻 button) and choose the **Text** tab.

| 🖁 Object Properties          |            |           |            |         |              |        | ×    |

|------------------------------|------------|-----------|------------|---------|--------------|--------|------|

| Blocks Embedded Blocks       | Components | Gienerics | Signals    | Bundles | Declarations | Frames | Text |

| Number of selected Comments: | 1          |           |            |         |              |        |      |

| Bounding Box                 |            |           |            |         |              |        |      |

| 🔽 Resize to fit text         |            |           |            |         |              |        |      |

| Text Position Top            |            |           |            |         |              |        | ◄    |

| Modify                       |            |           |            |         |              |        |      |

| Comment Text:                |            |           |            |         |              |        |      |

| OR1 2                        |            |           |            |         |              |        |      |

| alarm <= hold OR beep;       | _          |           |            |         |              |        |      |

|                              |            | Enter new | HDL text h | ere     |              |        |      |

|                              |            |           |            |         |              |        |      |

| 1                            |            |           |            |         |              |        |      |

|                              | OK         |           | Cancel     |         | Apply        | Help   | ,    |

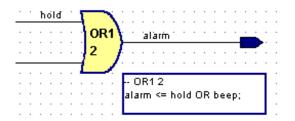

Check the **Resize to fit text** option and enter the following VHDL statement under the default -- OR1 2 comment in the dialog box: alarm <= hold OR beep;

The modified HDL text is checked for syntax errors and applied to the diagram when you click the  $\Box K$  or Apply button on the dialog box.

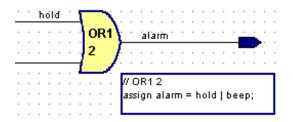

The functional blocks on the diagram are shown by default as simple rectangular shapes. However, it is sometimes useful to use logic notation when a block has a specific logical function. For example, in this block diagram, the *OR1* embedded block represents a logical OR function.

Select the embedded block and choose the pulldown  $\neg$  on the r button to display a palette of alternative shapes. Select  $\bigcirc$  from the palette to apply a logical OR shape to the embedded block on the diagram.

You can also hide the port arrow heads by clearing the **Show Ports when connected** check box in the **Embedded Blocks** tab of the Object Properties dialog box.

The OR1 embedded block should now look similar to the following picture:

It is also possible to indicate an active low (Not) or edge triggered clock signal. This feature can be used with the alternative shapes to represent extra functions such as an invertor, NAND, NOR or flip-flop. If required, you can rotate any block or component by 90 degree steps.

Refer to the "Logic Shape Notation" help topic for more information about these features.

The logical OR function could also be implemented by a ModuleWare component similar to that used in "Add ModuleWare Components" on page 1-51.

## Add a Panel and Edit the Title Block

Use the D button to add a panel and hold down the Left mouse button to drag the panel and enclose the graphical objects on your diagram. The panel is added with the default name Panel0 and can be useful to outline areas of a diagram. For example, you can divide a large diagram into separate printable page-sized areas or use a panel to outline a view used for simulation or animation.

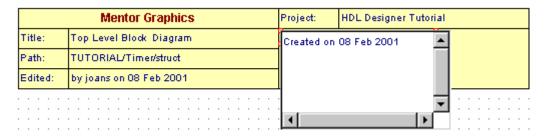

Complete the block diagram by editing the title and comments in the title block on the diagram. For example, enter the title Top Level Timer Block Diagram and a comment of the form: Created by <your name> on <date>.

The title block comprises a number of grouped comment text objects. Each comment text object can be edited directly by clicking twice on the text to display a text entry box.

|         | Mentor Graphics         | Project:   | HDL Designer Tutorial |

|---------|-------------------------|------------|-----------------------|

| Title:  | Top Level Block Diagram | Created on | 08 Feb 2001 🔺         |

| Path:   | TUTORIAL/Timer/struct   |            |                       |

| Edited: | by joans on 08 Feb 2001 |            |                       |

|         |                         |            | <b>.</b>              |

|         |                         |            |                       |

|         |                         |            |                       |

You can enter free-format text including line breaks and spaces which will be preserved on the diagram.

Click the Left mouse button outside the entry box to complete the text entry.

You can also edit an existing comment text object by double-clicking to display the **Text** tab in the Object Properties dialog box. When comments are edited in the dialog box, it is possible to enter any special characters (for example accents or Kanji characters) which are supported on your system.

Use the 📕 button to save the block diagram.

You have previously saved the diagram so you are not prompted for library and design unit names. However, you have changed the names of signals connected to input and output ports and the block diagram will be inconsistent with the symbol that was automatically created by the previous save. You are prompted whether to update the symbol. Click the Yes button to confirm.

The completed block diagram should look similar to the following picture:

The procedures in the following sections create a graphical state machine to describe the *Control* block. If you are using one of the HDL text design tools, refer to Appendix A for an alternative HDL text view of the *Control* block.

#### **Set State Machine Preferences**

You will create a state machine view in the next procedure. You can set master preferences which modify the way new diagrams are drawn. As an example, for this tutorial it is suggested that you reduce the default size used for a state.

Choose **State Machine** from the **Master Preferences** cascade of the **Options** menu in the design browser to display the State Machine Master Preferences dialog box and select the **Miscellaneous** tab:

| 😯 State Machine Master Preferences           |    |        | ×    |

|----------------------------------------------|----|--------|------|

| Appearance Default Values Miscellaneous Grid |    |        |      |

| State radius: 3000                           |    |        |      |

| Hierarchical state radius: 3000              |    |        |      |

| Transition priority radius: 80               |    |        |      |

| Transition style: Spline                     |    |        |      |

| Shrink state bubble to fit name              |    |        |      |

| Check syntax on entry                        |    |        |      |

| Default save name:fsm                        |    |        |      |

| Register state actions on next state         |    |        |      |

| Signal status default options                |    |        |      |

| Output signal default status: COMBINATORIAL  |    |        |      |

| Internal signal default status: REGISTERED   |    |        |      |

| Registered signal suffix/prefix:             |    |        |      |

| Clocked signal suffix/prefix:                |    |        |      |

| Use as: C Prefix C Suffix                    |    |        |      |

|                                              |    |        |      |

|                                              |    |        |      |

|                                              | OK | Cancel | Help |

You can set the minimum radius for states, hierarchical states and the transition priority object. The states will auto-size if the state name is larger than can be enclosed by the minimum radius. However, the minimum state size is overridden if you check **Shrink state bubble to fit name** which allows the states to shrink below this size if the state names are short.

Transitions on a state diagram are normally drawn with curved splines instead of the orthogonal polylines used for signals on a block diagram. However, the transition style can be changed to straight polylines.

Syntax checking on entry can be enabled or disabled (for example, if you want to enter non-HDL identifiers or comments while drafting a diagram). You can choose to register state actions on the next state instead of the current state.

You can also specify the default leaf save name for state diagrams, the default status for output and internal signals and the prefixes or suffixes used for the internal names of registered or clocked signals.

Change the state radius and hierarchical state radius values to 3000. This radius should be sufficient to enclose the state names used in this tutorial.

Examine the other preferences available in each tab of the State Machine Master Preferences dialog box.

Use the OK button to set the changed preference. You are prompted to confirm the change which will be used in the master preference next time you open a state diagram. Click the Yes button to confirm.

Notice that you can also display dialog boxes which allow you to set the master preferences for the block diagram, symbol, flow chart and truth table editors. You can use the Help buttons in each dialog box for more information about these preferences. However, you are advised not to change any of the other preferences before you have completed this tutorial.

#### **Create a Child State Diagram**

Move the cursor over the body of the *Control* block on the *Timer* block diagram, then press and release the Right mouse button to select the block and display the popup menu. Choose the **Open** cascade menu option **New View**. The Open Down Create New View dialog box is displayed:

| 限 Open Down Create Ne          | ×                                          |          |

|--------------------------------|--------------------------------------------|----------|

| Create a new view for:         | TUTORIAL/Control                           | ОК       |

| New view name:                 | fsm. sm                                    | Cancel   |

| Select type of view to create: | State Diagram 💌                            | Mappings |

|                                | Block Diagram<br>Flow Chart                |          |

|                                | State Diagram<br>Truth Table 🛛 📐           |          |

|                                | VHDL Architecture/Entity<br>Verilog Module |          |

Use the pulldown list to select the type of view you want to create. The view name defaults to *struct.bd* for a block diagram, *struct.ibd* for an Interface-Based Design (IBD) view, *flow.fc* for a flow chart, *fsm.sm* for a state machine, *tbl.tt* for a truth table or *untitled* for a VHDL architecture or Verilog module view. Alternatively, you can enter any other name of your choice or use the Mappings... button to modify the mapping for the current library.

You need not enter the two character extension (.*bd*, .*fc*, .*sm* or .*tt*) for graphical views as the correct extension is automatically added. However, if you do enter any other extension you are warned that the file will not be recognized.

Select **State Diagram** from the pulldown list of views you can create and use the default view name *fsm.sm*.

Solid handles are displayed when the body of a block (or other re-sizable object) is selected. You can display the Open Down Create New View dialog box directly by double-clicking on the body of a block which has no views defined.

A

A new state diagram (*TUTORIAL*\*Control*\*fsm* ['machine0']) is created as a child view of the *Control* block:

| TUTORIAL\Control\fsm ['machine0'] * (State Diagram)                                    |

|----------------------------------------------------------------------------------------|

| File Edit View HDL Djagram Flows Add Simulation Animation Options Window OLE Help      |

|                                                                                        |

|                                                                                        |

|                                                                                        |

| <u> </u>                                                                               |

| Global Actions Concurrent Statements Architecture Declarations Signals Stat            |

| Package List                                                                           |

| LIBRARY ieee;<br>USE ieee.std_logic_1164.all;                                          |

| USE ieee.std_logic_arith.all;                                                          |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

|                                                                                        |

| Mentor Graphics Project: HDL Designer Tutorial                                         |

| Title: <enter diagram="" here="" title=""> <enter comments="" here=""></enter></enter> |

| Path: TUTORIAL/Control/fsm                                                             |

| Edited: by joans on 08 Feb 2001                                                        |

|                                                                                        |

|                                                                                        |

| 「「「「「「」」」の「「「」」「「」」「「」」「「」」「」」                                                         |

| Ready                                                                                  |

A default state machine name (*machine0*) is appended to the design unit and view names but can be changed by choosing **Rename Concurrent State Machine** from the **Diagram** menu.

The state diagram is a blank sheet except for the default VHDL package list and labels for global actions, concurrent statements, architecture declarations, signals status, process declarations and state register statements. The state diagram also includes the default title block which you saved as a template in an earlier topic.

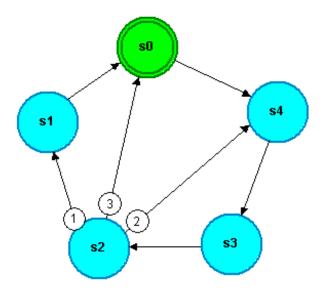

## **Add States and Transitions**

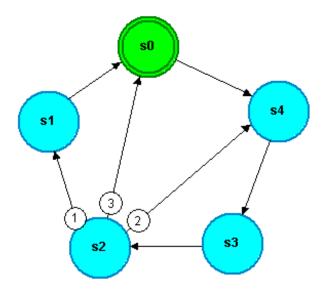

Use the  $\bigcirc$  button to add five states on your state diagram. The states are added with default names s0, s1, s2, s3 and s4. Notice that the first state you add is assumed to be the start state and is drawn in green with a double outline. The other states are drawn in cyan with a single outline.

Use the states as shown in the picture below. Notice that when you add more than one transition leaving a state, the transition priority is indicated by a number associated with the transition arc.

The priorities are initially assigned in the order that you add the transitions but will be re-assigned in a later topic if necessary.

If you add a transition in the wrong direction, you can easily change its direction by choosing **Reverse Direction** from the popup or **Diagram** menu. Note that a popup description (known as a graphic tip) is displayed when the cursor is stationary over an object. In particular, when the cursor is over a a transition, the source state and the destination state are named even if the states are outside the current window.

# Save the State Diagram

Use the **I** button to save the state diagram. The state diagram was created as a child view from its parent block diagram and is saved using the library, design unit and view names specified when it was created. The source browser view is updated to display the *Control* design unit.

You can pop the design browser window to the front by selecting it from the **Windows** menu list in an editor window.

The *Control* design unit is shown as a block in the browser because its interface is defined by the connections on its parent block diagram. The *Timer* design unit is shown as a component because it has no parent block diagram and its interface is defined by a symbol. Click on the  $\pm$  icon for the *Control* design unit to expand the design unit revealing that it contains a state diagram view.

Notice also that the icon used for instance *I0* in the hierarchy for the *struct.bd* view has changed to  $\Im$  indicating that it is now described by a state diagram. (If the hierarchy is not already displayed, click on the  $\mathbb{H}$  icon for the *struct.bd* view.)

The *OR1* embedded block is shown as a text view but the *DtoB* embedded block and the *Counter* block are still undefined.

### **Edit the States**

Select the start state (*s0* in the picture on page 1-26) and use the 🖾 button to display the **States** tab of the State Machine Object Properties dialog box. (Alternatively, you can display the dialog box by choosing **Object Properties** from the **Edit** menu or double-clicking on a state.)

| 眼 Object Prop                           | erties                   |            |       | ×         |

|-----------------------------------------|--------------------------|------------|-------|-----------|

| States Tra                              | nsitions Junctions       | Links Text |       |           |

| Number of sele                          |                          | · · ·      |       |           |

| Name:<br>State Type:                    | flush<br>Start State     |            |       |           |

|                                         |                          |            |       |           |

| - Outgoing tran                         | nsitions for this state— |            |       |           |

| Style:                                  | IF C CASE                |            |       | Settings  |

| 🔽 Implicit loc                          | opback                   |            |       |           |

| - Actions                               |                          |            |       |           |

| 🔽 Modify                                |                          |            |       | 🔽 Visible |

| hold<='1';<br>clear<='1';<br>beep<='0'; |                          |            |       | A         |

|                                         |                          |            |       |           |

| -                                       |                          |            |       | ×         |

| [                                       | OK                       | Cancel     | Apply | Help      |

The **States** tab allows you to enter a name and actions text for one or more selected states on a state diagram. You can also change the visibility of state actions and (when a single state is selected) change the state to a start state or a hierarchical state.

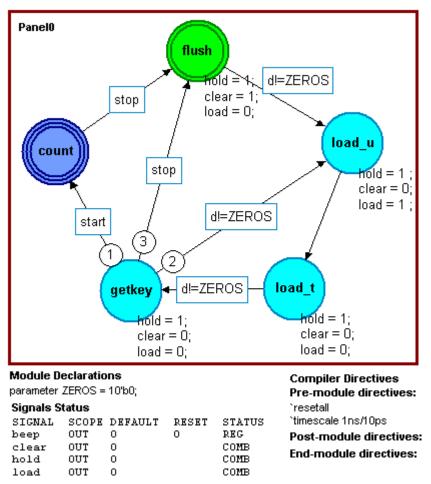

Use the dialog box to enter the following state names and actions replacing the default state names s0 to s4 in the picture on page 1-26:

| Old Name | New Name | Style | Actions                                 |

|----------|----------|-------|-----------------------------------------|

| s0       | flush    | IF    | hold<='1';<br>clear<='1';<br>beep<='0'; |

| s1       | count    | IF    | (no actions)                            |

| s2       | getkey   | IF    | hold<='1';                              |

| s3       | load_t   | IF    | hold<='1';                              |

| s4       | load_u   | IF    | hold<='1';<br>load<='1';                |

Notice that the VHDL Expression Builder dialog box is automatically displayed when you start to enter the actions. The dialog box can be used to choose from lists of the available port or local signal names, operators and example values. For example, choose the *hold* signal,  $\leq$  button, value '1' and  $\leq$  button to enter the action *hold* <= '1';.

The syntax for state actions is automatically checked and any errors reported on entry. VHDL statements must be terminated by a semicolon (;) character. Line breaks and spaces can be used for clarity and will be preserved on the diagram.

If the name is larger than the state, it auto-resizes to fit the new name. You can also resize a state by selecting the state and dragging one of its resize handles but you cannot make it smaller than the enclosed name.

You can also edit the state name or actions by direct text editing on the diagram or copy a state and paste its state actions into another state by choosing the **Paste State Actions** option from the **Paste Special** cascade in the popup menu.

## **Edit the Transitions**

Add conditions to the state diagram transitions as shown in the following table:

| Origin | Destination | Priority | Condition | Actions |

|--------|-------------|----------|-----------|---------|

| count  | flush       | 1        | stop='1'  | none    |

| getkey | flush       | 3        | stop='1'  | none    |

| getkey | count       | 1        | start='1' | none    |

| getkey | load_u      | 2        | d/=ZEROS  | none    |

| flush  | load_u      | 1        | d/=ZEROS  | none    |

| load_u | load_t      | 1        | (none)    | none    |

| load_t | getkey      | 1        | d/=ZEROS  | none    |

Hold down the Left mouse button and select the two transitions entering the state *flush* by dragging the cursor across them (or by using Shift+Left mouse button). Use the 🗃 button to display the **Transitions** tab of the State Machine Object Properties dialog box. Enter the condition text stop='1' in the dialog box using the expression builder and click the Apply button to add this condition to both of the selected transitions.

A confirmation dialog box is displayed warning that the transition from state *getkey* to state *count* has no condition and is not the lowest priority. Click the button to acknowledge the warning.

Repeat this procedure for the *start*='1' and d/=ZEROS conditions.

The condition syntax is checked on entry. Any valid VHDL fragment can be entered using line breaks and indentation to improve the legibility on the diagram if required.

Ensure that the transition priorities leaving the state *getkey* are the same as those shown in the table. You can change a transition priority in the **Transitions** tab of the State Machine Object Properties dialog box. Alternatively, you can use the putton to zoom in or the D button to view an area and use direct text editing to change the priority.

When you change a transition priority, the priority of the other transitions leaving the same state are automatically adjusted.

| 😯 Object Properties      |                     |       | ×       |

|--------------------------|---------------------|-------|---------|

| States Transitions       | Junctions Links Tex | t     |         |

| Number of selected trans |                     | ·     |         |

| - IF Condition           |                     |       |         |

| Modify                   |                     |       |         |

| start='1'                |                     |       | A<br>V  |

| Use Priority: 1          |                     |       | Visible |

| Modify                   |                     |       | Visible |

|                          |                     |       | *       |

| <u>.</u>                 |                     |       | ×       |

| 0                        | K Cancel            | Apply | Help    |

If you have zoomed in, use the *p* button to view all of the state diagram.

Use the 🔙 button to save your changes to the state diagram.

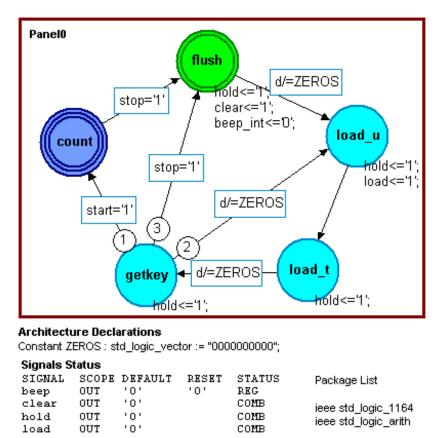

### **Create a Hierarchical State Diagram**

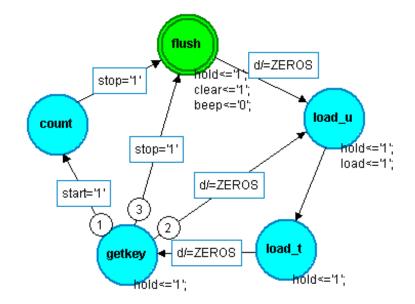

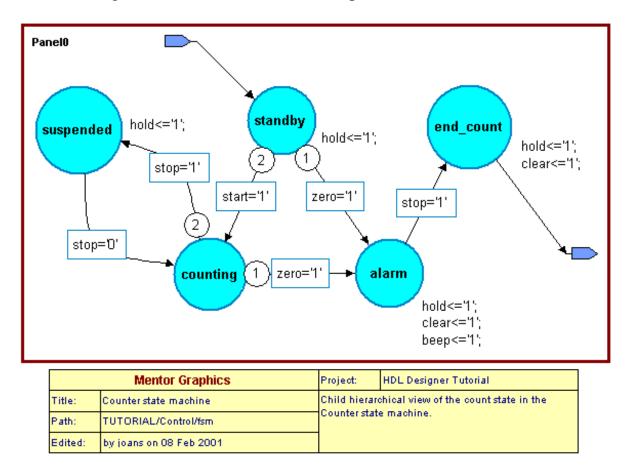

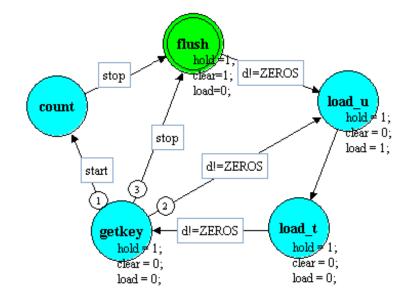

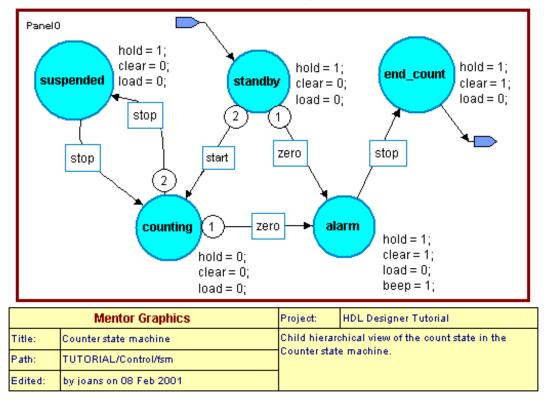

The state diagram should look similar to the following picture.

Select the *count* state and choose **Hierarchical State** in the **Change To** cascade from the **Diagram** menu. Alternatively, select the *count* state and choose the Hierarchical State pulldown option for the State Type in the **States** tab of the State Machine Object Properties dialog box. The *count* state is redrawn as a hierarchical state with a triple outline and darker fill color.

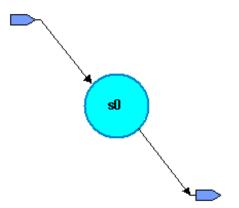

Double-click on the hierarchical state (or use the **Open Down** option from the popup menu) to create the new hierarchical child state diagram. A new child state diagram window is initialized with a default state *s0* connected to an entry point and exit point.

Notice that the name of the hierarchical state (*count*) is included in the window title: *TUTORIAL*\*Control*\*fsm[:count 'machine0']*. This naming convention shows that the child diagram is a partial view of the parent diagram.

Select the exit point and choose **Change to State** from the **Diagram** menu. While the new state is selected, drag with the Right mouse button and release the mouse button with the ghosted state to the left and below the first state. Use the **Copy Here** option from the popup menu to make a copy of the state at the cursor position.

Repeat this procedure to add two more states on the diagram. This is an alternative method for adding objects which can be useful when you want to add an object with the same or similar properties and attributes to an existing object.

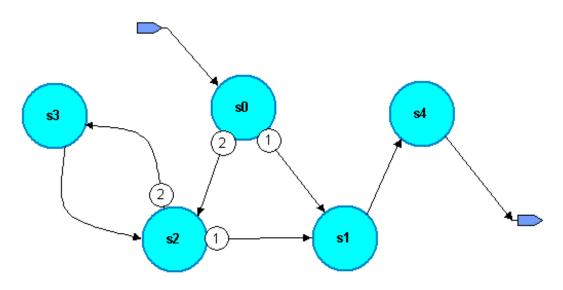

Use the 🔁 button to add a new exit point and the 💽 button to connect transitions between the states as shown in the following picture:

You can add route points while routing a transition by clicking at several points between states to create a smooth arc as shown in the picture between states s2 and s3

#### **Complete the Hierarchical State Diagram**

Use the **States** tab of the State Machine Object Properties dialog box to rename the states and add state actions as shown below:

| Old Name | New Name  | Style | Actions                                 |

|----------|-----------|-------|-----------------------------------------|

| s0       | standby   | IF    | hold<='1';                              |

| s1       | alarm     | IF    | hold<='1';<br>clear<='1';<br>beep<='1'; |

| s2       | counting  | IF    | (no actions)                            |

| s3       | suspended | IF    | hold<='1';                              |

| s4       | end_count | IF    | hold<='1';<br>clear<='1';               |

Use the **Transitions** tab to add the following conditions:

| Origin State | <b>Destination State</b> | Priority | Condition | Actions |

|--------------|--------------------------|----------|-----------|---------|

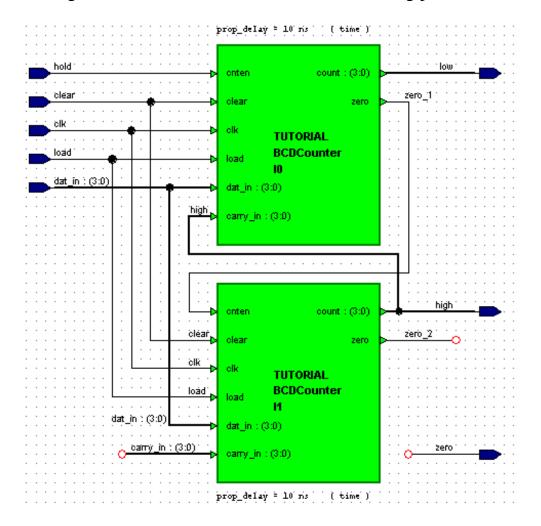

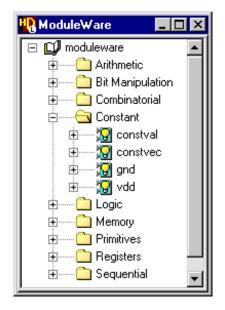

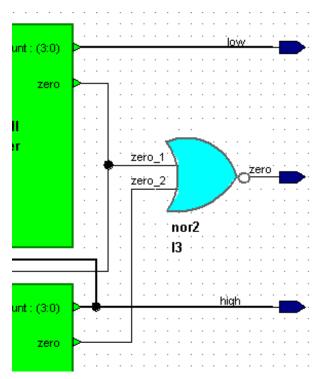

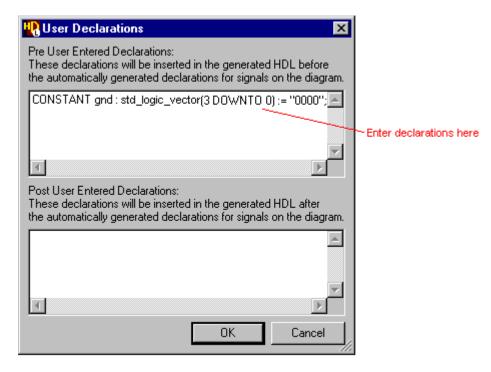

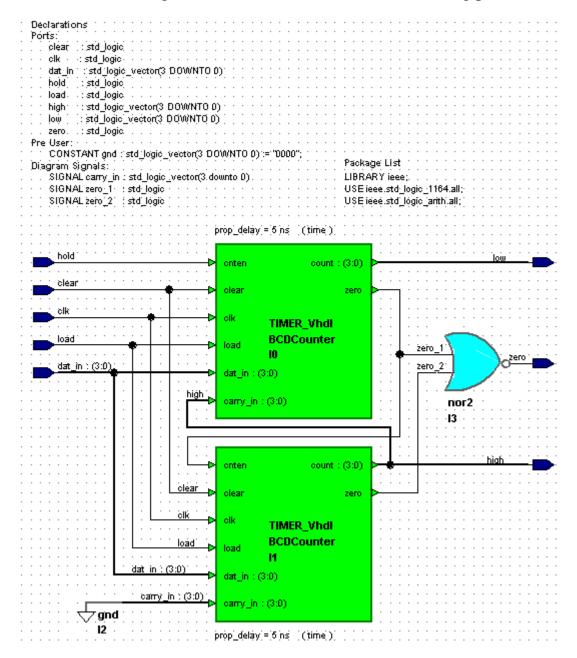

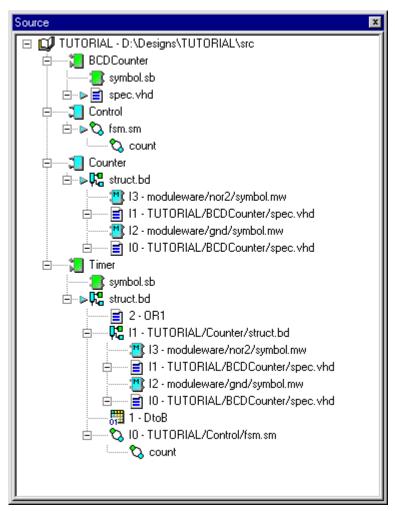

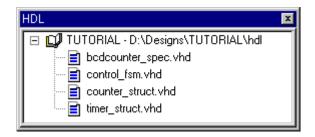

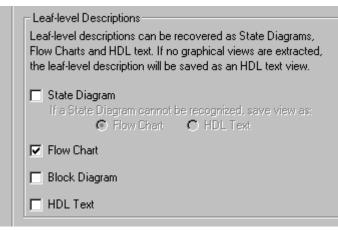

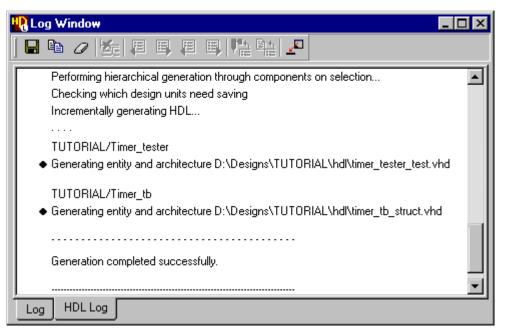

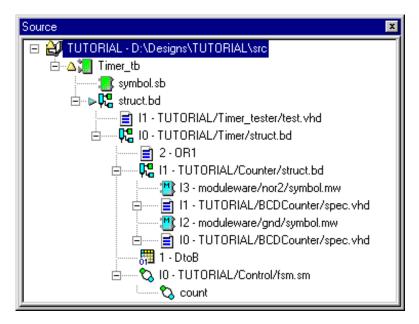

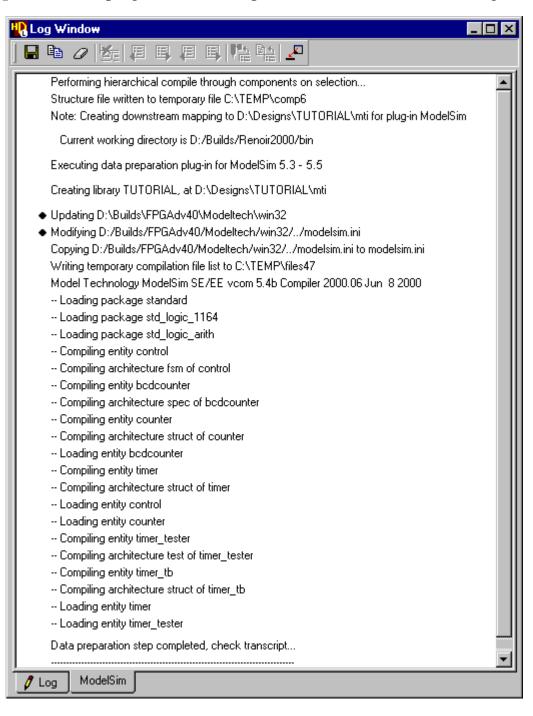

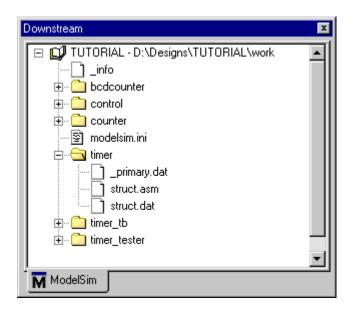

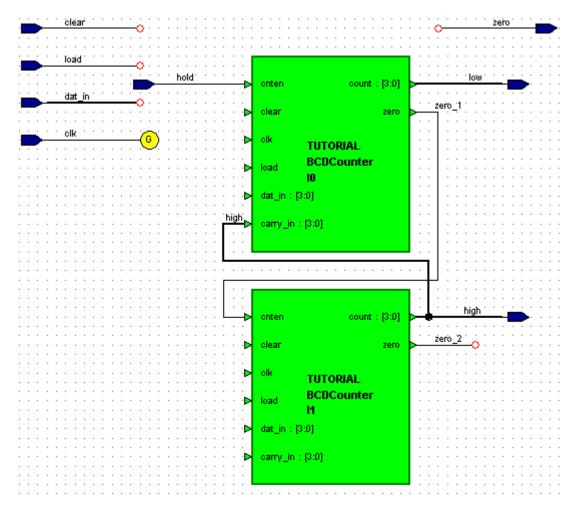

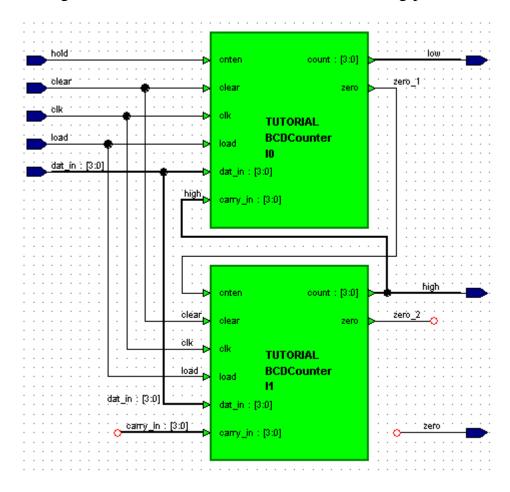

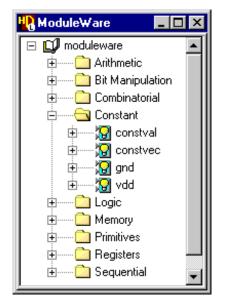

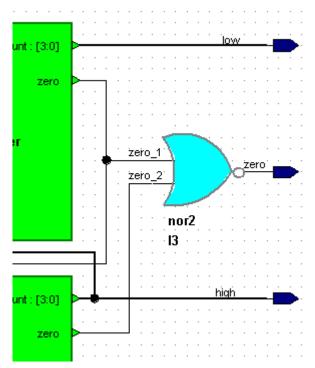

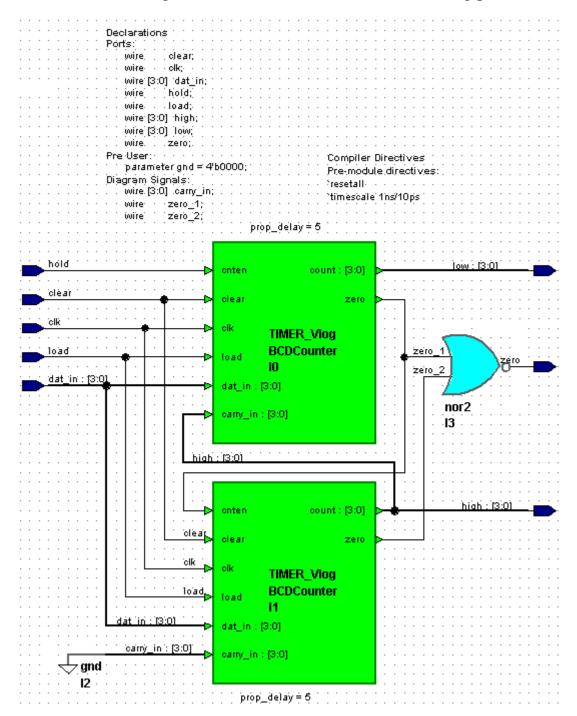

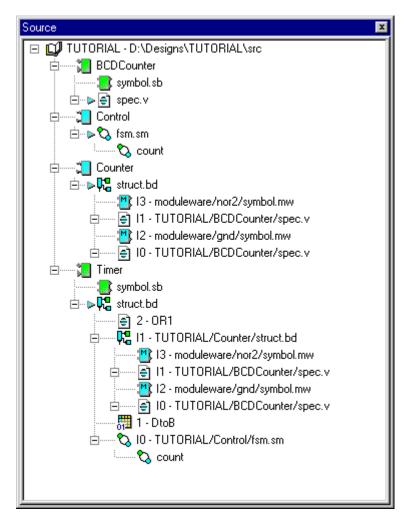

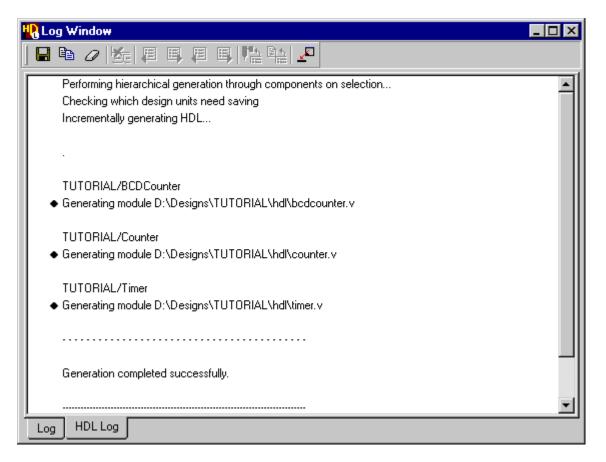

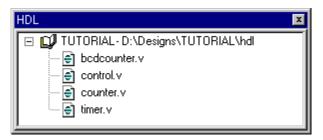

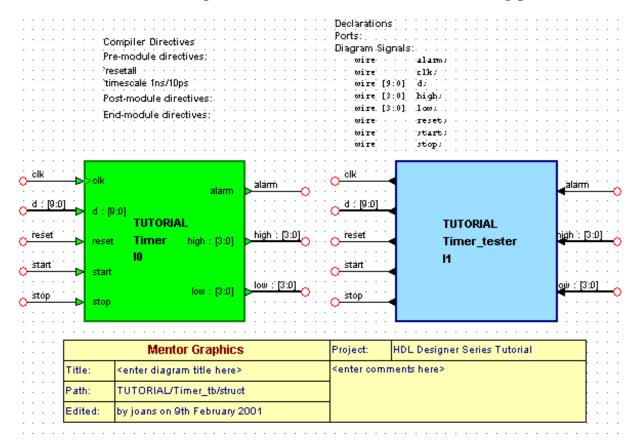

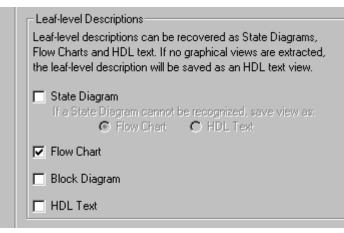

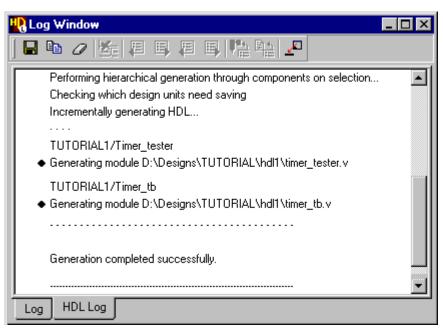

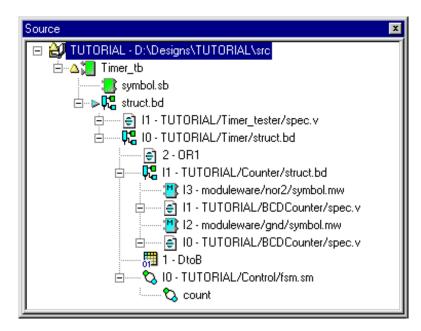

| suspended    | counting                 | 1        | stop='0'  | none    |