## HSPICE/SPICE<sup>™</sup> Interface and SPICE<sup>™</sup> 2G.6 Reference Manual

Product Version 5.0 June 2003  $\ensuremath{\mathbb{C}}$  1999-2003 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134, USA

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 1-800-862-4522.

All other trademarks are the property of their respective holders.

**Restricted Print Permission:** This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used solely for personal, informational, and noncommercial purposes;

- 2. The publication may not be modified in any way;

- 3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

- 4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

## Contents

| Preface                            | 7 |

|------------------------------------|---|

| About This Manual                  | 7 |

| What You Need To Know First        | 7 |

| Finding Information in This Manual | 7 |

| Using FrameMaker to Get Help       | 8 |

## <u>1</u>

| Introduction     | ) |

|------------------|---|

| Product Overview | ) |

| <u>SPICE</u>     | ) |

| <u>HSPICE</u>    | ) |

| Simulation Flow  | ) |

### <u>2</u>

| SPICE Circuit Simulation Interface            | 1 |

|-----------------------------------------------|---|

| <u>Overview</u>                               | 1 |

| Example of a SPICE Simulation Run1            | 1 |

| <u>control file</u>                           |   |

| <u>netlist file</u>                           | 3 |

| <u>spice.inp file</u>                         |   |

| <u>spice.sim file</u>                         |   |

| si.inp file: Used as Input to SPICE 1         | 3 |

| si.log file: Produced from the Simulation Run | 4 |

| si.out file: Output of a SPICE Simulation Run | 4 |

|                                               |   |

## <u>3</u>

| HSPICE Circuit Simulation Interface | 19 |

|-------------------------------------|----|

| Overview                            | 19 |

| Running HSPICE                      | 20 |

| Creating the Schematic              | 20 |

#### HSPICE/SPICE Interface and SPICE 2G.6 Reference Manual

| Generating the Run Directory 21 |

|---------------------------------|

| Editing the control File        |

| Starting the Analysis Run       |

| Generating the Netlist          |

| Creating the Input File         |

| Running the Simulation          |

| Translating the Output          |

| Viewing the Results             |

| Hierarchical Netlisting         |

| Primitive Cell Requirements     |

| Example                         |

## <u>4</u> HSPICE/SPICE Elements

| HSPICE/SPICE Elements                                 | 25 |

|-------------------------------------------------------|----|

| <u>Overview</u>                                       | 25 |

| HSPICE/SPICE Elements and Corresponding Library Cells | 26 |

| HSPICE/SPICE Model and Element Parameters             | 27 |

| Resistor                                              | 27 |

| <u>Capacitor</u>                                      | 28 |

| <u>Inductor</u>                                       |    |

| Transmission Line                                     |    |

| <u>Diode</u>                                          |    |

| <u>BJT</u>                                            |    |

| <u>JFET</u>                                           |    |

| <u>MOSFET</u>                                         |    |

| Formatting Functions                                  |    |

| Element Formats                                       | 37 |

| Model Format                                          | 39 |

## <u>5</u>

| Using SPICE              | 41 |

|--------------------------|----|

| Introduction             | 42 |

| Types of Analysis        | 42 |

| DC Analysis              | 42 |

| AC Small-Signal Analysis | 43 |

#### HSPICE/SPICE Interface and SPICE 2G.6 Reference Manual

| Transient Analysis                                     |

|--------------------------------------------------------|

| Analysis at Different Temperatures 44                  |

| <u>Convergence</u>                                     |

| Input Format                                           |

| Circuit Description                                    |

| Title Card, Comment Cards, and .END Card 47            |

| <u>Title Card</u>                                      |

| . <u>END Card</u>                                      |

| Comment Card                                           |

| Element Cards for Passive Circuit Elements and Sources |

| <u>Resistors</u>                                       |

| Capacitors and Inductors                               |

| Coupled (Mutual) Inductors                             |

| Transmission Lines (Lossless)                          |

| Linear Dependent Sources                               |

| Independent Sources                                    |

| Semiconductor Devices                                  |

| Element Cards for Semiconductor Devices                |

| Junction Diodes                                        |

| Bipolar Junction Transistors (BJT)                     |

| Junction Field-Effect Transistors (JFET)               |

| <u>MOSFET</u>                                          |

| MODEL Cards for Semiconductor Devices                  |

| <u>.MODEL Card</u>                                     |

| Diode Model Type                                       |

| NPN and PNP Model Type (BJT Model)                     |

| NJF and PJF Model Type (JFET Model)63                  |

| NMOS & PMOS Model Type (MOSFET Model)64                |

| <u>Subcircuits</u>                                     |

| . <u>SUBCKT Card</u>                                   |

| . <u>ENDS Card</u>                                     |

| Subcircuit Calls                                       |

| Control Cards                                          |

|                                                        |

|                                                        |

| . <u></u>                                              |

| <u>.OP Card</u>                                 |

|-------------------------------------------------|

| .DC Card                                        |

| .NODESET Card                                   |

|                                                 |

|                                                 |

|                                                 |

| <u>.AC Card</u>                                 |

| . <u>DISTO Card</u>                             |

| . <u>NOISE Card</u>                             |

| <u>.TRAN Card</u>                               |

| <u>.FOUR Card</u>                               |

| . <u>PRINT Card</u>                             |

| . <u>PLOT Card</u>                              |

| Example of Data Decks                           |

| <u>Circuit 1</u>                                |

| <u>Circuit 2</u>                                |

| <u>Circuit 3</u>                                |

| <u>Circuit 4</u>                                |

| <u>Circuit 5</u>                                |

| Nonlinear Dependent Sources                     |

| Voltage-Controlled Current Sources              |

| Voltage-Controlled Voltage Sources              |

| Current-Controlled Current Sources              |

| Current-Controlled Voltage Sources              |

| Bipolar Model Equations (Gmin terms omitted) 87 |

| <u>DC Model</u>                                 |

| <u>AC Model</u>                                 |

| Noise Model                                     |

| Temperature Effects                             |

| Excess Phase                                    |

| Alter Statement and the Source-Stepping Method  |

| <u>References</u>                               |

|                                                 |

| Index                                           |

## Preface

## **About This Manual**

This manual is for engineers and designers of integrated circuits. It is a reference to the following products:

- The HSPICE<sup>™</sup> interface, which lets you run an HSPICE simulation in the Cadence environment

- The SPICE interface, which lets you run a SPICE simulation in the Cadence environment

- The SPICE 2G.6 circuit simulator developed by the University of California at Berkeley

#### What You Need To Know First

Before you read this manual or use these simulations interfaces to run simulation, you should read

- The <u>Cadence Design Framework II User Guide</u> for general information about getting around in the Cadence software. This manual shows you how to start the system, use the mouse and windows, and start a design session.

- The <u>Simulation Environment Help</u> for setting up and running a basic simulation using menus and forms

#### **Finding Information in This Manual**

The following table summarizes the topics covered in this manual.

| For information about              | Read                                             |

|------------------------------------|--------------------------------------------------|

| Running a SPICE simulation         | Chapter 2, "SPICE Circuit Simulation Interface"  |

| Running an HSPICE simulation       | Chapter 3, "HSPICE Circuit Simulation Interface" |

| sample library & simulation models | Chapter 4, "SPICE/HSPICE Simulation Models"      |

| SPICE version 2G.6                 | Chapter 5, "Using SPICE "                        |

#### Using FrameMaker to Get Help

You can use FrameMaker to open the Online Reference Index directly. Clicking on a manual title in the Online Reference Index opens the Table of Contents for that manual. From the Table of Contents, you can go to specific pages in the manual. The arrows and buttons at the bottom of each page move you around in the document, return you to the Table of Contents or the Online Reference Index, or quit the Online Reference system.

## Introduction

This chapter includes the following topics:

- Product Overview

- Simulation Flow

## **Product Overview**

#### SPICE

SPICE is a general-purpose circuit simulator developed by the University of California at Berkeley. It is used for nonlinear DC, nonlinear transient, and linear AC analysis. Cadence supports a library of primitives and a full interface to SPICE version 2G.6. Cadence does not sell the SPICE program but supplies a copy of this public Domain program and its manual free of charge when you purchase the interface.

#### **HSPICE**

HSPICE is a general-purpose circuit simulator from Meta-Software. It has an extensive set of built-in device models, including models for small geometry MOSFETs and MESFETs. The program is compatible with SPICE and MSING input formats. Cadence supports a library of primitives and a full interface for HSPICE.

## **Simulation Flow**

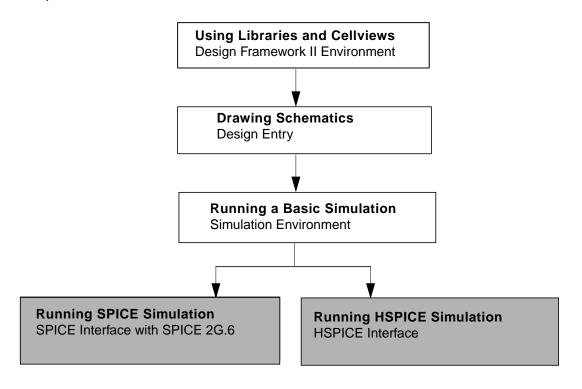

The following chart shows the flow of the tasks involved in running a simulation using SPICE and HSPICE and the name of the product you would use for each task. This manual covers the products in the shaded boxes.

June 2003

## **SPICE Circuit Simulation Interface**

This chapter contains the following topics:

- Overview

- Example of a SPICE Simulation Run

### Overview

To set up and run a basic simulation using menus and forms, refer to <u>Simulation</u> <u>Environment Help</u>. Here is information specific to running the SPICE simulator:

- SPICE does not have a command to read an input file, so the *netlist* file must be specified in the *control* file with the simulation environment file inclusion function, "[!netlist]", this tells the interface to include the *netlist* file in the file that is passed to SPICE. For an example of this, refer to the sample SPICE *control* file in "Example of a SPICE Simulation Run" on page 15. Any other command or stimulus files you want to use as input to SPICE can be specified in the same way.

- The template control file for SPICE includes two other files in addition to the netlist file, spice.inp and spice.sim. These files are for stimulus data and simulator commands. The Initialize command from the Simulation menu automatically creates templates for these files in a new run directory.

- The waveform interface for SPICE does not handle multiple analysis simulation runs. To view waveforms, perform one analysis for each simulation run.

- The Waveform Display program does not display results of AC small-signal analysis simulation runs. Use the SPICE .PRINT or .PLOT commands to generate SPICE text output, and read it using the view output command.

### **Example of a SPICE Simulation Run**

This section shows an example of input and output files needed for running a SPICE simulation.

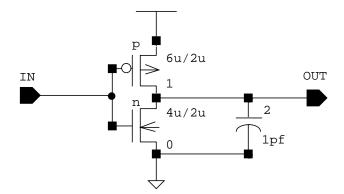

The following input and output files are for running the simulation on the inverter shown below:

- The *control* file is used as an input for running the simulation.

- The netlist file created by running the netlister on the design.

- The si.inp file is created by the simulation interface and is passed to SPICE. This file is formed by including the specified files in the control file and mapping the user-defined names to numbers suitable for SPICE.

- The spice.inp file is created by the *Initialize* command. Modify this file by adding the stimulus data.

- The *spice.sim* file is created by the *Initialize* command. Modify this file by adding the simulator commands.

- The *si.log* file is the log of the simulation run.

- The *si.out* file is the text output created by SPICE.

#### control file

```

* Spice control file

.options acct opts nopage limpts=1000

.width in=80 out=80

[!spice.inp]

[!netlist]

[!spice.sim]

.end

```

#### netlist file

```

* net 1 = vdd!

* net 0 = gnd!

* net 2 = /OUT

* net 3 = /IN

.MODEL Model1 pmos level=2 vto=-.7 kp=1.5e-05 gamma=.4

+lambda=.03 tox=6.e-07 xqc=.5

* pmos(0) = /1

M$#0 1 3 2 1 Model1 l=2u w=6u

* capacitor(1) = /2

C$#1 2 0 poly 1pf

.MODEL Model3 nmos level=2 vto=.7 kp=3.e-05 gamma=.2 +lambda=.02

+ tox=6.e-07 xqc=.5

* nmos(2) = /0

M$#2 2 3 0 0 Model3 l=2u w=4u

```

#### spice.inp file

vdd [#vdd!] [#gnd!] dc 5v vin [#/IN] 0 pwl 0 0 100ns 5v 150ns 5v 250ns 0

#### spice.sim file

.tran 1ns 300ns

#### si.inp file: Used as Input to SPICE

```

* Spice control file

.options acct opts nopage limpts=1000

.width in=80 out=80

vdd 1 0 dc 5v

vin 3 0 pwl 0 0 100ns 5v 150ns 5v 250ns 0

* net 1 = vdd!

* net 0 = qnd!

* net 2 = /OUT

* net 3 = /IN

.MODEL Model1 pmos level=2 vto=-.7 kp=1.5e-05 gamma=.4

+lambda=.03 tox=6.e-07 xqc=.5

* pmos(0) = /1

M$#0 1 3 2 1 Model1 l=2u w=6u

* capacitor(1) = /2

C$#1 2 0 poly 1pf

.MODEL Model3 nmos level=2 vto=.7 kp=3.e-05 gamma=.2

```

```

lambda=.02

+ tox=6.e-07 xqc=.5

* nmos(2) = /0

M$#2 2 3 0 0 Model3 l=2u w=4u

.tran lns 300ns

```

```

.end

```

#### si.log file: Produced from the Simulation Run

```

si version 4.0.55 Wed Apr 18 21:51:31 PDT 1990

(cds2082)

si: Loading user defined simulation run control file "~/.simrc".

si: Loading simulation environment file "/usr/mnt2/hpeter/4.0/group/

spice/test2/run1/si.env".

si: Loading simulation capabilities file "/usr/mnt2/hpeter/4.0/etc/

skill/si/simcap.ile".

Running simulation in directory: "/usr/mnt2/hpeter/4.0/group/spice/

test2/run1".

Running netlist

Begin netlist: Apr 26 11:58:45 1990

simulation library path = ". ~"

simulation library = testLib

library configuration = default

cell = spice.cct2

view = schematic

view list = ("spice" "cmos.sch" "schematic")

stopping view list = ("spice")

End netlist: Apr 26 11:58:54 1990

Running simin

Running runsim with simulator: "spice"

Begin simulation:

Apr 26 11:58:56 1990

End simulation:

Apr 26 12:02:38 1990

Running simout

Simulation completed successfully.

```

#### si.out file: Output of a SPICE Simulation Run

```

***4/26/90 ***** SPICE 2G.6 3/16/83 ****14:35:31***

* SPICE CONTROL FILE

**** INPUT LISTING TEMPERATURE = 27.000 DEG C

```

### HSPICE/SPICE Interface and SPICE 2G.6 Reference Manual

SPICE Circuit Simulation Interface

```

.OPTIONS ACCT OPTS NOPAGE LIMPTS=1000

.WIDTH IN=80 OUT=80

VDD vdd! gnd! DC 5V

VIN /IN gnd! PWL 0 0 100NS 5V 150NS 5V 250NS 0

* NET 1

=

VDD!

* NET 0

=

GND!

* NET 2

/OUT

=

* NET 3

=

/IN

.MODEL MODEL1 PMOS LEVEL=2

VTO=-.7 KP=1.5E-05

GAMMA=.4

+LAMBDA=.03

TOX=6

.E-07 XOC=.5

* PMOS(0) = /1

M/1 vdd! /IN /OUT vdd! MODEL1 L=2U

W=6U

* CAPACITOR(1) = /2

C/2 /OUT gnd! POLY 1PF

.MODEL MODEL3 NMOS LEVEL=2 VTO=.7 KP=3.E-05 GAMMA=.2

+ LAMBDA=.02

+ TOX = 6.E - 07

XOC=.5

* NMOS(2) = /0

M/0 /OUT /IN gnd! gnd! MODEL3 L=2U

W = 4U

.TRAN 1NS 300NS

.END

**** MOSFET MODEL PARAMETERS TEMPERATURE = 27.000 DEG C

MODEL1

MODEL3

TYPE

PMOS

NMOS

LEVEL

2.000

2.000

VTO

-0.700

0.700

ΚP

1.50D-05

3.00D-05

GAMMA

0.400

0.200

3.00D-02

2.00D-02

LAMBDA

TOX

6.00D-07

6.00D-07

XOC

0.500

0.500

**** OPTION SUMMARY TEMPERATURE = 27.000 DEG C

DC ANALYSIS -

GMIN

=

1.000D-12

RELTOL

1.000D-03

=

1.000D-12

ABSTOL

=

1.000D-06

VNTOL

=

LVLCOD

1

=

100

ITL1

=

ITL2

=

50

PIVTOL

1.000D-13

=

1.000D-03

PIVREL

=

TRANSIENT ANALYSIS -

METHOD

=

TRAP

```

| MAXORD            | =                   | 2                                       |

|-------------------|---------------------|-----------------------------------------|

| CHGTOL            | =                   | 1.000D-14                               |

| TRTOL             | =                   | 7.000D+00                               |

| LVLTIM            | =                   | 2                                       |

| MU                | =                   | 0.500                                   |

| ITL3              | =                   | 4                                       |

| ITL4              | =                   | 10                                      |

| ITL5              | =                   | 5000                                    |

| MISCELLAN         | eous -              |                                         |

| LIMPTS            | =                   | 1000                                    |

| LIMTIM            | =                   | 2                                       |

| CPTIME            | =                   | 10000000                                |

| NUMDGT            | =                   | 4                                       |

| TNOM              | =                   | 27.000                                  |

| DEFL              | =                   | 1.000D-04                               |

| DEFW              | =                   | 1.000D-04                               |

| DEFAD             | =                   | 0.000D+00                               |

| DEFAS             | =                   | 0.000D+00                               |

|                   |                     |                                         |

| * * * * * * * * * | * * * * * * * * * * | * * * * * * * * * * * * * * * * * * * * |

| MOSFET MO         | DEL PARAME          | TERS TEMPERATURE = 27.000 DEG C         |

|                   | MODEL1              | MODEL3                                  |

| TYPE              | PMOS                | NMOS                                    |

| LEVEL             | 2.000               | 2.000                                   |

| VTO               | -0.700              | 0.700                                   |

| KP                | 1.50D-05            | 3.00D-05                                |

| GAMMA             | 0.400               | 0.200                                   |

| LAMBDA            | 3.00D-02            | 2.00D-02                                |

| TOX               | 6.00D-07            | 6.00D-07                                |

| XQC               | 0.500               | 0.500                                   |

| **** OPTI         | ON SUMMARY          | TEMPERATURE = $27.000$ DEG C            |

| DC ANALYS         | IS -                |                                         |

| GMIN              | =                   | 1.000D-12                               |

| RELTOL            | =                   | 1.000D-03                               |

| ABSTOL            | =                   | 1.000D-12                               |

| VNTOL             | =                   | 1.000D-06                               |

| LVLCOD            | =                   | 1                                       |

| ITL1              | =                   | 100                                     |

| ITL2              | =                   | 50                                      |

| PIVTOL            | =                   | 1.000D-13                               |

| PIVREL            | =                   | 1.000D-03                               |

| TRANSIENT         | ANALYSIS            | -                                       |

| METHOD            | =                   | TRAP                                    |

| MAXORD            | =                   | 2                                       |

| CHGTOL            | =                   | 1.000D-14                               |

| TRTOL             | =                   | 7.000D+00                               |

| LVLTIM            | =                   | 2                                       |

|                   |                     | -                                       |

| MU              | _                 | 0.500             |                     |                     |                     |           |       |

|-----------------|-------------------|-------------------|---------------------|---------------------|---------------------|-----------|-------|

| MO<br>ITL3      | =                 | 4                 |                     |                     |                     |           |       |

|                 | =                 | _                 |                     |                     |                     |           |       |

| ITL4            | =                 | 10                |                     |                     |                     |           |       |

| ITL5            |                   | 5000              |                     |                     |                     |           |       |

| MISCELLA        |                   | 1000              |                     |                     |                     |           |       |

| LIMPTS          | =                 | 1000              |                     |                     |                     |           |       |

| LIMTIM          | =                 | 2                 |                     |                     |                     |           |       |

| CPTIME          | =                 | 100000            | 0000                |                     |                     |           |       |

| NUMDGT          | =                 | 4                 |                     |                     |                     |           |       |

| TNOM            | =                 | 27.000            |                     |                     |                     |           |       |

| DEFL            | =                 | 1.0001            |                     |                     |                     |           |       |

| DEFW            | =                 | 1.0001            |                     |                     |                     |           |       |

| DEFAD           | =                 | 0.0001            | 0+00                |                     |                     |           |       |

| DEFAS           | =                 | 0.0001            | 0+00                |                     |                     |           |       |

| * * * * * * * * | * * * * * * * * * | * * * * * * * * * | * * * * * * * * * * | * * * * * * * * * * | * * * * * * * * * * | * * * *   |       |

| INITIAL         | TRANSIENT         | SOLUTION          | I TEMPERA           | ATURE = 27          | .000 DEG            | С         |       |

| NODE VOL        | TAGE NODE         | VOLTAGE           | NODE VOLT           | ГАGE                |                     |           |       |

| (vdd!) 5        | .0000 (/0         | UT) 5.000         | )0 (/IN) (          | 0.0000              |                     |           |       |

| VOLTAGE         | SOURCE CU         | RRENTS            |                     |                     |                     |           |       |

| NAME            | CURRENT           | 1                 |                     |                     |                     |           |       |

| VDD             | -6.933D           | -12               |                     |                     |                     |           |       |

| VIN             | 0.000D+           | 00                |                     |                     |                     |           |       |

|                 | WER DISSI         |                   | 47D-11 WA           | ATTS                |                     |           |       |

| ******          | ******            | *******           | *******             | * * * * * * * * * * | ********            | * * * *   |       |

| OPERATIN        | G POINT I         | NFORMATIC         | N TEMPER            | RATURE = 2          | 27.000 DEC          | G C       |       |

| **** MOS        | FETS              |                   |                     |                     |                     |           |       |

|                 | M/1               | М/О               |                     |                     |                     |           |       |

| MODEL           | MODEL1            | MODEL3            | 3                   |                     |                     |           |       |

| ID              | 6.80E-1           |                   |                     |                     |                     |           |       |

| VGS             | -5.000            | 0.000             |                     |                     |                     |           |       |

| VDS             | 0.000             | 5.000             |                     |                     |                     |           |       |

| VBS             | 0.000             | 0.000             |                     |                     |                     |           |       |

| JOB CONC        |                   | 0.000             |                     |                     |                     |           |       |

|                 | STATISTI          | CS STIMMAR        | Y TEMPET            | RATURE = 2          | 7 000 DEC           | r C       |       |

| NUNODS          | NCNODS            | NUMNOD            | NUMEL               | DIODES              | BJTS                | JFETS     | MFETS |

| 4               | 4                 | 4                 | 5                   | 0                   | 0                   | 01115     | 2     |

| +<br>NUMTEM     | 4<br>ICVFLG       | 4<br>JTRFLG       | JACFLG              | INOISE              | U<br>IDIST          | NOGO      | 2     |

| 1               | 0                 | 301               | 0                   | 0                   | 0                   | NOGO<br>0 |       |

| ı<br>NSTOP      | 0<br>NTTBR        | NTTAR             | U<br>IFILL          |                     |                     | 0         |       |

| NSIOP<br>б.     | 13.               |                   |                     | IOPS                | PERSPA              |           |       |

|                 |                   | 13.               | 0.                  | 21.                 | 63.889              |           |       |

| NUMTTP          | NUMRTP            | NUMNIT            | MAXMEM              | MEMUSE              | COPYKNT             |           |       |

| 71.             | 4.                | 170.              | 249984              | 1576                | 15052.              |           |       |

| READIN          | 0.42              |                   |                     |                     |                     |           |       |

| SETUP           | 0.05              |                   |                     |                     |                     |           |       |

| TRCURV          | 0.00              | 0.                |                     |                     |                     |           |       |

| DCAN            | 0.18              | 13.               |                     |                     |                     |           |       |

| DCDCMP          |                   | 0                 |                     |                     |                     |           |       |

| 2 0 2 0 1 1 2   | 0.067             | 2.                |                     |                     |                     |           |       |

| DCSOL     | 0.067           |                       |                 |       |             |                 |

|-----------|-----------------|-----------------------|-----------------|-------|-------------|-----------------|

| ACAN      | 0.00            | 0.                    |                 |       |             |                 |

| TRANAN    | 3.63            | 170.                  |                 |       |             |                 |

| OUTPUT    | 0.00            |                       |                 |       |             |                 |

| LOAD      | 3.067           |                       |                 |       |             |                 |

| CODGEN    | 0.000           | lfs                   | 0.              |       |             |                 |

| CODEXC    | 0.000           |                       |                 |       |             |                 |

| MACINS    | 0.000           |                       |                 |       |             |                 |

| OVERHEAD  | 0.07            |                       |                 |       |             |                 |

| TOTAL JOB | TIME 4          | .35                   |                 |       |             |                 |

| ********  | * * * * * * * * | * * * * * * * * * * * | * * * * * * * * | ***** | * * * * * * | * * * * * * * * |

## **HSPICE Circuit Simulation Interface**

This chapter contains the following topics:

- Overview

- Running HSPICE

- <u>Hierarchical Netlisting</u>

### Overview

Using the HSPICE interface is very similar to using the SPICE interface. Before reading this chapter, which contains information specific to running an HSPICE simulation, read the chapter on the SPICE interface.

- With the HSPICE interface you can

- Generate flat or hierarchical netlists

- **u** Run local and remote simulations

- Use element and model parameters supported by HSPICE

- HSPICE differs from SPICE in its handling of waveform output from multiple analysis simulation runs.

The waveforms from each analysis are written to separate files that have automatically generated names in Waveform Storage Format (WSF) files. These files can be read by the Waveform Display program.

The waveforms from the first analysis are stored in the *raw/waves* file in the simulation run directory and can be viewed immediately using the Waveform Display program. To view a waveform file other than the default file *(raw/waves)*, use the *Attach* command from the Waveform Display menu.

The naming convention for the files in the raw subdirectory is

• Waveforms from the first analysis are stored in *waves*.

□ Waveforms from subsequent analyses are stored in files called *waves.suffix*, where *suffix* is automatically generated. The suffix consists of a code for the analysis type and a serial number starting from zero. Analysis type codes are

DC sweep sw transient tr AC ac

## **Running HSPICE**

This section describes the following:

- Creating the schematic

- Generating the run directory

- Editing the control file

- Starting the analysis run

- Generating the netlist

- Creating the input file

- Running the simulation

- Translating the output

- Viewing the results

Most of this information is covered in greater detail in the <u>Virtuoso Schematic Composer User</u> <u>Guide</u> and <u>Simulation Environment Help.</u> Here you will find only what is specific to HSPICE.

#### **Creating the Schematic**

Create schematics for HSPICE simulation in the same way as any other schematic in the Cadence Design Framework II (DFII) environment. The main difference is that each cell in the schematic (for example, transistors, resistors, capacitors) must have a *symbol* and an *hspice* view to be recognized by the HSPICE interface. For a list of the netlisting properties required for the *hspice* view, see "Primitive Cell Requirements" on page 27.

#### **Generating the Run Directory**

The first time you run a simulation, select the *Initialize* command from the Simulation menu to generate a run directory. This run directory is where the *control, netlist*, and simulation input and output files are kept for the simulation being run. When you want to keep an older simulation instead of overwriting it, you can generate and use multiple simulation run directories. Refer to <u>Simulation Environment Help</u>.

#### **Editing the control File**

When the system initially creates the run directory, it also creates a dummy control file.

Edit this file to include any information that is not in the schematic. Add the *sda* option on the *.options* line in the *control* file. Set *sda=2*, which tells HSPICE to generate a waveform file with the format required by the simulation environment.

Edit the *hspice.inp* file to add stimulus data and edit the *hspice.sim* file to add simulator commands.

#### **Starting the Analysis Run**

With the schematic entered and the *control* file generated, you are ready to start the simulation. Select the *Netlist/Simulate* command from the Simulation menu. This commands netlists the schematic and starts the simulation; simulation can be run in the background or foreground. Each step in the analysis process is described below.

#### Generating the Netlist

The simulation environment creates an HSPICE netlist for the desired schematic. This netlist contains the connectivity description in the proper format for HSPICE. See "Formatting Functions" for information about formats. You can generate a flat or a hierarchical netlist. Both have the same information, but their formats are different. You control the type of netlist generated by setting the simulation environment *simNetlistHier* variable. If this variable is set to *t*, a hierarchical netlist is created; otherwise, a flat netlist is created by default. Typically, you set this variable in your *.simrc* file.

#### **Creating the Input File**

Once the netlist is generated, the HSPICE interface automatically translates the instance and net names in the *control*, *hspice.inp*, *hspice.sim*, and *netlist* files to legal names for

HSPICE. When the translation completes, these files are assembled to create the HSPICE *si.inp* input file.

#### Running the Simulation

When the simulator input file (*si.inp*) is created, simulation starts. If the *simHost* variable is set to a different machine, the simulation runs remotely.

For more information about remote simulation, refer to Simulation Environment Help.

#### Translating the Output

When the simulation is finished, the text output and the waveform output are translated as follows:

- The simulation interface translates net and instance names that were previously translated back to the original user-assigned names. The resulting translated text output is stored in the *si.out* file.

- The waveform output of HSPICE is automatically generated in WSF format if the *sda=2* option is set in your *control* file. The interface converts this text format to binary WSF using the *wdd* program.

The translated waves file is stored in the raw directory under the current simulation run directory. HSPICE generates more than one waveform file when you perform more than one simulation for a job (for example, more than one transient simulation, or a transient simulation and an AC frequency sweep simulation). In this case, all waveform files are stored in the raw directory, but only the first waveform file is called *waves*. All other waveform files have the name waves with a unique suffix.

#### Viewing the Results

The simulation environment notifies you when analysis is complete so you can view the outputs. Information about the simulation run is recorded in the *si.log* file when a background simulation is run.

## **Hierarchical Netlisting**

The hierarchical netlister produces a netlist that is easier to read and understand than one that has been flattened. For more information about flat netlisting, refer to the of <u>Simulation</u> <u>Environment Help</u>. The following are primary features of a hierarchical netlist:

- The hierarchy of the netlist duplicates the hierarchy of your design. The netlister creates a separate subcircuit for each cell in your schematic. This can dramatically reduce the number of lines in the netlist, since the subcircuit definition is printed only once and all instances of the cell are netlisted as calls to the subcircuit.

- Unlike the flat netlister, which translates every instance and net name to a unique name, the hierarchical netlister translates only names that are illegal to HSPICE. To avoid naming conflicts, the hierarchical netlister makes every effort to keep the original user-assigned names in the netlist. When necessary, names are mapped, but the mapping is minimal. Characters that are illegal in HSPICE names are

.,()[]\$'<>

When any of these characters is found in a name, the character is automatically deleted. In some cases, the name is completely remapped. Usually this occurs when you have specified a name that is too long. HSPICE names are limited to eight characters. If a name is longer than eight characters, it is mapped by the interface.

When HSPICE maps the entire name, it assigns a unique number preceded by an *n* for net names, an *i* for instance names, and an *m* for macro and model names.

The first character of an element name in the netlist indicates the element type. The netlister automatically adds a prefix to all instance names. For example, MOSFET instance names are prefixed with m, and resistor names with r.

#### **Primitive Cell Requirements**

A cell must have both a *symbol* and an *hspice* view to be recognized by the HSPICE interface. The *hspice* view for a cell must contain the same pins that exist in the *symbol* view for the cell. For netlisting, define the following properties in the *hspice* view:

#### NLPElementPostamble

Indicates to the flat netlister how to format the element cards for an instance of the cell.

#### ■ NLPModelPreamble

Indicates to the flat netlister how to format the model card for an instance of the cell.

#### ■ hnlHspiceFormatInst

Indicates to the hierarchical netlister what procedure to call to format and print the element cards for an instance of the cell.

#### hnlHspiceParamList

Indicates to the hierarchical netlister what parameters can be inherited. The value of this parameter must be the name of a Cadence SKILL<sup>™</sup> language variable, whose value is the list of parameters that can be inherited. Any parameter that does not appear on this list cannot inherit its value and must be assigned fixed values.

#### hnlHspiceFormatModel

Indicates to the hierarchical netlister what procedure to call to format and print out the model card for an instance of the cell.

#### Example

The following are the property values for the above netlisting properties in the *hspice* view of the *nmos* cell in the *sample* library:

```

NLPElementPostamble = nlpExpr("[@NLPElementComment:%\n]

[@NLPnmosElementCard]")

NLPModelPreamble = nlpExpr("[@NLPmosfetModelCard]")

hnlHspiceFormatInst = "hnlHspicePrintNMOSfetElement()"

hnlHspiceParamList = "hnlHspiceMOSfetParamList"

hnlHspiceFormatModel = "hnlHspicePrintMOSfetModel()"

```

The flat netlister uses expressions defined in the *nlpglobals* cell to format elements and models. The first two properties, therefore, tell the netlister to format the element and model cards with the *NLPnmosElementCard* and *NLPmosfetModelCard* expressions, defined in the *hspice* view of the *nlpglobals* cell.

For hierarchical netlisting, the element and model cards are formatted using the procedures defined in the *hspice* formater. For the *nmos* transistor, these procedures are called *hnIHspicePrintNMOSfetElement* and *hnIHspicePrintMOSfetModel*.

## 4

## **HSPICE/SPICE Elements**

This chapter contains the following topics:

- Overview

- HSPICE/SPICE Elements and Corresponding Library Cells

- <u>HSPICE/SPICE Model and Element Parameters</u>

- Formatting Functions

### Overview

This chapter is divided into three sections.

The first section lists the HSPICE/SPICE elements and the corresponding cells in the *sample* library.

The second section has information about the library cells, terminal names, element and model parameters, for each HSPICE/SPICE element.

The third section has information about the formatting functions for each HSPICE/SPICE element.

# HSPICE/SPICE Elements and Corresponding Library Cells

| HSPICE/SPICE Element<br>(Model Type) | Library Cell |

|--------------------------------------|--------------|

| R                                    | res          |

| R                                    | resistor     |

| С                                    | сар          |

| С                                    | capacitor    |

| С                                    | pcapacitor   |

| L                                    | inductor     |

| Т                                    | tline        |

| G                                    | soi.vc       |

| G                                    | vcisrc       |

| E                                    | SOV.VC       |

| E                                    | vcvsrc       |

| F                                    | soi.ic       |

| Н                                    | sov.ic       |

| V                                    | SOV          |

| V                                    | VSIC         |

| I                                    | soi          |

| I                                    | isrc         |

| D                                    | diode        |

| D                                    | pdiode       |

| Q(npn)                               | npn          |

| Q(npn)                               | npns         |

| Q(pnp)                               | pnp          |

| Q(pnp)                               | pnps         |

| J(njf)                               | njfet        |

| J(pjf)                               | pjfet        |

| HSPICE/SPICE Element<br>(Model Type) | Library Cell |  |

|--------------------------------------|--------------|--|

| M(nmos)                              | ndepl        |  |

| M(nmos)                              | nfet         |  |

| M(nmos)                              | nmos         |  |

| M(nmos)                              | nmosd        |  |

| M(nmos)                              | nmose        |  |

| M(nmos)                              | nsftn        |  |

| M(nmos)                              | nxfr         |  |

| M(pmos)                              | pdepl        |  |

| M(pmos)                              | pfet         |  |

| M(pmos)                              | pmos         |  |

| M(pmos)                              | pmosd        |  |

| M(pmos)                              | pmose        |  |

| M(pmos)                              | psftn        |  |

| M(pmos)                              | pxfr         |  |

### **HSPICE/SPICE Model and Element Parameters**

#### Resistor

#### HSPICE/SPICE Element: Resistor Element Name: R Used by Library Cells: *res*, *resistor*

| Terminal Name | Level of<br>Simulation | Direction   |

|---------------|------------------------|-------------|

| A             | Circuit                | inputOutput |

| Y             | Circuit                | inputOutput |

| Element<br>Parameter | Data Type | Units |

|----------------------|-----------|-------|

| r                    | float     | ohms  |

| tc                   | string    |       |

#### Capacitor

#### HSPICE/SPICE Element: Capacitor Element Named: C Used by Library Cells: cap, capacitor, pcapacitor

| - |

|---|

| Element Parameter | DataType | Units  |

|-------------------|----------|--------|

| С                 | float    | farads |

| ic                | string   |        |

#### Inductor

#### HSPICE/SPICE Element: Inductor Element Name: L Used by Library Cell: inductor

| Terminal Name        | Level of<br>Simulation | Direction   |

|----------------------|------------------------|-------------|

| PLUS                 | Circuit                | inputOutput |

| MINUS                | Circuit                | inputOutput |

|                      |                        |             |

| Element<br>Parameter | Data Type              | Units       |

| 1                    | float                  | henrys      |

| Element<br>Parameter | Data Type | Units |

|----------------------|-----------|-------|

| ic                   | string    |       |

#### **Transmission Line**

#### HSPICE/SPICE Element: Transmission Line Element Name: T Used by Library Cell: *tline*

| Terminal Name | Level of<br>Simulation | Direction   |

|---------------|------------------------|-------------|

| N1            | Circuit                | inputOutput |

| N2            | Circuit                | inputOutput |

| N3            | Circuit                | inputOutput |

| N4            | Circuit                | inputOutput |

| Element<br>Parameter | Data Type | Units    |

|----------------------|-----------|----------|

| z0                   | float     | ohms     |

| td                   | float     | seconds  |

| f                    | float     | hertz    |

| nl                   | float     | unitless |

| ic                   | string    |          |

#### Diode

#### HSPICE/SPICE Element: Diode Element Name: D Model Type: D Used by Library Cell: diode

| Terminal Name | Level of<br>Simulation | Direction   |

|---------------|------------------------|-------------|

| PLUS          | Circuit                | inputOutput |

| MINUS         | Circuit                | inputOutput |

| Element Parameter | Data Type | Units    |

|-------------------|-----------|----------|

| area              | float     | unitless |

| off               | string    | "off"    |

| ic                | string    |          |

| Model Parameter | Data Type | Units         |

|-----------------|-----------|---------------|

| is              | float     | amperes       |

| rs              | float     | ohms          |

| n               | float     | unitless      |

| tt              | float     | seconds       |

| cjo             | float     | farads        |

| vj              | float     | volts         |

| m               | float     | unitless      |

| eg              | float     | electronvolts |

| xti             | float     | unitless      |

| kf              | float     | unitless      |

| af              | float     | unitless      |

| fc              | float     | unitless      |

| ibv             | float     | amperes       |

|                 |           |               |

| Model Parameter | Data Type | Units |

|-----------------|-----------|-------|

| bv              | float     | volts |

#### BJT

| HSPICE/SPICE Elem<br>Element Name: Q<br>Model Type: NPN, PI<br>Used by Library Cell | NP                  | pnps        |

|-------------------------------------------------------------------------------------|---------------------|-------------|

| Terminal Name                                                                       | Level of Simulation | n Direction |

| С                                                                                   | Circuit             | inputOutput |

| В                                                                                   | Circuit             | inputOutput |

| E                                                                                   | Circuit             | inputOutput |

| SUB                                                                                 | Circuit             | inputOutput |

|                                                                                     |                     |             |

| Element Parameter                                                                   | Data Type           | Units       |

| area                                                                                | float               | unitless    |

| off                                                                                 | string              | "off"       |

| ic                                                                                  | string              |             |

|                                                                                     |                     |             |

| Model Parameter                                                                     | Data Type           | Units       |

| is                                                                                  | float               | amperes     |

| bf                                                                                  | float               | unitless    |

| nf                                                                                  | float               | unitless    |

| ise                                                                                 | float               | amperes     |

|                                                                                     | <b>a</b> .          |             |

float

float

float

float

ne

br

nr

isc

unitless

unitless

unitless

amperes

| Model Parameter | Data Type | Units         |

|-----------------|-----------|---------------|

| nc              | float     | unitless      |

| rb              | float     | ohms          |

| rbm             | float     | ohms          |

| re              | float     | ohms          |

| rc              | float     | ohms          |

| cje             | float     | farads        |

| vje             | float     | volts         |

| mje             | float     | unitless      |

| tf              | float     | seconds       |

| xtf             | float     | unitless      |

| itf             | float     | amperes       |

| ptf             | float     | degrees       |

| cjc             | float     | farads        |

| vjc             | float     | volts         |

| mjc             | float     | unitless      |

| xcjc            | float     | unitless      |

| tr              | float     | seconds       |

| cjs             | float     | farads        |

| vjs             | float     | volts         |

| mjs             | float     | unitless      |

| xtb             | float     | unitless      |

| eg              | float     | electronvolts |

| xti             | float     | unitless      |

| kf              | float     | unitless      |

| af              | float     | unitless      |

| fc              | float     | unitless      |

| vtf             | float     | volts         |

|                 |           |               |

| Model Parameter | Data Type | Units   |

|-----------------|-----------|---------|

| irb             | float     | amperes |

| ikr             | float     | amperes |

| var             | float     | volts   |

| vaf             | float     | volts   |

| ikf             | float     | amperes |

#### JFET

#### HSPICE/SPICE Element: JFET Element Name: J Model Type: NJF, PJF Used by Libary Cells*: njfet, pjfet*

| Terminal Name | Level of Simulation | Direction   |

|---------------|---------------------|-------------|

| D             | Circuit             | inputOutput |

| G             | Circuit             | inputOutput |

| S             | Circuit             | inputOutput |

| Element<br>Parameter | Data Type | Units    |

|----------------------|-----------|----------|

| area                 | float     | unitless |

| off                  | string    | "off"    |

| ic                   | string    |          |

| Model Parameter | Data Type | Units                |

|-----------------|-----------|----------------------|

| vto             | float     | volts                |

| beta            | float     | amperes/square volts |

| lambda          | float     | 1/volts              |

| rd              | float     | ohms                 |

| rs              | float     | ohms                 |

| Model Parameter | Data Type | Units    |

|-----------------|-----------|----------|

| cgs             | float     | farads   |

| cgd             | float     | farads   |

| pb              | float     | volts    |

| is              | float     | amperes  |

| kf              | float     | unitless |

| af              | float     | unitless |

| fc              | float     | unitless |

#### MOSFET

#### HSPICE/SPICE Element: MOSFET Element Name: M Model Type: NMOS, PMOS Used by Library Cells: ndepl, nfet, nmos, mosd, nmose, nsftn, nxfr, pdepl, pfet, pmos, pmos, pmose, psftn, pxfr

| Terminal Name | Level of Simulation | Direction   |

|---------------|---------------------|-------------|

| D             | Circuit             | inputOutput |

| G             | Circuit             | inputOutput |

| S             | Circuit             | inputOutput |

| В             | Circuit             | inputOutput |

|               |                     |             |

| Element<br>Parameter | Data Type | Units         |

|----------------------|-----------|---------------|

|                      | float     | meters        |

| W                    | float     | meters        |

| ad                   | float     | square meters |

| as                   | float     | square meters |

| pd                   | float     | meters        |

| ps                   | float     | meters        |

| Element<br>Parameter | Data Type | Units    |

|----------------------|-----------|----------|

| nrd                  | float     | unitless |

| nrs                  | float     | unitless |

| off                  | string    | "off"    |

| ic                   | string    |          |

| Model<br>Parameter | Data Type | Units                 |

|--------------------|-----------|-----------------------|

| level              | integer   | unitless              |

| vto                | float     | volts                 |

| kp                 | float     | amperes/volts squared |

| gamma              | float     | volts**0.5            |

| phi                | float     | volts                 |

| lambda             | float     | 1/volts               |

| rd                 | float     | ohms                  |

| rs                 | float     | ohms                  |

| cbd                | float     | farads                |

| cbs                | float     | farads                |

| is                 | float     | amperes               |

| pb                 | float     | volts                 |

| cgso               | float     | farads/meter          |

| cgdo               | float     | farads/meter          |

| cgbo               | float     | farads/meter          |

| rsh                | float     | ohms/square           |

| сј                 | float     | farads/square meter   |

| mj                 | float     | unitless              |

| cjsw               | float     | farads/meter          |

| mjsw               | float     | unitless              |

| Model<br>Parameter | Data Type | Units                           |

|--------------------|-----------|---------------------------------|

| js                 | float     | amperes/square meter            |

| tox                | float     | meters                          |

| nsub               | float     | 1/cubic centimeters             |

| nss                | float     | 1/square centimeters            |

| nfs                | float     | 1/square centimeters            |

| tpg                | integer   | unitless                        |

| xj                 | float     | meters                          |

| ld                 | float     | meters                          |

| uo                 | float     | square centimeters/volt seconds |

| ucrit              | float     | volts/centimeter                |

| uexp               | float     | unitless                        |

| utra               | float     | unitless                        |

| vmax               | float     | meters/second                   |

| neff               | float     | unitless                        |

| xqc                | float     | unitless                        |

| kf                 | float     | unitless                        |

| af                 | float     | unitless                        |

| fc                 | float     | unitless                        |

| delta              | float     | unitless                        |

| theta              | float     | 1/volts                         |

| eta                | float     | unitless                        |

| kappa              | float     | unitless                        |

## **Formatting Functions**

This section describes the formatting functions included with the HSPICE/SPICE interface. The cells in the *sample* library that use these formatting functions are also listed. The syntax for these formatting functions is that of the *nlpglobal* functions, but the same parameters are also defined in the *hspice* formatter for hierarchical netlisting.

This section uses the following notations:

| <>    | name in the brackets is an identifier                        |

|-------|--------------------------------------------------------------|

| {}    | item(s) in braces can be repeated as many times as necessary |

| []    | item(s) in brackets are optional                             |

| @name | value of property name is substituted                        |

## **Element Formats**

Below is the list of HSPICE/SPICE elements and their formats:

#### res

r<name> <A> <Y> @r @ns @tc1 @tc2 @scale @rsh ac=@ac m=@m

The res cell in the sample library uses this format.

#### resistor

r<name> <PLUS> <MINUS> @r @ns @tc1 @tc2 @scale @rsh ac=@ac m=@m

The *resistor* cell in the *sample* library uses this format.

#### сар

c<name> <Y> gnd! @c @ns @tc1 @tc2 @scale @cj ic=@ic m=@m

The cap cell in the sample library uses this format.

### capacitor

c<name> <PLUS> <MINUS> @c @ns @tc1 @tc2 @scale @cj ic=@ic m=@m

The capacitor and pcapacitor cells in the sample library use this format.

#### inductor

l<name> <PLUS> <MINUS> @l @tc1 @tc2 @nt ic=@ic

The *inductor* cell in the *sample* library uses this format.

#### transmission line

t<name> <N1> <N2> <N3> <N4> z0=@z0 td=@td f=@f n1=@n1 ic=@ic

The *tline* cell in the *sample* library uses this format.

#### diode

```

d<name> <PLUS> <MINUS> <cellName> w=@w l=@l area=@area pj=@pj wp=@wp

lp=@lp wm=@wm lm=@lm @off ic=@ic m=@m

```

The *diode* and *pdiode* cells in the *sample* library use this format.

#### BJT

```

q<name> <C> <B> <E> <SUB> <cellName> area=@area @off ic=@ic m=@m

```

The *npns* and *pnps* cells in the *sample* library use this format.

#### JFET

j<name> <D> <G> <S> <cellName> area=@area w=@w l=@l @off ic=@ic m=@m

The *njfet* and *pjfet* cells in the *sample* library use this format.

### MOSfet

The ndepl, nfet, nsftn, pdepl, pfet, and psftn cells in the sample library use this format.

### NMOSfet

The *nxfr, nmos, nmosd,* and *nmose* cells in the *sample* library use this format.

### NPN

q<name> <C> <B> <E> vee! <cellName> area=@area off" off ic=@ic m=@m

The *npn* cell in the *sample* library uses this format.

#### **PMOSfet**

"m<name> <D> <G> <S> vdd! <cellName> w=@w l=@l ad=@ad as=@as pd=@pd ps=@ps nrd=@nrd

nrs=@nrs off" off ic=@ic m=@m

The *pxfr, pmos, pmosd,* and *pmose* cells in the *sample* library use this format.

#### PNP

```

"q<name> <C> <B> <E> vcc! <cellName> @area off" off ic=@ic m=@m

```

The pnp cell in the sample library uses this format.

## **Model Format**

Below is the list of HSPICE/SPICE models and their model card format.

#### Diode

```

.model <cellName> d level=@level area=@area eg=@eg is=@is jsw=@jsw n=@n pj=@pj

tlev=@tlev xti=@xti ibv=@ibv tcv=@tcv vb=@vb af=@af kf=@kf rs=@rs trs=@trs

cjo=@cjo cjp=@cjp cta=@cta ctp=@ctp fc=@fc fcs=@fcs m=@m mjsw=@mjsw pb=@pb

php=@php tt=@tt ef=@ef er=@er jf=@jf jr=@jr w=@w l=@l tox=@tox wm=@wm lm=@lm

wp=@wp lp=@lp xm=@xm xp=@xp xoi=@xoi xom=@xom

```

The *diode* and *pdiode* cells in the *sample* library use this format.

### BJT

.model <cellName> @modelType bf=@bf br=@br bulk=@bulk eg=@eg is=@is iss=@iss nf=@nf nr=@nr subs=@subs isc=@isc ise=@ise nc=@nc ne=@ne vaf=@vaf var=@var ikf=@ikf ikr=@ikr irb=@irb rb=@rb rbm=@rbm re=@re rc=@rc cjc=@cjc cje=@cje cjs=@cjs fc=@fc mjc=@mjc mje=@mje mjs=@mjs vjc=@vjc vje=@vje vjs=@vjs xcjc=@xcjc itf=@itf ptf=@ptf tf=@tf tr=@tr vtf=@vtf xtf=@xtf tlev=@tlev tre1=@tre1 tre2=@tre2 trb1=@trb1 trb2=@trb2 trc1=@trc1 trc2=@trc2 trm1=@trm1 trm2=@trm2 xtb=@xtb xti=@xti af=@af kf=@kf

The npn, npns, pnp, and pnps cells in the sample library use this format.

### JFET

.model <cellName> @modelType level=%s" level a=@a alpha=@alpha beta=@beta d=@d gamds=@gamds lambda=@lambda w=@w l=@l wdel=@wdel ldel=@ldel tcv=@tcv vto=@vto eg=@eg gapl=@gapl gap2=@gap2 is=@is n=@n ni=@ni xti=@xti af=@af kf=@kf rd=@rd rg=@rg rs=@rs trd=@trd trg=@trg trs=@trs cgd=@cgd cgs=@cgs fc=@fc m=@m pb=@pb capop=@capop ctd=@ctd cts=@cts tt=@tt bex=@bex lam1=@lam1 nchan=@nchan sat=@sat ucrit=@ucrit vbi=@vbi vgexp=@vgexp vp=@vp tlev=@tlev tlevc=@tlevc tpb=@tpb

The *njfet* and *pjfet* cells in the *sample* library use this format.

### MOSfet

.model<cellName> @modelType level=@level vto=@vto nss=@nss tpg=@tpg phi=@phi

gamma=@gamma nsub=@nsub bulk=@bulk bex=@bex kp=@kp lambda=@lambda

ecrit=@ecrit neff=@neff nfs=@nfs ucrit=@ucrit uexp=@uexp uo=@uo utra=@utra

vmax=@vmax xj=@xj ld=@ld theta=@theta clm=@clm dns=@dns fds=@fds mbl=@mbl

mob=@mob nu=@nu nwe=@nwe nwm=@nwm scm=@scm tcv=@tcv ufds=@ufds vbo=@vbo

vfds=@vfds vsh=@vsh wic=@wic fl=@fl mob=@mob af=@af kf=@kf cgbo=@cgbo

cgdo=@cgdo cgso=@cgso cox=@cox meto=@meto tox=@tox wd=@wd capop=@capop

cfl=@cfl cf2=@cf2 cf3=@cf3 cf4=@cf4 cf5=@cf5 cf6=@cf6 alpha=@alpha is=@is

js=@js jsw=@jsw vcr=@vcr cbd=@cbd cbs=@cbs cj=@cj cjsw=@cjsw mj=@mj

mjsw=@mjsw pb=@pb php=@php ldif=@ldif rd=@rd rs=@rs rsh=@rsh trd=@trd

trs=@trs delta=@delta kappa=@kappa eta=@eta

The *ndepl, nfet, nmos, nmosd, nmose, nsftn, nxfr, pdepl, pfet, pmos, pmosd, pmose, psftn,* and *pxfr* cells in the *sample* library use this format.

# Using SPICE

This chapter contains the following topics:

- Introduction

- <u>Types of Analysis</u>

- <u>Convergence</u>

- Input Format

- <u>Circuit Description</u>

- Title Card, Comment Cards, and .END Card

- Element Cards for Passive Circuit Elements and Sources

- Semiconductor Devices

- Element Cards for Semiconductor Devices

- MODEL Cards for Semiconductor Devices

- <u>Subcircuits</u>

- Control Cards

- Example of Data Decks

- Nonlinear Dependent Sources

- <u>Bipolar Model Equations (Gmin terms omitted)</u>

- Alter Statement and the Source-Stepping Method

- References

## Introduction

SPICE is a general-purpose circuit simulation program for nonlinear DC, nonlinear transient, and linear AC analyses. Circuits may contain resistors, capacitors, inductors, mutual inductors, independent voltage and current sources, four types of dependent sources, transmission lines, and the four most common semiconductor devices: diodes, BJTs, JFETs, and MOSFETs.

SPICE has built-in models for the semiconductor devices, and the user need specify only the pertinent model parameter values. The model for the BJT is based on the integral charge model of Gummel and Poon; however, if the Gummel-Poon parameters are not specified, the model reduces to the simpler Ebers-Moll model. In either case, charge storage effects, ohmic resistances, and a current-dependent output conductance may be included.

The diode model can be used for either junction diodes or Schottky barrier diodes. The JFET model is based on the FET model of Shichman and Hodges. Three MOSFET models are implemented: MOS1 is described by a square-law I-V characteristic, MOS2 is an analytical model, while MOS3 is a semi-empirical model. Both MOS2 and MOS3 include second-order effects such as channel length modulation, subthreshold conduction, scattering limited velocity saturation, small-size effects and charge-controlled capacitances.

## **Types of Analysis**

## **DC Analysis**

The DC analysis portion of SPICE determines the dc operating point of the circuit with inductors shorted and capacitors opened. A DC analysis is automatically performed prior to a transient analysis to determine the transient initial conditions and prior to an AC small-signal analysis to determine the linearized, small-signal models for nonlinear devices. If requested, the DC small-signal value of a transfer function (ratio of output variable to input source), input resistance, and output resistance will also be computed as a part of the DC solution. The DC analysis can also be used to generate DC transfer curves: a specifie DC output variables are stored for each sequential source value. If requested, SPICE also will determine the DC small-signal sensitivities of specified output variables with respect to circuit parameters. The DC analysis options are specified on the .DC, .TF, .OP, and .SENS control cards.

To see the small-signal models for nonlinear devices in conjunction with a transient analysis operating point, the .OP card must be provided. The DC bias conditions will be identical for each case, but the more comprehensive operating point information is not available to be printed when transient initial conditions are computed.

## AC Small-Signal Analysis

The AC small-signal portion of SPICE computes the AC output variables as a function of frequency. The program first computes the DC operating point of the circuit and determines linearized, small-signal models for all of the nonlinear devices in the circuit. The resultant linear circuit is then analyzed over a user-specified range of frequencies. The desired output of an AC small-signal analysis is usually a transfer function (voltage gain, transimpedance, etc.). If the circuit has only one AC input, it is convenient to set that input to unity and zero phase so that output variables have the same value as the transfer function of the output variable with respect to the input.

The generation of white noise by resistors and semiconductor devices can also be simulated with the AC small-signal portion of SPICE. Equivalent noise source values are determined automatically from the small-signal operating point of the circuit, and the contribution of each noise source is added at a given summing point. The total output noise level and the equivalent input noise level are determined at each frequency point. The output and input noise levels are normalized with respect to the square root of the noise bandwidth and have the units Volts/rt Hz or Amps/rt Hz. The output noise and equivalent input noise can be printed or plotted in the same fashion as other output variables. No additional input data is necessary for this analysis.

Flicker noise sources can be simulated in the noise analysis by including values for the parameters KF and AF on the appropriate device model cards.

The distortion characteristics of a circuit in the small-signal mode can be simulated as a part of the AC small-signal analysis. The analysis is performed assuming that one or two signal frequencies are imposed at the input.

The frequency range and the noise and distortion analysis parameters are specified on the .AC, .NOISE, and .DISTO control lines.

## **Transient Analysis**

The transient analysis portion of SPICE computes the transient output variables as a function of time over a user-specified time interval. The initial conditions are automatically determined by a dc analysis. All sources that are not time dependent (for example, power supplies) are set to their DC value. For large-signal sinusoidal simulations, a Fourier analysis of the output waveform can be specified to obtain the frequency domain Fourier coefficients. The transient time interval and the Fourier analysis options are specified on the .TRAN and .FOURIER control lines.

## Analysis at Different Temperatures

All input data for SPICE is assumed to have been measured at 27 °*C* (300 K). The simulation also assumes a nominal temperature of 27 °*C*. The circuit can be simulated at other temperatures by using a .TEMP control line.

Temperature appears explicitly in the exponential terms of the BJT and diode model equations. In addition, saturation currents have a built-in temperature dependence. The temperature dependence of the saturation current in the BJT models is determined by

$IS(T1) = IS(T0)^{(T1/T0^{*}XTI)} \exp(q^{EG^{*}(T1-T0)/(k^{T1}^{T0}))$

where k is Boltzmann's constant; q is the electronic charge;EG is the energy gap, which is a model parameter; and XTI is the saturation current temperature exponent (also a model parameter, and usually equal to 3). The temperature dependence of forward and reverse beta is according to the formula

beta(T1)=beta(T0)\*(T1/T0)\*\*XTB

where T1 and T0 are in degrees Kelvin and XTB is a user-supplied model parameter. Temperature effects on beta are carried out by appropriate adjustment to the values of BF, ISE, BR, and ISC. Temperature dependence of the saturation current in the junction diode model is determined by

$IS(T1) = IS(T0)^{(T1/T0)^{*}(XTI/N)} \exp(q^{EG^{T1-T0}/(k^{N}T1^{T0}))$

where N is the emission coefficient, which is a model parameter, and the other symbols have the same meaning as above.

**Note:** For Schottky barrier diodes, the value of the saturation current temperature exponent, XTI, is usually 2.

Temperature appears explicitly in the value of junction potential, PHI, for all the device models. The temperature dependence is determined by

PHI(TEMP) = k\*TEMP/q\*log(Na\*Nd/Ni(TEMP)\*\*2)

where k is Boltzmann's constant, q is the electronic charge, Na is the acceptor impurity density, Nd is the donor impurity density, Ni is the intrinsic concentration, and EG is the energy gap.

Temperature appears explicitly in the value of surface mobility, UO, for the MOSFET model. The temperature dependence is determined by  $UO(TEMP) = UO(TNOM)/(TEMP/TNOM)^{**}(1.5)$

The effects of temperature on resistors is modeled by the formula

value(TEMP) = value(TNOM)\*(1+TC1\*(TEMP-TNOM)+TC2\*(TEMP-TNOM) \*\*2))

where TEMP is the circuit temperature, TNOM is the nominal temperature, and TC1 and TC2 are the first- and second-order temperature coefficients.

## Convergence

Both DC and transient solutions are obtained by an iterative process, which is terminated when both of the following conditions hold:

- 1. The non linear branch currents converge to within a tolerance of 0.1 percent or 1 picoamp (1.0E-12 Amp), whichever is larger.

- 2. The node voltages converge to within a tolerance of 0.1 percent or 1 microvolt (1.0E-6 Volt), whichever is larger.

Although the algorithm used in SPICE has been found to be very reliable, in some cases it will fail to converge to a solution. When this failure occurs, the program will print the node voltages at the last iteration and terminate the job. In such cases, the node voltages that are printed are not necessarily correct or even close to the correct solution.

Failure to converge in the DC analysis is usually due to an error in specifying circuit connections, element values, or model parameter values. Regenerative switching circuits or circuits with positive feedback probably will not converge in the DC analysis unless the OFF option is used for some of the devices in the feedback path, or the .NODESET card is used to force the circuit to converge to the desired state.

## Input Format