# Exercise 2.1: Creating a LabVIEW FPGA VI

### **Exercise Objective**

This exercise will introduce you to basic concepts and methods of programming LabVIEW FPGA. You will create an application from scratch that shows many of the basic features of LabVIEW FPGA and R Series. This application will also show the parallelism of a LabVIEW FPGA system.

### Hands-On Summary

- Introduce LabVIEW FPGA

- Learn how to setup and configure a R Series device using the LabVIEW Project

- Create an FPGA Application that adds two numbers and benchmarks the execution.

### Hardware Setup

## Part 0: Configuring the R Series Device in MAX

In this section you will learn the following:

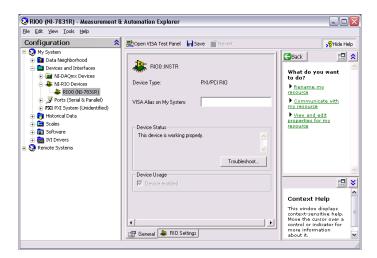

• Discovering a R Series in Measurement and Automation Explorer (MAX)

1. Confirm that your RIO device shows up in MAX. Since we will be running the R Series on the windows machine, no further configuration is required to access the device from LabVIEW.

# Part 1: Developing the FPGA Application

In this section you will learn:

- Develop, target, download, and run an application on an FPGA.

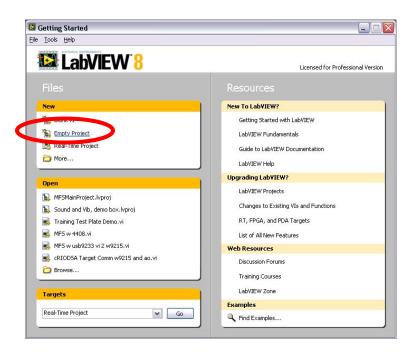

- 1. Launch LabVIEW 8 and open an Empty Project.

2. Click the **Save All** button and save your project as Custom Trigger to the "Intro Demo" folder located on the desktop. Your project should look like this:

| 🛃 P  | rojec        | t Exp    | lorer - (   | Custom T    | rigge | r.lvproj |      | _ 🗆 🗙    |

|------|--------------|----------|-------------|-------------|-------|----------|------|----------|

| Eile | <u>E</u> dit | ⊻iew     | Project     | Operate     | Tools | ₩indow   | Help |          |

| ]  * | 16           | Ø        | χ 🗈         | 🗅 X         | 5     | H        | • 🚰  | ]] 🐉 🎯 👔 |

| B- 1 | 🔒 Pr         | oject: 🤇 | Lustom Tr   | igger.lvpro | j     |          |      |          |

| 6    | b 💂          | My Co    | mputer      |             |       |          |      |          |

|      | ļ            | 🏆 De     | pendenci    | es          |       |          |      |          |

|      | L. 1         | 🍝 Bu     | ild Specifi | cations     |       |          |      |          |

|      |              | _        |             |             |       |          |      |          |

|      |              |          |             |             |       |          |      |          |

|      |              |          |             |             |       |          |      |          |

|      |              |          |             |             |       |          |      |          |

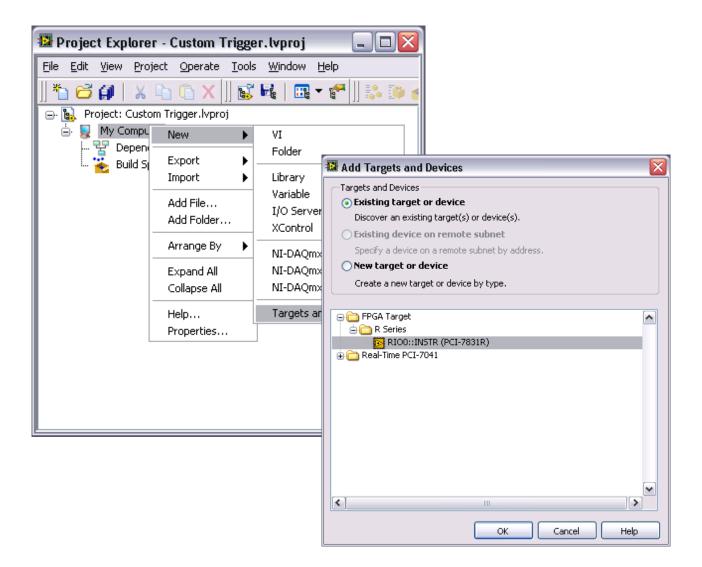

3. **Right-click on My Computer** and select **New>>Targets and Devices**. This will allow us to add an FPGA target to our project. Expand the FPGA Target folder, highlight the PCI-7831R device and select OK.

4. The LabVIEW Project should look like this:

Replace this with new figure

- 5. Developing the LabVIEW FPGA Application

- In this section you will:

- Explore the function palettes while targeted for FPGA.

- Design an application that adds two numbers and benchmarks the code

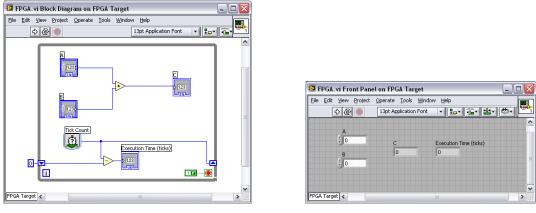

The completed application should look like this:

Block Diagram

Front Panel

6. In the LabVIEW Project Window, right-click on the FPGA target (PCI-7831R) and select New>>VI to start a new LabVIEW FPGA VI (LabVIEW programs are called Virtual Instruments or VI's). Save this VI as AddFPGA.vi by (File>>Save As) to signify that this program will be run on the FPGA.

| Project Explorer - Custom Trigger.lvpro File Edit View Project Operate Tools Windon      ** Constraints of the tools of too | ₩ Help<br>B - 2 <sup>4</sup>    33 (9 d                                                                                                              |                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| PRATarget (R100::INSR, PCI-783     R3     AM 45 Observed Clock     Iffer Expansion Chassis (Connector 1)     N19215 (Sick 1)     N19215 (Sick 2)     N19411 (Sick 3)     N19411 (Sick 3)     N19474 (Sick 4)     Dependencies     Build Specifications     Build Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | New Reset Download Bitfile or Attributes To Flash Memory Add File Add File Add File Arrange By Expand All Collapse All Remove Rename Help Properties | VI     Folder     Library     XControl     R Series Expansion Chassis     FPGA I/O     FPGA Base Clock     FIFO |

New VI

- 7. When the LabVIEW front panel appears, go to the block diagram by selecting **Window>>Show block diagram**.

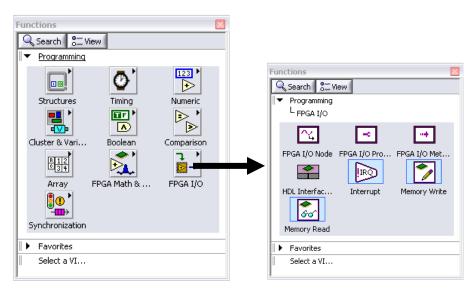

- 8. Right-click in the white area on the block diagram to display the **Functions** palette. Click on the thumb tack icon in the top left corner of the **Functions** palette to tack it down.

FunctionsPallete here

9. Navigate to the **Help** menu and select **Show context help**. Then browse through the **Functions** palette to familiarize yourself with the many math, digital logic, comparison, input/output, math and analysis functions and IP libraries that are available.

Browsing the LabVIEW FPGA functions palette

10. Go back to the LabVIEW front panel (gray screen), go to View >> Controls Palette. This will turn the controls Palette ON

| 🔛 A  | ddFPG        | A.vi Front Panel on FPG                                                                                    | A Targ        | et *                   |                                                |              |

|------|--------------|------------------------------------------------------------------------------------------------------------|---------------|------------------------|------------------------------------------------|--------------|

| Eile | <u>E</u> dit | View Project Operate                                                                                       | <u>T</u> ools | <u>W</u> indow         | Help                                           |              |

|      | [            | <u>C</u> ontrols Palette                                                                                   |               |                        | ■ <u>1</u> 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ₩ <b>₽</b> 3 |

|      |              | Eunctions Palette<br>Tools Palette                                                                         |               |                        |                                                | <b>^</b>     |

|      |              | Error List<br>VI Hierarchy<br>Browse Relationships                                                         | Ctrl          | l+L                    | •                                              |              |

|      |              | Cl <u>a</u> ss Browser<br><u>G</u> etting Started Window<br><u>N</u> avigation Window<br>T <u>o</u> olbars | v             | l+Shift+B<br>l+Shift+N | • • • • • • • • • • • • • • • • • • •          |              |

|      |              |                                                                                                            |               |                        |                                                |              |

| FPGA | Targe        | Ē                                                                                                          |               |                        |                                                | -            |

| Controls          |             | ×                    |

|-------------------|-------------|----------------------|

| 🔍 Search 🛛 👫 Vie  | w           |                      |

| ll▼ <u>Modern</u> |             |                      |

| 123               | 80          | :12 ►<br>34<br>[*] ■ |

| Numeric           | Boolean     | Array & Cluster      |

|                   |             | Ring ▼ ►<br>Enum     |

| List & Table      | Graph       | Ring & Enum          |

|                   |             |                      |

| Containers        | Decorations |                      |

| I ► System        |             |                      |

| ↓ Classic         |             |                      |

| Select a Contro   | l           |                      |

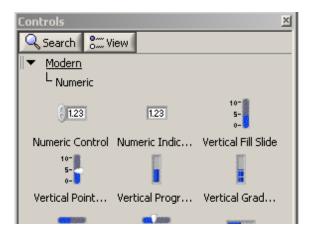

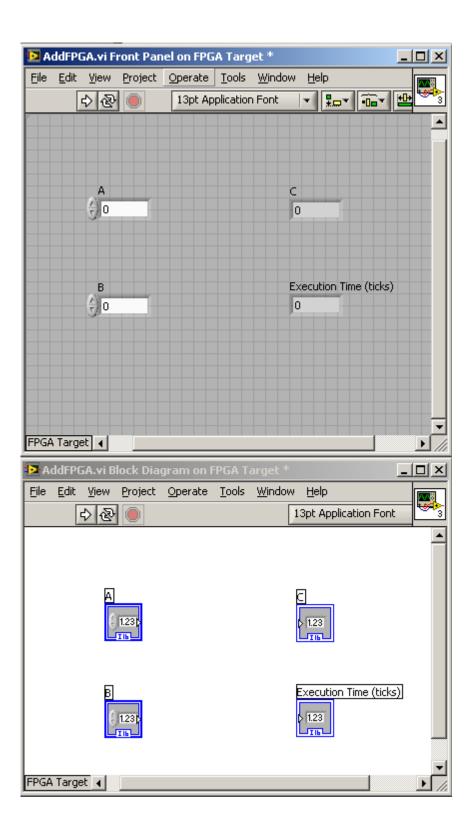

11. From Controls Palette press "Numeric" button which will envoke Numeric Palette. Now place two numeric controls and two numeric indicator in the front panel. You can always go back a level by clicking the upper level in the top left corner (Modern).

12. In "Front Panel" rename the controls **A** and **B**, and the indicators as **C** and **Execution Time** (ticks). It is easier to name the component while placing. To rename right click in the middle of the controls and then click "Properties" and change the name in properties (it is faster to Delete and place them again and name while placing). The Front Panel and Block Diagrams should look like this now.

13. Change their data type to be an Unsigned Byte integer, by right-clicking on each of them and selecting **Representation** » **Unsigned Byte** from the shortcut menu. Notice U8 in at the bottom of each icon in Block Diagram (it was I16 initially).

| Visible Items<br>Find Indicator                                                  |                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hide Indicator<br>Change to Control<br>Change to Constant<br>Description and Tip |                                                                                                                                                                                                                |

| Numeric Palette                                                                  |                                                                                                                                                                                                                |

| Create                                                                           |                                                                                                                                                                                                                |

| Data Operations                                                                  |                                                                                                                                                                                                                |

| Advanced )                                                                       | _                                                                                                                                                                                                              |

| Representation )                                                                 | Unsigned Byte                                                                                                                                                                                                  |

|                                                                                  |                                                                                                                                                                                                                |

| ✓ View As Icon                                                                   | ?                                                                                                                                                                                                              |

| ✓ View As Icon<br>Properties                                                     |                                                                                                                                                                                                                |

|                                                                                  | ?                                                                                                                                                                                                              |

|                                                                                  | ?<br>EXT DBL SGL                                                                                                                                                                                               |

|                                                                                  | ?           EXT         DBL         SGL           Image: SGL         Image: SGL         Image: SGL           Image: SGL         Image: SGL         Image: SGL           I64         I32         I16         I8 |

14. In the block diagram, add a while loop around the four controls. Tis is done by right clicking and then in Functions >> Structures >> While Loop (as shown in screen shot below), make sure the terminals for the controls and indicator are inside the While loop.

| ľ | 100 A        | ddFP0        | GA.vi Bi         | lock Dia  | igram on F                                                                                                  | PGA T         | arget *        | ·                           | _       |   |

|---|--------------|--------------|------------------|-----------|-------------------------------------------------------------------------------------------------------------|---------------|----------------|-----------------------------|---------|---|

|   | <u>F</u> ile | <u>E</u> dit | ⊻iew             | Project   | <u>O</u> perate                                                                                             | <u>T</u> ools | <u>W</u> indow | <u>H</u> elp                |         |   |

|   |              |              | \$ @             |           |                                                                                                             |               | 1              | 3pt Applicati               | on Font | 3 |

|   |              | A<br>1.23    |                  |           |                                                                                                             |               | 1.23<br>08     |                             |         | • |

| 1 | [            | µ            | Functior         | าร        |                                                                                                             |               | Q Searc        | th L                        |         |   |

| 1 |              | Prog         | ramming          | ;         |                                                                                                             |               |                | <ul> <li>(ticks)</li> </ul> |         |   |

| I |              |              |                  | ]         | ₩,                                                                                                          |               | 123            |                             |         |   |

|   |              | -            |                  |           | <b>⊨</b> 0Structure                                                                                         |               |                |                             |         |   |

|   |              | 51           | tructure         | is        | p h                                                                                                         | V             | Vhile Loop     |                             | •       |   |

|   |              |              |                  |           | ▣┛                                                                                                          |               |                | <b>.</b>                    |         |   |

|   |              | Clus         | ter & Va         | ari       | For Loop                                                                                                    | Ŵ             | /hile Loop     | Timed Str                   | ructu   |   |

|   |              |              | R12<br>034       |           | 89 <u>400</u> 988<br>9<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8<br>8 |               |                |                             |         |   |

|   |              |              | Array            |           | ase Structur                                                                                                | e             |                |                             |         |   |

|   |              |              | <mark>∎</mark> • |           |                                                                                                             |               |                |                             |         |   |

|   |              | Sync         | hroniza          | ition Fla | at Sequenc.                                                                                                 | Stad          | iked Sequ.     | Diagram                     | Disa    |   |

|   |              | Favo         |                  |           |                                                                                                             |               | LOCAL          | GLC                         | в       |   |

|   |              | Selec        | taVI             |           | nditional Di                                                                                                | Lo            | cal Variable   | e Global V                  | ariable |   |

|   |              |              |                  |           |                                                                                                             |               |                | Œ                           | 3       |   |

| 1 |              |              |                  | 1         | Decorations                                                                                                 |               |                | Feedbac                     | k Node  | • |

|   | FPGA         | A Targe      | et 🔺             |           |                                                                                                             |               |                |                             |         |   |

- 15. Place the **Add** function (Functions>>Numeric) inside the while loop.

- 16. If you do not have the Tools Palette visible, turn ON Tools Palette from View>>Tools Palette. In Tools click on "Wire Reel" button and wire A and B to the inputs of the add function and wire C to the add function output. Wiring may feel tricky and may require some practice.

| A 🛃  | ddFP | GA.vi B                      | lock Dia | gram on I  | PGA T | arget * | ·                           |          |

|------|------|------------------------------|----------|------------|-------|---------|-----------------------------|----------|

| Eile | Edit |                              |          | Operate    |       |         |                             |          |

|      |      | <b>₽</b>                     |          |            |       |         | 13pt Application Font       | <b>•</b> |

|      | ſ    | A<br>( 1.23)<br>B<br>( 1.23) |          | <b>↓</b> → |       |         | 23<br>secution Time (ticks) |          |

| FPGA | Tarq |                              |          |            | _     | _       |                             |          |

A common use of parallelism in LabVIEW FPGA is for benchmarking purposes. Since LabVIEW FPGA implements independent tasks in parallel, we can easily add benchmarking code in parallel to our main application without effecting the performance.

- 17. Right click on the left edge of the While Loop and select Add Shift Register.

- Initialize the shift register by dropping down a numeric constant of zero from the Numeric Palette (which is accessible from the Functions Palette Functions>>Numeric>>Numeric Constant).

| 😫 AddFPGA.vi Block Di                          | Functions      |                        | ×                | 민지          |

|------------------------------------------------|----------------|------------------------|------------------|-------------|

| <u>File E</u> dit <u>V</u> iew <u>P</u> roject | 🔍 Search 🛛 👫 V | iew                    |                  | ·····       |

| 🔹 🕑 🥘                                          | Programming    |                        |                  | 3           |

|                                                |                |                        |                  |             |

| 8                                              | ⊳              | $\triangleright$       | $\triangleright$ |             |

| 1.230                                          | Add            | Subtract               | Multiply         |             |

|                                                | ÷R<br>IQ       | ] <u>132</u> )<br>]DBL | ₽>               |             |

|                                                | Quotient & R   | Conversion             | Increment        |             |

| B                                              |                |                        | ₽123             |             |

|                                                | Decrement      | Compound Ar            | Saturation Ari   |             |

|                                                |                | Ð                      | ×2               |             |

|                                                | Absolute Value | Negate                 | Scale By Pow     |             |

|                                                | Io             |                        | 123              |             |

|                                                | Sign           | Data Manipul           | Numeric Cons     |             |

|                                                | + Enum         | Ring                   |                  |             |

| TDCA Township of                               | Enum Constant  | Ring Constant          |                  | -           |

| FPGA Target                                    | I ► Favorites  |                        |                  | <u>Þ</u> // |

19. Now, drop down a **Tick Count** function (**Functions>>Timing**), select the counter units to be **Ticks** and keep the size of the internal counter as 32 Bit. **Click OK.**

| 🔁 Configure Tick Count   | × |

|--------------------------|---|

| Counter Units            |   |

| Ticks                    |   |

| Size of Internal Counter |   |

| 32 Bit                   |   |

| ,                        |   |

| OK Cancel Help           |   |

|                          |   |

Configure Tick Count Dialog

- 20. Wire the output of the Tick Count function to the shift register on the right side of the While Loop

- 21. Drop down a **Subtract** function on to the block diagram.

- 22. Wire the output of the shift register on the left side of the While Loop and the value of the **Tick Count** function to one inputs of the Subtract function. Wire the output of the Subtract function to the indicator labeled **Execution Time (ticks**).

- 23. Save the VI and project. Click the **Run button** to start the compile process. The following window will appear:

| Warning                                                               |                                                                                                               |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                                                       | et can take minutes to hours. Click the OK button to<br>prinected from a compile and want to reconnect, click |

| In the future, this dialog should<br>Okiever appear<br>Okiever appear |                                                                                                               |

Figure 20. FPGA Build Warning

This is just telling you that compiling the FPGA code can take a long time. Click **OK** and the compiling process will begin. After the build process completes, you may run the VI in FPGA interactive mode. In this mode, the embedded VISA server passes data from the FPGA over the PCI bus to your PC. The update rate in interactive mode is typically limited to about 10 S/s.

While the application is compiling, ask one of the instructors if you have any questions or comments. You've worked hard—sit back and enjoy 5-10 minutes of well deserved rest and relaxation while your LabVIEW FPGA application compiles! If desired, you may read the comments below that explain the compilation process and other topics that may be of interest.

| ompile Status                                                                                          |                                                           |                      |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|--|

| Server Service ID                                                                                      | Client Service ID                                         | Start Time           |  |

| 0                                                                                                      | CustomTri~8B_FPGATarg~A7_SimpleAI~40_ybf4cex2~0F          | 1/17/2006 5:07:39 PM |  |

| Client Name                                                                                            | Status                                                    | Last Update Time     |  |

| localhost                                                                                              | Compiling VHDL 1/17/2006 5:08:34 PM                       |                      |  |

| Details                                                                                                |                                                           |                      |  |

| the output directory. Ou                                                                               | tput products for this core may be overwritten.<br>niles. |                      |  |

| Regenerating IP<br>the output directory. Ou<br>Generating Implementation<br>Generating the VHDL instal | n files.                                                  |                      |  |

Figure 21. Snapshot during FPGA compilation

#### Understand the LabVIEW FPGA Compilation Process

The LabVIEW FPGA Module uses an industry-standard Xilinx ISE compiler. First, your graphical LabVIEW FPGA code is translated to text-based VHDL code. At this time, the **Generating Intermediate Files** dialogue is displayed. Then the Xilinx ISE compiler tools are invoked and the VHDL code is optimized, reduced, and synthesized into a hardware circuit realization of your LabVIEW design. This process also applies timing constraints on the circuit design that ensure an efficient use of FPGA resources (sometimes called "fabric").

A great deal of optimization is performed during the compilation process to reduce digital logic and create an optimal implementation of the LabVIEW application. The end result is a highly optimized silicon implementation that provides true parallel processing with the performance and reliability benefits of dedicated hardware circuitry. Since there is no operating system on the FPGA chip, the code is implemented in a way that ensures maximum performance and reliability.

The end result is a bit stream file that is loaded into your LabVIEW FPGA .VI file. When you run the application, the bitstream is loaded into the FPGA chip to configure the gate array logic. While the application is running on the FPGA, data for the front panel controls and indicators is passed over the network several times per second to enable **Interactive Mode** testing of the application. Later we will build a real-time host interface to the application that enables high speed data transfer and interrupt synchronization between the floating-point host processor and integer-based FPGA chipset.

NOTE: If you disconnect during the compilation, you will need to run the application once while targeted to the FPGA in order to load the bitstream into the FPGA VI file from the compile server.

#### FPGA Clock Speed

By default, the FPGA clock runs at 40 MHz. This means that one **Tick** of the FPGA clock is equal to 25 nanoseconds. By changing the compile options, you can increase the FPGA clock speed up to 200 MHz (5 nanoseconds). There are some drawbacks to using higher clock speeds that you should be aware of before changing the compile option. For more information, refer to the CompactRIO Technical Developers Library by visiting (http://www.ni.com/compactrio) or click the **Help** button on the **Target>Build Options** menu.

#### Understanding the Compilation Report

A SLICE is a collection of logic components on the FPGA. The percentage shown is the percentage of the FPGA used. As the FPGA reaches greater than 90% usage, the compiler performs more optimization to make the most efficient use of resources. For simple applications, the compiler does not "try" very hard to optimize, as it does not need to make efficient use of FPGA resources. For this reason, you may be able to fit more onto the FPGA than this report would lead you to believe.

#### Debugging your FPGA Algorithms before Compilation

Because LabVIEW FPGA uses the same high level LabVIEW source code that is used on all LabVIEW targets, you can execute the same code on any processor in a functionally equivalent manner. This makes LabVIEW a powerful universal programming language for rapid development of embedded systems. Although the execution timing will be different when implemented on the FPGA, the control logic and integer math functionality is the same regardless of how the code is targeted. When running LabVIEW FPGA code in Windows, you can use breakpoints, probes, highlight execution mode and other standard debugging tools to validate the FPGA code. While working in Windows, you can enable the LabVIEW FPGA palette view by clicking the options button at the top-right corner of your functions palette and selecting **FPGA Hardware** in the **Palette View** menu.

When the compiler is complete, the compile report will be generated. This report shows the start and end compilation time, the number of SLICEs used, a compiled clock rate (40 MHz), and an estimated maximum clock rate.

| ummary Advanced                                                                                                          |                                                                                     |   |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---|

| Status: Compilation successful.                                                                                          |                                                                                     | ^ |

| Compilation Summary                                                                                                      |                                                                                     |   |

| Device Utilization Summary:<br>Number of BUFGMUXs<br>Number of External IOBs<br>Number of LOCed IOBs<br>Number of SLICEs | 3 out of 16 18%<br>104 out of 484 21%<br>104 out of 104 100%<br>963 out of 14336 6% |   |

| Clock Rates: (Requested rates and<br>Base clock: 40 MHz Onboard Clo<br>Compiled Rate: 40.<br>Theoretical Maximum: 82.63  | 108938MHz                                                                           |   |

| Start Time: 1/17/2006 5:07:39 PM<br>Ind Time: 1/17/2006 5:14:21 PM                                                       | 4                                                                                   | ~ |

Figure 22. Build Report

A SLICE is a collection of logic components on the FPGA. The percentage shown is the percentage of the FPGA used. In most cases, you can actually fit more onto the FPGA than this report would lead you to believe. For simple applications, the compiler does not "try" very hard to optimize, as it does not need to make efficient use of FPGA resources. The compiler will begin to optimize the compiled code when 95% of the FPGA resources are used.

- 24. Click **OK** to close the build report. The FPGA VI will begin to run automatically. Adjust the analog output (AO 0) voltage and observe the reaction of the system.

- 25. Click **Stop Server** to close the compile server.

- 26. Run the VI and watch how it adds the two numbers. You should also notice that the code takes 6 ticks (or 150 nanoseconds) to execute. Remember we selected an Unsigned Byte representation for the controls and indicators. Therefore each control has a range 0-255. Since the indicator also has the same 8 bit range notice what occurs when 2 large numbers are

added together. For example, 240+120 returns 104 as a result. This is due to overflow and occurs when the result does not have enough bits to store the result. There are special nodes found in the Functions>>Numeric>>Saturation Arithmetic palette that can be used to handle these types of situations. We will discuss these a little later in the lesson.

27. After you have run and tested the code close the application and the Project Manager.

#### ALL STAR (OPTIONAL)

- 28. Now open the precompiled example found in the project named Exercise 21.pjt in the Solutions folder. The VI you should open is named Ex 2 1 optional.vi.

- 29. Looking at the block diagram you will notice that we added a subtraction task to the VI. Run this VI and you will notice that the execution time is still 6 ticks. The execution time remains the same because the addition and subtraction tasks are performed in parallel.