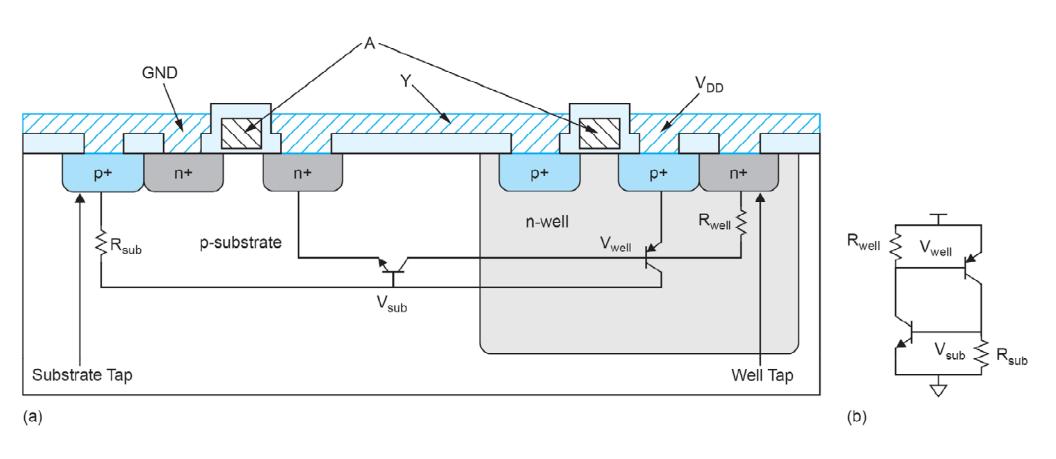

FIGURE 7.12 Origin and model of CMOS latchup

## 7.3.6 Latchup

Early adoption of CMOS processes was slowed by a curious tendency of CMOS chips to develop low-resistance paths between  $V_{\rm DD}$  and GND, causing catastrophic meltdown. The phenomenon, called *latchup*, occurs when parasitic bipolar transistors formed by the substrate, well, and diffusion turn ON. With process advances and proper layout procedures, latchup problems can be easily avoided.

The cause of the latchup effect [Estreich82, Troutman86] can be understood by examining the process cross-section of a CMOS inverter, as shown in Figure 7.12(a), over which is laid an equivalent circuit. In addition to the expected nMOS and pMOS transistors, the schematic depicts a circuit composed of an non-transistor, a pop-transistor, and two resistors connected between the power and ground rails (Figure 7.12(h)). The npntransistor is formed between the grounded n-diffusion source of the nMOS transistor, the p-type substrate, and the n-well. The resistors are due to the resistance through the substrate or well to the nearest substrate and well taps. The cross-coupled transistors form a bistable silicon-controlled rectifier (SCR). Ordinarily, both parasitic bipolar transistors are OFF. Latchup can be triggered when transient currents flow through the substrate during normal chip power-up or when external voltages outside the normal operating range are applied. If substantial current flows in the substrate, Vsub will rise, turning ON the npntransistor. This pulls current through the well resistor, bringing down Vwell and turning ON the pap-transistor. The pap-transistor current in turn raises V<sub>sub</sub>, initiating a positive feedback loop with a large current flowing between VDD and GND that persists until the power supply is turned off or the power wires melt.

Fortunately, latchup prevention is easily accomplished by minimizing  $R_{\text{sub}}$  and  $R_{\text{well}}$ . Some processes use a thin epitaxial layer of lightly doped silicon on top of a heavily doped Voo

[a]

n+ Guard Ring

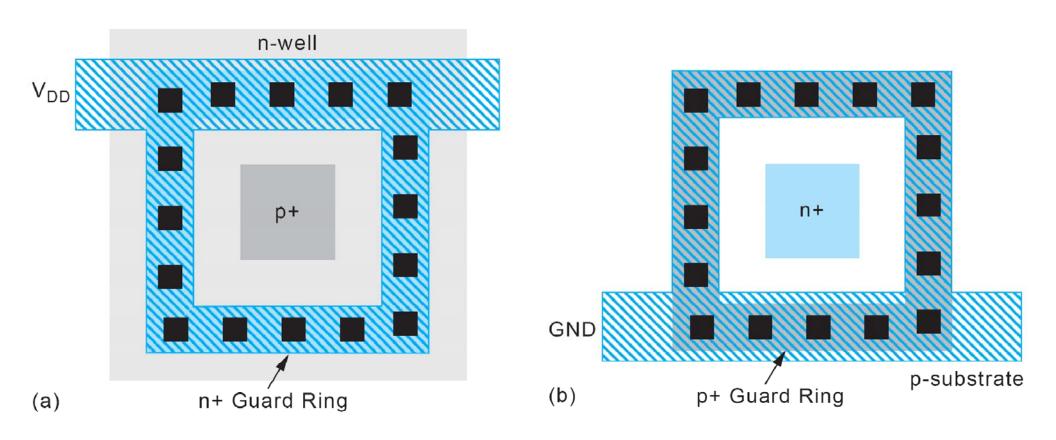

FIGURE 7.13 Guard rings

substrate that offers a low substrate resistance. Most importantly, the designer should place substrate and well taps close to each transistor. A conservative guideline is to place a tap adjacent to every source connected to  $V_{DD}$  or GND. If this is not practical, you can obtain more detailed information from the process vendor (they will normally specify a maximum distance for diffusion to substrate/well tap) or try the following guidelines:

- Every well should have at least one tap.

- All substrate and well taps should connect directly to the appropriate supply in metal.

- A tap should be placed for every 5-10 transistors, or more often in sparse areas.

- nMOS transistors should be clustered together near GND and pMOS transistors should be clustered together near V<sub>IIII</sub>, avoiding convoluted structures that intertwine nMOS and pMOS transistors in checkerboard patterns.

I/O pads are especially susceptible to latchup because external voltages can ring below GND or above  $V_{DD}$ , forward biasing the junction between the drain and substrate or well and injecting current into the substrate. In such cases, guard rings should be used to collect the current, as shown in Figure 7.13. Guard rings are simply substrate or well taps tied to the proper supply that completely surround the transistor of concern. For example, the n+ diffusion in Figure 7.13(b) can inject electrons into the substrate if it falls a diode drop below 0 volts. The p+ guard ring tied to ground provides a low-resistance path to collect these electrons before they interfere with

the operation of other circuits outside the guard ring. All diffusion structures in any circuit connected to the external world must be guard ringed, i.e., n+ diffusion by p+ connected to GND or p+ diffusion by n+ connected to  $V_{DD}$ . For the ultra-paranoid, double guard rings may be employed; i.e., n+ ringed by p+ to GND, then n+ to  $V_{DD}$  or p+ ringed by n+ to  $V_{DD}$  then p+ to GND.

SOI processes avoid latchup entirely because they have no parasitic bipolar structures. Also, processes with  $V_{DD}$  < 1.4–2 V are immune to latchup because the two parasitic transistors will never have a large enough voltage to sustain positive feedback [Johnston96]. Therefore, latchup has receded to a minor concern in nanometer processes.

FIGURE 7.13 Guard rings