## Ion-Implanted Complementary MOS Transistors in Low-Voltage Circuits

RICHARD M. SWANSON, MEMBER, IEEE, AND JAMES D. MEINDL, FELLOW, IEEE

Abstract—Simple but reasonably accurate equations are derived, which describe MOS transistor operation in the weak inversion region near turn-on. These equations are used to find the transfer characteristics of complementary MOS (CMOS) inverters. The smallest supply voltage at which these circuits will function is approximately 8kT/q. A boron ion implantation is used for adjusting MOST turn-on voltage for low-voltage circuits.

### INTRODUCTION

R ECENTLY, techniques have been developed for fabricating complementary MOS transistors with low turn-on voltages, enabling them to be used in circuits with supply voltages less than 1.35 V [1]-[3]. MOS transistors in low-voltage digital circuits are, by necessity, operating near their turn-on or threshold voltage. Unfortunately, in the vicinity of turn-on, the assumptions commonly used in deriving device characteristic equations are inaccurate [4]. In Section I of this paper, new MOS transistor characteristic equations are derived, which are simple but reasonably accurate in the weak inversion region near turn on, as well as elsewhere.

In Section II these equations are used to find the transfer characteristic of a low-voltage complementary MOS inverter and the minimum supply voltage at which the inverter will function is determined. This limit is important since it serves to define the minimum power-speed product that can be achieved with CMOS digital circuits.

In Section III a technique of adjusting MOST turn-on voltage by ion implantation is described. A theory of the turn-on voltage change as a function of the implantation parameters is developed and a brief description of the MOST fabrication procedure is included. By using ion implantation in conjunction with standard aluminum-gate MOS processing, low-voltage complementary integrated circuits with excellent performance characteristics can be achieved.

## I. DEVICE EQUATIONS INCLUDING WEAK INVERSION EFFECTS

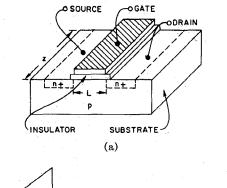

An n-channel MOS transistor [Fig. 1(a)] is analyzed. As illustrated in Fig. 1(b),  $\psi_s$  is the total band bending and  $\phi_f$  is the potential difference between the intrinsic

Manuscript received October 14, 1971; revised December 1, 1971. This work was partly supported by the Department of Health, Education and Welfare under PHS research Grant 5 POI GM17940-02 and by the U.S. Army Electronics Command under Contract DAAB-7-69-C-0192.

The authors are with the Department of Electrical Engineering, Stanford University, Stanford, Calif. 94305. level (midband gap) and the Fermi level. The potential difference between the electron quasi-Fermi level and the bulk Fermi level is  $\phi_c$ , which is nonzero because there is a transverse electron current flowing (i.e., a drain-source voltage is applied).

Integrating Poisson's equation, the total charge in the semiconductor is given approximately [4] by

$$Q_s = -\sqrt{2q\epsilon_s N_A(\psi_s + kT/q)} \exp\left[q(\psi_s - \phi_c - 2|\phi_f|)/kT\right]).$$

(1)

This gives the total semiconductor charge per unit area  $Q_s = Q_n + Q_B$  as a function of  $\psi_s$  and  $\phi_c$ . Two distinct cases of this equation can be identified. These are 1) a weak inversion case where the inversion layer charge per unit area  $Q_n$  is much less than the depletion region charge per unit area  $Q_B$  and 2) a strong inversion case where  $Q_n$  is much greater than  $Q_B$ . Making approximations appropriate in each of these cases, the following formulas, giving  $Q_n$  as a function of the gate voltage  $V_G$  and the electron quasi-Fermi level  $\phi_c$  are derived in the Appendix.

1) Weak Inversion:

$$-Q_n = C_0 \left( n \frac{kT}{q} \right) \exp \left( \frac{q}{nkT} \left[ V_G - V_T(\phi_c) - n \frac{kT}{q} \right] \right),$$

(2a)

valid when  $V_G \leq V_T(\phi_c) + n(kT/q)$ .

2) Strong Inversion:

$$-Q_n = C_0 [V_G - V_T(\phi_c)], \qquad (2b)$$

valid when  $V_G \ge V_T (\phi_c) + n(kT/q)$ .  $C_0$  is the oxide capacitance per unit area.

$$V_{T}(\phi_{c}) = V_{FB} + 2 |\phi_{f}| + \phi_{c}$$

$$+ \frac{1}{C_{0}} \sqrt{2q\epsilon_{s}N_{A}(2 |\phi_{f}| + \phi_{c})}, \qquad (3)$$

is the threshold voltage referenced to the substrate.  $V_{FB}$  is the flat-band voltage [5].

$N_A$  is the substrate doping density and  $\epsilon_s$  is the semiconductor dielectric constant.

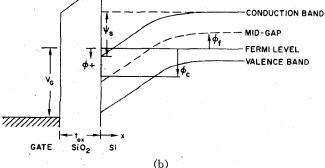

$$n = \frac{C_d + C_{fs} + C_0}{C_0}$$

(4)

$$C_{d} \triangleq \frac{\partial}{\partial \psi_{s}} \left( Q_{B} \right) |_{\psi_{s}=2 \left| \phi_{f} \right| + \phi_{c}};$$

Fig. 1. (a) Physical structure of n-channel MOST. (b) Band diagram of n-channel MOST.

and

$$Q_B = \sqrt{2q\epsilon_s N_A(\psi_s)}$$

so that

$$C_{d} = \frac{\sqrt{2q\epsilon_{s}N_{A}}}{2\sqrt{2}|\phi_{f}| + \phi_{c}}$$

(5)

and  $C_{fs} = qN_{fs}$ , where  $N_{fs}$  is the fast surface state density per electron volt evaluated at  $\psi_s = \phi_c + 2|\phi_f|$ .

A simple physical explanation of (2a) is presented here in lieu of the complete derivation given in the Appendix. If the gate voltage is varied by a small amount  $\Delta V_G$  there will be a small change in surface potential,  $\Delta \psi_s$ .  $\Delta \psi_s$  may be found with the aid of the equivalent circuit shown in Fig. 2.  $C_e$  is the capacitance of the mobile electrons, or  $(\partial Q_n/\partial \phi_s)$ . When the surface is strongly inverted  $C_e$  is much larger than  $C_o$ ,  $C_d$ , and  $C_{fs}$ so that  $\psi_s$  is essentially constant. However, when the surface is weakly inverted  $C_e$  is small compared to  $C_d$ and  $C_{fs}$ . The equivalent circuit then yields  $\Delta \psi_s =$  $(1/n)\Delta V_G$ . In weak inversion  $Q_n$  varies as a constant  $\times \exp [q(\psi_s - \phi_c)kT]$ . From this, it is apparent that  $Q_n \sim \exp \left[ q V_G / n k T - q \phi_c / k T \right]$ . The remaining terms in (2a) are found by considerations presented in the Appendix.

It can be easily shown [5] that when a MOST is operated in the linear region (small drain voltage) the drain-to-source conductance  $g_D$  is given by [5],

$$g_D = \frac{Z}{L} \mu_n \left| Q_n(\phi_c = 0) \right|. \tag{6}$$

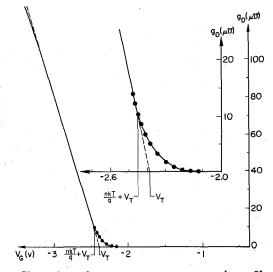

Plots of the measured versus theoretical linear region  $g_D$

Fig. 3. Channel conductance  $g_p$  versus gate voltage  $V_\sigma$  for device 1. — experiment;  $\cdots$  theory.

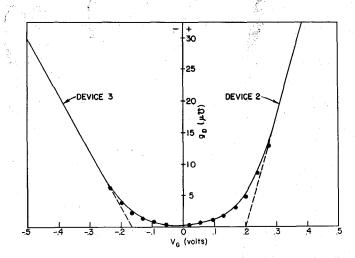

Fig. 4. Channel conductance  $g_D$  versus gate voltage  $V_C$  for devices 2 and 3. —experiment; .... theory.

for three devices are shown in Figs. 3 and 4. Table I contains pertinent data about the devices.

The drain current-voltage characteristics of a MOST are now found using the following relation for the drain current  $I_D$  [4]

$$I_{D} = (Z/L)\mu_{n} \int_{0}^{V_{D}} |Q_{n}(\phi_{c})| d\phi_{c}.$$

(7)

Here Z is the channel width, L, the channel length,  $\mu_n$ , the effective electron surface mobility, and  $V_D$ , the drainto-source voltage. The two relations for  $Q_n$ , (2a), and (2b), when inserted in (7) generate three distinct modes 148

TABLE I

| Devices  | Device Constants                                                                                          | Calculated from Plot                                                                                                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device 1 | $N_D = 1 \times 10^{15} \text{ cm}^{-3}$<br>$t_{0x} = 1000 \text{ Å}$<br>$m = 1 + \frac{C_d}{C_0} = 1.46$ | $V_T = 2.39 \text{ V}$<br>n = 3.08<br>$N_{fs} = 3.8 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$<br>$K = 153 \ \mu\text{A}/\text{V}^2$<br>$= \frac{Z}{L} \ \mu C_0$    |

| Device 2 | $N_A = 1.6 \times 10^{16} \text{ cm}^{-3}$<br>$t_{0x} = 1000 \text{ Å}$<br>m = 2.05                       | $ \begin{array}{l} V_{\rm T} &= 0.20 \ {\rm V} \\ n &= 2.80 \\ N_{fs} &= 1.6 \ \times 10^{11} \ {\rm cm^{-2} \ eV^{-1}} \\ K &= 180 \ \mu {\rm A}/{\rm V^2} \end{array} $ |

| Device 5 | $N_D = 1 \times 10^{15} t_{0x} = 10000 \text{ \AA} m = 1.46$                                              | $V_T =165 \text{ V}$<br>n = 2.70<br>$N_{fs} = 2.7 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$<br>$K = 90 \ \mu\text{A}/\text{V}^2$                                    |

of operation for the MOST. The characteristic equations for each mode are presented below.

## A. Strong Inversion Only

In this case the gate voltage is large enough to strongly invert the entire channel. Equation (2b) applies to the integration (7). The defining criteria for this region are

$$V_G \ge V_T(0) + n(kT/q)$$

and

$$V_G \geq V_T(V_D) + n(kT/q)$$

where the argument of  $V_T$  gives the value of  $\phi_c$  at which (3) is evaluated. Solving the preceding inequality for  $V_D^*$  gives  $V_D \leq V_D^*$  where

$$V_{D}^{*} = V_{G} - \left(V_{T} + n\frac{kT}{q}\right) + V_{B}\left[1 + \frac{V_{B}}{4|\phi_{f}|} - \sqrt{\left(1 + \frac{V_{B}}{4|\phi_{f}|}\right)^{2} + \frac{V_{G} - [V_{T} + n(kT/q)]}{2|\phi_{f}|}}\right].$$

(8)

Here  $V_B$  is defined as  $|Q_b(\psi_s = 2|\phi_f|)|/C_0$  and  $V_T = V_T(0)$ . Using (2a), (7) becomes

$$I_{D} = (Z/L)\mu_{n}C_{0}\left\{ (V_{G} - V_{FB} - 2 |\phi_{f}|)V_{D} - \frac{V_{D}^{2}}{2} - V_{B} \frac{4 |\phi_{f}|}{3} \left[ \left( 1 + \frac{V_{D}}{2 |\phi_{f}|} \right)^{3/2} - 1 \right] \right\} \right]$$

(9a)

valid when  $V_D \leq V_D^*$  and  $V_G \geq V_T + n(kT/q)$ . Equations (9a), (9b) can be simplified by assuming that  $V_D \ll 2|\phi_f|$  yielding

$$I_{D} \cong \frac{Z}{L} \mu_{n} C_{0} \bigg[ (V_{G} - V_{T}) V_{D} - \frac{V_{D}^{2}}{2} \bigg], \qquad (9b)$$

valid when  $V_D \leq (V_G - (V_T + n(kT/q))/m$ , where  $m = (C_0 + C_d)/C_0$ .

#### IEEE JOURNAL OF SOLID-STATE CIRCUITS, APRIL 1972

## B. Mixed Strong and Weak Inversion

In this case, the gate voltage is large enough to strongly invert the channel near the source but the drain voltage is also large enough to cause weak inversion near the drain. In other words, the device is operating near saturation. The criteria are  $V_G \ge V_T(0) + n(kT/q)$  and  $V_G \leq V_T(V_D) + n(kT/q)$ . This yields  $V_D \geq V_D^*$ . In this case (2b) applies to that part of the integration where  $0 \leq \phi_c \leq V_D^*$  and (2a) applies when  $V_D^* \leq \phi_c \leq$  $V_D$ . The major contribution of (1) to the integration is for  $V_D^* \leq \phi_c \leq V_D^* + n(kT/q)$  because the integrand decreases exponentially in  $\phi_c$ . The bulk charge term in  $V_T(\phi_c)$ , (3), will vary only slightly in this range and thus it is reasonable to expand about  $\phi_c = V_D^*$ . This gives  $V_T(\phi_c) = V_T(V_D^*) + m(\phi_c - V_D^*)$  where  $m = (C_0 + C_0)^*$  $(C_d)/C_0$ . Equation (7) becomes upon integrating and noting that  $V_G = V_T(V_D^*) + n(kT/q)$ ,

$$I_{D} = \frac{Z}{L} \mu_{n} C_{0} \left\{ \left( V_{G} - V_{FB} - 2 |\phi_{f}| \right) V_{D}^{*} - \frac{V_{D}^{*2}}{2} - V_{B} \frac{4 |\phi_{f}|}{3} \left[ \left( 1 + \frac{V_{D}^{*}}{2 |\phi_{f}|} \right)^{3/2} - 1 \right] + \frac{1}{m} \left( n \frac{kT}{q} \right)^{2} \left( 1 - \exp \left[ \frac{-mq}{nkt} \left( V_{D} - V_{D}^{*} \right) \right] \right) \right\}, \quad (10)$$

valid when  $V_D \ge V_D^*$  and  $V_G \ge V_T + n(kT/q)$ .

The  $C_d$  term in *n* is evaluated at  $p_c = V_D^*$ .

## C. Weak Inversion Only

In this case the gate voltage is not large enough to strongly invert the channel at any point. The criterion is  $V_G \leq V_T + n(kT/q)$ .

Integrating as before

$$I_{D} = \frac{Z}{L} \mu_{n} C_{0} \frac{1}{m} \left( n \frac{kT}{q} \right)^{2} \exp \left[ \frac{q}{nkT} \left( V_{G} - V_{T} - n \frac{kT}{q} \right) \right]$$

$$\cdot \left\{ 1 - \exp \left[ \frac{-mq}{nkT} V_{D} \right] \right\}, \quad (11)$$

valid when  $V_G \leq V_T + n(kT/q)$ . The  $C_d$  term in n is evaluated at  $\phi_c = V_D^*$ .

Equations (9a), (9b), (10), and (11) characterize the dc behavior of the MOST. The noticeable effects of the weak inversion region are 1) exponential dependence of  $I_D$  on  $V_G$  and  $V_D$  when  $V_G \leq V_T + n(kT/q)$  and 2) exponential transition into saturation instead of the classical parabolic form.

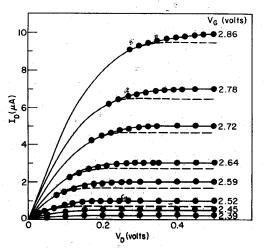

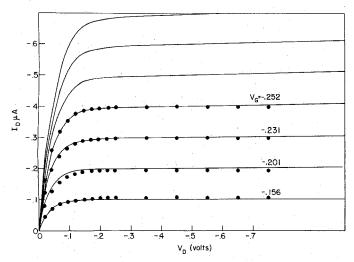

The drain characteristics of the device whose  $Q_n$  versus  $V_G$  relation is shown in Fig. 3 were measured and plotted in Fig. 5. On the same graph, both the classical theory (dashed line) and the theory including weak inversion effects (solid line) are shown. Good agreement is obtained between the experimental data and the predictions of the weak inversion theory.

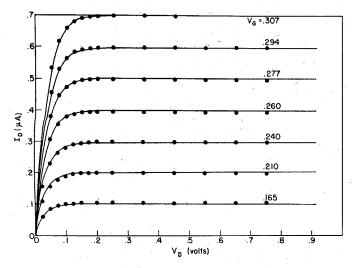

Figs. 6 and 7 show the experimental and theoretical drain characteristics of a low-threshold voltage complementary pair whose  $Q_n$  versus  $V_G$  relations are shown in Fig. 4. Only the weak inversion region is plotted. The

Fig. 5. Drain characteristics for device 1. — experiment; ----classical theory (9a); ···· theory including weak inversion effects (10a) and (11a).

Fig. 6. Drain characteristics for device 2 in weak inversion region. — experiment; ···· theory (11a).

Fig. 7. Drain characteristics for device 3. — experiment; .... theory (11a).

values of  $V_T$ , n, and  $K = (Z/L)\mu C_o$  used in the calculations for Figs. 5, 6, and 7 were taken from Table I. Again, good agreement is obtained for both the n-channel and p-channel devices.

## II. LOW-VOLTAGE COMPLEMENTARY INVERTERS

Complementary MOS logic circuits offer distinct advantages in power consumption compared to single-ended circuits. However, to obtain the greatest power savings and lowest power-speed product they should be operated at the lowest practical supply voltage [6]. Realizing that MOS transistors do not turn off as abruptly as the classical equations (9a) and (9b) indicate, but are weakly inverted at gate voltages below  $V_T$ , it is desirable to find the minimum supply voltage  $V_s$  at which complementary circuits will operate. To this end, the transfer characteristic of a complementary inverter is now determined.

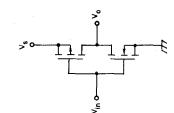

The inverter circuit being analyzed is shown in Fig. 8. The following notations are used.  $V_{Tp}$  and  $V_{Tn}$  are the magnitude of the thresholds of the n- and p-channel devices, respectively.  $K_n = (Z/L)\mu_n C_o$  is the gain constant of the n-channel device and  $K_p$  similarly for the p-channel device  $m_n$  and  $n_n$ , as defined in Section I, refer to the values of m and n for the n-channel device. For the p-channel device  $m_p$  replaces  $m_n$  and  $n_p$  replaces  $n_n$ . It is assumed that both transistors are in the weak-inversion-only region. This will be the case if  $V_s - V_{Tp} - n_p(kT/q) \leq V_{in} \leq V_{Tn} + n_n(kT/q)$ .

Equating the drain current, as found by (11) for both devices, yields

$$\begin{split} I_{D} &= K_{n} \left( n_{n} \frac{kT}{q} \right)^{2} \frac{1}{m_{n}} \\ &\cdot \exp \left[ \left[ q \left( V_{\text{in}} - V_{Tn} - n_{n} \frac{kT}{q} \right) \middle/ n_{n} kT \right] \right. \\ &\cdot (1 - \exp \left[ -m_{n} q V_{0} / n_{n} kT \right]) \\ &= K_{p} \left( n_{p} \frac{kT}{q} \right)^{2} \frac{1}{m_{p}} \\ &\cdot \exp \left[ \left[ q \left( V_{s} - V_{\text{in}} - V_{Tp} - n_{p} \frac{kT}{q} \right) \middle/ n_{p} kT \right] \\ &\cdot (1 - \exp \left[ -m_{p} q (V_{s} - V_{0}) / n_{p} kT \right] \right]. \end{split}$$

Solving for  $V_{in}$  gives

$$V_{in} = \frac{kT}{q} \left( \frac{n_n n_p}{n_n + n_p} \right) \ln \left( \frac{K_p}{K_n} \frac{n_p^2 m_n}{n_n^2 m_p} \right) + \frac{n_n}{n_n + n_p} V_s + \frac{n_n n_p}{n_n + n_p} \left( \frac{V_{Tn}}{n_n} - \frac{V_{Tp}}{n_p} \right) + \frac{kT}{q} \left( \frac{n_n n_p}{n_n + n_p} \right) \ln \left( \frac{1 - \exp\left[ -\frac{m_p q (V_s - V_0) / n_p kT \right]}{1 - \exp\left[ -\frac{m_p q V_0 / n_n kT \right]} \right)}.$$

(12)

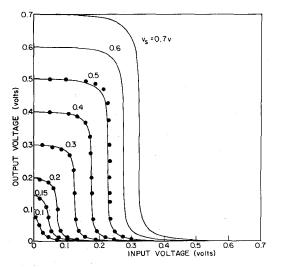

The measured transfer characteristic for the complementary pair (devices 2 and 3) for various power supply voltages is shown in Fig. 9. Equation (12), using the

Fig. 8. CMOS inverter circuit.

Fig. 9. CMOS inverter transfer characteristics. — experiment; .... theory (12a).

device constants from Table I, is also plotted in Fig. 9. It is interesting to note that there is no hysteresis in the transfer characteristic, even when  $V_s < |V_{T_R}| + |V_{T_P}|$ .

A simple expression for the inverter gain may be found by assuming  $m_n = m_p = m$  and  $n_n = n_p = n$ . Differentiating (12) with respect to  $V_o$  gives the reciprocal of the inverter gain. The maximum gain is found to occur at  $V_o = V_s/2$  and is given by

$$A_* = \frac{1}{m} \left( \exp\left[\frac{mqV_s}{2nkT}\right] - 1 \right)$$

(13)

It is seen that  $V_s$  must be at least 3–4 nkT/mq for the inverter to have sufficient gain for use in a digital circuit. Thus

$$V_{s,\min} \approx 4 \, \frac{nkT}{mq}$$

(14)

If  $N_{fs} = 0$  then n/m = 1 and the inverter displays the maximum nonlinearity obtainable in semiconductor material [7]. Transistors fabricated using conventional clean oxide techniques including a low temperature anneal in forming gas will have n/m in the neighborhood of 2 (see Table I), giving a minimum usable supply of about 8kT/q or 0.2 V at 27°C. Standard fabrication techniques yield a spread in turn-on voltages on the order of 0.2 V so a practical supply voltage could never be quite as low as 0.2 V. However, regardless of improvements in control of threshold during fabrication, the supply voltage can never be less than that given by (14).

It is interesting to note that reduced operating temperatures permit lower supply voltages [7].

## III. Adjusting MOST Turn-on Voltage by Ion Implantation

In the preceding discussion of low-voltage complementary MOS circuits, it has been assumed that the transistor turn-on voltage could always be adjusted to the desired value, approximately half the supply voltage [8]. Using conventional aluminum gate processing this is possible with n-channel devices. Unfortunately, aluminum gate p-channel devices will always have turn-on voltages of -2 V or less. This section discusses a technique for ion-implanting boron [9] through the gate oxide to form a shallow p-layer in the channel region of a pchannel device. This technique decreases the magnitude of the turn-on voltage from its initial value. As a result, devices whose original thresholds were in the neighborhood of -2-3 V can have their thresholds shifted as close to zero as desired. Device 3, whose transfer and drain characteristics are shown in Figs. 4 and 6, was fabricated by this method, resulting in  $V_{TP} = -0.17$  V.

It will be assumed that the implanted boron concentration  $N_A$  (at the semiconductor surface), is greater than the n-type substrate doping density  $N_D$  creating a p-type surface layer. A depletion region will exist at the p-n junction extending a distance  $1_p$  from the junction toward the surface where from [4]

$$1_{p} = \frac{N_{D}}{N_{A}} \left[ \frac{2\epsilon(|\phi_{fp}| + |\phi_{fn}|)}{q} \frac{N_{A}}{(N_{A} - N_{D})N_{D}} \right]^{1/2}, \quad (15)$$

assuming that the boron density is uniformly distributed from the surface to a depth W. The total implanted dose per unit area in the silicon is  $N_I = N_A W$ .

For boron doses of interest  $N_A$  will be much greater than  $N_D$ . In this case (15) becomes

$$1_p = \frac{W}{qN_1} \sqrt{2qN_D\epsilon_s(|\phi_{fn}| + |\phi_{fp}|)}.$$

(16)

Since  $|\phi_{fn}| \approx |\phi_{fp}|$ , (16) can be approximated by

$$1_{p} \simeq W \frac{Q_{B}(\psi_{s} = 2 |\phi_{f}|)}{q N_{I}}.$$

(17)

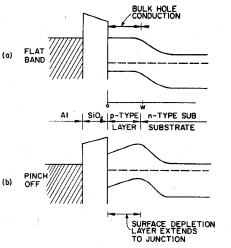

Equation (17) reevals that if  $N_I$  is greater than  $Q_B(\psi_s = 2|\phi_I|)/q$ , the junction depletion region will not extend to the semiconductor surface.  $Q_B/q$  is about  $10^{i1}$  cm<sup>-2</sup> for the typical n-type substrate resistivity of 5  $\Omega$ -cm. From considerations below, it is seen that if  $N_I$  is less than  $10^{11}$  cm<sup>-2</sup> the shift in turn-on voltage is less than 0.5 V. In practice a larger shift in turn-on voltage is usually desired causing  $1_p$  to be less than W. The possibility then exists for an undepleted region of mobile holes to exist near the semiconductor surface. This situation is illustrated in Fig. 10(a). Increasing the gate voltage from the value at flat band creates a surface depletion region will extend to the junction depletion region removing all mobile holes from the channel region

Fig. 10. Band structure for a boron-implanted p-channel MOS transistor.

as illustrated in Fig. 10(b). This is the turn-on voltage for the device.

At this point, calculating the turn-on after implantation  $V_{TI}$  is straightforward. The depth of the surface depletion layer  $\mathbf{1}_s$  is

$$1_{*} = \sqrt{\frac{2\epsilon_{*}\psi_{t}}{qN_{A}}}, \qquad (18)$$

where  $\psi_t$  is the surface depletion region band bending in the p-layer. At turn-on  $1_s + 1_p = W$  so that

$$\sqrt{\frac{2\epsilon_*\psi_i}{qN_A}} + \frac{Q_BW}{qN_I} = W.$$

(19)

Solving (19) for  $\psi_t$  gives

$$\psi_t = \frac{qN_I W (1 - Q_B / qN_I)^2}{2\epsilon_s}.$$

(20)

The gate voltage at turn-on, including charge from both the surface and junction depletion regions, is thus

$$V_{TI} = \Phi_{MS} - \frac{Q_{SS}}{C_0} - (|\phi_{fn}\rangle + |\phi_{fp}|) + \psi_t + \frac{qN_I}{C_0} - \frac{Q_B}{C_0}.$$

(21)

$\Phi_{MS}$  is the metal-semiconductor work function for the n-type substrate. The turn-on voltage prior to implantation is

$$V_{T} = \Phi_{MS} - \frac{Q_{SS}}{C_{0}} - 2 |\phi_{fn}| - \frac{Q_{B}}{C_{0}}$$

(22)

The shift in turn on  $\Delta V_T$  is thus

$$\Delta V_{T} = V_{TI} - V_{T} = (|\phi_{fp}| - |\phi_{fn}|) + \frac{qN_{I}}{C_{0}} + \frac{qN_{I}W(1 - Q_{B}/qN_{I})^{2}}{2\epsilon_{s}}.$$

(23)

$(|\phi_{fp}| - |\phi_{fn}|)$  can usually be neglected.

The last term in (23) is the surface band bending and must be less than  $2|\phi_{fp}|$  or the surface would become

n-type, prohibiting further band bending. If the surface becomes n-type before the surface depletion region extends deep enough to entirely deplete the p-layer the device cannot be turned off. Since  $\psi_t$  must be less than  $2|\phi_{tp}|$  for complete turn-off to be possible, (20) gives

$$2 |\phi_{fp}| \le \psi_t = \frac{q N_I W}{2\epsilon_s} \tag{24}$$

assuming  $Q_B/qN_I \ll 1$ . The maximum possible shift in threshold  $\Delta V_{T \max}$ , while having a device that can be turned off, is, using (23) and (24),

$$\Delta V_{T \max} = 2 \left| \phi_{fp} \right| + \frac{4 \left| \phi_{fp} \right| \epsilon'_s}{WC_0} = 2 \left| \phi_{fp} \right| \left[ \frac{2\epsilon_s/W}{C_0} + 1 \right]$$

(25)

Thinner p-layers allow larger shifts in turn-on voltage. When both the gate oxide and W are 1000 Å,  $\Delta V_{T \max}$  is about 5.2 V.

The threshold-shifting boron implantation is done after gate oxidation. Only those ions that pass through the oxide will contribute to  $N_I$ . Computer calculations of the Lindhard, Scharff, and Schiott depth-penetration theory [10] predict that the boron will have a Gaussian concentration profile centered about a depth which depends on the implantation voltage and a standard deviation about one third this depth. At a 30-kV implantation voltage, 50 percent of the boron will penetrate a 1000-Å gate oxide, at 40 kV 80 percent will penetrate a 1000-Å gate 93 percent will penetrate. Energies in the range of 30-50 kV have been found suitable for device fabrication provided the doses are adjusted to allow for the partial penetration.

The implantation must be followed by an anneal to restore crystal damage and activate the boron. Annealing for ten minutes at 1050°C appears to give complete activation and gives good SiO<sub>2</sub>-Si interface characteristics. Following this anneal the junction depth is about 1500 Å. If the anneal is performed at less than 900°C, the boron will not be totally active and the device properties are degraded. Device 3 received a dose of  $1.1 \times 10^{12}$ cm<sup>-2</sup> at 30 kV and was annealed at 1050°C. The resulting shift in turn-on voltage was +2 V.

The turn-on voltages of n-channel devices can also be shifted in a positive direction by boron implantation. Of course, in this case there is no junction formed by the implantation. If the depth of the boron is much less than the surface depletion-layer depth,  $Q_B$  will not be greatly affected by the implant and the turn-on shift will be  $\Delta V_T = qN_I/C_c$ .

CMOS integrated circuits with a wide variety of threshold voltages can be fabricated using ion implantation to adjust threshold voltages and to provide a predeposition for doping p-type regions where the n-channel devices are located.

### Conclusion

The fast surface state density  $N_{fs}$  is the most important factor in determining the performance of MOS

transistors in the weak inversion region near turn-on. At room temperature CMOS circuits can operate at supply voltages as low as 0.2 V, provided the fast surface state density is low enough. Ion implantation of boron is a convenient method of adjusting the turn-on voltage of MOS transistors, both n- and p-channel, to permit operation at low supply voltages.

## Appendix

The total charge per unit area  $Q_s$  in the semiconductor is given by Sze [4]. For substrate doping levels of interest  $q\psi_s/kT > 20$  when  $\psi_s$  is near threshold.  $Q_s$  is then approximated by

$$Q_s$$

$$= -\sqrt{2q\epsilon_s N_A(\psi_s + (kT/q) \exp \left[q(\psi_s - \phi_c - 2 |\phi_f|)/kT\right])},$$

(26)

where  $N_A$  is the *R*-type substrate-doping density and  $\epsilon_s$  is the dielectric constant of the semiconductor. Assuming that the voltage developed across the surface inversion layer is much less than  $2|\phi_f|$ , the immobile charge in the surface depletion region  $Q_B$  is

$$Q_B = -\sqrt{2q\epsilon_s N_A \psi_s}.$$

(27)

This leaves  $Q_n = Q_s - Q_B$  mobile electrons per unit area in the inversion layer.

$$Q_n$$

$$= -\left[\sqrt{2q\epsilon_{s}N_{A}(\psi_{s} + (kT/q) \exp\left[q(\psi_{s} - \phi_{c} - 2 |\phi_{f}|)/kT\right]}\right) - \sqrt{2q\epsilon_{s}N_{A}\psi_{s}}\right]$$

(28)

The gate voltage  $V_G$  is given by

$$V_{g} = \Phi_{MS} + \psi_{s} - \frac{Q_{SS}}{C_{0}} - \frac{Q_{fs0}}{C_{0}} + \frac{qN_{fs}}{C_{0}} (\psi_{s} - \phi_{c} - 2 |\phi_{f}|) - \frac{Q_{n}}{C_{0}} - \frac{Q_{B}}{C_{0}}.$$

(29)

$\Phi_{MS}$  is the metal semiconductor work function,  $Q_{SS}$  the fixed interface charge per unit area,  $Q_{fso}$  the charge in filled fast surface states per unit area when  $\psi_s = \phi_c + 2|\phi_f|$ ,  $N_{fs}$  the fast surface state density per electronvolt at  $\psi_s = \phi_c + 2|\phi_f|$ , and  $C_0$  the oxide capacitance per unit area.

$Q_n$  is found as a function of  $V_G$  by eliminating  $\psi_s$  from (28) and (29). This cannot be done in closed form. However, from (28) two distinct regions can be identified. A weak inversion region is defined by

$$(kT/q) \exp \left[q(\psi_s - \phi_c - 2 |\phi_f|)/kT\right] \ll \psi_s,$$

(i.e., the bulk charge dominates the inversion layer charge) and a strong inversion region by  $(kT/q) \exp[q(\psi_s - \phi_c - 2|\phi_f|)/kT] \gg \psi_s$ . The weak inversion criterion is valid when  $\psi_s \leq \phi_c + 2|\phi_f|$ . For  $\psi_s$  slightly greater than  $\phi_c + 2|\phi_f|$  the exponential rapidly increases and the strong inversion criterion is valid.

For the weak inversion region,  $Q_n$  is found by a first-

order Taylor-series expansion of (28) in powers of  $\exp[q(\psi_s - \phi_c - 2|\phi_f|)/kT]$ . This gives

$$-Q_n = \frac{\sqrt{2q\epsilon_s N_A}}{2\sqrt{\psi_s}} \frac{kT}{q} \exp\left[q(\psi_s - \phi_c - 2 |\phi_f|)/kT\right].$$

(30)

Since there will be significant mobile charge only when  $\psi_s$  is in the vicinity of  $\phi_c + 2|\phi_f|$  it is reasonable to expand the  $Q_B$  term in (29) about  $\psi_s = \phi_c + 2|\phi_f|$ . By the weak inversion criterion  $Q_n$  (30) is negligible compared with  $Q_B$  and (29) becomes

$$V_{G} = V_{FB} + \phi_{c} + 2 |\phi_{f}| + \frac{\sqrt{2q\epsilon_{s}N_{A}(\phi_{c} + 2 |\phi_{f}|)}}{C_{0}} + \left(1 + \frac{C_{d}}{C_{0}} + \frac{C_{fs}}{C_{0}}\right)(\psi_{s} - \phi_{c} - 2 |\phi_{f}|)$$

or

$$\psi_s - \phi_c - 2 |\phi_f| = \frac{1}{n} [V_G - V_T(\phi_c)].$$

(31)

where

$$V_{FB} = \Phi_{MS} - \frac{Q_{SS}}{C_0} - \frac{Q_{fS0}}{C_0}$$

$$n = \frac{C_d + C_{fs} + C_0}{C_0}$$

and

$$V_T(\phi_c) = V_{FB} + \phi_c + 2 |\phi_f| + \frac{\sqrt{2q\epsilon_c N_A(\phi_c + 2 |\phi_f|)}}{C_0}$$

(32)

is the gate voltage when  $\psi_s = \phi_c + 2|\phi_f|$ .  $C_d$  and  $C_{fs}$  are given by (5).

Inserting (31) into (30) and evaluating the denominator at  $\psi_s = \phi_c + 2|\phi_f|$  gives  $Q_n$  as a function of  $V_G$  in the weak inversion region.

$$-Q_n = C_d(kT/q) \exp q[V_G - V_T(\phi_c)]/nkT].$$

(33)

When  $\psi_s$  is some small amount (several kT/q) greater than  $\phi_c + 2|\phi_s|$  the exponential term in (28) dominates and the strong inversion criterion is satisfied. From (29) it is apparent that  $\psi_s$  varies logarithmically with  $V_G$  in the strong inversion region. As a first approximation it is assumed that  $\psi_s$  is pinned a small potential  $\Delta\phi$  above  $\phi_c + 2|\phi_f|$ . In other words  $\psi_s = 2|\phi_f| + \Delta\phi$  when the surface is strongly inverted. Equation (29) then yields, upon solving for  $Q_n$ ,

$$-Q_n = C_0 \left[ V_G - V_T(\phi_c) - \left( 1 + \frac{C_d}{C_0} \right) \Delta \phi \right] \cdot \qquad (34)$$

$\Delta \phi$  is found by assuming that the weak inversion equation (33) must be just tangent to the strong inversion equation (34). The point of tangency  $V_{\alpha}$  is the dividing point above which (34) is valid and below which (33) is valid. Equating (33) and (34) and their derivatives

at  $V_{\alpha}$  yields

$$\Delta \phi = \frac{1}{1 + \frac{C_d}{nC_0}} \frac{kT}{q} \left[ \ln \left( \frac{nC_0}{C_d} \right) - 1 \right]$$

(35)

$$V_{\alpha} = V_T(\phi_c) + \left(1 + \frac{C_d}{C_0}\right) \Delta \phi + n(kT/q).$$

(36)

Equations (33)-(36) thus furnish an approximate description of the inversion laver charge in both the strong and weak inversion regions.

Usually a turn-on voltage  $V'_T(\phi_c)$  is experimentally defined by extension of the linear portion (strong inversion) of the  $Q_n$  versus  $V_G$  relation to zero charge. From (34) this means that  $V'_{T}(\phi_{c}) = V_{T}(\phi_{c}) + (1 + (C_{d}/C_{0}))$  $\Delta \phi$ . Substituting this relation for  $V'_{T}(\phi_{c})$  into (33)-(36) yields the following convenient equations

$$-Q_n = C_0 \left( n \, \frac{kT}{q} \right) \exp \left[ \frac{q}{nkT} \left( V_G - V'_T(\phi_c) - n \, \frac{kT}{q} \right) \right],$$

(37)

valid when  $V_G \leq V'_T(\phi_c) + n(kT/q)$  and

$$-Q_n = C_0 [V_G - V'_T(\phi_c)], \qquad (38)$$

## References

- K. Nagane and T. Fanak, "Al<sub>2</sub>O<sub>8</sub> complementary MOS tran-sistors," in Proc. 1st Conf. Solid-State Devices, pp. 132-136, Tokvo. 1969.

- [2] T. Leuenberger and E. Vittoz, "Complementary-MOS low-power low-voltage integrated binary counter," Proc. IEEE (Special Issue on Materials and Processes in Integrated

- (5) Ferrar 1850 of Materials and 1900esses in Integrated Electronics), vol. 59, pp. 1528-1532, Sept. 1969.

[3] R. G. Daniels and R. R. Burgess, "The electronic wristwatch; an application for Si Gate CMOS-IC's," ISSCC Dig. Tech. Papers, 1971.

[4] S. M. Sze, Physics of Semiconductor Devices. New York:

- [4] S. M. Sze, 1 hysics of Semiconductor Decurs. Lett. Wiley, 1969, p. 517.

[5] A. S. Grove, Physics and Technology of Semiconductor Devices. New York: Wiley, 1967.

[6] J. D. Meindl and R. M. Swanson, "Potential improvements of directed simplify" Proc IEEE.

- in power speed performance of digital circuits," Proc. IEEE,

- in power speed performance of digital circuits," Proc. IEEE, vol. 59, pp. 815-816, May 1971.

[7] R. W. Keyes, "Physical problems and limits in computer logic," IEEE Spectrum, vol. 6, pp. 36-45, May 1969.

[8] J. R. Burns, "Switching response of complementary symmetry MOS transistor logic circuits," RCA Rev., vol. 24, pp. 627-661, Dec. 1964.

[9] J. F. Gibborg "Logic circuitation" in the circuitation of the ci

- J. F. Gibbons, "Ion implantation in semiconductors,—Part 1: Range distribution theory and experiments," *Proc. IEEE*, vol. 56, pp. 295–319, March 1968. [9]

- [10] W. S. Johnson and J. F. Gibbons, "Projected range statistics in semiconductors," Stanford Univ. Press, Stanford, Calif., 1970

# Complementary Transistor-Transistor Logic (CT<sup>2</sup>L)-An Approach to High-Speed Micropower Logic

ROBERT A. STEHLIN, MEMBER, IEEE, AND GEORGE W. NIEMANN, MEMBER, IEEE

Abstract-A new approach to micropower integrated circuits has been developed and is called complementary transistor-transistor logic (CT<sup>2</sup>L).<sup>1</sup> This logic combines the inherent low standby power of a complementary inverter with the high speed of the T<sup>2</sup>L-type input. Results of the monolithic fabricated circuits are presented.

#### INTRODUCTION

$\neg$  HE concept of using complementary (p-n-p and n-p-n) transistors in logic circuits was advanced by Baker,<sup>2</sup> for obtaining a maximum efficiency design. Some of the features of a circuit that uses complementary transistors at the output are the following.

1) Drive capabilities are excellent since the load is driven by a low-impedance source in both directions.

2) Both the high- and low-output voltages are clamped by the  $V_{CE(sat)}$  of the transistors.

- 3) Fast switching speeds are inherent at low powers.

- 4) The circuit operates with only one power supply.

5) There is low standby power; i.e., when there is NO LOAD, the power dissipated is that of the base currents.

This paper describes the development of a new approach to micropower microelectronic digital circuits called complementary transistor-transistor logic (CT<sup>2</sup>L). This logic combines the inherent low standby power and excellent drive capability of a complementary inverter with the high speed of the  $T^2L$ -type input. This new logic achieves high speeds (2 MHz) while maintaining very low worst case standby power (300  $\mu$ W). Worst case standby power is for a "0" input and + 10 percent power-supply voltage.

Manuscript received October 7, 1971; revised November 1, 1971. This work was sponsored in part by NASA Langley under contracts NASI-4350 and NASI-7106. The authors are with Texas Instruments Incorporated, Dallas,

Tex.

<sup>&</sup>lt;sup>1</sup>U. S. Patents 3 506 846 and 3 473 045. <sup>2</sup>R. H. Baker, "Maximum efficiency switching circuits," M.I.T. Lincoln Laboratory, Cambridge, Mass., Tech. Rep. 110.