# Synopsys FPGA Synthesis Synplify Pro Quick Start Guide

June 2009

http://solvnet.synopsys.com

#### **Disclaimer of Warranty**

Synopsys, Inc. makes no representations or warranties, either expressed or implied, by or with respect to anything in this manual, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose of for any indirect, special or consequential damages.

## **Copyright Notice**

Copyright © 2009 Synopsys, Inc. All Rights Reserved.

Synopsys software products contain certain confidential information of Synopsys, Inc. Use of this copyright notice is precautionary and does not imply publication or disclosure. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the prior written permission of Synopsys, Inc. While every precaution has been taken in the preparation of this book, Synopsys, Inc. assumes no responsibility for errors or omissions. This publication and the features described herein are subject to change without notice.

## Trademarks

#### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, Design Compiler, DesignWare, Formality, HDL Analyst, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SiVL, SCOPE, Simply Better Results, SNUG, SolvNet, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (SM)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

### **Restricted Rights Legend**

Government Users: Use, reproduction, release, modification, or disclosure of this commercial computer software, or of any related documentation of any kind, is restricted in accordance with FAR 12.212 and DFARS 227.7202, and further restricted by the Synopsys Software License and Maintenance Agreement. Synopsys, Inc., Synplicity Business Group, 600 West California Avenue, Sunnyvale, CA 94086, U. S. A.

Printed in the U.S.A June 2009

# Contents

#### **Chapter 1: Quick Start Overview**

#### **Chapter 2: Process Flow**

| Top-Down and Compile Point Design Flows | 13     |

|-----------------------------------------|--------|

|                                         | <br>10 |

#### **Chapter 3: Set up Design Information**

Select a Target Device 16

| Set Implementation Options   | 17 |

|------------------------------|----|

| State Machine Implementation | 17 |

| Resource Sharing             | 18 |

| Pipelining                   | 18 |

| Retiming                     | 19 |

| Formal Verification          | 20 |

#### **Chapter 4: Set up Timing Information**

| Set Timing Constraints                                                                                  | 24 |

|---------------------------------------------------------------------------------------------------------|----|

| Define Compile Points                                                                                   | 25 |

| Set Constraints (Compile Point Synthesis)<br>Set Top-level Constraints<br>Set Compile Point Constraints | 26 |

| Run                                                                                                     | 28 |

#### **Chapter 5: Analyze Results**

| /iew the Log File                  | 1 |

|------------------------------------|---|

| RTL View                           | 2 |

| Technology View                    | 3 |

| Design Hierarchy Exploration Tools | 3 |

| Advanced Find Capabilities         | 6 |

| Filtered and Flattened Views       | 7 |

| Crossprobing Across Views4         | 1 |

| Cross-tool Crossprobing42Other Options43Mouse Strokes44                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use FSM Viewer                                                                                                                                                                                                                                                                          |

| Other Tools to Validate Synthesis Results       48         Use Formal Verification       48         Use syn_probe Attribute       49         Identify RTL debugger       49                                                                                                             |

| Chapter 6: Specify Directives and Attributes                                                                                                                                                                                                                                            |

| syn_maxfan                                                                                                                                                                                                                                                                              |

| Chapter 7: Basics of Timing Constraints                                                                                                                                                                                                                                                 |

| Example57Input Ports62Output Ports64Setting Multicycle Path Constraints66                                                                                                                                                                                                               |

| Chapter 8: Analyze Timing Results                                                                                                                                                                                                                                                       |

| Timing Information Display       .71         Critical Path Views       .71         Generate a Technology View for the Most Critical Path       .72         Generate Critical Path View in the Timing Analyzer       .73         Generate Critical Path View from the Log File       .76 |

| Chapter 9: Refine Options to Improve Timing<br>Compare Synthesis Results with Place-and Route Results                                                                                                                                                                                   |

| Forward Annotate Incremental Results                                                                                                                                                                                                                                                    |

| Chapter 10: Additional Features and Topics<br>Output Netlist                                                                                                                                                                                                                            |

# CHAPTER 1 Quick Start Overview

What does the Synplify Pro software Offer? — The Synplify Pro software consists of a fast, high-performance, sophisticated logic synthesis engine that utilizes proprietary technology called Behavior Extracting Synthesis Technology<sup>®</sup> (BEST<sup>™</sup>) to deliver highly efficient FPGA and CPLD designs. Starting with Verilog and VHDL hardware description language input files, the software generates an optimized netlist in the most popular CPLD and FPGA vendor formats.

**Who Will Find This Guide Useful?** — This guide provides the steps and options of a design flow and can be used by:

- Engineers who want to evaluate the software without actually running it. The guide includes many graphic examples that show the capabilities of the software.

- Engineers who want to get a quick start to run synthesis.

- Managers who want to understand the capabilities and features of the software before purchasing.

**How is the information organized?** — The document is organized as described below. You can click on the links in the columns to take you to the sections:

|                                              | Describes                                                                           | Page |

|----------------------------------------------|-------------------------------------------------------------------------------------|------|

| Process Flow                                 | The top-down and Compile Point Synthesis flows.                                     | 11   |

| Set up Design Information                    | The steps used to set up your project                                               | 15   |

| Add Source Files                             | —for Synplify Pro synthesis.                                                        | 15   |

| Select a Target Device                       |                                                                                     | 16   |

| Set Implementation Options                   |                                                                                     | 17   |

| Set up Timing Information                    | How to set general timing                                                           | 23   |

| Set Timing Constraints                       | <ul> <li>constraints and define compile<br/>points for the Compile Point</li> </ul> | 24   |

| Define Compile Points                        | Synthesis flow.                                                                     | 25   |

| Set Constraints (Compile Point<br>Synthesis) |                                                                                     | 26   |

| Run                                          | How to synthesize the design.                                                       | 28   |

| Analyze Results                              | How to view the synthesis results                                                   | 29   |

| View the Log File                            | —using the log file and some built-in<br>tools like the HDL Analyst tool for        | 31   |

| Use the HDL Analyst® Tool                    | graphic analysis and the FSM viewer for state machine implementations.              | 31   |

| Use FSM Viewer                               | Also describes how to formally verify your results with LEC.                        | 45   |

| Other Tools to Validate Synthesis<br>Results |                                                                                     | 48   |

| Use Formal Verification                      |                                                                                     | 48   |

| Use syn_probe Attribute                      |                                                                                     | 49   |

| Identify RTL debugger                        |                                                                                     | 49   |

| Specify Directives and Attributes            | How to use attributes and directives                                                | 51   |

| syn_maxfan                                   | —to fine-tune the way the design is synthesized.                                    | 52   |

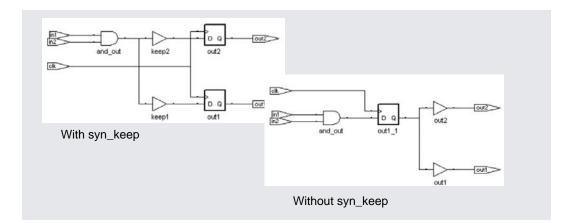

| syn_keep                                     |                                                                                     | 52   |

| syn_ramstyle                                 |                                                                                     | 53   |

| Timing Information Display                                |                                                                                                                                                         | 71 |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Critical Path Analysis in a Technology<br>View            |                                                                                                                                                         | 71 |

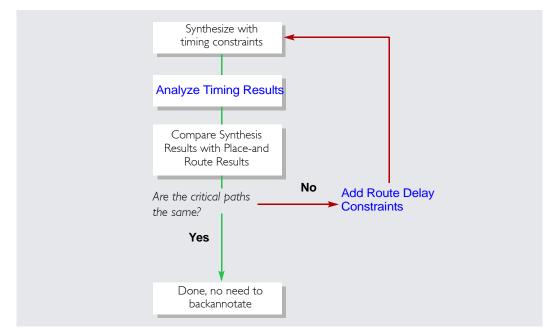

| Refine Options to Improve Timing                          |                                                                                                                                                         | 79 |

| Refine Timing Results                                     |                                                                                                                                                         | 79 |

| Compare Synthesis Results with<br>Place-and Route Results |                                                                                                                                                         | 80 |

| Forward Annotate Incremental<br>Results                   | How to forward annotate<br>incremental results (updates) in a<br>Compile Point Synthesis flow so that<br>your complete design project is<br>up-to-date. | 82 |

|                                                           |                                                                                                                                                         |    |

|                                                           |                                                                                                                                                         |    |

Describes...

Synplify Pro tool.

Basic timing concepts used in the

How to analyze timing results and -use options to improve timing.

**Basics of Timing Constraints**

**Clock Descriptions**

Rise and Fall Constraints

Input and Output Delays

Clock Groups

Multicycle Paths

Analyze Timing Results

Critical Path Report

I/O Standard

Specifying Timing Information

Page

55

55

56

59

60

61

65 67

69

69

|                                                       | Describes                           | Page |

|-------------------------------------------------------|-------------------------------------|------|

| Additional Features and Topics:                       | Additional features and options for | 85   |

| Synplify Premier Physical Synthesis                   | -synthesis.                         |      |

| Synthesis Output Files                                | _                                   |      |

| Using Multiple Clock Domains                          | _                                   |      |

| Using Scripts and Batch Mode                          | _                                   |      |

| Using the Tcl Find Command for<br>Setting Constraints | _                                   |      |

| Running Place and Route                               | _                                   |      |

| Using Identify with Synplify Pro                      | _                                   |      |

### CHAPTER 2

# **Process Flow**

The Synplify Pro software is designed to give you the best overall circuit performance with a minimal amount of effort.

Topics include the following process flows:

- Process Flow Diagram, on page 11

- Top-Down and Compile Point Design Flows, on page 13

## **Process Flow Diagram**

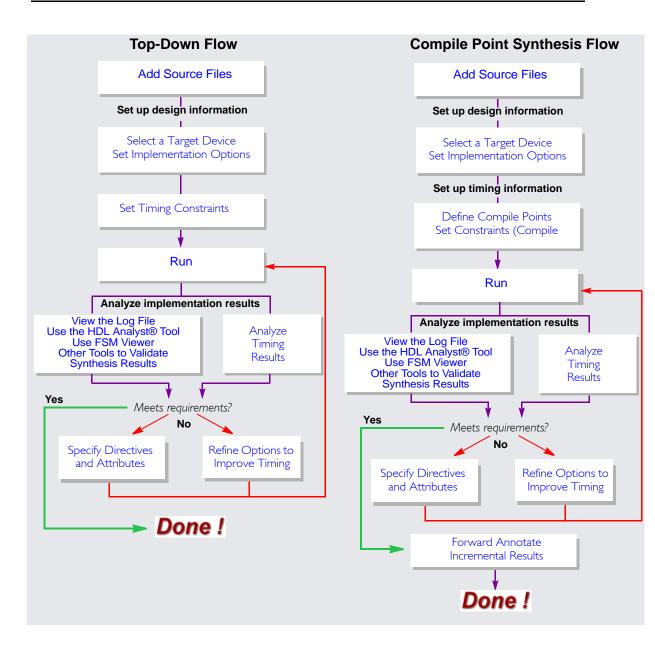

The following figure shows you two Synplify Pro flows with simple steps to trade off between timing and area to help you reach your goals quickly.

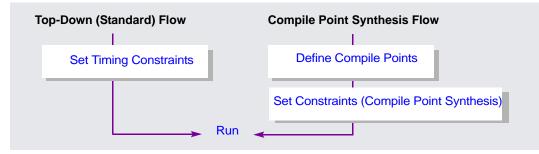

The top-down flow is the traditional synthesis flow with a global approach to synthesis. With the Compile Point Synthesis flow, you can design incrementally and synthesize only what is necessary.

## **Top-Down and Compile Point Design Flows**

A Compile Point Synthesis flow differs from a traditional top-down flow in that it divides the design into parts that can be processed independently or synthesized incrementally, using a team design approach. Unlike other bottom-up solutions, it is highly automated and eliminates the need for time consuming and error prone scripts. Compile point synthesis is based on compile points, which are smaller synthesis units of the main design that are treated as individual blocks.

The Compile Point Synthesis flow is available for certain design families. Check the Device tab of the Implementation Options dialog box for applicable technology families. For Altera designs, you can use this flow with the Altera Quartus II Incremental Compilation methodology to preserve design implementation data so as to make incremental place and route updates. Similarly, you can use the Xilinx Incremental flows with the place-and-route tool for team-based design. See the Synplify Pro software documentation and the appropriate application notes for details.

#### CHAPTER 3

# Set up Design Information

There are three basic tasks involved in setting up a design. Both the top-down and Compile Point Synthesis flows use the same design setup. Topics include:

- Add Source Files, on page 15

- Select a Target Device, on page 16

- Set Implementation Options, on page 17

# Add Source Files

After you have installed the software, set up the design project. Then, add source files.

Source files need to be ordered such that the top-level file is last in the source file list. If you have mixed language source files (a combination of Verilog and VHDL files), specify the top-level file using Implementation Options ->Verilog or VHDL tab, as shown below.

|                                                                                   |                              |        | Verilog            |

|-----------------------------------------------------------------------------------|------------------------------|--------|--------------------|

| Top Level Module:                                                                 | Compiler Directives and Para | meters |                    |

| eight_bit_uc         Verilog Language         Verilog 2001         System Verilog | Parameter Name               | E=8    | Extract Parameters |

| Allow Duplicate Modules                                                           | to Project File)             |        |                    |

| Library Directories:                                                              |                              |        |                    |

|                                                                                   |                              |        |                    |

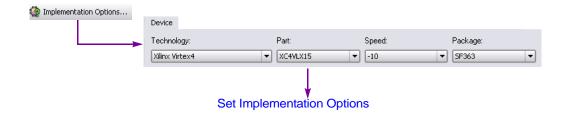

## Select a Target Device

Choose the technology family using the Device panel of the Implementation Options dialog box. Select the part, package, and speed grade, as applicable. Remember that the speed grade you choose has a direct impact on timing estimates. For the Compile Point Synthesis flow, you must select an appropriate technology family.

## Set Implementation Options

Set options for the synthesis run from the Options tab of the Implementation Options dialog box. Some of the global options that influence the tradeoff between speed and area include:

- State Machine Implementation

- Resource Sharing

- Pipelining

- Retiming

Some of these options can also be set on a per instance basis.

Formal Verification is a global option that provides a netlist compatible with the Cadence Conformal<sup>TM</sup> Equivalence Checker tool for design verification.

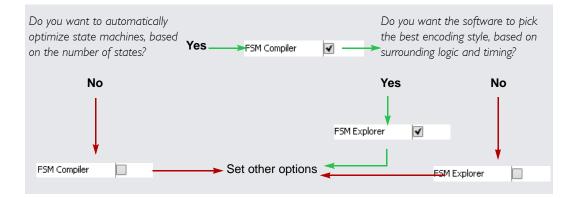

#### **State Machine Implementation**

Use the FSM Compiler and the FSM Explorer to automatically select encoding styles that determine how the state machines are implemented. The encoding style affects timing estimates. You also can define state machine implementations for individual instances using attributes such as syn\_encoding. You enable these options by selecting the FSM Compiler and FSM Explorer check boxes on the left side of the Project view.

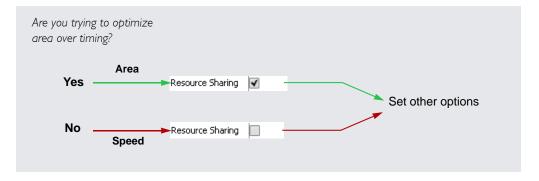

## **Resource Sharing**

Resource sharing is another option that influences the tradeoff between speed and area. Turn on this option when you want to optimize area. You enable this option by selecting the Resource Sharing check box on the left side of the Project view.

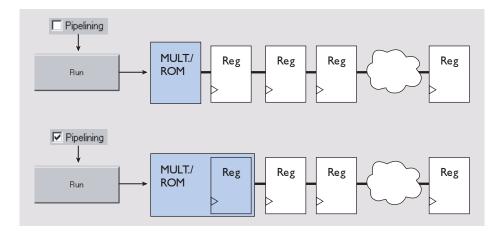

## Pipelining

Pipelining is available for certain device families only. Check the Device or Options tab of the Implementation Options dialog box for applicable technology families. You can either set the options globally or on individual registers.

Pipelining is the process of moving adjacent registers into multipliers or ROMs so as to increase throughput and ensure faster circuit performance. It does not add new register stages. The following figure shows you how to set it globally.

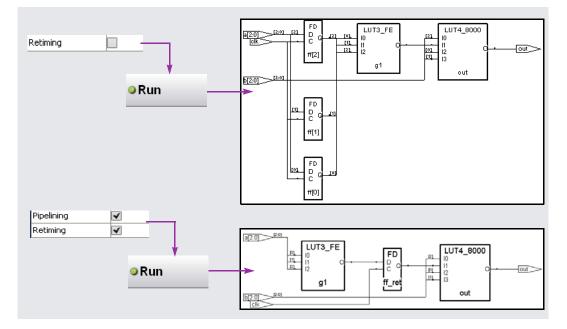

## Retiming

Retiming is available for certain device families only and is a technique related to pipelining. Retiming improves the timing performance of sequential circuits by automatically moving registers (register balancing) across combinatorial gates or LUTs. This process improves timing while ensuring identical behavior as seen from the primary inputs and outputs of the design. Retiming moves registers across gates or LUTs, but does not change the number of registers in a cycle or path from a primary input to a primary output. However, it can change the total number of registers in a design. The algorithm retimes only edge-triggered registers. It does not retime level-sensitive latches.

When you turn on the retiming option, pipelining is turned on automatically.

### **Formal Verification**

This option is available for certain device technologies, and lets you use the Cadence Conformal Equivalence Checker tool for formal design verification. In verification mode, the software generates files that are used by Conformal Equivalence Checker to verify equivalence between the RTL code and the post-synthesis netlist. Device

| ▼ XC4VLX15 ▼ | 1. [  |                           |

|--------------|-------|---------------------------|

|              | SF363 | <ul> <li>▼ -10</li> </ul> |

|              |       |                           |

|              |       | Value                     |

|              |       | •                         |

|              |       | 10000                     |

|              |       |                           |

|              |       |                           |

|              |       |                           |

|              |       |                           |

|              |       |                           |

|              |       | 3                         |

|              |       | 3                         |

|              |       |                           |

|              |       |                           |

|              |       |                           |

# CHAPTER 4 Set up Timing Information

Synplify Pro synthesis is timing-driven. Consequently, the more precise and complete the information you supply, the more accurate the timing estimates, and the closer the synthesized implementation is to your design goals. The Synplify Pro tool begins optimizing for area once your timing performance constraints are set.

Define timing goals through constraints. Constraint setup steps differ for the two flows:

Refer to the following topics:

- Set Timing Constraints, on page 24

- Set Constraints (Compile Point Synthesis), on page 26

- Run, on page 28

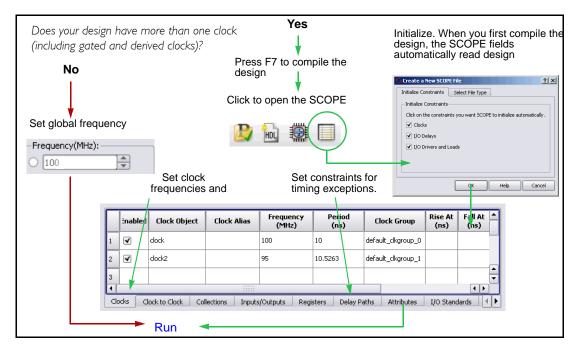

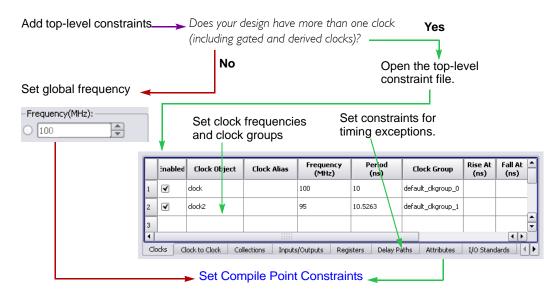

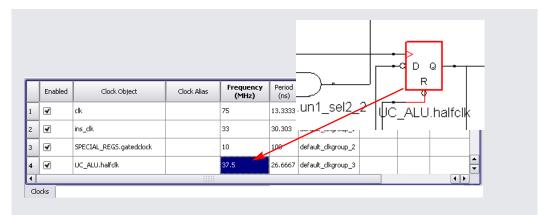

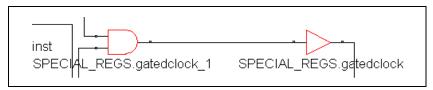

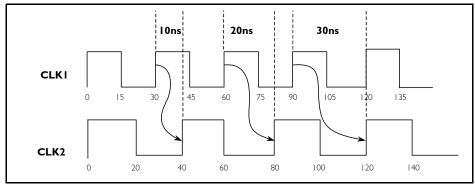

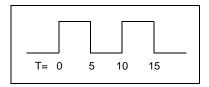

# Set Timing Constraints

As a minimum, you must set a global clock frequency, which can be done in the Project view or through the Constraints tab of the Implementation Options dialog box. However, using a global frequency alone is not recommended because this option sets all clocks to the same value and assigns them to the same clock group. Synthesis assumes that all clocks are related and calculates timing for every path between the clocks.

When using multiple-clock designs, you should specify clock frequencies for each clock. Also, define timing exceptions like false path and multi-cycle path constraints. For defining timing constraints, use the SCOPE<sup>®</sup> interface which makes it easy to enter constraint definitions.

# **Define Compile Points**

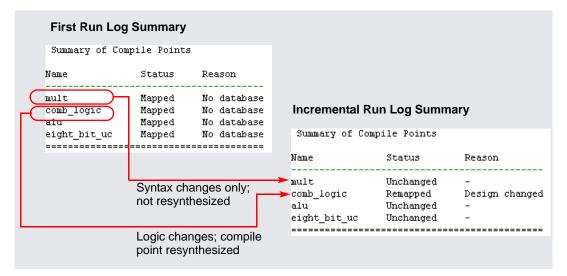

Compile points are design modules that act as relatively independent synthesis units: they have their own constraint files and are optimized individually. They are resynthesized only as needed, based on an analysis of design dependencies and the nature of design changes. The synthesis process for compile points is called the Compile Point Synthesis flow. In this incremental flow, compile points are defined through the SCOPE interface.

| With th design | ie c<br>inf | ompile<br>ormati | pile the desi<br>ed design, th<br>on is automa<br>PE fields | e –       |          |      | open tl<br>interfa |       |                                          |     | the Sele<br>evel, an |                 |   |                     |                     |   |

|----------------|-------------|------------------|-------------------------------------------------------------|-----------|----------|------|--------------------|-------|------------------------------------------|-----|----------------------|-----------------|---|---------------------|---------------------|---|

| select         | the         | e com            | mpile Points<br>bile point mo<br>ile, and add t             | dules. Sa | ave      |      |                    | Initi | ate a New Si<br>alize Constrain<br>Top L | ts  | Select File          | e Type<br>Level | Ĭ | Compile<br>npile Po | e Point<br>int Type | - |

| ĺ              |             | Enabled          |                                                             | Module    |          |      |                    | Тур   | e                                        |     | Comme                | nt              |   |                     |                     |   |

|                | 1           | •                |                                                             |           |          | -    | locked             |       |                                          |     |                      |                 |   |                     |                     |   |

|                | 2           |                  | prep4<br>ins decode                                         |           |          |      |                    |       |                                          |     |                      |                 |   |                     |                     |   |

|                | 3           |                  | prgm_cntr<br>reg file                                       |           |          |      |                    |       |                                          |     |                      |                 |   |                     |                     |   |

|                | 4           |                  | data_mux<br>alu                                             |           |          |      |                    |       |                                          |     |                      |                 |   |                     |                     |   |

|                | 5           |                  | mult<br>spcl_regs                                           |           |          |      |                    |       |                                          |     |                      |                 | _ |                     |                     |   |

|                | 6           |                  | io<br>INS_ROM                                               |           |          |      |                    |       |                                          |     |                      |                 |   |                     |                     |   |

|                | 7           |                  |                                                             |           |          |      |                    |       |                                          |     |                      |                 |   | ÷                   |                     |   |

|                | Co          | ollections       | Inputs/Outputs                                              | Registers | Delay Pa | aths | Attribu            | ites  | I/O Standards                            | Con | npile Points         | Other           | • |                     |                     |   |

Set Constraints (Compile Point Synthesis)

# Set Constraints (Compile Point Synthesis)

Set constraints at the top level and for each compile point.

## **Set Top-level Constraints**

In a Compile Point Synthesis flow, set top-level constraints as you do in a normal synthesis flow. See the following figure.

### **Set Compile Point Constraints**

Compile points can be nested. Parent compile points contain compile points within. Child compile points are nested within compile points. Parent constraints do not propagate to the child compile point, so you must set constraints for each compile point. However, compile point constraints are considered during synthesis of the parent.

select

|             |         |                                                         | ate a New SCOPE File                      | ct File Type                                        |                             |                                                         |                 | [               | ? ×              |     |  |

|-------------|---------|---------------------------------------------------------|-------------------------------------------|-----------------------------------------------------|-----------------------------|---------------------------------------------------------|-----------------|-----------------|------------------|-----|--|

|             |         |                                                         |                                           | ) Top Level 🔵                                       | Block Level                 | <ul> <li>Compile Point</li> </ul>                       | -               |                 |                  |     |  |

|             |         | Selec                                                   | t a Module                                |                                                     |                             | Compile Point                                           | Туре            |                 | -                |     |  |

|             |         |                                                         | ROM                                       |                                                     |                             | default                                                 |                 |                 | -                |     |  |

|             |         |                                                         | _mux<br>decode                            |                                                     |                             | Selectdefau<br>compile point I<br>your current t        | type (soft)     |                 | rve              |     |  |

|             |         |                                                         | ecify I/O dela<br>or the compile          |                                                     | et                          |                                                         | , por           |                 |                  |     |  |

|             |         | e clocks, sp<br>onstraints fo                           | ecify I/O dela<br>or the compile          |                                                     | ROM_cp.sd                   |                                                         |                 | E-II AL         |                  |     |  |

| F           |         | e clocks, sp                                            | ecify I/O dela<br>or the compile          | point                                               |                             |                                                         | Rise At<br>(ns) | Fall At<br>(ns) | Duty Cycl<br>(%) |     |  |

| F           | DORT CO | e clocks, sp<br>onstraints fo                           | ecify I/O dela<br>or the compile<br>C\syn | point                                               | ROM_cp.sd                   | `<br> c *                                               | Rise At         |                 | Duty Cycl        |     |  |

| F           | DORT CO | e clocks, sp<br>onstraints fo<br>Clock Object           | ecify I/O dela<br>or the compile<br>C\syn | point                                               | ROM_cp.sd<br>Period<br>(ns) | Clock Group                                             | Rise At         |                 | Duty Cycl        |     |  |

| F           | Enabled | e clocks, sp<br>onstraints fo<br>Clock Object           | ecify I/O dela<br>or the compile<br>C\syn | point                                               | ROM_cp.sd<br>Period<br>(ns) | Clock Group                                             | Rise At         |                 | Duty Cycl        |     |  |

| F<br>1<br>2 | Enabled | e clocks, sp<br>onstraints fo<br>Clock Object           | ecify I/O dela<br>or the compile<br>C\syn | point                                               | ROM_cp.sd<br>Period<br>(ns) | Clock Group                                             | Rise At         |                 | Duty Cycl        | e • |  |

| F<br>1<br>2 | Enabled | e clocks, sp<br>onstraints fo<br>Clock Object<br>clock2 | ecify I/O dela<br>or the compile<br>C\syn | Point<br>Stify_pro1\INS<br>Frequency<br>(MHz)<br>95 | ROM_cp.sd<br>Period<br>(ns) | Clock Group<br>default_clkgroup_1<br>default_clkgroup_2 | Rise At         | (ns)            | Duty Cycl<br>(%) | e • |  |

## Run

After you have set all the options and constraints, click Run. View the results of synthesis in the log file, or analyze them graphically using various built-in tools.

| oRun − | <br>one !> | Analyze Results<br>Analyze Timing Results |

|--------|------------|-------------------------------------------|

|        |            |                                           |

### CHAPTER 5

# Analyze Results

There are many ways in which you can check the implementation results. Use any of the following tools:

- View the Log File, on page 31

- Use the HDL Analyst® Tool, on page 31

- Use FSM Viewer, on page 45

- Other Tools to Validate Synthesis Results, on page 48

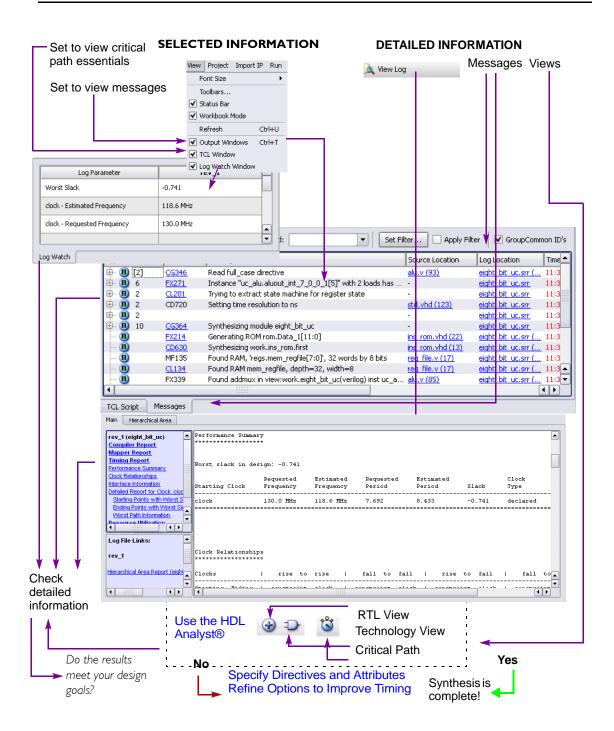

A summary is shown in the figure below.

## View the Log File

The log file contains detailed information about the synthesis results, including details of the most critical paths, the number of primitives in the netlist, and the FSM encoding style. It is a good idea to run place and route even if the log file reports a timing goal failure. This is due to the fact the Synplify Pro tool is not knowledgeable about the final placement and routing of your design. The timing data given in the log file is an estimate.

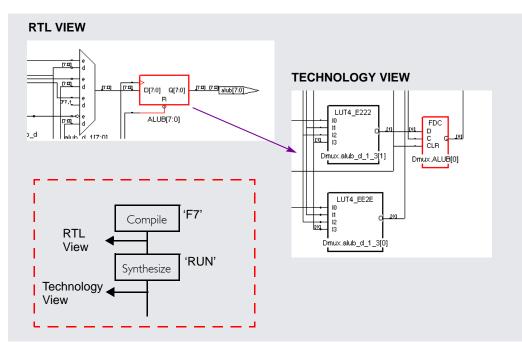

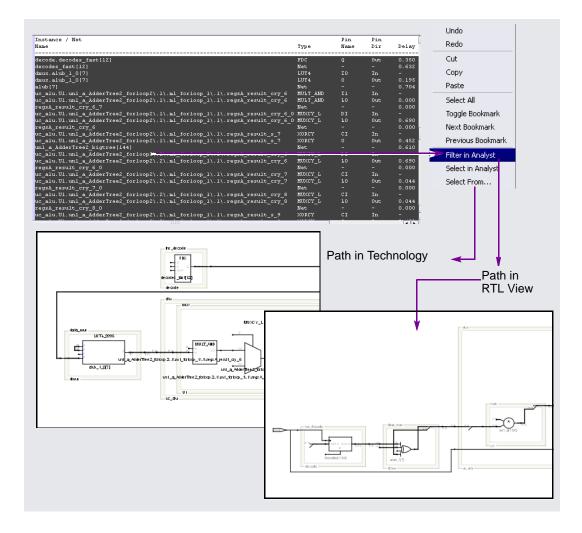

## Use the HDL Analyst® Tool

The HDL Analyst environment provides graphical means to debug and analyze your design at two different stages of the design process: compilation (RTL View) and mapping (Technology View). The software maintains the names extracted from your code, so you can more easily follow the mapping of the logic from RTL to Technology view.

In addition to the RTL and Technology views and the timing analysis features (described separately in Analyze Timing Results, on page 69), the HDL Analyst tool has the following features that help you debug your implementation.

- Design Hierarchy Exploration Tools

- Advanced Find Capabilities

- Filtered and Flattened Views

- Crossprobing Across Views

- Cross-tool Crossprobing

- Other Options

- Mouse Strokes

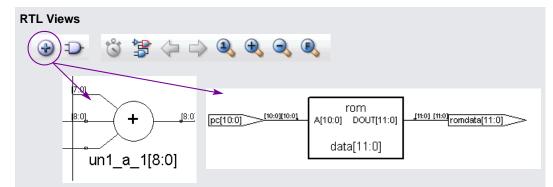

## **RTL View**

This view shows the design after it is compiled. The software extracts the structure implied by the HDL language. The RTL view does not display target-specific components, so components are represented in a generic style.

To open the RTL view you must have a compiled design (use F7 to compile or click Run to synthesize). Then click on the icon, as shown in this figure:

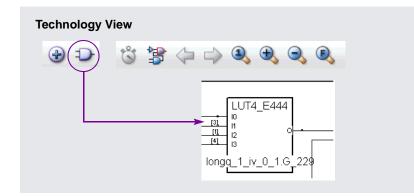

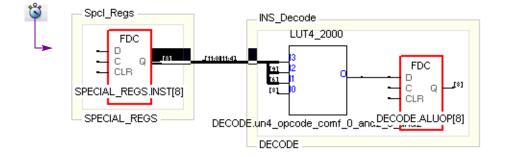

### **Technology View**

This view shows the design after synthesis is complete. The design is optimized and mapped to components that are specific to the target architecture. If the technology has the structure, a DFF with synchronous reset is mapped to a synchronous reset DFF.

The technology view shows you how the generic RTL structure is implemented for your technology. You also can view the critical path.

To open the Technology view, you must have a synthesized design (click Run to synthesize). Then click on the icon shown in the following figure:

### **Design Hierarchy Exploration Tools**

Since most large designs are hierarchical, the Synplify Pro HDL Analyst tool helps you view hierarchy details and put the details in context. You can browse and navigate hierarchy with Push/Pop mode and the Hierarchy Browser.

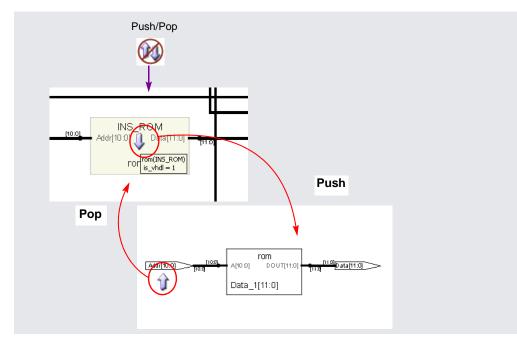

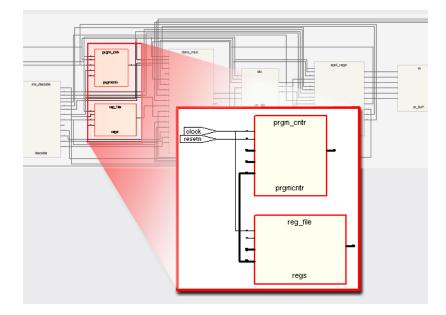

#### Push/Pop Mode

You can navigate design hierarchy by pushing down into a high-level schematic object and popping back up. Pushing down into an object takes you to a lower-level schematic that shows the internal logic of the object. Popping up from a lower level brings you back to the parent higher-level object. You cannot pop up from the top level.

You can push down into the following kinds of schematic objects:

- Non-hidden hierarchical instances. To push into a hidden instance, unhide it first.

- Technology-specific primitives (not logic primitives)

- Inferred ROMs<sup>1</sup> and state machines in RTL views. Inferred ROMs, RAMs, and state machines do not appear in Technology views, because they are resolved into technology-specific primitives.

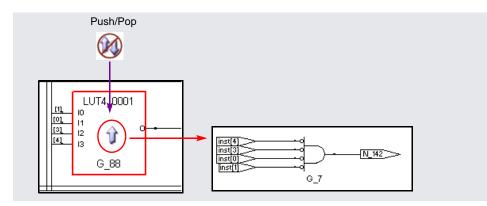

Click on the Push/Pop icon to traverse the design hierarchy. These cursors appear (1) and (1) when the design hierarchy can be traversed. This cursor appears (1) when the design hierarchy has reached its lowest or highest level.

Push or pop as follows:

• To *pop*, place the pointer in an empty area of the schematic background, then click or use the appropriate mouse stroke. See Mouse Strokes, on page 44.

<sup>1.</sup> An inferred ROM is one that is created during synthesis; the ROM is not instantiated in your RTL code.

• To *push* into an object, place the mouse pointer over the object and click or use the appropriate mouse stroke. See Mouse Strokes, on page 44.

The following figure shows an additional use for the Push/Pop icon. You can push into a lookup table in a Technology view and check the mapped functions.

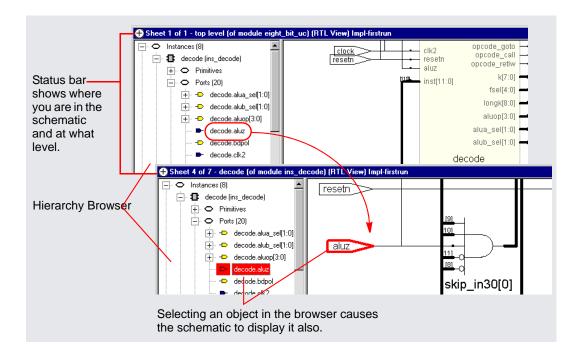

#### **Hierarchy Browser Navigation**

When you open an RTL view or a Technology view, the Hierarchy Browser appears in the left pane of the view. The browser in the RTL view displays the hierarchy specified in the RTL design description; in the Technology view it displays the hierarchy after mapping.

A schematic and its associated Hierarchy Browser are linked so that you can crossprobe objects between them. Selecting an object in one displays it in the other.

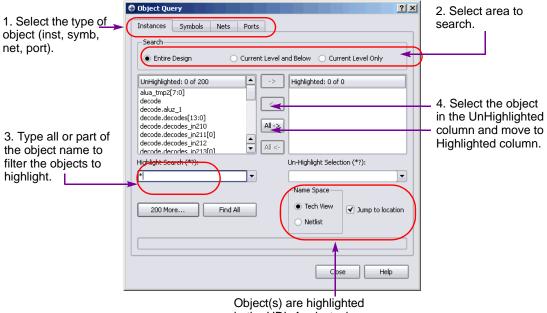

### **Advanced Find Capabilities**

You can locate objects using the command Edit -> Find. In an HDL Analyst view, this displays the Object Query dialog box, which lists candidate schematic objects by type (Instances, Symbols, Nets, or Ports) and lets you use wildcards to find objects by name.

You can find objects at any level of your design:

- Entire Design (all levels at once)

- Current Level & Below

- Current Level Only

All found objects are selected, whether or not they are displayed in the current schematic, so that you then can perform other operations on them.

in the HDL Analyst. views.

### **Filtered and Flattened Views**

Filtering is a useful first step in analysis, because it focuses analysis on the relevant parts of the design. Flattening eliminates the hierarchy of the design. Default flattening operations are global: the entire design is flattened from the current level down.

#### Filtering

A filtered schematic shows a subset of your design.

Any command that results in a filtered schematic is a filtering command. Some commands, like the Expand commands, increase the amount of logic displayed, but they are still considered filtering commands because the resulting view is still a subset. Other commands like Filter Schematic remove objects from the current display.

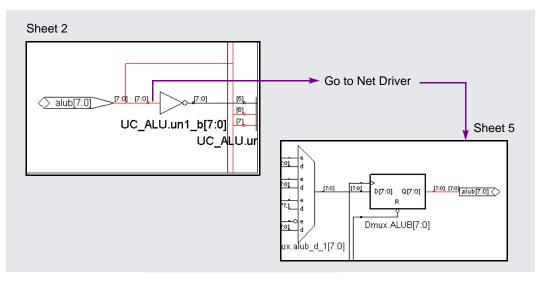

You can use filtering commands to trace signals at a single level of hierarchy or across the entire design. If you select a net, then right-click in the view and select Go to Net Driver, the view highlights the element driving the selected net. If the driver is on another schematic sheet, the software automatically moves to the correct sheet.

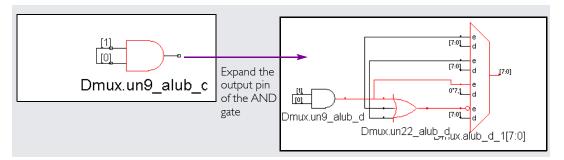

Similarly, you can start with the output of an AND gate, and use the Expand command to see what this gate drives:

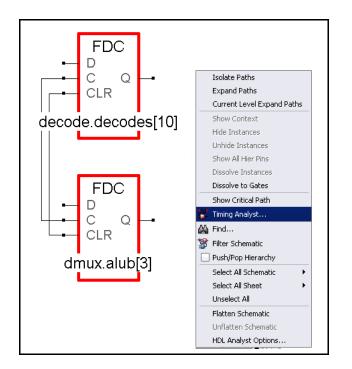

Right-click in the HDL Analyst views to access the pop-up menu. The following table lists the most common filtering commands:

| Filtering Command                  | Description                                                               |

|------------------------------------|---------------------------------------------------------------------------|

| Filter Schematic, Isolate Paths    | Reduces the displayed logic.                                              |

| Dissolve Instances (filtered view) | Makes selected instances transparent, exposing their lower-level details. |

| Filtering Command                                                                                                | Description                                        |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Expand<br>Expand to Register/Port<br>Expand Paths<br>Expand Inwards<br>Select Net Driver<br>Select Net Instances | Displays logic connected to the current selection. |

| Show Critical Path<br>Flattened Critical Path<br>Hierarchical Critical Path                                      | Shows critical paths.                              |

### Flattening

A flattened schematic contains no hierarchical objects. The flattening commands shown below are from the HDL Analyst menu. The most versatile commands are Dissolve Instances and Flatten Current Schematic, which you can also use for selective flattening.

| Command                                             | Unfiltered Schematic                                                                                                                                         | Filtered Schematic                                                                                                                      |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Dissolve Instances                                  | Flattens selected instances                                                                                                                                  |                                                                                                                                         |

| Flatten Current<br>Schematic (Flatten<br>Schematic) | Flattens at the current level<br>and all lower levels. RTL view:<br>flattens to generic logic level<br>Technology view: flattens to<br>technology-cell level | Flattens only non-hidden<br>transparent hierarchical<br>instances; opaque and<br>hidden hierarchical<br>instances are not<br>flattened. |

| RTL -> Flattened View                               | Creates a new, unfiltered RTL<br>schematic of the entire<br>design, flattened to the level<br>of generic logic cells.                                        |                                                                                                                                         |

| Technology -><br>Flattened View                     | Creates a new, unfiltered<br>Technology schematic of the<br>entire design, flattened to the<br>level of technology cells.                                    |                                                                                                                                         |

| Command                                     | Unfiltered Schematic                                                                                                                                                                                                                                                         | Filtered Schematic |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Technology -><br>Flattened to Gates<br>View | Creates a new, unfiltered<br>Technology schematic of the<br>entire design, flattened to the<br>level of Boolean logic gates.<br>Creates a filtered, flattened<br>Technology view schematic<br>that shows only the instances<br>with the worst slack times<br>and their path. |                    |

| Technology -><br>Flattened Critical Path    | Creates a new, unfiltered<br>Technology schematic of the<br>entire design, flattened to the<br>level of Boolean logic gates.<br>Creates a filtered, flattened<br>Technology view schematic<br>that shows only the instances<br>with the worst slack times<br>and their path. |                    |

| Unflatten Schematic                         | Undoes any flattening done<br>by Dissolve Instances and<br>Flatten Current Schematic at<br>the current schematic level.<br>Returns to the original<br>schematic, as it was before<br>flattening (and any filtering).                                                         |                    |

### **Crossprobing Across Views**

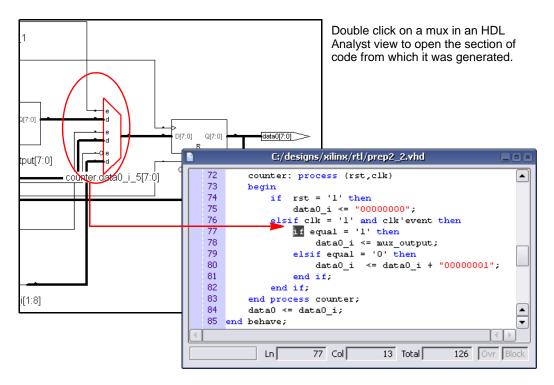

You can crossprobe between HDL Analyst views, the Text Editor, the Tcl window, and the FSM viewer, because the views are tightly linked to your code. Double-clicking on a component in a HDL Analyst view takes you to the section of code from which it was generated. If you double click a mux, you open the section of code from which it was generated. In this example, the mux is generated from the VHDL case statement shown.

Conversely, you can select a section of code from the Text Editor and the corresponding RTL gates for that code are highlighted in the RTL view. You must first have an RTL view open. Then, select the code in the source file. You can crossprobe from any text file, for instance, place-and-route files.

To see just the structures that correspond to the selected code on one sheet, click Filter icon. This isolates the selected structures on one schematic sheet. Click the Back icon to return to the previous view.

### **Cross-tool Crossprobing**

The Synplify Pro software allows easy crossprobing between Synplify Pro processes and several other third-party tools:

• Altera Quartus Place & Route software allows bidirectional crossprobing between Quartus II Floorplanner and the Synplify Pro synthesis tool's HDL Analyst tool.

• Xilinx Place & Route software allows crossprobing from the Xilinx timing file (.twr) to the HDL Analyst tool.

The Synplify Pro software also crossprobes between Synplify Pro processes. When two copies of the Synplify Pro tool are running simultaneously on one machine, enabling crossprobing allows both HDL Analyst tools to communicate with each other. For example, if external crossprobing is engaged and the same design is open in two copies of the software, selecting an instance in the HDL Analyst tool in one copy of the Synplify Pro tool results in the same instance being highlighted in the HDL Analyst tool of the second Synplify Pro tool.

### **Other Options**

There are a number of useful options you can set using the Options -> HDL Analyst Options command. For example, you can view cell interiors in the Technology view, like the LUTs in this figure:

| HDL Analyst Options     Y      Text General Sheet Size Visual Properties     |                          |                           |

|------------------------------------------------------------------------------|--------------------------|---------------------------|

| Text General Sheet Size Visual Properties<br>General options<br>Set Defaults | Show Cell<br>Interior On | Show Cell<br>Interior Off |

| Compact symbols Show cell interior                                           | LUT2_E                   |                           |

| Show sheet connector index Compress buses                                    | G_133                    | G_133                     |

| No buses in flattened technology view Dissolve levels:                       | LUT3_FE                  |                           |

| Instances added for expansion: 2000                                          | G_140                    | G_140                     |

| OK Cancel Help                                                               |                          |                           |

You can copy images from any schematic view to the clipboard. To do so, open a schematic view, and select Edit -> Copy Image. The cursor changes to a camera. Hold down the left button and drag the cursor to define the rectangular area you want to capture, and then release the button. The image is copied to the clipboard.

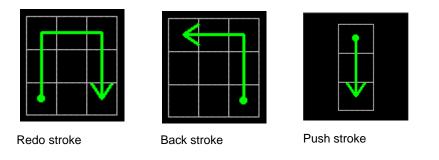

### **Mouse Strokes**

To access several frequently used menu commands, you can use the mouse while holding down the right mouse button as you draw the pattern. The mouse strokes you draw are interpreted on an invisible grid of one or three rows, depending on the stroke.

For information about all the mouse strokes, select Help -> Mouse Stroke Tutor.

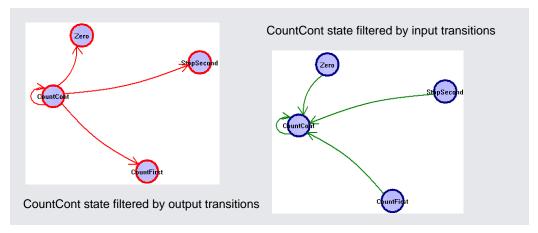

# Use FSM Viewer

The FSM (finite state machine) viewer is a graphic analysis tool that displays state transition bubble diagrams and implementation information for FSMs in the design. You can use this viewer to view state machines implemented by either the FSM Compiler or the FSM Explorer.

- 1. To start the FSM viewer, open the RTL view and either

- Select the FSM instance, click the right mouse button and select View FSM from the popup menu.

- Push down into the FSM instance using the Push/Pop icon or the command from the popup menu.

The FSM viewer opens. The viewer consists of a transition bubble diagram and a table for the encoding and transitions.

2. The following table summarizes basic analysis operations.

| To View                                                                              | Do this                                                                                                      |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| From and to states, and conditions for each transition                               | Click the Transitions tab at the bottom of the table.                                                        |

| The correspondence between the states<br>and the FSM registers in the RTL view       | Click the RTL Encoding tab.                                                                                  |

| The correspondence between the states<br>and the registers in the Technology<br>View | Click the Mapped Encodings tab<br>(available after synthesis).                                               |

| Only the transition diagram without the table                                        | Select View -> FSM table or click the FSM<br>Table icon. You might have to scroll to<br>the right to see it. |

This figure shows you the mapping information for a state machine. The Transitions tab shows you simple equations for conditions for each state. The RTL Encodings tab has a State column that shows the state names in the source code, and a Registers column for the corresponding RTL encoding. The Mapped Encoding tab shows the state names in the code mapped to actual values.

|                                      | Viewer cur                                                                                                      |                                                                                                                                                                                | Cauntor                                                                                                                                                                                     | HE                                         | Stop Step and<br>Stop First                                                                                                          | -                                                    |                                                                                                                                                                              |                                                                                                     | Bubble Diagram   |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|

|                                      |                                                                                                                 | To State                                                                                                                                                                       |                                                                                                                                                                                             |                                            | Condition                                                                                                                            |                                                      |                                                                                                                                                                              | <u> </u>                                                                                            |                  |

| 2                                    |                                                                                                                 |                                                                                                                                                                                | p&!Start&!Reset<br>ip&!Start&!Reset                                                                                                                                                         |                                            |                                                                                                                                      |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

| 4                                    |                                                                                                                 |                                                                                                                                                                                | p&!Start&!Reset                                                                                                                                                                             |                                            |                                                                                                                                      |                                                      |                                                                                                                                                                              | - 1                                                                                                 |                  |

| 5                                    |                                                                                                                 | topSecond Sta                                                                                                                                                                  | art&!Reset                                                                                                                                                                                  |                                            |                                                                                                                                      |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

| Ĩ ► \                                | Transitions /                                                                                                   | RTL Encoding                                                                                                                                                                   | as 🖌 Mapped Enco                                                                                                                                                                            | dings / 🔳                                  |                                                                                                                                      |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

|                                      |                                                                                                                 |                                                                                                                                                                                |                                                                                                                                                                                             |                                            |                                                                                                                                      |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

|                                      | <b>1</b>                                                                                                        | L                                                                                                                                                                              |                                                                                                                                                                                             |                                            |                                                                                                                                      |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

| í                                    | From State                                                                                                      | To State                                                                                                                                                                       |                                                                                                                                                                                             |                                            |                                                                                                                                      | _                                                    |                                                                                                                                                                              |                                                                                                     |                  |

|                                      |                                                                                                                 |                                                                                                                                                                                |                                                                                                                                                                                             |                                            | Condition                                                                                                                            |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

| 1                                    |                                                                                                                 |                                                                                                                                                                                | Laplevel&Reset                                                                                                                                                                              |                                            | Condition                                                                                                                            |                                                      |                                                                                                                                                                              |                                                                                                     |                  |

| 1                                    | LapDisplay<br>Zero                                                                                              | LapDisplay<br>LapDisplay                                                                                                                                                       | Laplevel&!Reset<br>Lap&!Start&!Reset                                                                                                                                                        |                                            | Condition                                                                                                                            | _                                                    | •                                                                                                                                                                            |                                                                                                     |                  |

| 1<br>2<br>3                          | LapDisplay<br>Zero                                                                                              | LapDisplay<br>LapDisplay                                                                                                                                                       | · ·                                                                                                                                                                                         |                                            | Condition                                                                                                                            | _                                                    | tate Degis                                                                                                                                                                   | tor                                                                                                 |                  |

| 2                                    | LapDisplay<br>Zero                                                                                              | LapDisplay<br>LapDisplay<br>StopSecond                                                                                                                                         | Lap&!Start&!Reset                                                                                                                                                                           | t                                          | Condition                                                                                                                            |                                                      | itate Regis                                                                                                                                                                  |                                                                                                     |                  |

| 3                                    | LapDisplay<br>Zero<br>StopSecond                                                                                | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond                                                                                                                           | Lap&!Start&!Reset<br>!Lap&!Start&!Rese                                                                                                                                                      | t                                          | Condition                                                                                                                            | Zero                                                 | cur_sta                                                                                                                                                                      | te[0]                                                                                               |                  |

| 2<br>3<br>4                          | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond                                        | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopDiff                                                                                                               | Lap&!Start&!Reset<br>!Lap&!Start&!Rese<br>Lap&!Start&!Reset                                                                                                                                 | t<br>t                                     | Condition                                                                                                                            | Zero                                                 |                                                                                                                                                                              | te[0]<br>te[1]                                                                                      |                  |

| 2<br>3<br>4<br>5<br>6<br>7           | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond<br>StopDiff                            | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopDiff<br>StopDiff                                                                                                   | Lap&IStart&IReset<br>ILap&IStart&IReset<br>Lap&IStart&IReset<br>Start&IReset<br>Lap&IStart&IReset<br>ILap&IStart&IReset                                                                     | t<br>:<br>:<br>t                           | Condition                                                                                                                            | Zero                                                 | tFirst cur_stantCont cur_sta                                                                                                                                                 | tte[0]<br>tte[1]<br>tte[2]                                                                          |                  |

| 2<br>3<br>4<br>5<br>6<br>7<br>8      | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond<br>StopDiff<br>StopFirst               | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopDiff<br>StopDiff<br>StopFirst                                                                                      | Lap&IStart&IReset<br>ILap&IStart&IReset<br>Lap&IStart&IReset<br>Start&IReset<br>Lap&IStart&IReset<br>ILap&IStart&IReset<br>ILap&IStart&IRese                                                | t<br>:<br>:<br>t                           | Condition                                                                                                                            | Cour<br>Cour<br>Stop                                 | cur_sta<br>ntFirst cur_sta<br>ntCont cur_sta<br>First cur_sta<br>Diff cur_sta                                                                                                | nte[0]<br>nte[1]<br>nte[2]<br>nte[3]<br>nte[4]                                                      |                  |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond<br>StopDiff<br>StopFirst<br>CountFirst | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopSecond<br>StopDiff<br>StopDiff<br>StopFirst<br>StopFirst                                                           | Lap&IStart&Reset<br>ILap&IStart&Reset<br>Lap&IStart&Reset<br>Start&Reset<br>Lap&IStart&Reset<br>ILap&IStart&Reset<br>Lap&IStart&Reset                                                       | t<br>:<br>:<br>t                           | Condition                                                                                                                            | Zerc<br>Cour<br>Cour<br>Stop<br>Stop                 | cur_sta<br>ntFirst cur_sta<br>ntCont cur_sta<br>First cur_sta<br>Diff cur_sta<br>Second cur_sta                                                                              | tte[0]<br>tte[1]<br>tte[2]<br>tte[3]<br>tte[4]<br>tte[5]                                            |                  |

| 2<br>3<br>4<br>5<br>6<br>7<br>8      | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond<br>StopDiff<br>StopFirst               | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopSecond<br>StopDiff<br>StopDiff<br>StopFirst<br>StopFirst                                                           | Lap&IStart&IReset<br>ILap&IStart&IReset<br>Lap&IStart&IReset<br>Start&IReset<br>Lap&IStart&IReset<br>ILap&IStart&IReset<br>ILap&IStart&IRese                                                | t<br>:<br>:<br>t                           | Condition                                                                                                                            | Zerc<br>Cour<br>Cour<br>Stop<br>Stop                 | cur_sta<br>ntFirst cur_sta<br>ntCont cur_sta<br>First cur_sta<br>Diff cur_sta                                                                                                | tte[0]<br>tte[1]<br>tte[2]<br>tte[3]<br>tte[4]<br>tte[5]                                            |                  |

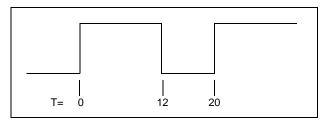

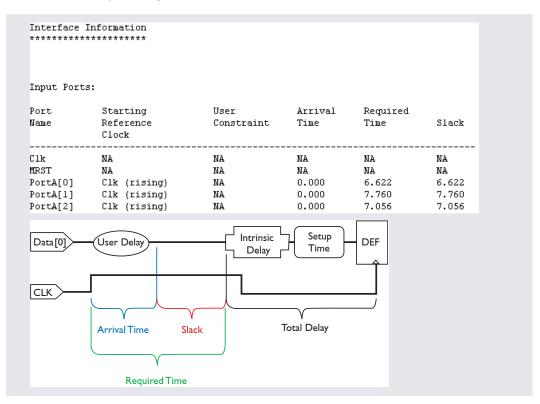

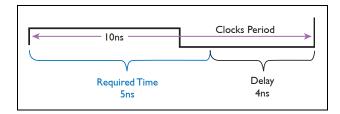

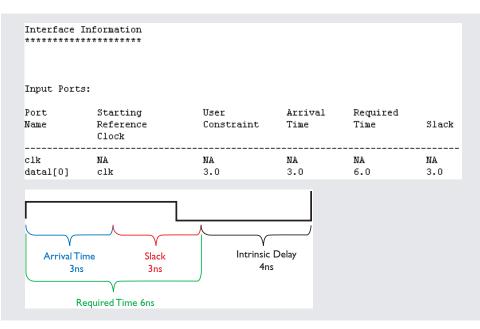

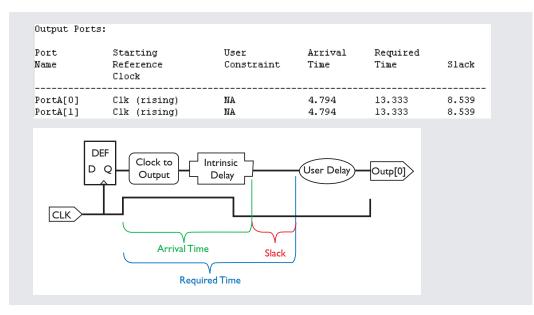

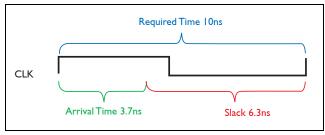

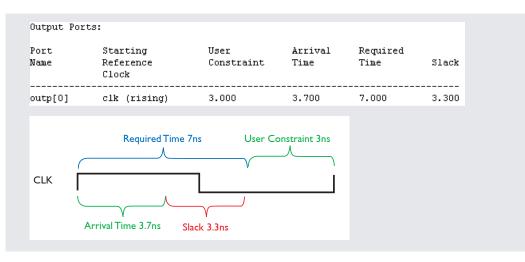

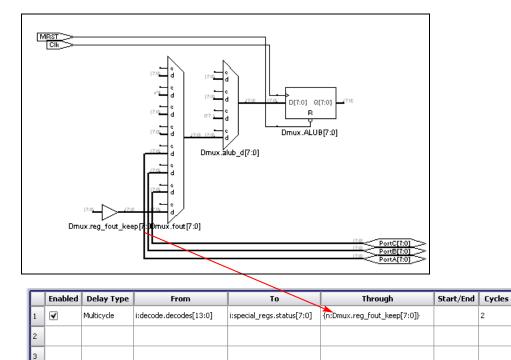

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | LapDisplay<br>Zero<br>StopSecond<br>StopFirst<br>CountCont<br>StopSecond<br>StopDiff<br>StopFirst<br>CountFirst | LapDisplay<br>LapDisplay<br>StopSecond<br>StopSecond<br>StopSecond<br>StopDiff<br>StopDiff<br>StopFirst<br>StopFirst                                                           | Lap&IStart&Reset<br>ILap&IStart&Reset<br>Lap&IStart&Reset<br>Start&Reset<br>Lap&IStart&Reset<br>ILap&IStart&Reset<br>Lap&IStart&Reset                                                       | t<br>:<br>:<br>t                           | Condition                                                                                                                            | Zerc<br>Cour<br>Cour<br>Stop<br>Stop                 | cur_sta<br>ntFirst cur_sta<br>ntCont cur_sta<br>First cur_sta<br>Diff cur_sta<br>Second cur_sta                                                                              | tte[0]<br>tte[1]<br>tte[2]<br>tte[3]<br>tte[4]<br>tte[5]                                            |                  |