# Synopsys FPGA Synthesis User Guide

June 2009

http://solvnet.synopsys.com

### **Disclaimer of Warranty**

Synopsys, Inc. makes no representations or warranties, either expressed or implied, by or with respect to anything in this manual, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose of for any indirect, special or consequential damages.

### **Copyright Notice**

Copyright © 2009 Synopsys, Inc. All Rights Reserved.

Synopsys software products contain certain confidential information of Synopsys, Inc. Use of this copyright notice is precautionary and does not imply publication or disclosure. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the prior written permission of Synopsys, Inc. While every precaution has been taken in the preparation of this book, Synopsys, Inc. assumes no responsibility for errors or omissions. This publication and the features described herein are subject to change without notice.

### Trademarks

### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, Design Compiler, DesignWare, Formality, HDL Analyst, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SiVL, SCOPE, Simply Better Results, SNUG, SolvNet, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

### Service Marks (SM)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

### **Restricted Rights Legend**

Government Users: Use, reproduction, release, modification, or disclosure of this commercial computer software, or of any related documentation of any kind, is restricted in accordance with FAR 12.212 and DFARS 227.7202, and further restricted by the Synopsys Software License and Maintenance Agreement. Synopsys, Inc., Synplicity Business Group, 600 West California Avenue, Sunnyvale, CA 94086, U. S. A.

Printed in the U.S.A June 2009

# Contents

### **Chapter 1: Introduction**

| The Synopsys FPGA Product Family       22         The FPGA Synthesis Tools       22         Synopsys FPGA Tool Features       23            |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Scope of the Document       26         The Document Set       26         Audience       26                                                  |

| Getting Started       27         Starting the Software       27         Getting Help       27         Requesting Technical Support       28 |

| User Interface Overview                                                                                                                     |

### **Chapter 2: FPGA Logic and Physical Synthesis Flows**

| Logic Synthesis Design Flow                                                                                                                                                                                                                                                                                                                                                                                                  | 32                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Synplify Premier Synthesis Design Flows         Logic Synthesis with Enhanced Optimization         Design Plan-Based Logic Synthesis         Graph-Based Physical Synthesis         Graph-Based Physical Synthesis with Design Planner         Design Plan-based Physical Synthesis                                                                                                                                          | 36<br>38<br>42<br>46       |

| Actel Physical Synthesis       Set up the Actel Physical Synthesis Project         Run Logic Synthesis for the Actel Physical Synthesis Flow       Set up Actel Physical Synthesis Results for Actel Physical Synthesis         Validate Logic Synthesis Results for Actel Physical Synthesis       Set up Actel Physical Constraints         Run Actel Physical Synthesis       Analyze Results of Actel Physical Synthesis | 52<br>56<br>56<br>57<br>57 |

| Altera Physical Synthesis | . 60<br>. 61<br>. 65<br>. 66<br>. 66          |

|---------------------------|-----------------------------------------------|

| Xilinx Physical Synthesis | .70<br>.74<br>.75<br>.75<br>.75<br>.75<br>.77 |

| Prototyping Design Flow   | . 80                                          |

### **Chapter 3: Preparing the Input**

| Setting Up HDL Source Files       8         Creating HDL Source Files       8         Checking HDL Source Files       8         Editing HDL Source Files with the Built-in Text Editor       8         Setting Editing Window Preferences       8         Using an External Text Editor       9         Using Hyper Source       9                                                                  | 2<br>3<br>5<br>8<br>0 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Using Mixed Language Source Files                                                                                                                                                                                                                                                                                                                                                                   | 5                     |

| Working with Constraint Files       9         When to Use Constraint Files over Source Code       9         Tcl Syntax Guidelines for Constraint Files       9         Using a Text Editor for Constraint Files       10         Using Synopsys Design Compiler Constraints       10         Checking Constraint Files       10         Generating Constraint Files for Forward Annotation       10 | 8<br>9<br>0<br>2<br>4 |

| Using Input from Related Tools                                                                                                                                                                                                                                                                                                                                                                      | 6                     |

| Converting Synopsys DesignWare Components                                                                                                                                                                                                                                                                                                                                                           | 7                     |

### **Chapter 4: Working with IP Input**

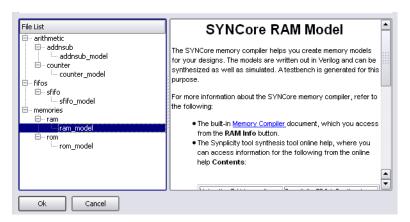

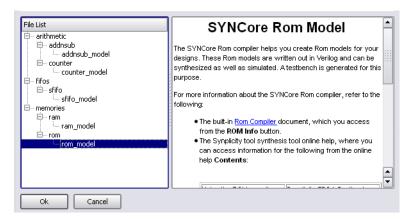

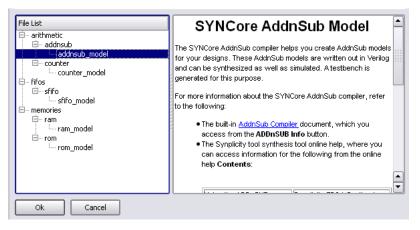

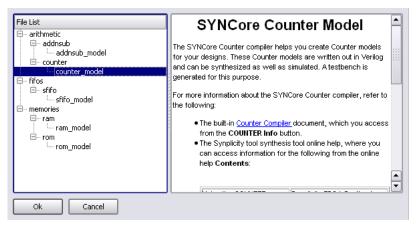

| Generating IP with SYNCore       11         Specifying FIFOs with SYNCore       11         Specifying RAMs with SYNCore       11         Specifying ROMs with SYNCore       12         Specifying Adder/Subtractors with SYNCore       13         Specifying Counters with SYNCore       13                                                                                                                                            | 14<br>19<br>25<br>30       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

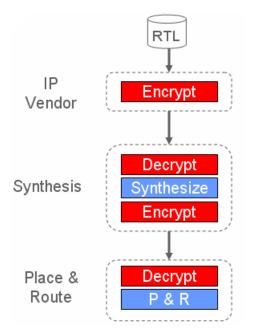

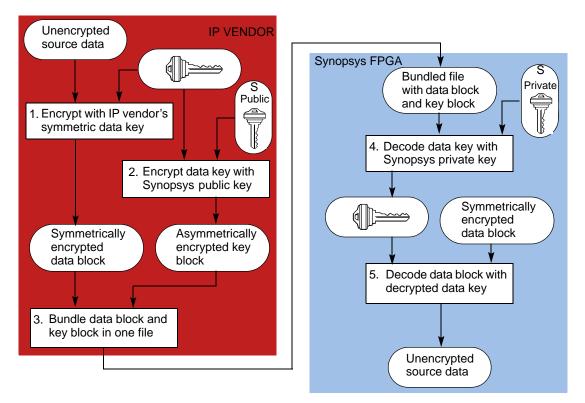

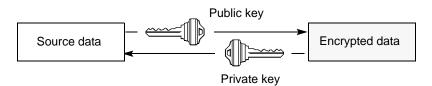

| The ReadyIP Encryption Flow       14         Overview of the Synopsys ReadyIP Flow       14         Encryption and Decryption       14                                                                                                                                                                                                                                                                                                 | 43                         |

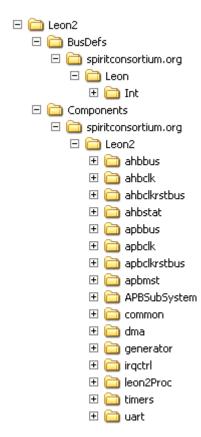

| Working with Encrypted IP       14         Encrypting Your IP       14         Preparing the IP Package       15         Evaluating Vendor IP       15                                                                                                                                                                                                                                                                                 | 48<br>53                   |

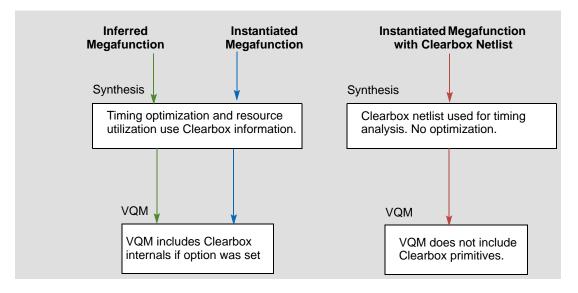

| Working with Altera IP       16         Using Altera LPMs or Megafunctions in Synthesis       16         Implementing Megafunctions with Clearbox Models       16         Implementing Megafunctions with Grey Box Models       17         Including Altera MegaCore IP Using an IP Package       18         Including Altera Processor Cores Generated in SOPC Builder       18         Working with SOPC Builder Components       19 | 61<br>65<br>75<br>81<br>86 |

| Working with Lattice IP                                                                                                                                                                                                                                                                                                                                                                                                                | 94                         |

| Working with Xilinx IP       19         Xilinx IP Cores       19         Including Xilinx Cores for Logic and Physical Synthesis       19                                                                                                                                                                                                                                                                                              | 95                         |

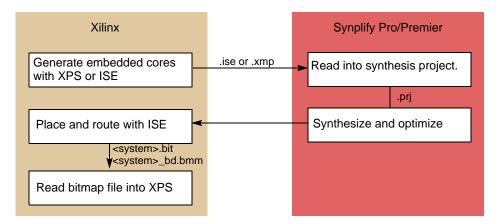

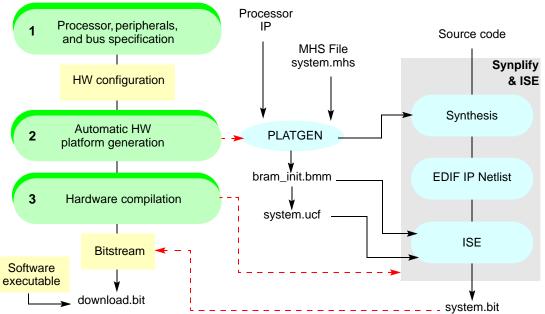

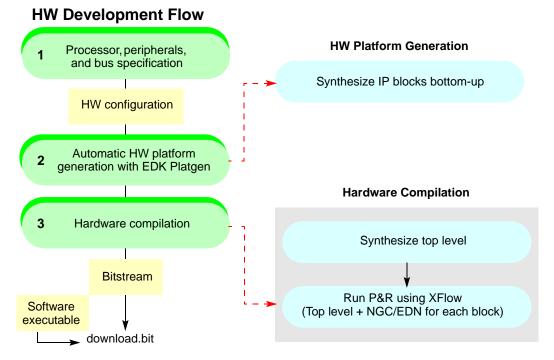

| Including Xilinx EDK Cores       19         The Synplify-EDK Design Flow       19         Working with EDK Cores       20         Xilinx Hardware Development Flows       20                                                                                                                                                                                                                                                           | 99<br>04                   |

### **Chapter 5: Specifying Constraints**

| Using the SCOPE UI                                   | . 212 |

|------------------------------------------------------|-------|

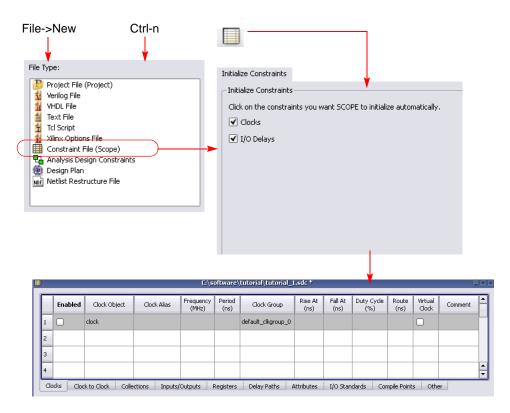

| Creating a Constraint File Using the SCOPE Window    | . 212 |

| Entering and Editing Constraints in the SCOPE Window | . 214 |

| Setting SCOPE Display Preferences                    | . 217 |

| Specifying Timing Constraints                        | . 219 |

| Entering Default Constraints                         | . 219 |

| Setting Clock and Path Constraints                   | . 220 |

Preface

| Defining Clocks222Defining Input and Output Constraints220Specifying Standard I/O Pad Types220Specifying Xilinx Timing Constraints220Using -route for Physical Synthesis in Xilinx Designs230                                                                                                                                                                                                                         | 6<br>8<br>8           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Specifying Timing Exceptions       23         Defining From/To/Through Points for Timing Exceptions       23         Defining Multi-cycle Paths       23         Defining False Paths       23                                                                                                                                                                                                                        | 1<br>4                |

| Using Collections       23         Comparing Methods for Defining Collections       23         Creating and Using Collections (SCOPE Window)       23         Creating Collections (Tcl Commands)       24         Using the Tcl Find Command to Define Collections       24         Using the Expand Tcl Command to Define Collections       24         Viewing and Manipulating Collections (Tcl Commands)       24 | 7<br>8<br>1<br>4<br>6 |

| Using Auto Constraints                                                                                                                                                                                                                                                                                                                                                                                                | 1                     |

| Translating Altera QSF Constraints                                                                                                                                                                                                                                                                                                                                                                                    | 3                     |

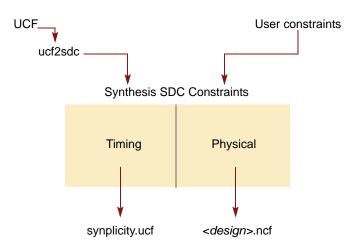

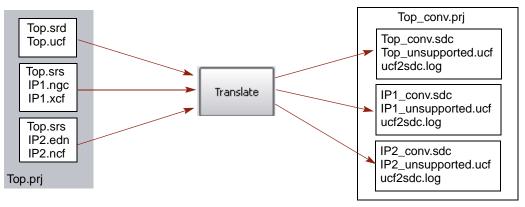

| Converting and Using Xilinx UCF Constraints       254         Using Xilinx UCF Constraints in a Logic Synthesis Design       254         Using Xilinx UCF Constraints in a Physical Synthesis Design       254         Support for UCF Conversion       264         Using the Legacy UCF2SDC Utility       264                                                                                                        | 5<br>8<br>0           |

### Chapter 6: Setting up a Logic Synthesis Project

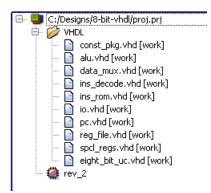

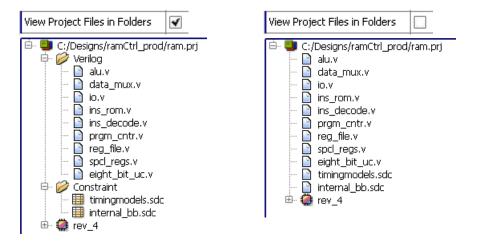

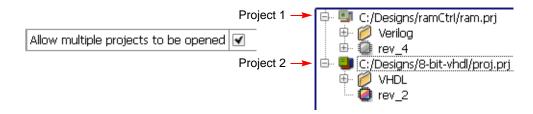

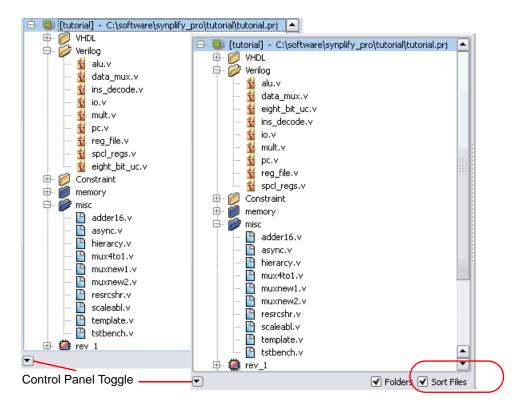

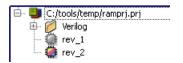

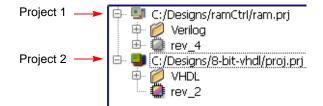

| Setting Up Project Files<br>Creating a Project File<br>Opening an Existing Project File<br>Making Changes to a Project<br>Setting Project View Display Preferences<br>Updating Verilog Include Paths in Older Project Files |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

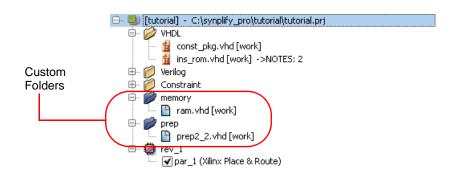

| Project File Hierarchy Management<br>Creating Custom Folders<br>Other Custom Folder Operations<br>Other Custom File Operations                                                                                              |  |

| Setting Up Implementations and Workspaces                                                                                                                                                                                   |  |

| Setting Logic Synthesis Implementation Options       | . 289<br>. 292<br>. 294<br>. 296<br>. 297 |

|------------------------------------------------------|-------------------------------------------|

| Entering Attributes and Directives                   | . 304                                     |

| Specifying Attributes and Directives                 |                                           |

| Specifying Attributes and Directives in VHDL         |                                           |

| Specifying Attributes and Directives in Verilog      |                                           |

| Specifying Attributes Using the SCOPE Editor         |                                           |

| Specifying Attributes in the Constraints File (.sdc) | . 310                                     |

| Searching Files                                      | . 312                                     |

| Identifying the Files to Search                      |                                           |

| Filtering the Files to Search                        |                                           |

| Initiating the Search                                |                                           |

| Search Results                                       |                                           |

|                                                      |                                           |

| Archiving Files and Projects                         |                                           |

| Archive a Project                                    |                                           |

| Un-Archive a Project                                 |                                           |

| Copy a Project                                       | . 323                                     |

### Chapter 7: Setting up a Physical Synthesis Project

| Setting up for Physical Synthesis                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

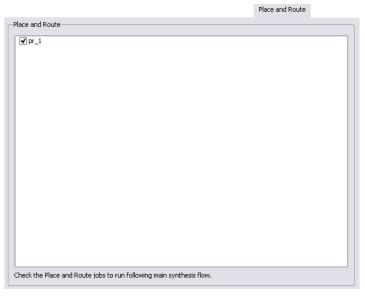

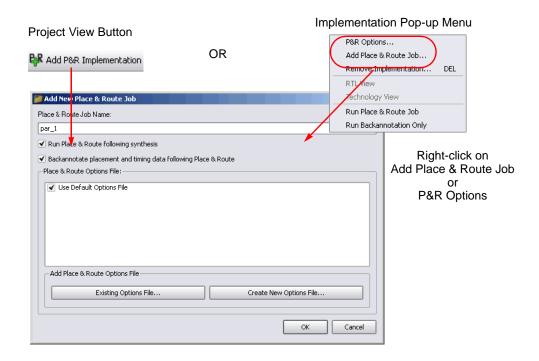

| Setting Options for Physical Synthesis330Setting Synplify Premier Netlist Restructuring Optimizations330Creating a Place and Route Implementation332Specifying Altera Place-and-Route Options337Specifying Xilinx Place-and-Route Options in a Tcl File340Specifying Xilinx Place-and-Route Options in an .opt File341Specifying Xilinx Global Placement Options346 |

| Setting Constraints for Physical Synthesis347Using Design Planner Floorplan Constraints347Translating Pin Location Files348Translating Actel I/O Constraints348Setting Physical Synthesis Constraints for Altera349                                                                                                                                                 |

| Forward-Annotating Physical Synthesis Constraints                                                                                                                                                                                                                                                                                                                   |

| Backannotating Physical Synthesis Constraints | . 353 |

|-----------------------------------------------|-------|

| Backannotating Place-and-Route Data           | . 353 |

| Generating a Xilinx Coreloc Placement File    | . 354 |

### **Chapter 8: Inferring High-Level Objects**

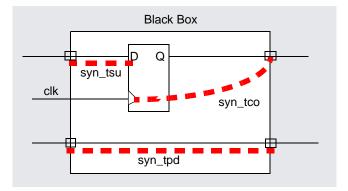

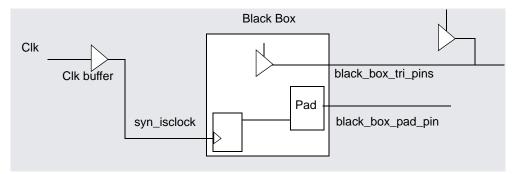

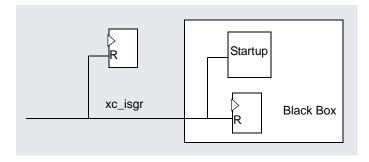

| Defining Black Boxes for Synthesis<br>Instantiating Black Boxes and I/Os in Verilog<br>Instantiating Black Boxes and I/Os in VHDL<br>Adding Black Box Timing Constraints<br>Adding Other Black Box Attributes                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Defining State Machines for Synthesis<br>Defining State Machines in Verilog<br>Defining State Machines in VHDL<br>Specifying FSMs with Attributes and Directives                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

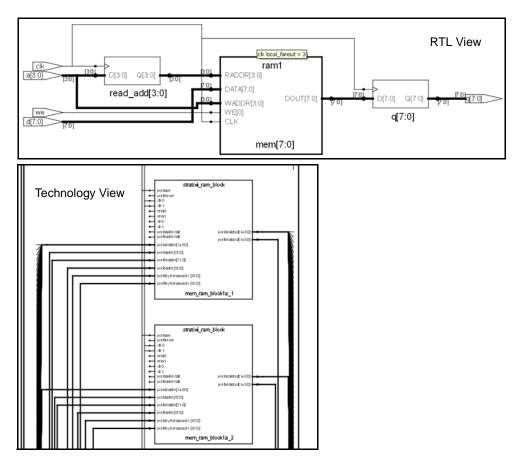

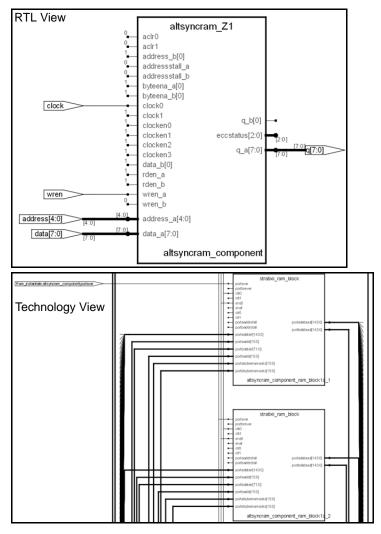

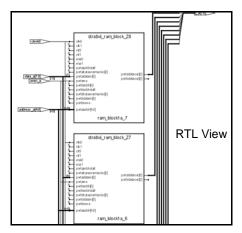

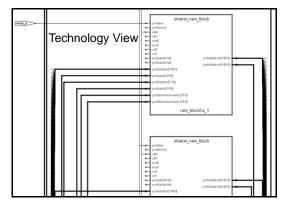

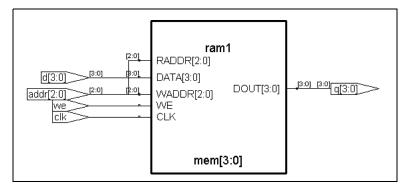

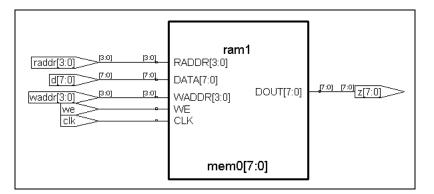

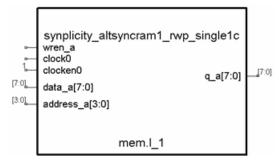

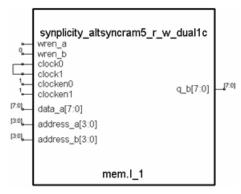

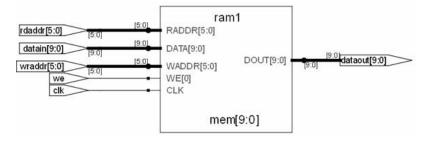

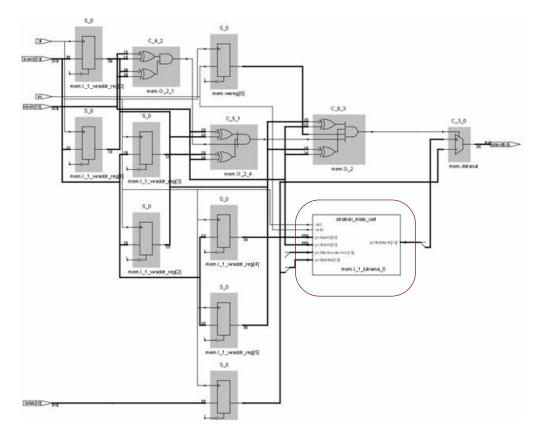

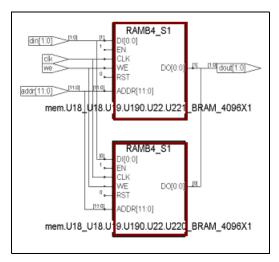

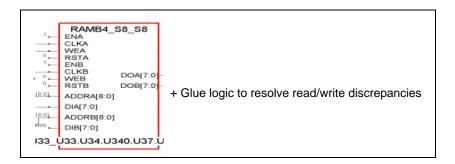

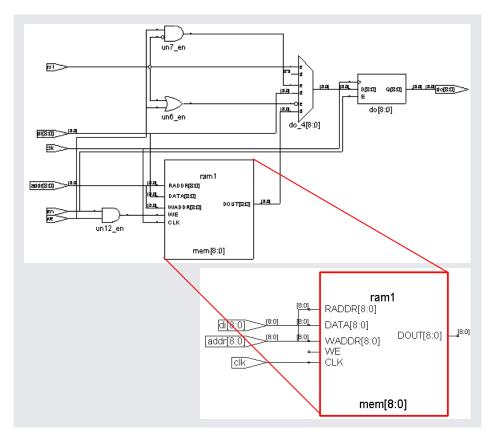

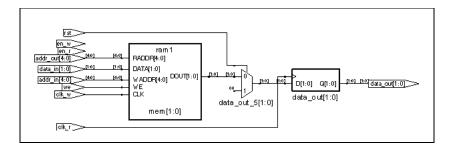

| Inferring RAMs<br>Inference Versus Instantiation<br>Basic Guidelines for Coding RAMs<br>Specifying RAM Implementation Styles<br>Implementing Altera RAMs Automatically<br>Implementing Xilinx RAMs Automatically<br>Implementing Altera FLEX and APEX RAMs<br>Implementing Altera Stratix Multi-Port RAMs<br>Implementing Altera Stratix III LUTRAMs<br>Inferring Altera Stratix III LUTRAMs<br>Inferring Xilinx Block RAMs Using Registered Addresses<br>Inferring Xilinx Block RAMs Using Registered Output<br>Mapping Xilinx ROM to Block RAM | 372<br>373<br>378<br>379<br>383<br>385<br>388<br>389<br>391<br>393 |

| Initializing RAMs<br>Initializing RAMs in Verilog<br>Initializing RAMs in VHDL<br>Initializing Xilinx RAM                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

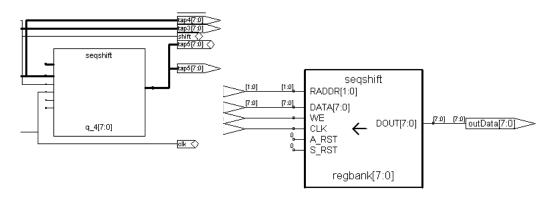

| Inferring Shift Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 410                                                                |

| Working with LPMs<br>Instantiating Altera LPMs as Black Boxes<br>Instantiating Altera LPMs Using VHDL Prepared Components<br>Instantiating Altera LPMs Using a Verilog Library                                                                                                                                                                                                                                                                                                                                                                   | 417<br>421                                                         |

### **Chapter 9: Specifying Design-Level Optimizations**

| Tips for Optimization       426         General Optimization Tips       426         Optimizing for Area       427         Optimizing for Timing       428                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pipelining       429         Prerequisites for Pipelining       429         Pipelining the Design       430                                                                                                                                                                                                                                                                                                                               |

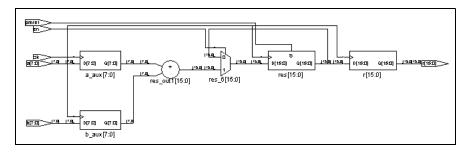

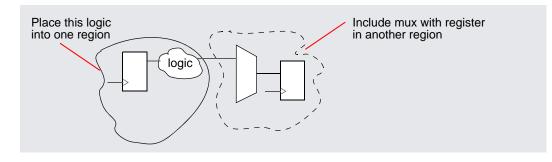

| Retiming433Controlling Retiming433Retiming Example435Retiming Report436How Retiming Works437How Retiming Works With Synplify Premier Regions439                                                                                                                                                                                                                                                                                           |

| Preserving Objects from Optimization                                                                                                                                                                                                                                                                                                                                                                                                      |

| Optimizing Fanout                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Sharing Resources                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Inserting I/Os                                                                                                                                                                                                                                                                                                                                                                                                                            |

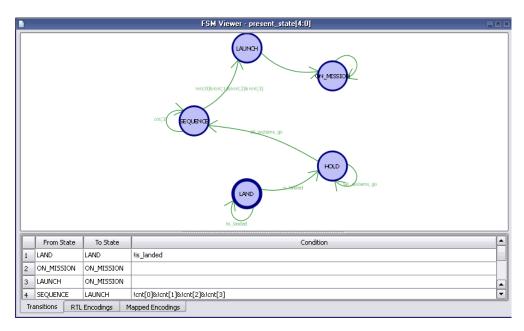

| Optimizing State Machines       453         Deciding when to Optimize State Machines       453         Running the FSM Compiler       455         Running the FSM Explorer       458                                                                                                                                                                                                                                                      |

| Inserting Probes                                                                                                                                                                                                                                                                                                                                                                                                                          |

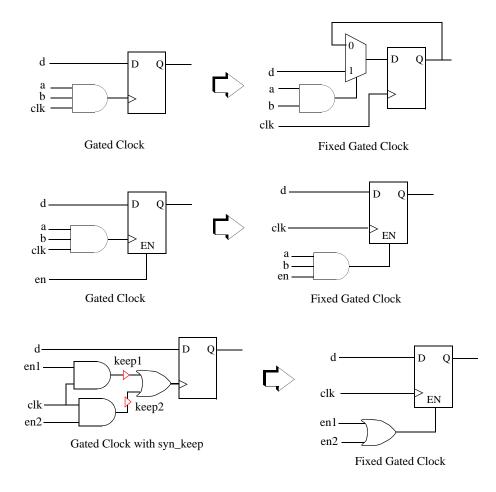

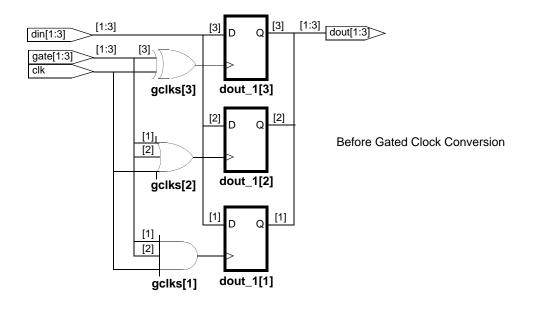

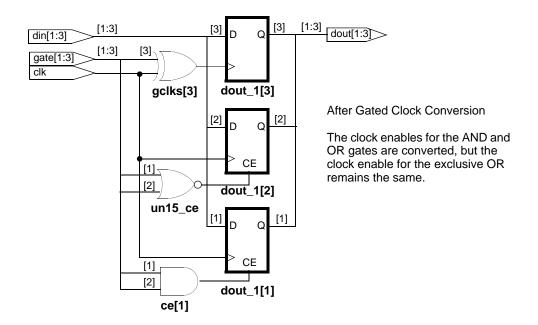

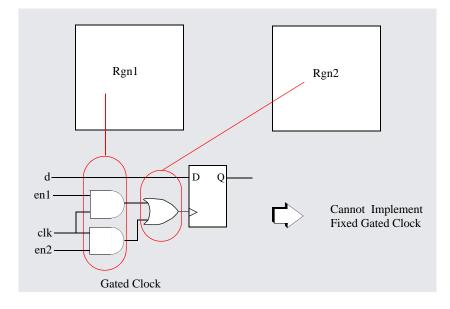

| Working with Gated Clocks       464         Gated Clocks in Synopsys FPGA Designs       464         Prerequisites for Gated Clock Conversion       467         Synthesizing a Gated Clock Design       469         Using Gated Clocks for Black Boxes       471         Analyzing Gated Clock Conversion Reports       472         Working with Gated Clock Error Messages       473         Restrictions on Using Gated Clocks       475 |

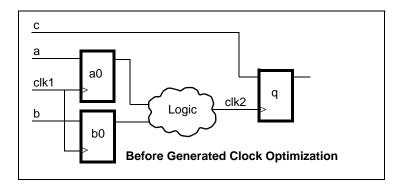

| Optimizing Generated Clocks                 | . 477 |

|---------------------------------------------|-------|

| Generated-Clock Optimization Example        | . 477 |

| Enabling Generated-Clock Optimization       | . 478 |

| Conditions for Generated-Clock Optimization | . 479 |

### **Chapter 10: Fast Synthesis**

| About Fast Synthesis                       | 482 |

|--------------------------------------------|-----|

| Using Fast Synthesis                       | 483 |

| Fast Synthesis and Other Synthesis Options | 485 |

### Chapter 11: Floorplanning with Design Planner

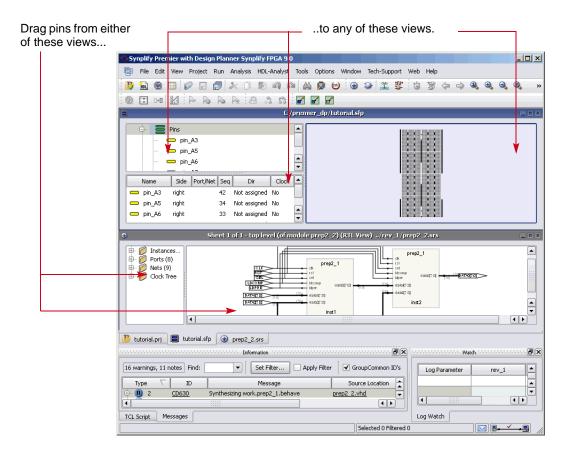

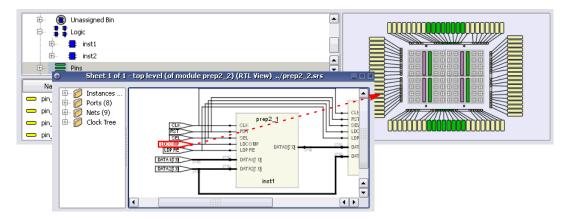

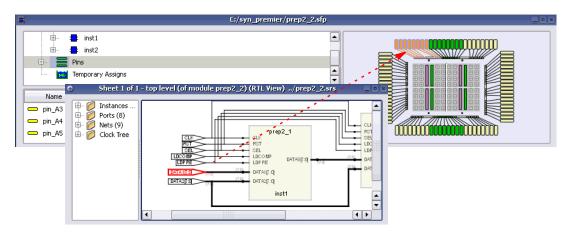

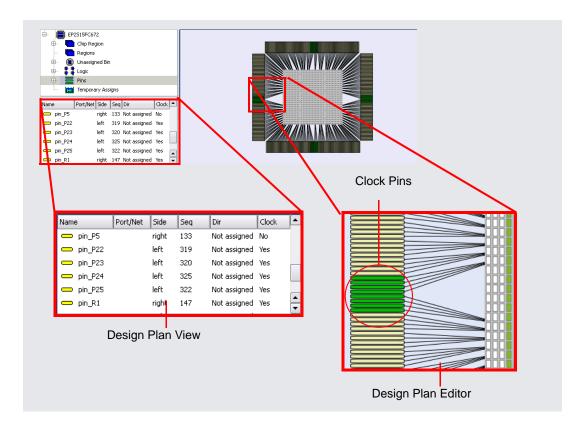

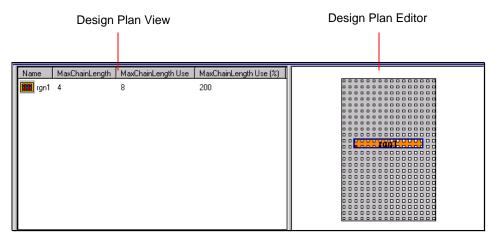

| Using Design Planner       48         Starting Design Planner       48         Copying Objects in the Design Planner Tool       49         Controlling Pin Display in the Design Plan Editor       49         Creating and Using a Design Plan File for Physical Synthesis       49                                                                                                                   | 38<br>90<br>91                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Assigning Pins and Clocks       49         Assigning Pins Interactively       49         Importing Pin Assignments from Pin Assignment Files       49         Assigning Clock Pins       49         Modifying Pin Assignments       50         Using Temporary Pin Assignments       50         Viewing Assigned Pins in Different Views       50         Viewing Pin Assignment Information       50 | 95<br>98<br>98<br>90<br>01<br>02 |

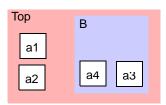

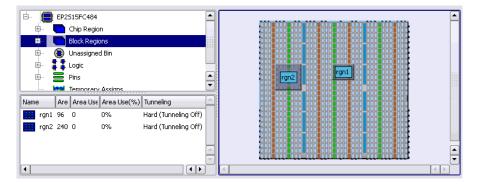

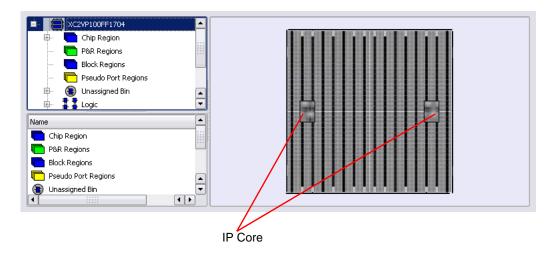

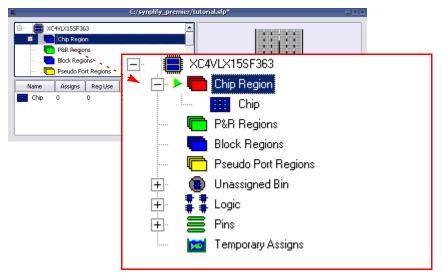

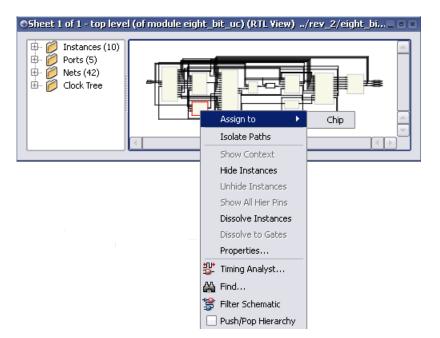

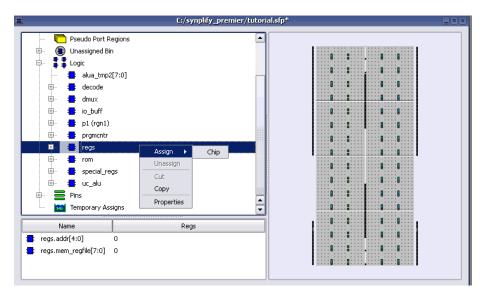

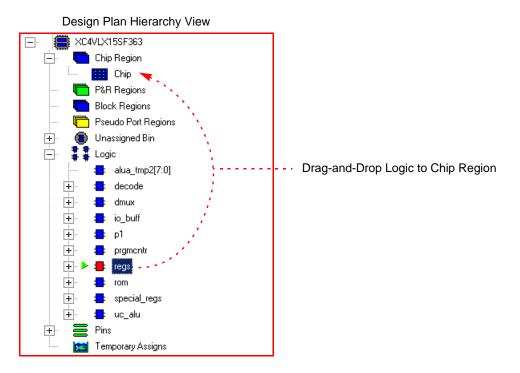

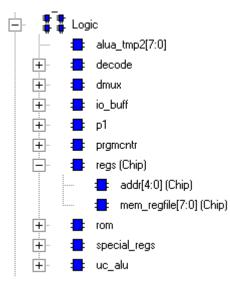

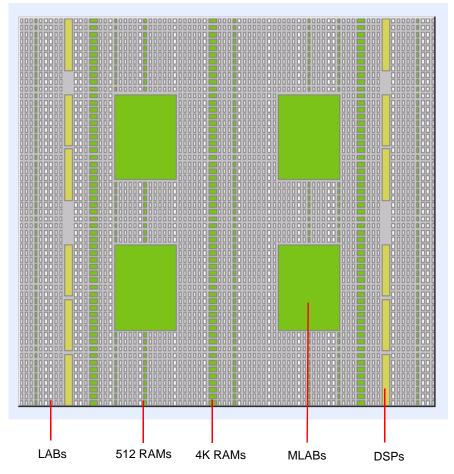

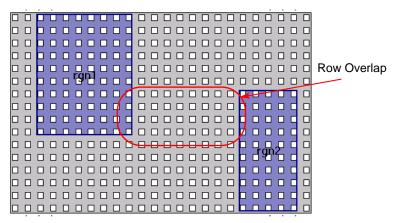

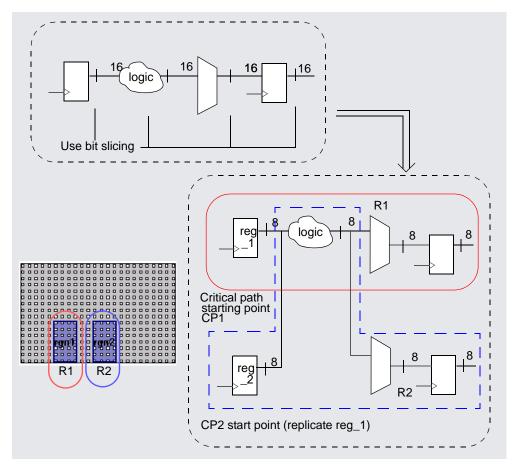

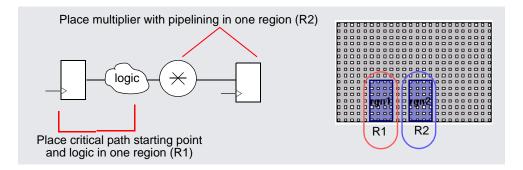

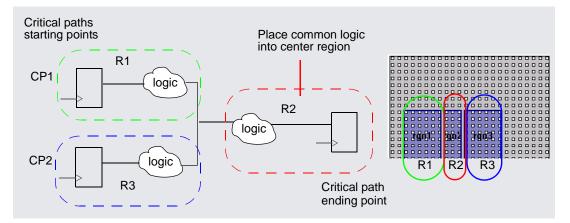

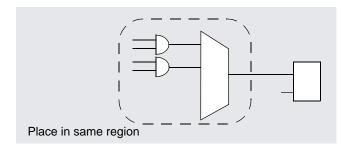

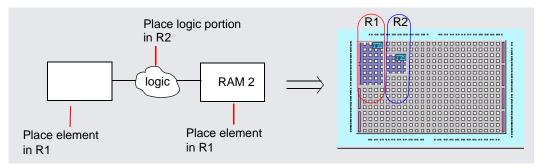

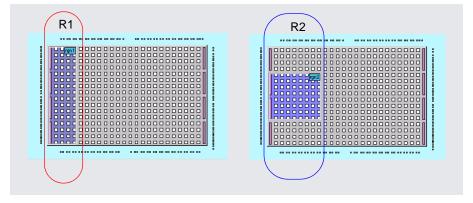

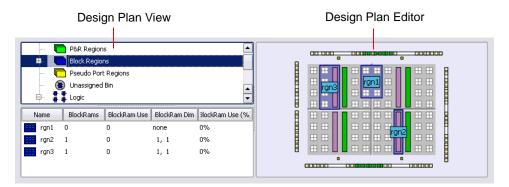

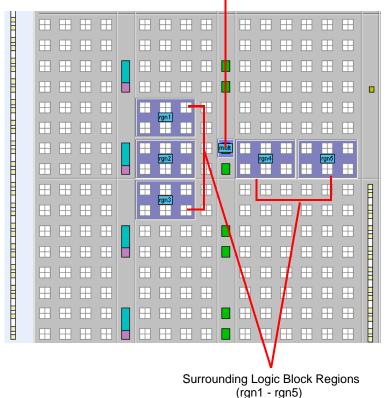

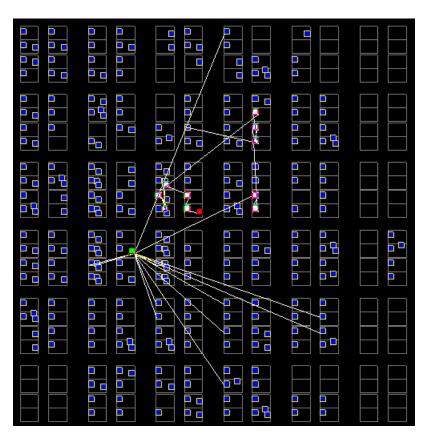

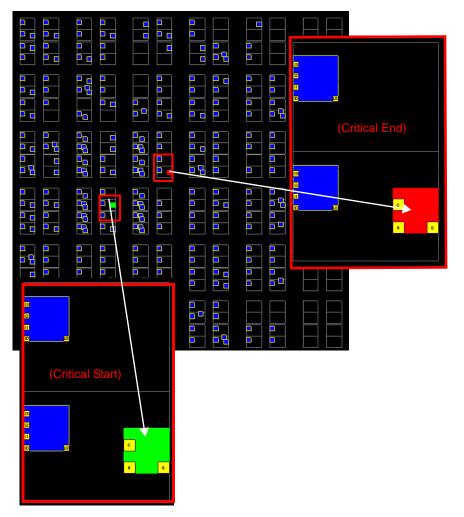

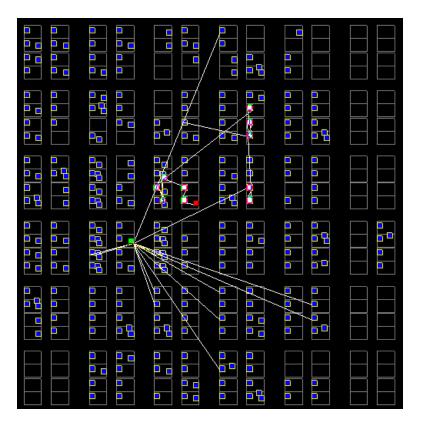

| Working with Regions50Creating Regions50Using Region Tunneling50Moving and Sizing Regions50Viewing Intellectual Property (IP) Core Areas51Assigning Logic to Top-level Chip Regions51Assigning Logic to Regions51Replicating Logic Manually51Assigning Critical Paths from Island Timing to a Region51Checking Utilization51                                                                          | )5<br>)7<br>)9<br> 0<br> 4<br> 5 |

| Working with Altera Regions                                                                                                                                                                                                                                                                                                                                                                           | 20                               |

| Working with Xilinx Regions                                                                                                                                                                                                                                                                                                                                                                           |                                  |

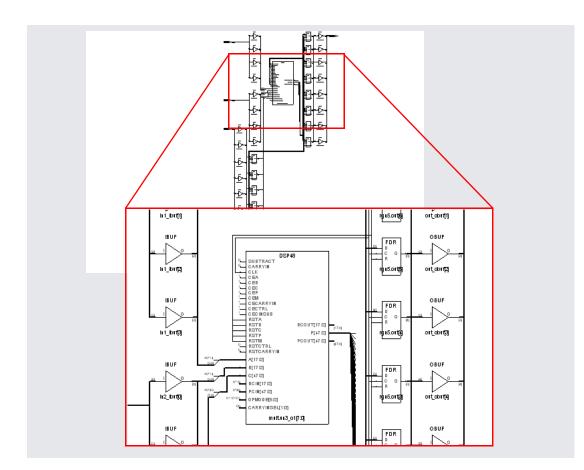

| Assigning Objects to Xilinx Regions       527         Assigning Xilinx Critical Paths to Design Planner Regions       527         Assigning Xilinx Block RAMs to Regions       534         Assigning Xilinx Block Multipliers to Regions       539         Assigning Xilinx DSP Blocks to Regions       540 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Using Process-Level Hierarchy542                                                                                                                                                                                                                                                                            |

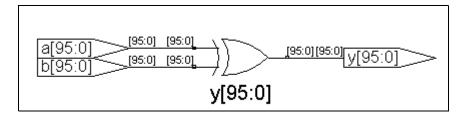

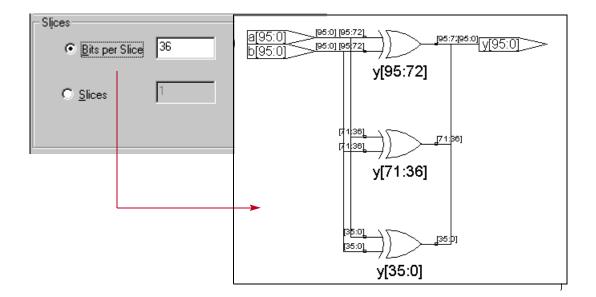

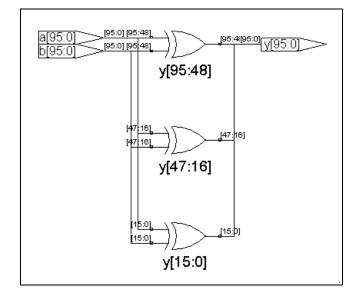

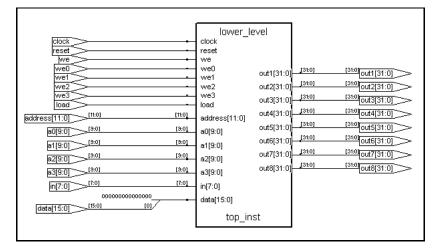

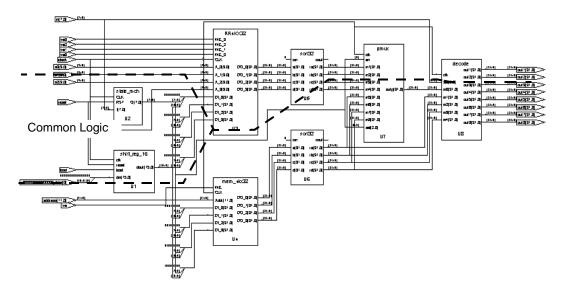

| Bit Slicing                                                                                                                                                                                                                                                                                                 |

| Zippering                                                                                                                                                                                                                                                                                                   |

### **Chapter 12: Running Logical Compile Points**

| Logical Compile-Point Synthesis       560         Overview       560         Traditional Bottom-up Design and Compile Points       561                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

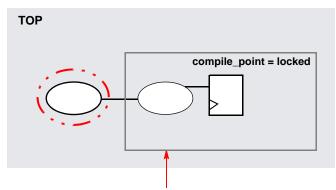

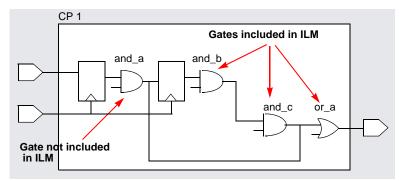

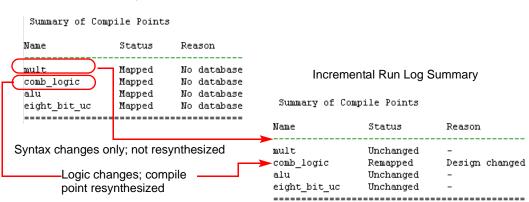

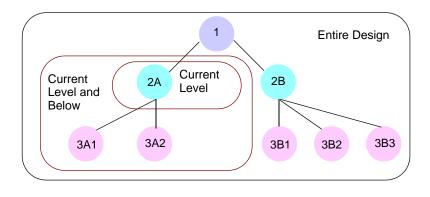

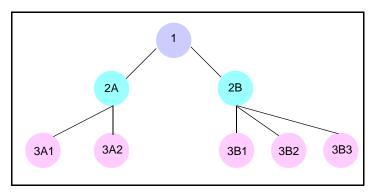

| About Compile Points       562         Nesting: Child and Parent Compile Points       562         Advantages of Using Compile Points       563         Compile Point Types       564         Compile Point Feature Summary       567         Using syn_hier with Compile Points       568         Using syn_allowed_resources with Compile Points       568         define_compile_point and define_current_design       569         About Interface Logic Models (ILMs)       570 |

| Compile Point Synthesis       571         Compile Point Optimization       571         Forward-annotation of Compile-point Timing Constraints       572                                                                                                                                                                                                                                                                                                                            |

| Using Compile-point Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Xilinx Compile-point Synthesis Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### Chapter 13: Using Multiprocessing

| Multiprocessing With Compile Points | 588 |

|-------------------------------------|-----|

| Setting Maximum Parallel Jobs5      | 588 |

| License Utilization                 | 589 |

### Chapter 14: Synthesizing and Analyzing the Log File

| Synthesizing Your Design       592         Running Logic Synthesis       592         Running Physical Synthesis       592                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

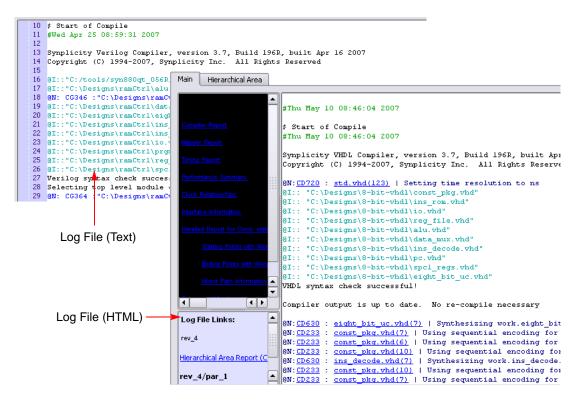

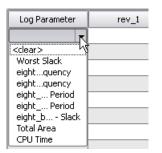

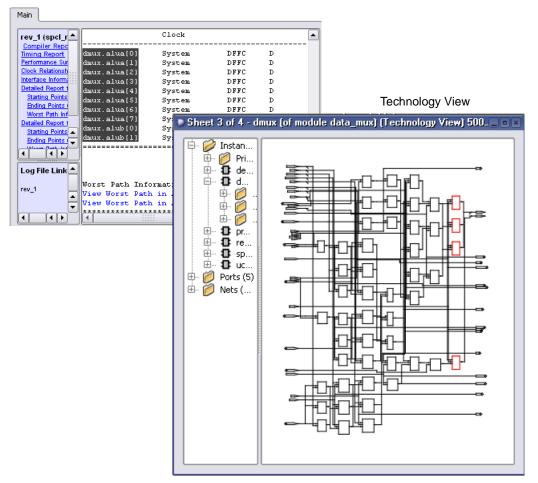

| Checking Log Results       596         Viewing the Log File       596         Analyzing Results Using the Log File Reports       599         Using the Log Watch Window       600                                                                                                                               |

| Handling Messages       602         Checking Results in the Message Viewer       602         Filtering Messages in the Message Viewer       604         Filtering Messages from the Command Line       606         Automating Message Filtering with a Tcl Script       607         Handling Warnings       609 |

| Validating Logic Synthesis for Physical Synthesis                                                                                                                                                                                                                                                               |

### Chapter 15: Analyzing with HDL Analyst and FSM Viewer

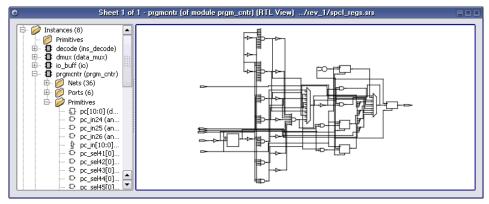

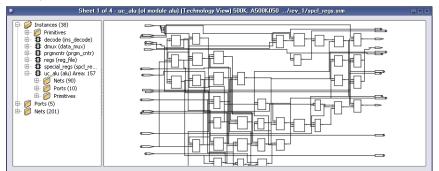

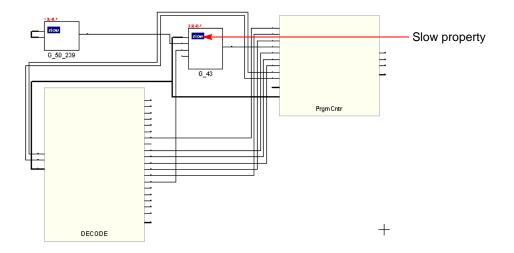

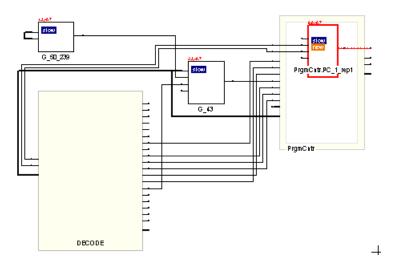

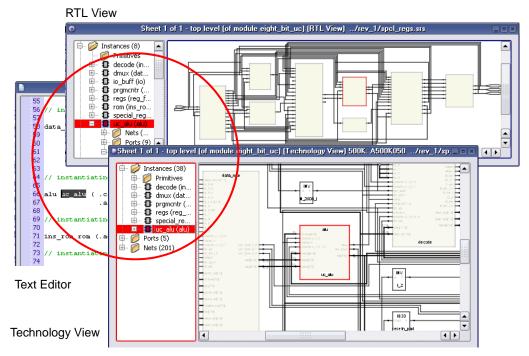

| Working in the Schematic Views<br>Differentiating Between the Views<br>Opening the Views<br>Viewing Object Properties | 615<br>615<br>617 |

|-----------------------------------------------------------------------------------------------------------------------|-------------------|

| Selecting Objects in the RTL/Technology Views                                                                         |                   |

| Moving Between Views in a Schematic Window                                                                            |                   |

| Setting Schematic View Preferences                                                                                    | 623               |

| Managing Windows                                                                                                      | 625               |

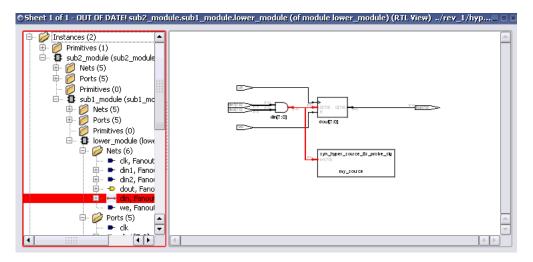

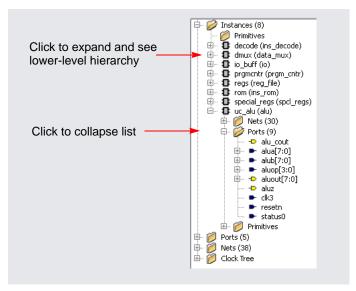

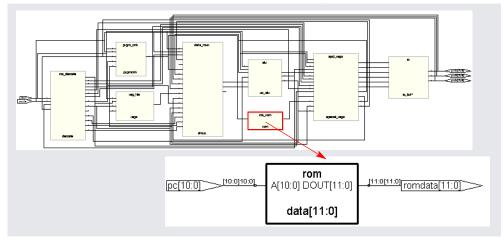

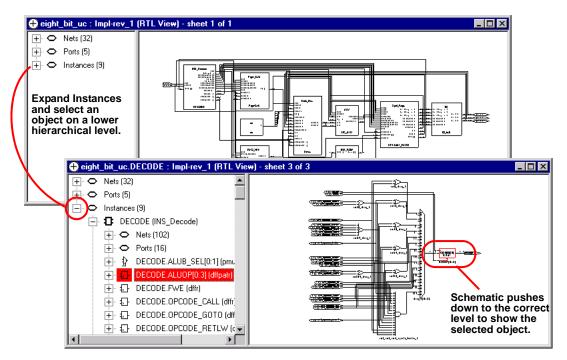

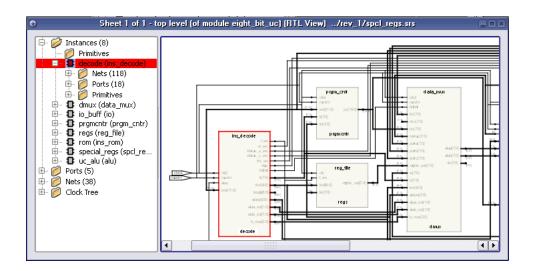

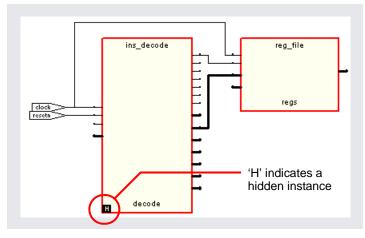

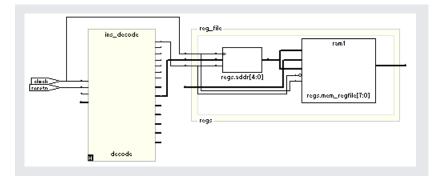

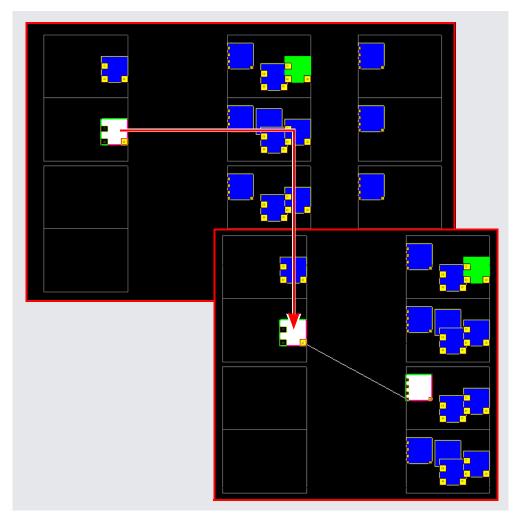

| Exploring Design Hierarchy                                                                                            | 627               |

| Traversing Design Hierarchy with the Hierarchy Browser                                                                |                   |

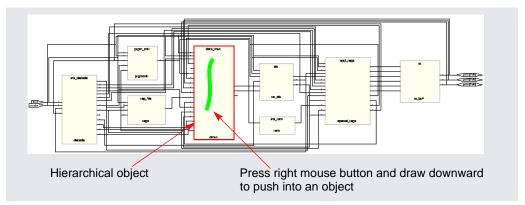

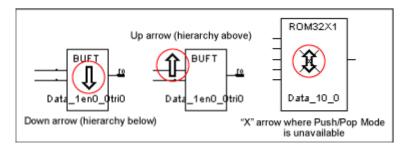

| Exploring Object Hierarchy by Pushing/Popping                                                                         |                   |

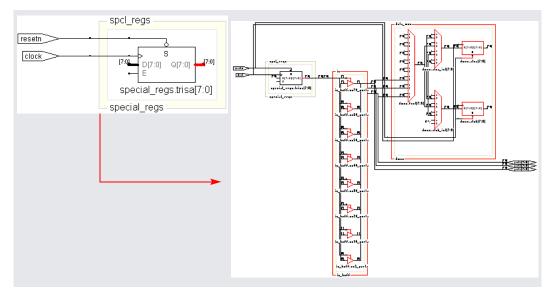

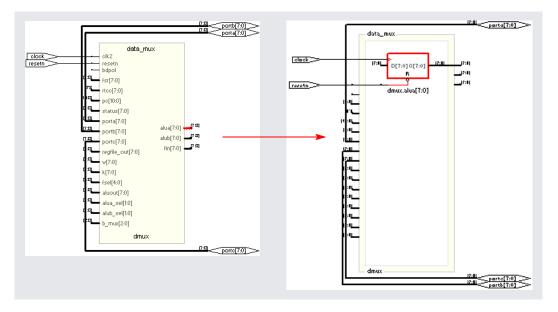

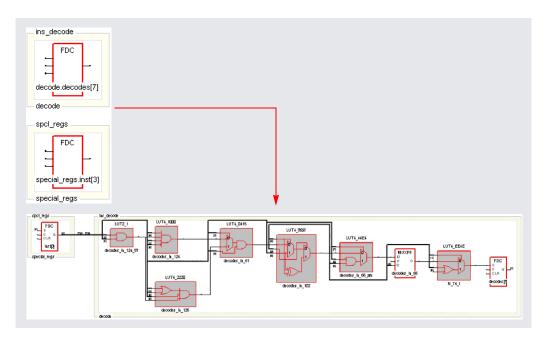

| Exploring Object Hierarchy of Transparent Instances                                                                   |                   |

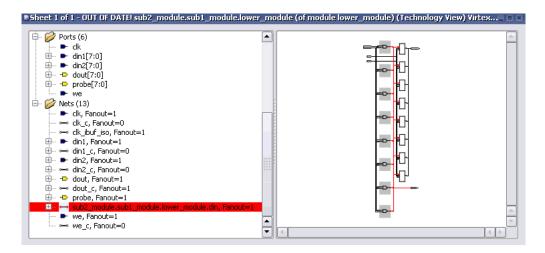

| Finding Objects                                                                                                       | 635               |

| Browsing to Find Objects                                                                                              |                   |

| Using Find for Hierarchical and Restricted Searches                                                                   |                   |

| Using Wildcards with the Find Command                                                                                 |                   |

| Using Find to Search the Output Netlist                                                                               | 643               |

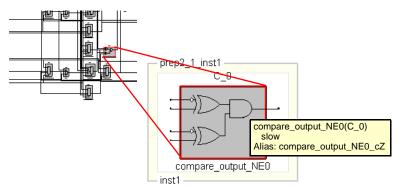

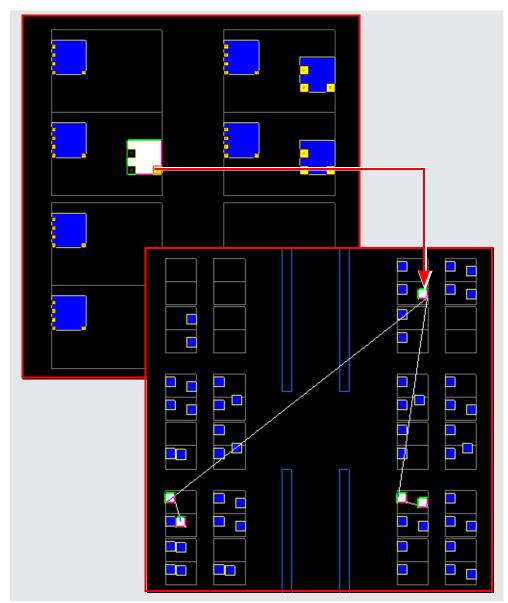

| Crossprobing                                                                                                          | 645               |

| Crossprobing within an RTL/Technology View                                                                            |                   |

| Crossprobing from the RTL/Technology View                                                                             |                   |

| Crossprobing from the Text Editor Window                                                                              |                   |

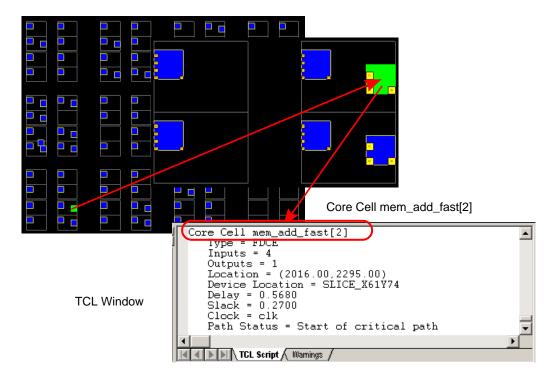

| Crossprobing from the Tcl Script Window                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

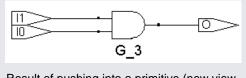

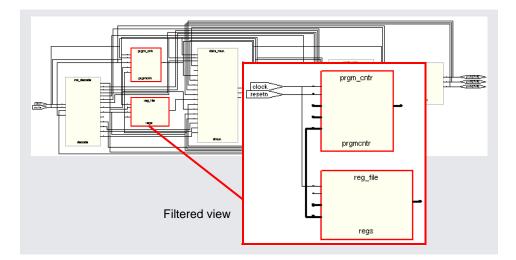

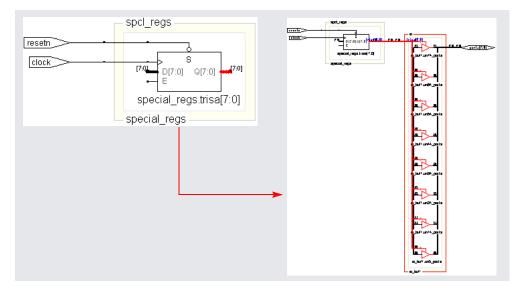

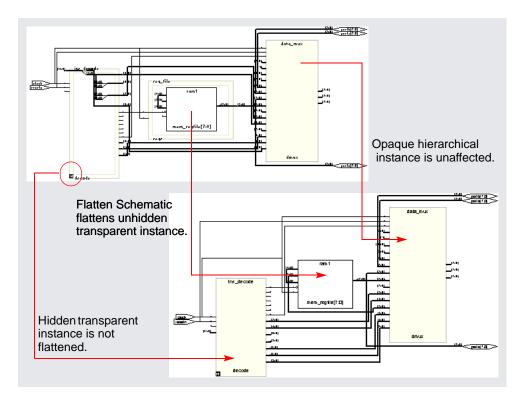

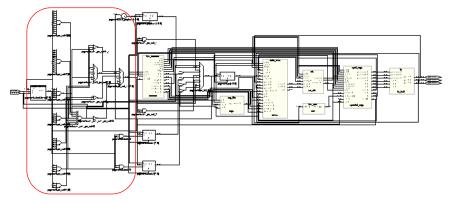

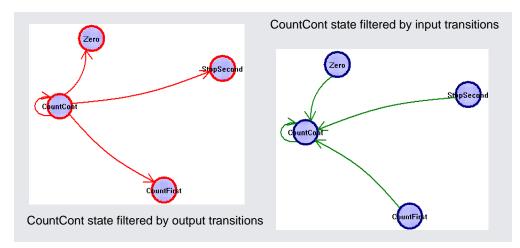

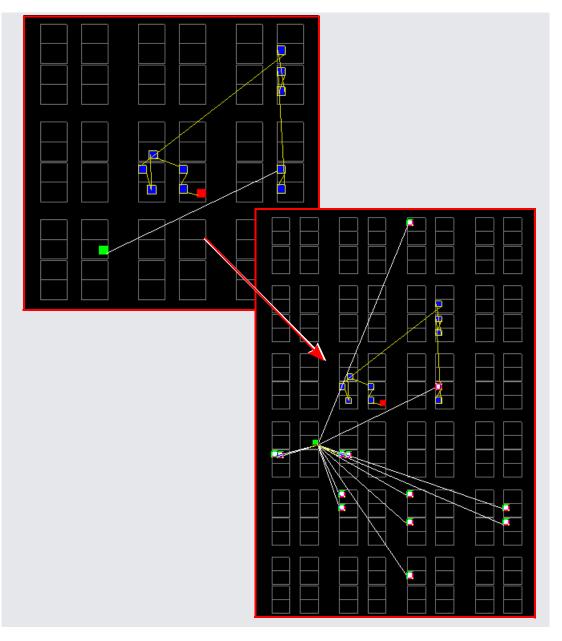

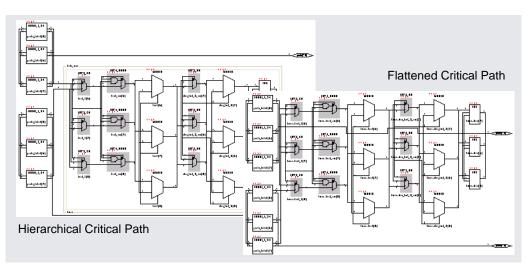

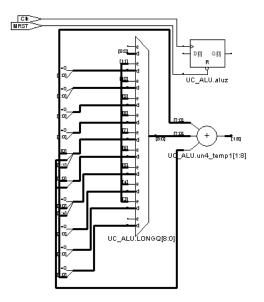

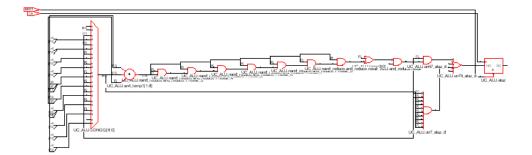

| Analyzing With the HDL Analyst Tool       654         Viewing Design Hierarchy and Context       655         Filtering Schematics       658         Expanding Pin and Net Logic       660         Expanding and Viewing Connections       664         Flattening Schematic Hierarchy       665         Minimizing Memory Usage While Analyzing Designs       670 |

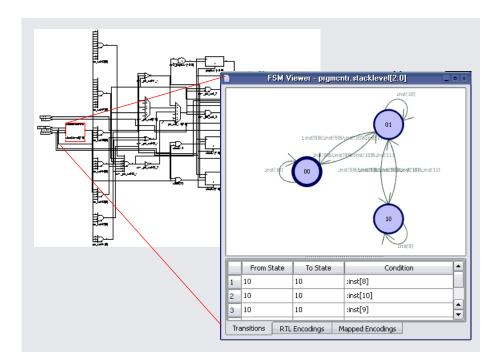

| Using the FSM Viewer                                                                                                                                                                                                                                                                                                                                             |

### **Chapter 16: Analyzing Designs in Physical Analyst**

| Analyzing Physical Synthesis Results       678         Analyzing Physical Synthesis Results Using Various Tools       678         Comparing Performance Results       680         Running Multiple Implementations       681         Checking Altera Pre-Placement Physical Synthesis Results       681  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

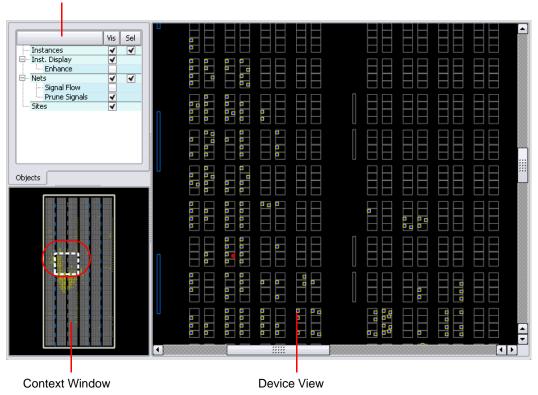

| Using Physical Analyst                                                                                                                                                                                                                                                                                   |

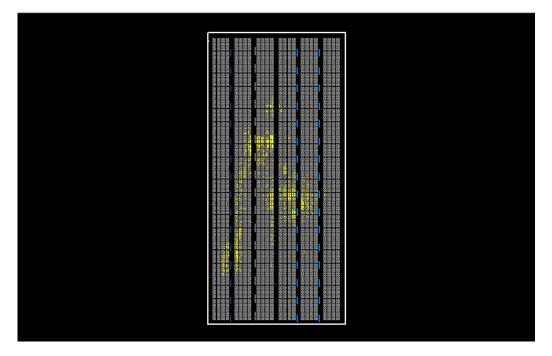

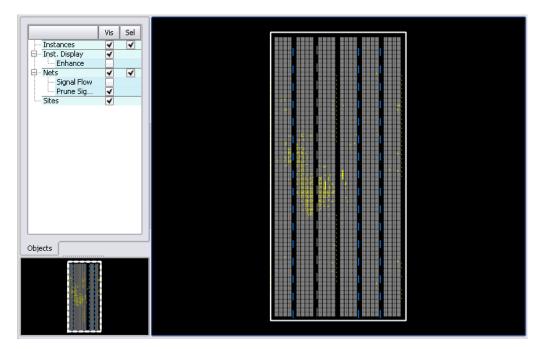

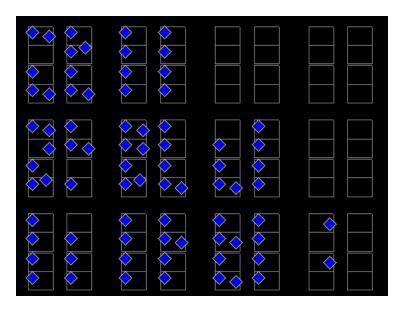

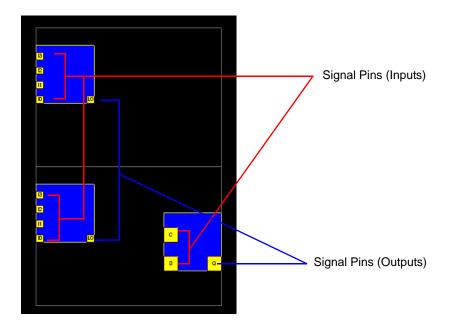

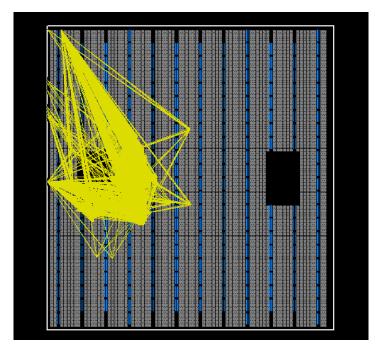

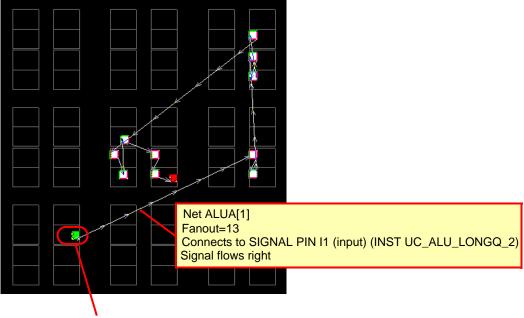

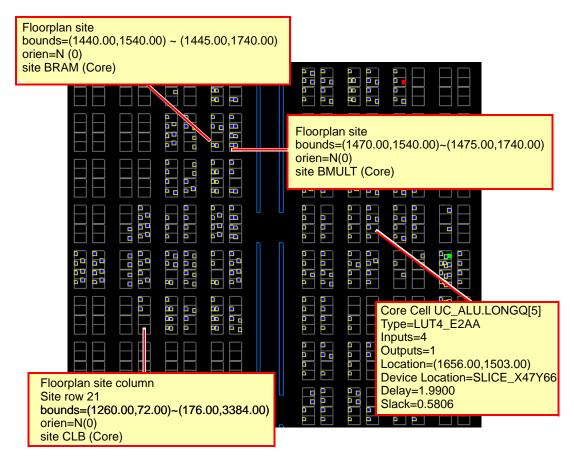

| Displaying and Selecting Objects       689         Setting Visibility for Physical Analyst Objects       689         Displaying Instances and Sites in Physical Analyst       690         Displaying Nets in Physical Analyst       694         Selecting Objects in Physical Analyst       696          |

| Querying Physical Analyst Objects       699         Viewing Properties in Physical Analyst       699         Using Tool Tips to View Properties in Physical Analyst       702                                                                                                                            |

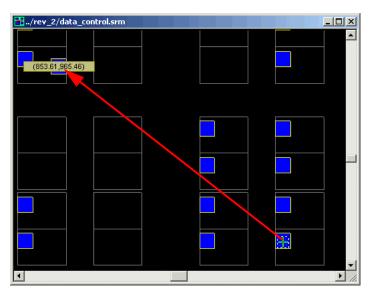

| Finding Objects       704         Using Find to Locate Physical Analyst Objects)       704         Finding Physical Analyst Objects by Their Locations       708         Using Markers to Find Physical Analyst Objects       708         Identifying Encrypted IP Objects in Physical Analyst       711 |

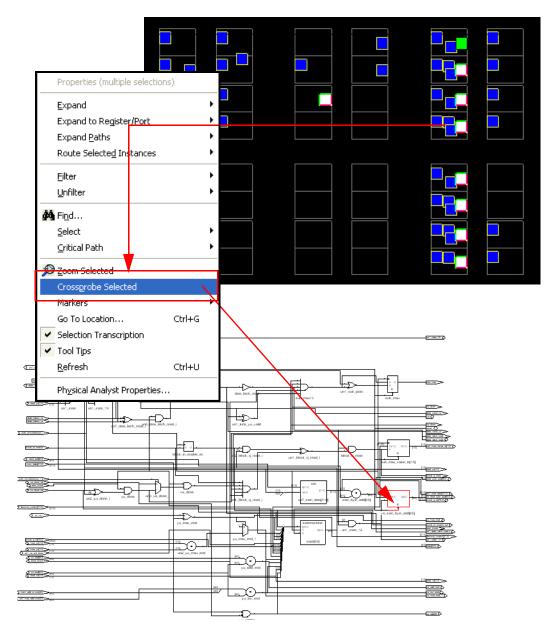

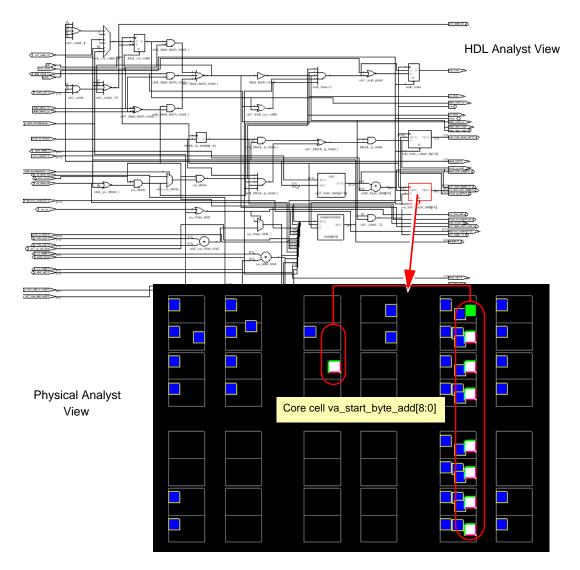

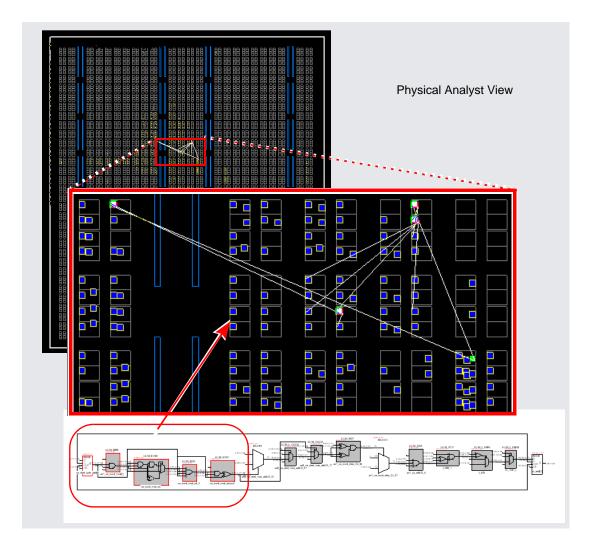

| Crossprobing in Physical Analyst                                                                                                                                                                                                                                                                         |

| Crossprobing from the RTL View to Physical Analyst |     |

|----------------------------------------------------|-----|

| Analyzing Netlists in Physical Analyst             |     |

| Expanding Pin and Net Logic in Physical Analyst    | 722 |

| Expanding Pin and Net Logic in Physical Analyst    |     |

### **Chapter 17: Analyzing Timing**

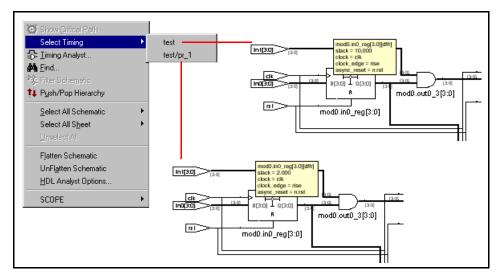

| Analyzing Timing in Schematic Views    | 30<br>31<br>33       |

|----------------------------------------|----------------------|

| Using the Stand-alone Timing Analyst   |                      |

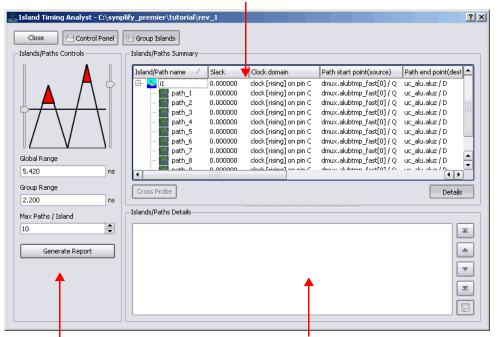

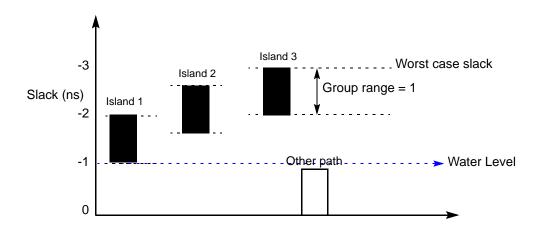

| Using the Island Timing Analyst        | 43<br>45<br>47<br>48 |

| Analyzing Timing with Physical Analyst | 50<br>53             |

| Handling Negative Slack                | 56                   |

### **Chapter 18: Optimizing for Specific Targets**

| Optimizing Actel Designs<br>Using Predefined Actel Black Boxes  |     |

|-----------------------------------------------------------------|-----|

| Using ACTGen Macros                                             | 761 |

| Working with Radhard Designs                                    | 762 |

| Improving Performance in Actel Physical Synthesis Designs       | 763 |

| Optimizing Altera Designs Design Tips for APEX and FLEX Designs |     |

| Determining ROM Implementation                                  |     |

| Working with Altera EABs and ESBs                               |     |

| Working with Altera PLLs                                        | 769 |

| Instantiating Special Buffers as Black Boxes in Altera Designs  | 770 |

| Specifying Altera I/O Locations<br>Packing I/O Cell Registers in Altera Designs<br>Specifying HardCopy and Stratix Companion Parts<br>Specifying Core Voltage in Stratix III Designs<br>Using LPMs in Simulation Flows<br>Improving Altera Physical Synthesis Performance<br>Working with Quartus II<br>Configuring Max+Plus II for FLEX and ACEX1K<br>Configuring Max+Plus II for MAX Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 774<br>775<br>776<br>777<br>779<br>779<br>779                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Optimizing Lattice Designs<br>Instantiating Lattice Macros<br>Using Lattice GSR Resources<br>Inferring Carry Chains in Lattice XPLD Devices<br>Inferring Lattice PIC Latches<br>Controlling I/O Insertion in Lattice Designs<br>Forward-Annotating Lattice Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 785<br>787<br>788<br>788<br>788<br>794                                                                                            |

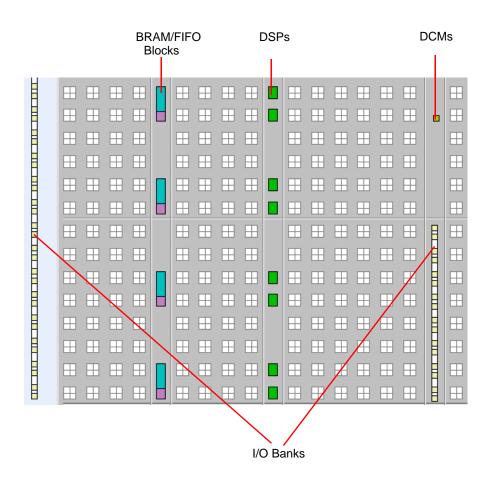

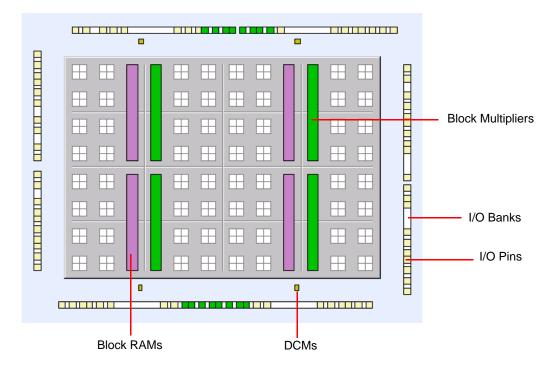

| Optimizing Xilinx Designs<br>Designing for Xilinx Architectures<br>Specifying Global Sets/Resets and Startup Blocks<br>Inferring Wide Adders<br>Instantiating CoreGen Cores<br>Instantiating Virtex PCI Cores<br>Packing Registers for Xilinx I/Os<br>Specifying Xilinx Register INIT Values<br>Inserting Xilinx Register INIT Values<br>Inserting Xilinx I/Os and Specifying Pin Locations<br>Working with Xilinx Buffers<br>Specifying RLOCs<br>Specifying RLOCs and RLOC_ORIGINs with the synthesis Attribute<br>Using Clock Buffers in Virtex Designs<br>Working with Clock Skews in Xilinx Virtex-5 Physical Designs<br>Instantiating Special I/O Standard Buffers for Virtex<br>Reoptimizing With EDIF Files<br>Improving Xilinx Physical Synthesis Performance<br>Running Post-Synthesis Simulation<br>Working with Xilinx Place-and-Route Software | 797<br>798<br>800<br>801<br>804<br>805<br>807<br>810<br>812<br>818<br>819<br>821<br>821<br>822<br>824<br>825<br>826<br>827<br>828 |

### Chapter 19: Working with Synthesis Output

| Passing Information to the P&R Tools     | 832 |

|------------------------------------------|-----|

| Specifying Pin Locations                 | 832 |

| Specifying Locations for Actel Bus Ports | 833 |

|      | Specifying Macro and Register Placement833Passing Technology Properties834Specifying Padtype and Port Information834                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ger  | nerating Vendor-Specific Output                                                                                                                                                                             |

| Invo | bking Third-Party Vendor Tools838Configuring Tool Tags838Invoking a Third-Party Tool839                                                                                                                     |

| Ch   | apter 20: Running Post-Synthesis Operations                                                                                                                                                                 |

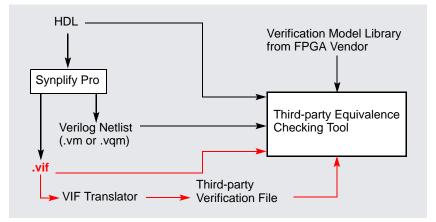

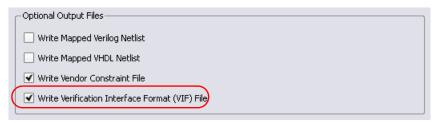

| VIF  | Formal Verification Flow844Overview of the VIF Flow844Generating a VIF File845Using a Tcl Script for VIF Conversion847Handling Equivalency Check Failures848                                                |

| Rur  | nning Place-and-Route after Synthesis                                                                                                                                                                       |

| Sim  | ulating with the VCS Tool851                                                                                                                                                                                |

| Res  | synthesizing with QuickLogic Information                                                                                                                                                                    |

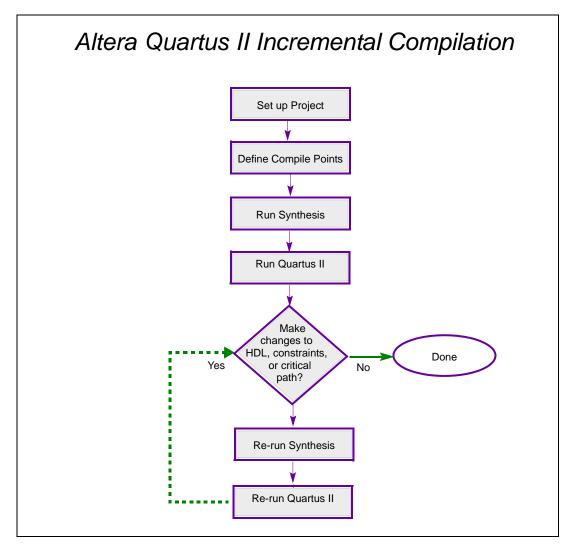

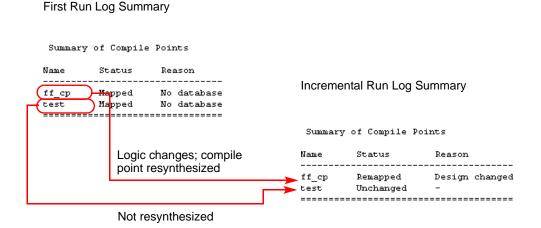

| Qua  | artus II Incremental Compilation                                                                                                                                                                            |

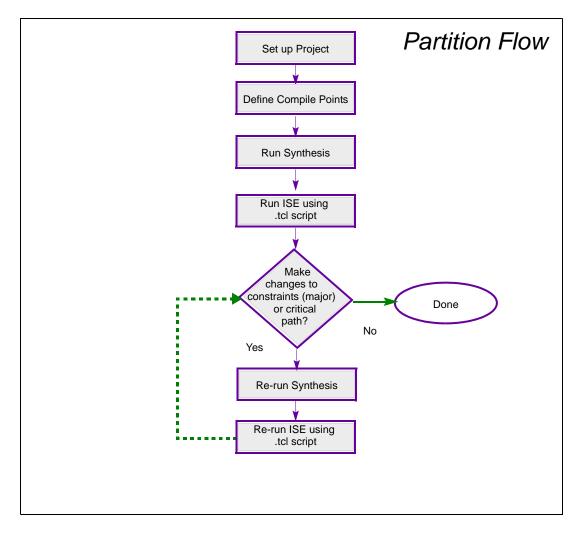

| Wo   | rking with Xilinx Incremental Flows                                                                                                                                                                         |

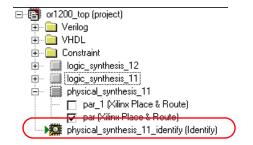

| Wo   | rking with the Identify RTL Debugger868Launching from the Synplify Pro or Synplify Premier Tool868Launching from the Synplify Tool870Handling Problems with Launching Identify872Using the Identify Tool873 |

### **Chapter 21: Process Optimization and Automation**

| Using Batch Mode                      | 876 |

|---------------------------------------|-----|

| Running Batch Mode on a Project File  | 876 |

| Running Batch Mode with a Tcl Script  | 877 |

| Working with Tcl Scripts and Commands | 878 |

| Using Tcl Commands and Scripts        | 878 |

| Generating a Job Script                                | 879 |

|--------------------------------------------------------|-----|

| Creating a Tcl Synthesis Script                        | 879 |

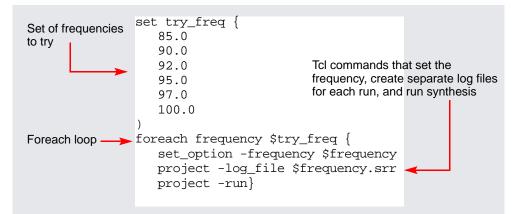

| Using Tcl Variables to Try Different Clock Frequencies | 881 |

| Using Tcl Variables to Try Several Target Technologies | 882 |

| Running Bottom-up Synthesis with a Script              | 883 |

| Automating Flows with synhooks.tcl                     | 884 |

Preface

# Introduction

This introduction to the Synplify  $^{\mathbb{R}}$ , Synplify  $Pro^{\mathbb{R}}$ , and Synplify  $^{\mathbb{R}}$  Premier software describes the following:

- The Synopsys FPGA Product Family, on page 22

- Scope of the Document, on page 26

- Getting Started, on page 27

- User Interface Overview, on page 29

Throughout the documentation, features and procedures described apply to all tools, unless specifically stated otherwise.

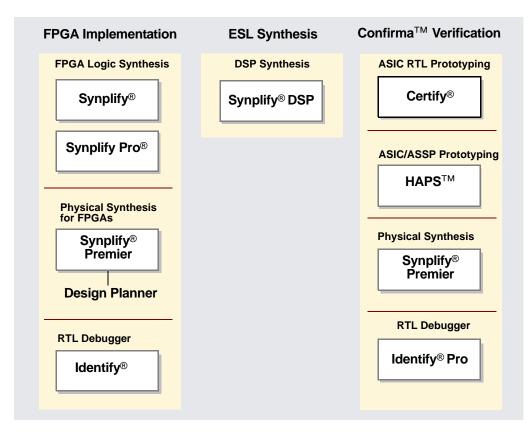

## The Synopsys FPGA Product Family

The Synopsys<sup>®</sup> family of synthesis tools is based on core logic synthesis technology, and share a common look and feel. The following figure shows the Synopsys<sup>®</sup> Synplicity<sup>®</sup> line of products.

### **The FPGA Synthesis Tools**

This section briefly describes the FPGA synthesis tools Synplify, Synplify Pro, and Synplify Premier synthesis tools.

### Synplify and Synplify Pro Software

Synplify<sup>®</sup> and Synplify Pro<sup>®</sup> are logic synthesis tools for FPGAs (Field Programmable Gate Arrays) and Complex PLDs (Programmable Logic Devices). For input, the software uses high-level designs written in Verilog and VHDL hardware description languages (HDLs). Using proprietary Behavior Extracting Synthesis Technology<sup>®</sup> (B.E.S.T.)<sup>®</sup> the tool converts the HDL into small, high-performance, design netlists that are optimized for popular technology vendors. Optionally, the software can write postsynthesis VHDL and Verilog netlists that you can use to verify functionality through simulation.

The Synplify Pro software offers a superset of the Synplify features.

### **Synplify Premier Software**

The Synplify Premier tool offers a push-button, graph-based physical synthesis approach improving overall device performance while simultaneously delivering tight correlation between pre-route timing estimates and final post place-and-route results.

The Synplify Premier product supports three physical design flows. See *Synplify Premier Synthesis Design Flows*, on page 35 for descriptions. You can also use it in the prototyping flow, described in *Prototyping Design Flow*, on page 80.

### **Synopsys FPGA Tool Features**

This table distinguishes between the Synplify Pro, Synplify, Synplify Premier, and Synplify Premier with Design Planner products.

|                                                                               | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|-------------------------------------------------------------------------------|----------|-----------------|---------------------|------------------------|

| Performance                                                                   |          |                 |                     |                        |

| Behavior Extracting Synthesis<br>Technology <sup>®</sup> (BEST <sup>™</sup> ) | Х        | Х               | Х                   | Х                      |

| Vendor-Generated Core/IP<br>Support (certain technologies)                    |          | Х               | Х                   | Х                      |

| FSM Compiler                                                                  | Х        | Х               | Х                   | Х                      |

|                                                                 | Synplify | Synplify<br>Pro | Synplify<br>Premier | Synplify<br>Premier DP |

|-----------------------------------------------------------------|----------|-----------------|---------------------|------------------------|

| FSM Explorer                                                    |          | Х               | Х                   | Х                      |

| Gated Clock Conversion                                          |          | Х               | Х                   | Х                      |

| Register Pipelining                                             |          | Х               | Х                   | Х                      |

| Register Retiming                                               |          | Х               | Х                   | Х                      |

| Code Analysis                                                   |          |                 |                     |                        |

| SCOPE <sup>®</sup> Spreadsheet                                  | х        | Х               | Х                   | Х                      |

| HDL Analyst®                                                    | Option   | Х               | Х                   | Х                      |

| Timing Analyzer – Point-to-point                                |          | Х               | Х                   | Х                      |

| FSM Viewer                                                      |          | Х               | Х                   | Х                      |

| Crossprobing                                                    |          | Х               | Х                   | Х                      |

| Probe Point Creation                                            |          | Х               | Х                   | Х                      |

| Physical Design                                                 |          |                 |                     |                        |

| Design Plan File                                                |          |                 |                     | Х                      |

| Logic Assignment to Regions                                     |          |                 |                     | Х                      |

| Area Estimation and Region<br>Capacity                          |          |                 |                     | Х                      |

| Pin Assignment                                                  |          |                 |                     | Х                      |

| Physical Synthesis<br>Optimizations                             |          |                 |                     | Х                      |

| Graph-based Physical Synthesis                                  |          |                 | Х                   | Х                      |

| Island Timing Analyst                                           |          |                 | Х                   | Х                      |

| Physical Analyst                                                |          |                 | Х                   | Х                      |

| Prototyping                                                     |          |                 | Х                   | Х                      |

| Automatic translation of<br>Synopsys® DesignWare®<br>components |          |                 | х                   | х                      |

|                                             | Synplify | Synplify<br>Pro | Synplify<br>Premier                      | Synplify<br>Premier DP                   |

|---------------------------------------------|----------|-----------------|------------------------------------------|------------------------------------------|

| Team Design                                 |          |                 |                                          |                                          |

| Mixed Language Design                       |          | Х               | Х                                        | Х                                        |

| Modular Flow (certain<br>technologies)      |          | Х               | Х                                        | х                                        |

| Compile Points                              |          | Х               | Х                                        | Х                                        |

| True Batch Mode (Floating<br>licenses only) |          | Х               | Х                                        | Х                                        |

| GUI Batch Mode (Floating<br>licenses)       | Х        | Х               | Х                                        | ×                                        |

| Batch Mode Post-synthesis P&R<br>Run        | -        | Х               | Х                                        | ×                                        |

| Back-annotation of P&R Data                 | -        | -               | -                                        | Х                                        |

| Formal Verification Flow                    |          | X               | x<br>(Physical<br>synthesis<br>disabled) | x<br>(Physical<br>synthesis<br>disabled) |

| Identify Integration                        | Limited  | Х               | Х                                        | Х                                        |

| Back-annotation of P&R Data                 |          |                 |                                          | Х                                        |

| Design Environment                          |          |                 |                                          |                                          |

| Technical Resource Center                   | х        | Х               | Х                                        | Х                                        |

| Text Editor View                            | х        | Х               | Х                                        | Х                                        |

| Log Watch Window                            |          | Х               | Х                                        | Х                                        |

| Message Window                              |          | Х               | Х                                        | Х                                        |

| Tcl Window                                  |          | Х               | Х                                        | Х                                        |

| Workspaces                                  |          | Х               | Х                                        | Х                                        |

| Multiple Implementations                    |          | Х               | Х                                        | Х                                        |

| Vendor Technology/Family<br>Support         | Х        | Х               | Limited                                  | Limited                                  |

## Scope of the Document

The following explain the scope of this document and the intended audience.

### The Document Set

This user guide is part of a document set that includes a reference manual and a tutorial. It is intended for use with the other documents in the set. It concentrates on describing how to use the Synplify software to accomplish typical tasks. This implies the following:

- The user guide only explains the options needed to do the typical tasks described in the manual. It does not describe every available command and option. For complete descriptions of all the command options and syntax, refer to the User Interface Overview chapter in the Synopsys FPGA Synthesis Reference Manual.

- The user guide contains task-based information. For a breakdown of how information is organized, see *Getting Help*, on page 27.

### Audience

The Synplify, Synplify Pro, and Synplify Premier software tools are targeted towards the FPGA system developer. It is assumed that you are knowledge-able about the following:

- Design synthesis

- RTL

- FPGAs

- Verilog/VHDL

- Physical Synthesis

## **Getting Started**

This section shows you how to get started with the Synplify software. It describes the following topics, but does not supersede the information in the installation instructions about licensing and installation:

- Starting the Software, on page 27

- Getting Help, on page 27

- Requesting Technical Support, on page 28

### Starting the Software

- 1. If you have not already done so, install the Synplify software according to the installation instructions.

- 2. Start the software.

- If you are working on a Windows platform, select

Programs->Synplicity->product version from the Start button.

- If you are working on a UNIX platform, type the appropriate command at the command line:

synplify synplify\_pro synplify\_premier synplify premier dp

The command starts the synthesis tool, and opens the Project window. If you have run the software before, the window displays the previous project. For more information about the interface, see the User Interface Overview chapter of the *Reference Manual*.

### **Getting Help**

Before you call Synopsys Support, look through the documented information. You can access the information online from the Help menu, or refer to the PDF version. The following table shows you how the information is organized.

| For help with             | Refer to the                                                                          |

|---------------------------|---------------------------------------------------------------------------------------|

| Using software features   | Synopsys FPGA Synthesis User Guide                                                    |

| How to                    | Synopsys FPGA Synthesis User Guide, application notes on the support web site         |

| Flow information          | <i>Synopsys FPGA Synthesis User Guide</i> , application notes on the support web site |

| Error messages            | Online help (select Help->Error Messages)                                             |

| Licensing                 | Synopsys FPGA Licensing Document (PDF)                                                |

| Attributes and directives | Synopsys FPGA Synthesis Reference Manual                                              |

| Synthesis features        | Synopsys FPGA Synthesis Reference Manual                                              |

| Language and syntax       | Synopsys FPGA Synthesis Reference Manual                                              |

| Tcl syntax                | Online help (select Help->Tcl Help)                                                   |

| Tcl synthesis commands    | Synopsys FPGA Synthesis Reference Manual                                              |

| Product updates           | Synopsys FPGA Synthesis Reference Manual<br>(Web menu commands)                       |

### **Requesting Technical Support**

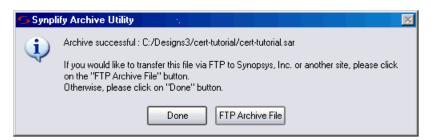

To request assistance from Technical Support for the Synopsys FPGA synthesis products, use the SolvNet Online Support utility - an online webbased interface from which you can submit your request form and attach project files. This is the preferred mechanism for contacting Technical Support and may facilitate a faster response than requesting support through email.

You can access SolvNet Online Support in one of these ways:

- From the tool: Tech-Support->Submit Support Request. This opens a wizard that walks you through the process of making a request and attaching related files from your project.

- From the tool: Tech-Support->Web Support.

- Through the link on the web page: http://solvnet.synopsys.com.

28

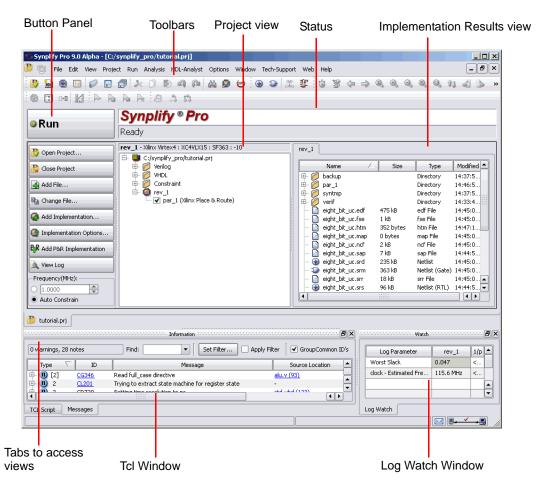

## User Interface Overview

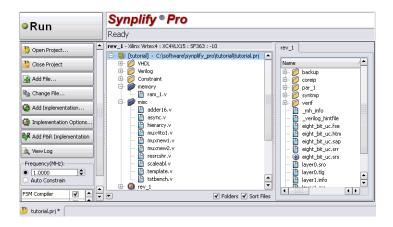

The user interface (UI) consists of a main window, called the Project view, and specialized windows or views for different tasks. For details about each of the features, see Chapter 2, *User Interface Overview* of the *Synopsys FPGA Synthesis Reference Manual*. The Synplify Pro and Synplify Premier tools have the same standard interface, while Synplify uses a different interface.

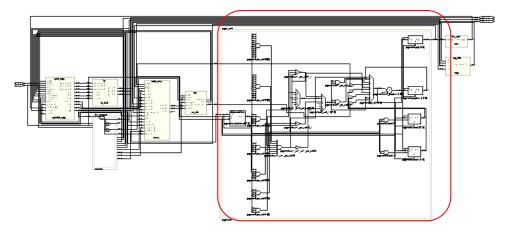

### Synplify Pro and Synplify Premier Standard Interface

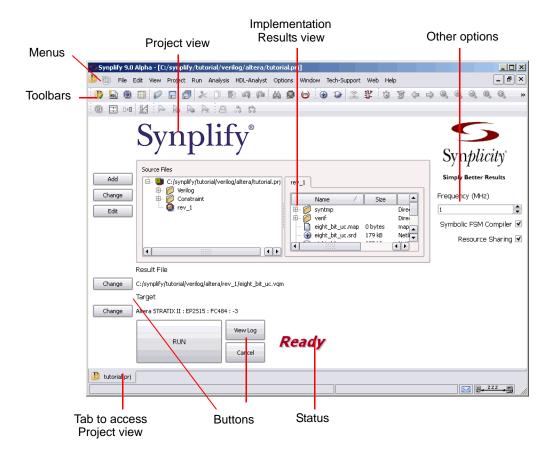

### **Synplify Interface**

The following figure shows you the Synplify interface.

#### Synopsys, Inc.

600 West California Avenue, Sunnyvale, CA 94086 USA Phone: +1 408 215-6000, Fax: +1 408 222-068 www.solvnet.com

Copyright © 2009 Synopsys, Inc. All rights reserved. Specifications subject to change without notice. Synopsys, Behavior Extracting Synthesis Technology, Certify, DesignWare, HDL Analyst, Identify, SCOPE, "Simply Better Results", SolvNet, Synplicity, the Synplicity logo, Synplify, Synplify ASIC, Symplify Pro, Synthesis Constraints Optimization Environment, and VCS are registered trademarks of Synopsys, Inc. BEST, Confirma, HAPS, HapsTrak, High-performance ASIC Prototyping System, IICE, MultiPoint, Physical Analyst, System Designer, and TotalRecall are trademarks of Synopsys, Inc. All other names mentioned herein are trademarks or registered trademarks of their respective companies.

### CHAPTER 2

# FPGA Logic and Physical Synthesis Flows

This describes the following tool flows:

- Logic Synthesis Design Flow, on page 32

- Synplify Premier Synthesis Design Flows, on page 35

- Actel Physical Synthesis, on page 52

- Altera Physical Synthesis, on page 60

- Xilinx Physical Synthesis, on page 69

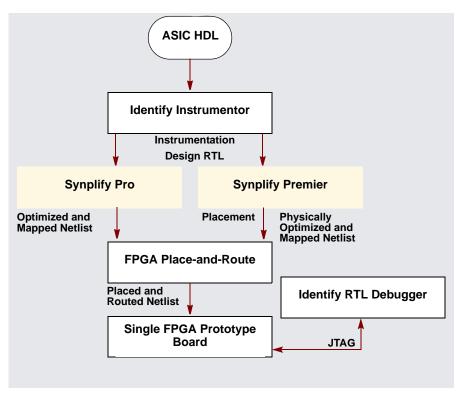

- Prototyping Design Flow, on page 80

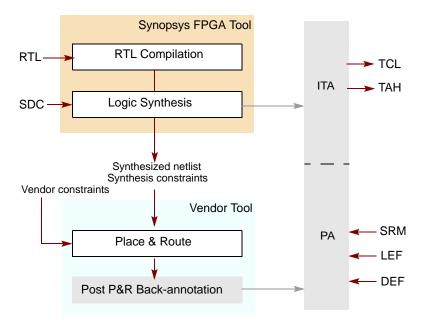

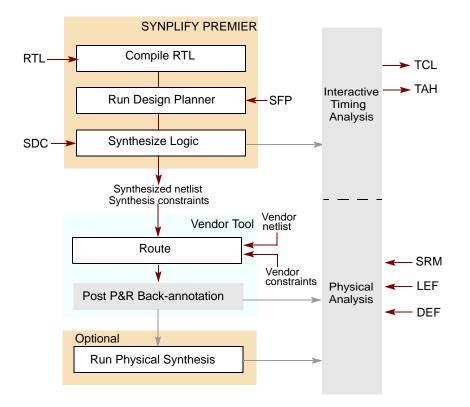

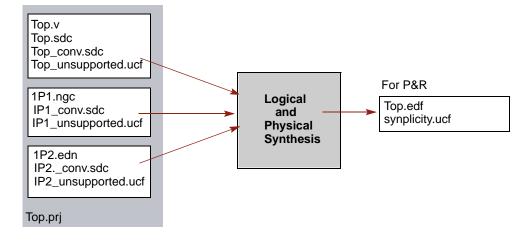

## Logic Synthesis Design Flow

The Synopsys FPGA tools synthesize logic by first compiling the RTL source, and then doing logical mapping and optimizations. After logic synthesis, you get a vendor-specific netlist and constraint file that you use as inputs to the place-and-route (P&R) tool.

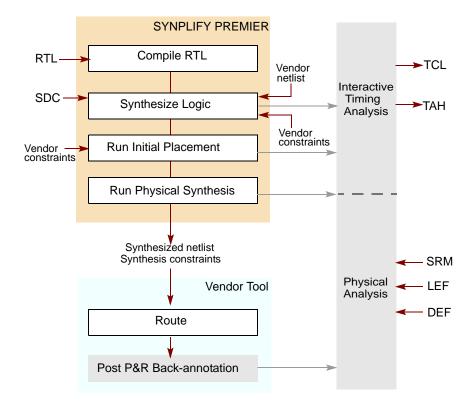

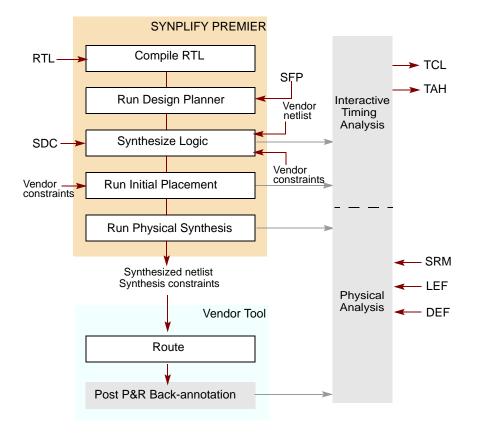

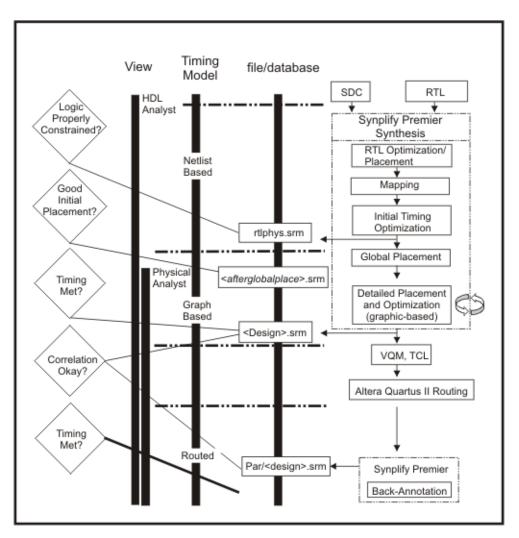

The following figure shows the phases and the tools used for logic synthesis and some of the major inputs and outputs. You can use the Synplify, Synplify Pro, or Synplify Premier synthesis software for this flow. The interactive timing analysis, physical analysis, and backannotation steps that are shown in gray are optional. Although the flow shows the vendor constraint files as direct inputs to the P&R tool, you should add these files to the synthesis project for timing black boxes.

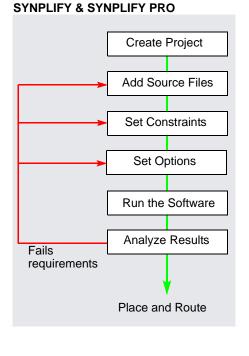

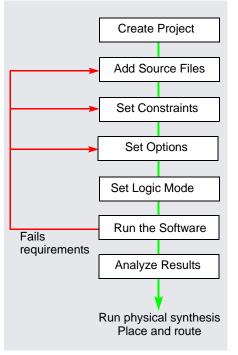

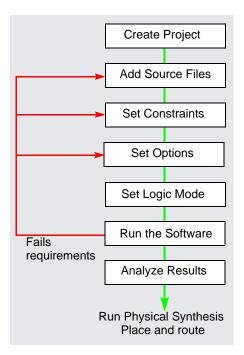

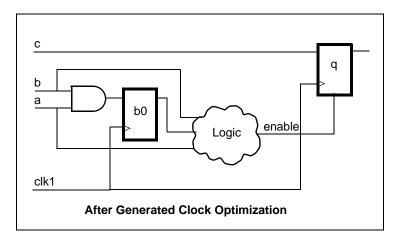

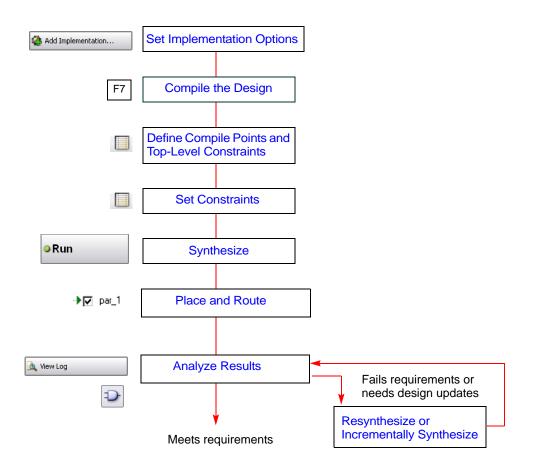

### Logic Synthesis Procedure

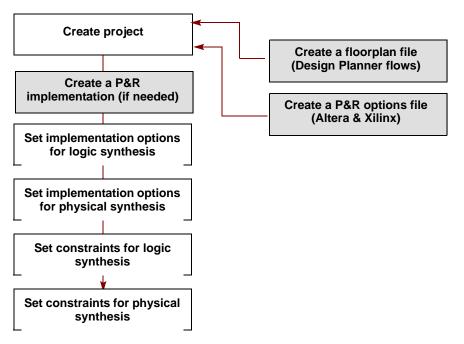

For a design flow with step-by-step instructions based on specific design data, download the tutorial from the website. The following steps summarize the process, which is also illustrated in the figure that follows.

1. Create a project.

- 2. Add the source files to the project.

- 3. Set attributes and constraints for the design.

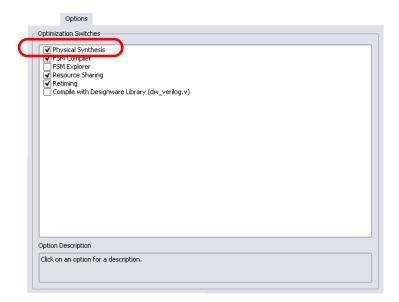

- 4. Set options for the implementation in the Implementation Options dialog box.

- 5. If you are running Synplify Premier in logic synthesis mode, disable the Physical Synthesis option in the Project view.

This setting directs the software to only run logic synthesis, without any physical optimizations. For other logic synthesis modes in the Synplify Premier tool, see *Fast Synthesis*, on page 481 and *Logic Synthesis with Enhanced Optimization*, on page 36.

- 6. Click Run to run logic synthesis.

- 7. Analyze the results, using the log file, the HDL Analyst schematic views, the Message window and the Log Watch window.

After you have completed the design, you can use the output files to run place-and-route with the vendor tool and implement the FPGA. If you are using the Synplify Premier software, you can choose to run physical synthesis before place-and-route.

The following figure lists the main steps in the flow:

### SYNPLIFY PREMIER

### Copyright © 2009 Synopsys, Inc. 34

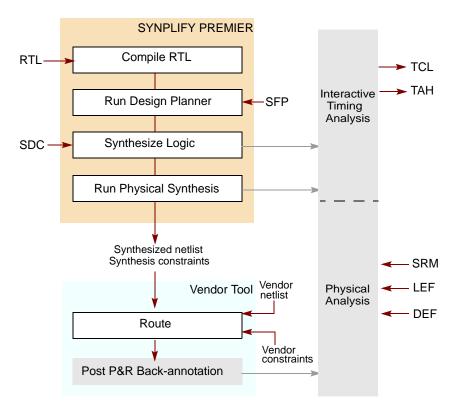

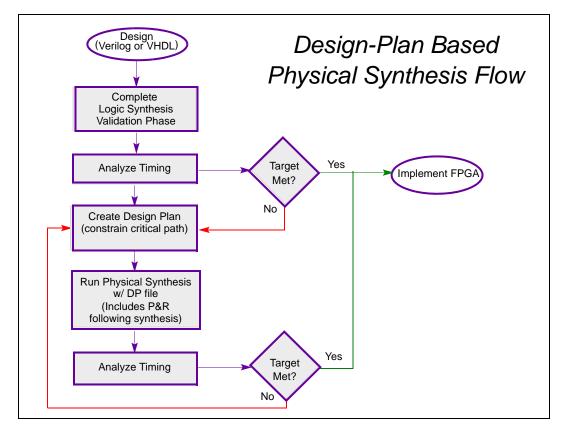

## Synplify Premier Synthesis Design Flows

You use the Synplify Premier tool to perform logic synthesis as well as physical synthesis. The logic synthesis flows let you run logic synthesis as a separate step. The physical synthesis flows include logic synthesis.

The following table lists the Synplify Premier logical and physical synthesis flows. Some of these flows are only available in certain technologies.

| Logic Synthesis Flows                                             |                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logic Synthesis Design Flow, on page 32                           | Same as Synplify Pro logic synthesis                                                                                                                                                                                                            |

| Logic Synthesis with Fast Synthesis                               | Synplify Premier logic synthesis with fast<br>synthesis runtimes. For details about this<br>flow, see <i>Fast Synthesis</i> , on page 481.                                                                                                      |

| Logic Synthesis with Enhanced<br>Optimization, on page 36         | Synplify Premier logic synthesis includes<br>additional optimizations during logic<br>synthesis and provides an output netlist<br>with better QoR than when running basic<br>logic synthesis. Enhanced Optimization is<br>turned on by default. |

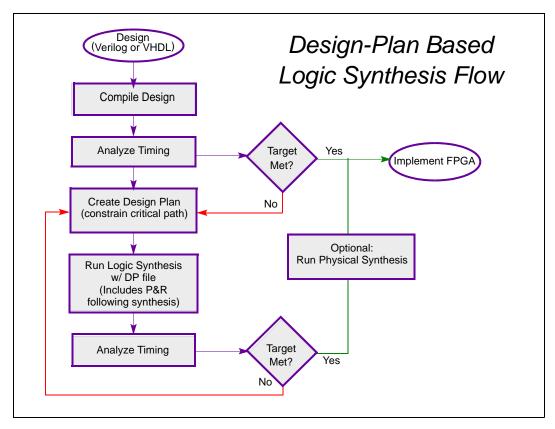

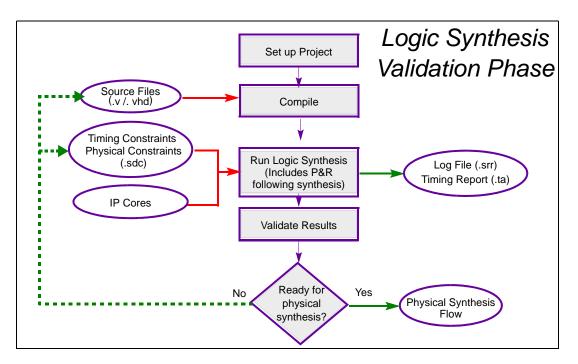

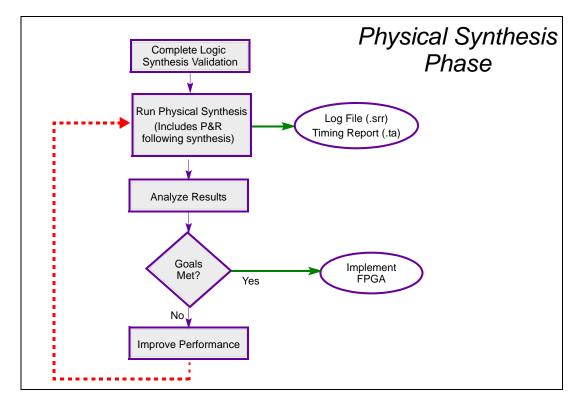

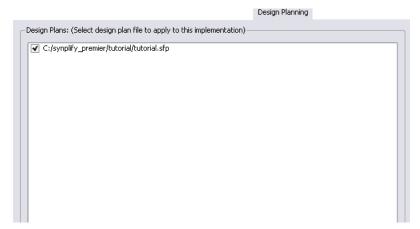

| Design Plan-Based Logic Synthesis,<br>on page 38                  | Synplify Premier logic synthesis with<br>placement constraints from a floorplan file<br>(needs Design Planner option)                                                                                                                           |

| Physical Synthesis Flows                                          |                                                                                                                                                                                                                                                 |

| Graph-Based Physical Synthesis, on<br>page 42                     | Automated physical synthesis. This includes the enhanced logic synthesis optimizations.                                                                                                                                                         |

| Graph-Based Physical Synthesis<br>with Design Planner, on page 46 | Automated physical synthesis that uses<br>floorplan file constraints (needs Design<br>Planner option)                                                                                                                                           |

| Design Plan-based Physical<br>Synthesis, on page 48               | Physical synthesis with placement<br>constraints from a floorplan file (needs<br>Design Planner option)                                                                                                                                         |

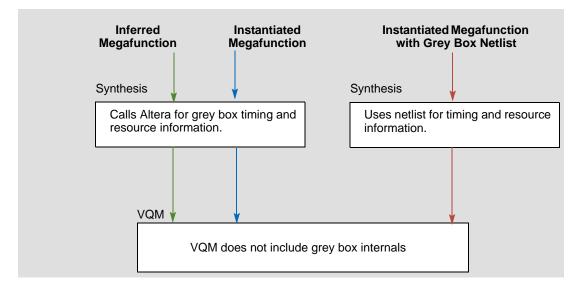

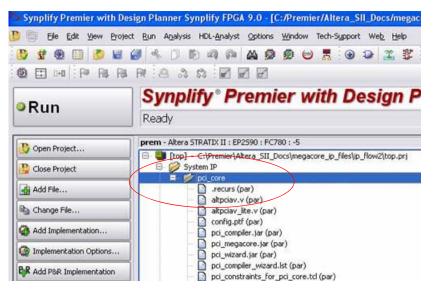

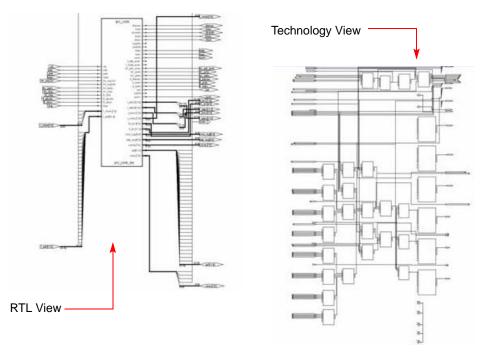

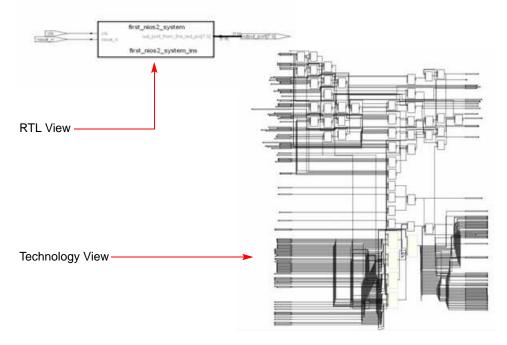

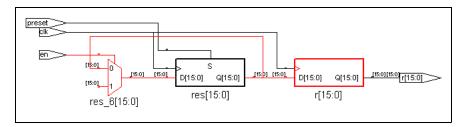

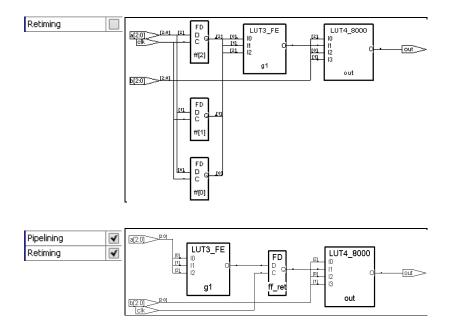

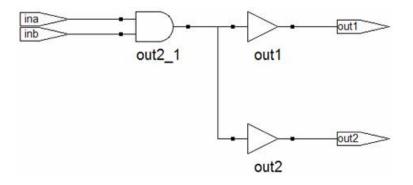

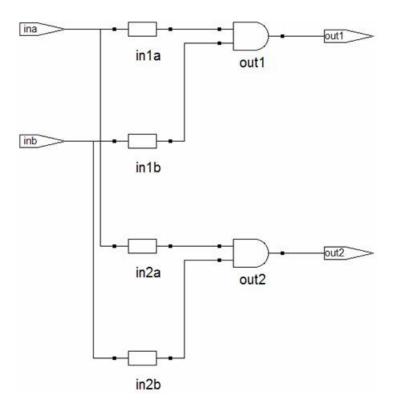

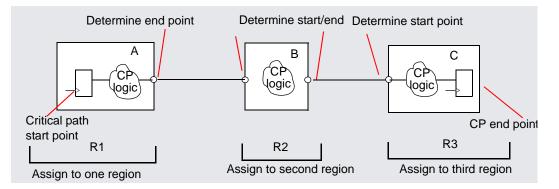

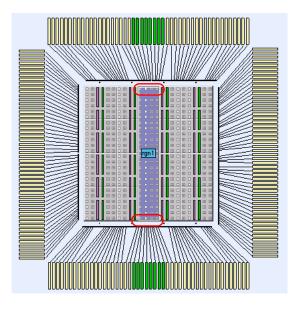

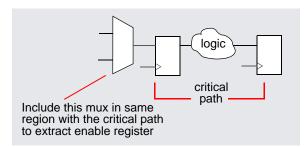

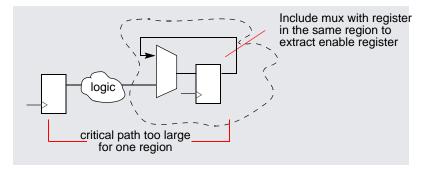

### Logic Synthesis with Enhanced Optimization