# FUNCTIONAL SPECIFICATION FOR SYSTEMC 2.0

Final

Version 2.0-P October 5, 2001

Copyright (c) 1996-2001 by all Contributors. All Rights reserved.

## **Copyright Notice**

Copyright © 1996-2001 by all Contributors. All Rights reserved. This software and documentation are furnished under the SystemC Open Source License (the License). The software and documentation may be used or copied only in accordance with the terms of the License agreement.

## **Right to Copy Documentation**

The License agreement permits licensee to make copies of the documentation. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any.

## **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and comply with them.

## Disclaimer

THE CONTRIBUTORS AND THEIR LICENSORS MAKE NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## Trademarks

SystemC and the SystemC logo are trademarks of Synopsys, Inc.

## **Bugs and Suggestions**

Please report bugs and suggestions about this document to

http://www.systemc.org

## CONTRIBUTORS

The contributors to this functional specification are the members of the SystemC Language Working Group.

- Stuart Swan, Cadence Design Systems, Inc.

- Dirk Vermeersch, CoWare, Inc.

- Dündar Dumlugöl, CoWare, Inc.

- Peter Hardee, CoWare, Inc.

- Takashi Hasegawa, Fujitsu Microelectronics, Inc.

- Adam Rose, Motorola

- Marcello Coppola, ST Microelectronics

- Martin Janssen, Synopsys, Inc.

- Thorsten Grötker, Synopsys, Inc.

- Abhijit Ghosh, Synopsys, Inc.

- Kevin Kranen, Synopsys, Inc.

# TABLE OF CONTENTS

| 1. In         | ntroduction                          | 6  |

|---------------|--------------------------------------|----|

| 1.1           | Brief review of SystemC 1.0          | 6  |

| 1.2           | Objectives of SystemC 2.0            | 7  |

| 1.3           | Communication and synchronization    | 8  |

| 1.4           | Models of computation within SystemC | 8  |

| 1.5           | Layered approach                     | 9  |

| 1.6           | Scope of this specification          | 10 |

| 1.7           | Document overview                    | 10 |

| 1.8           | Acknowledgements                     | 11 |

| PART I.       | CORE LANGUAGE                        | 12 |

| 2. G          | lossary of Terms                     | 13 |

| <b>3. P</b> 1 | rocesses                             | 14 |

| 3.1           | Process terminology                  | 14 |

| 3.2           | Process initialization               | 15 |

| <b>4.</b> M   | Iodel of Time                        | 16 |

| 4.1           | Absolute time vs. relative time      | 16 |

| 4.2           | Integer-valued vs. real-valued       | 16 |

| 4.3           | New model of time                    | 17 |

| 5. E          | vents and Dynamic Sensitivity        | 19 |

| 5.1           | wait() method                        | 19 |

| 5.2           | next_trigger() method                | 21 |

| 5.3           | Event type                           | 21 |

| 5.4           | SystemC scheduler                    | 22 |

| 5.5           | SystemC execution model              | 23 |

| 5.6           | Non-determinism in SystemC           | 24 |

| 6. In         | iterfaces, Ports, and Channels       | 26 |

| 7. In         | iterfaces                            | 27 |

| 7.1           | Interface examples                   | 27 |

| 7.2           | Interface base class                 | 28 |

| 7.3           | Layered communication example        | 28 |

| 8. P          | orts                                 | 31 |

| 8.1           | Attaching multiple interfaces        | 32 |

| 8.2           | Port base class                      | 34 |

| <i>8.3</i>    | Port examples                        | 36 |

| 8.4           | Port-less channel access             | 37 |

| 9. C          | hannels                              | 39 |

| 9.1           | Channel refinement                   | 39 |

| 9.2           | Sensitivity                          | 40 |

| <i>9.3</i>    | Design rules                         | 40 |

| 9.4           | Channel attributes                   | 42 |

| 10.           | Primitive Channels                   | 43 |

| 10.1         | Synchronization                     | 43  |

|--------------|-------------------------------------|-----|

| 10.2         | Primitive channel base class        | 43  |

| 10.3         | sc_signal <t></t>                   | 45  |

| 10.4         | sc_fifo <t></t>                     | 48  |

| 10.5         | sc_mutex                            | 52  |

| 10.6         | sc_mq                               | 53  |

| 10.7         | RGprotocol                          | 58  |

| 11.          | Hierarchical Channels               | 63  |

| 11.1         | Guidelines                          | 63  |

| 11.2         | Hierarchical channel example        | 64  |

| 11.3         | Composite channels                  | 68  |

| 11.4         | Typedefs                            | 69  |

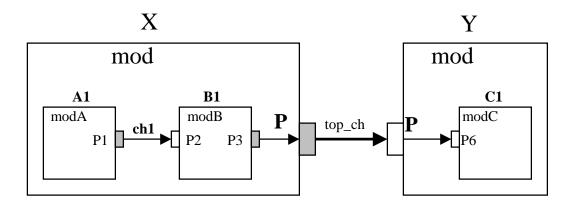

| 12.          | Communication Refinement            | 70  |

| <b>13.</b> I | Miscellaneous                       | 78  |

| 13.1         | Module inheritance and SC_CTOR      | 78  |

| 13.2         | end_of_elaboration() method         | 79  |

| 13.3         | Changes wrt SystemC 1.0             | 79  |

| 13.4         | Roadmap                             | 80  |

| PART II.     | ELEMENTARY CHANNELS                 | 81  |

| <b>14.</b> ] | Elementary Channels                 | 82  |

| PART III     | METHODOLOGY-SPECIFIC LIBRARIES      | 83  |

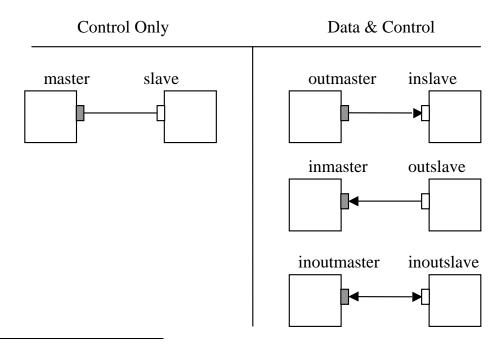

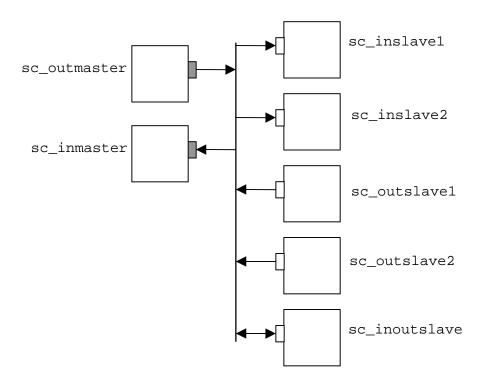

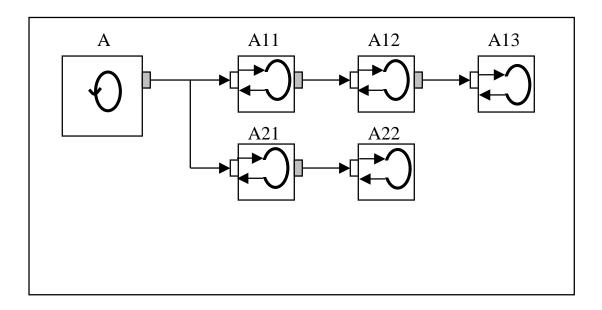

| <b>15.</b> I | Master-Slave Communication Library  | 84  |

|              | Functional level                    | 85  |

| 15.2         | Bus cycle accurate level            | 101 |

| 15.3         | Examples                            | 112 |

| Append       | ix A. Pseudo Code for the Scheduler | 129 |

# **1. INTRODUCTION**

This functional specification describes the system level modeling features made available in SystemC 2.0. First, the primary modeling constructs in SystemC 1.0 are briefly reviewed. Next, the new system level modeling constructs in SystemC 2.0 are introduced. We show how these new modeling constructs enable users to cleanly model communication and synchronization in systems and even allow users to implement new models of computation within SystemC. The new features for modeling communication and synchronization are sufficiently general that all of the existing mechanisms in SystemC 1.0 for communication and synchronization can now be constructed on top the new SystemC 2.0 features.

This specification assumes that the reader has some familiarity with C++ and with an HDL such as Verilog or VHDL. Furthermore, a full understanding of SystemC 2.0 requires an understanding of SystemC 1.0 as outlined in the SystemC 1.0 User's Guide. The SystemC language itself is entirely based on C++ and the modeling constructs within SystemC are provided as a C++ class library.

*Note*: SystemC 2.0 is a superset of SystemC 1.0, i.e., all SystemC 1.0 designs are still valid in SystemC 2.0.

## 1.1 BRIEF REVIEW OF SYSTEMC 1.0

SystemC 1.0 provides a set of modeling constructs that are similar to those used for RTL and behavioral modeling within an HDL such as Verilog or VHDL.

Similar to HDLs, users can construct structural designs in SystemC 1.0 using modules, ports, and signals. Modules can be instantiated within other modules, enabling structural design hierarchies to be built. Ports and signals enable communication of data between modules, and all ports and signals are declared by the user to have a specific data type. Commonly used data types include single bits, bit vectors, characters, integers, floating point numbers, vectors of integers, etc. SystemC 1.0 also includes support for four state logic signals (i.e. signals that model 0, 1, X, and Z).

An important data type that is found in SystemC 1.0 but not in HDLs is the fixed-point type. This type is used to model fixed-point numbers in digital signal processing applications. It is easy and natural to model fixed-point numbers in SystemC, but this is very difficult to do in HDLs.

In VHDL, concurrent behaviors are modeled using processes. In Verilog, concurrent behaviors are modeled using "always" blocks and continuous assignments. In SystemC 1.0, concurrent behaviors are also modeled using processes. A process can be thought of as an independent thread of control, which resumes execution when some set of events occur or some signals change, and then suspends execution after performing some action. In SystemC 1.0, there is a limited ability for specifying the condition under which a process resumes execution: the process can only be sensitive to changes of values of particular signals, and the set of signals to which the process is sensitive must be pre-specified before simulation starts.

Since processes execute concurrently and may suspend and resume execution at userspecified points, SystemC process instances generally require their own independent execution stack. (An equivalent situation in the software world arises in multi-threaded applications— each thread requires its own execution stack.) Certain processes in SystemC which suspend at restricted points in their execution do not actually require an independent execution stack— these processes types are termed "SC\_METHODs". Optimizing SystemC designs to take advantage of SC\_METHODs provides dramatic simulation performance improvements when the number of process instances in a design is large.

Hardware signals have several properties, which make modeling them in software non-trivial. Firstly, users often want to simulate hardware signals and registers as being initialized to "X" when simulation starts. This is useful for detecting reset problems in designs via X propagation techniques in simulation. In SystemC 1.0, this feature is provided within the  $sc_logic$  and  $sc_lv$  data types.

Secondly, hardware signals sometimes have multiple drivers. In this case a function is needed to compute a resolved value based on each of the driving values. This function must automatically be called when any of the driving values changes. For example, when a signal is driven with a 1 and a Z, the resolved value should be 1, but when driven with a 1 and a 0, the resolved value should be X. In SystemC1.0, resolved logic signals are provided to handle this modeling.

Thirdly, hardware signals do not immediately change their output value when they are assigned a new value, either in simulation or in the real world. There is always some delay (perhaps very small) until the new value assigned to a signal is made available to other processes in the design. This delay is crucial to proper modeling of hardware, since it allows for example two registers to swap values on a clock edge. In comparison two software variables cannot swap values without the introduction of a third temporary variable.

Like VHDL and Verilog, SystemC 1.0 supports the concept of delayed signal assignments and delta cycles in order to properly model hardware signals. A delta cycle can be thought of as a very small step of time within the simulation, which does not increase the user-visible time. Multiple delta cycles can occur at a given time point. When a signal assignment occurs, other processes do not see the newly assigned value until the next delta cycle. Processes that are sensitive to the signal resume execution if the signal value is changed with respect to its previous value.

#### 1.2 OBJECTIVES OF SYSTEMC 2.0

One of the primary goals of SystemC 2.0 is to enable system level modeling—that is, modeling of systems above the RTL level of abstraction, including systems which might be implemented in software or hardware or some combination of the two. One of the challenges in providing a system level design language is that there is a wide range of design models of computation, design abstraction levels, and design methodologies used in system design. To address this challenge in SystemC 2.0, a small but very general purpose modeling foundation has been added to the language. On top of this language foundation we can then add the more specific models of computation, design libraries, modeling guidelines, and design methodologies which are required for system design.

The small, general purpose modeling foundation in SystemC 2.0 is termed the "core language" and is the central component of the SystemC 2.0 standard.

Other components of the SystemC 2.0 standard include elementary library models which build on the core language (e.g. timers, FIFOs, signals, etc.) and which are widely applicable.

It is recognized that many different models of computation and design methodologies may be used in conjunction with SystemC. For this reason the design libraries and models needed to support these specific design methodologies are considered to be separate from the SystemC 2.0 core language standard.

## 1.3 <u>COMMUNICATION AND SYNCHRONIZATION</u>

Many of the language features already within SystemC 1.0 are also very useful for system level modeling.

The structural description features available in SystemC 1.0 (modules and ports) are also useful for system design, as are the extensive set of data types and the ability to express concurrency using processes. However the SystemC 1.0 mechanism for communication and synchronization—the hardware signal—is not sufficiently general for system level modeling. For example in a system level design a designer might want to specify that several modules communicate using queues, or that several processes execute concurrently and manage access to shared global data using mutexes.

SystemC 2.0 introduces a new set of features for generalized modeling of communication and synchronization. These are: channels, interfaces, and events. A channel is an object, which serves as a container for communication and synchronization. Channels implement one or more interfaces. An interface specifies a set of access methods to be implemented within a channel, but the interface itself does not provide the implementation. An event is a flexible, low-level synchronization primitive that is used to construct other forms of synchronization.

Channels, interfaces, and events enable designers to model the wide range of communication and synchronization found in system designs. Examples include HW signals, queues (FIFO, LIFO, message queues, etc.), semaphores, memories, and busses (both as RTL and transactionbased models).

## 1.4 MODELS OF COMPUTATION WITHIN SYSTEMC

People have been talking about models of computation quite a lot in recent years. This is probably because there are many different possible models of computation, and it is not always clear which one is best suited for a particular system design task. In the broadest sense, a model of computation is defined by the following:

- 1) The model of time employed (real-valued, integer-valued, untimed) and the event ordering constraints within the system (globally ordered, partially ordered, unordered).

- 2) The supported method(s) of communication between concurrent processes.

- 3) The rules for process activation.

In SystemC 2.0, the simple and flexible synchronization capabilities provided by events and the wait() method allow a broad range of different channel types to be implemented without having to change the underlying simulation engine. All the required functionality is already present in the simulation kernel. Thus, SystemC 2.0 supports a very powerful generic model of computation. While the global model of time is fixed to an integer model, designers can construct specific channels to achieve their precise rules for communication between processes, process activation, and system wide event ordering.

Although continuous time models as used for example in analog modeling cannot yet be constructed in SystemC, virtually any discrete time system can be modeled in SystemC. Some well-known models of computation, which can be quite naturally modeled in SystemC 2.0, include:

- Static Multi-rate Data-flow

- Dynamic Multi-rate Data-flow

- Kahn Process Networks

- Communicating Sequential Processes

- Discrete Event as used for

- RTL hardware modeling

- network modeling (e.g. waiting-room models)

- transaction-based SoC platform modeling

One example of how it is possible to achieve this layering of specific models of computation on top of the core language features within SystemC 2.0 is the hardware signal. In SystemC 1.0, the hardware signal was the only mechanism available for communication and synchronization between processes. In SystemC 2.0, the hardware signal is now implemented completely on top of channels, interfaces, and events. The SystemC 2.0 simulation kernel has no special support for hardware signals and is not aware if any are being used in a particular design. Note that this layering was introduced into SystemC in an unobtrusive way that enables existing SystemC 1.0 designs to continue to work unchanged in SystemC 2.0.

## 1.5 LAYERED APPROACH

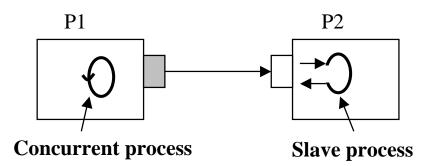

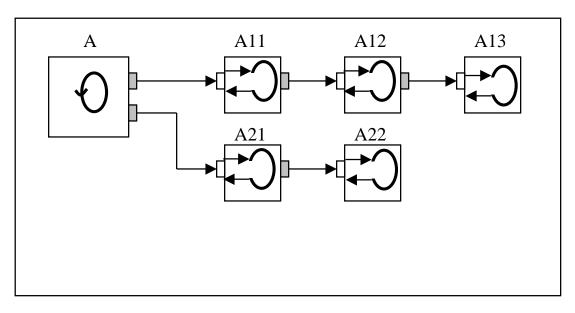

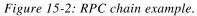

We are pursuing a layered approach (see Figure 1-1). The SystemC simulation kernel forms the base layer. In order to facilitate both the modeling at higher levels of abstraction as well as the creation of refined communication channels, we introduce *dynamic sensitivity* and extend the notion of *events* at the next layer. This allows defining *channel types* and *interfaces<sup>1</sup>* and, where needed, *ports* offering dedicated access methods. This layer implements the so-called *interface-method-call* (IMC) scheme, which supports e.g. dynamic master/slave relationships between

<sup>&</sup>lt;sup>1</sup> Interfaces are prerequisite to implement channels.

processes. Parts of SystemC 1.0, i.e., *signals*, will be implemented on top of the channels, interfaces and ports layer. The IMC scheme is a generalization of the RPC scheme as introduced in SystemC 1.1beta. Hence, the RPC scheme can be implemented on top of the other four layers.

| Remote Procedure Calls (RPC)   |

|--------------------------------|

| Signals                        |

| Channels, Interfaces and Ports |

| Events & Dynamic Sensitivity   |

| SystemC Simulation Kernel      |

| Figure | 1-1: | Layered | Approach. |

|--------|------|---------|-----------|

|        |      |         |           |

#### 1.6 SCOPE OF THIS SPECIFICATION

For SystemC to be successful as a system level modeling and IP delivery language, the following standards need to be in place.

- 1) The core language features which support system level modeling need to be defined and standardized.

- 2) Modeling guidelines which allow for interoperability of models from multiple vendors, and within multiple design flows, need to be established.

- 3) Library code which is not part of the core SystemC language definition, but which provides useful commonly used "utility" functionality needs to be developed and standardized. This library code will facilitate model interoperability and will make it easier for users to adopt SystemC.

- 4) Common design methodologies need to be established and proliferated.

A key point is that core language features need to be kept separate from modeling guidelines, library code, and design methodologies. In other words, the core language features should be general and support a wide variety of modeling styles and design methodologies.

By keeping the core language small and general purpose, we will make SystemC easier to use and implement.

#### 1.7 DOCUMENT OVERVIEW

This functional specification is organized in three parts. The first and biggest part describes the core language features. The second part describes the elementary channels that are part of SystemC, and the third part describes methodology-specific channels, such as the sc\_link\_mp channel, which is part of the master-slave communication library. An appendix contains the pseudo-code of the SystemC 2.0 scheduler.

## 1.8 <u>ACKNOWLEDGEMENTS</u>

Many companies and individuals have contributed time and resources in the development of both SystemC 1.0 and SystemC 2.0. Some of these contributors are listed in the contributors section of this specification and in the SystemC 1.0 User's Guide.

It should be noted that the fundamental mechanisms used to model communication and synchronization in SystemC 2.0 – interfaces, channels, and events – were inspired by similar constructs in Professor Daniel Gajski's SpecC language. (For further information, see "SpecC: Specification Language and Methodology" at www.wkap.nl).

# PART I. CORE LANGUAGE

# 2. GLOSSARY OF TERMS

The most common terms used in this document are explained in Table 2-1. Terms related to processes are explained in the following chapter.

Table 2-1: General terminology.

| Method               | A C++ method, i.e., a member function of a class.                                                                                                                                                                                        |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Module               | A structural entity, which can contain processes, ports, channels, and other modules. Modules allow expressing structural hierarchy.                                                                                                     |

| Interface            | An interface provides a set of method declarations, but provides no method implementations and no data fields.                                                                                                                           |

| Channel              | A channel implements one or more interfaces, and serves as a container for communication functionality.                                                                                                                                  |

| Port                 | A port is an object through which a module can access a channel's interface. But modules can also access a channel's interface directly.                                                                                                 |

| Primitive Channel    | A primitive channel is atomic, that is, it doesn't contain processes or modules, and it cannot directly access other channels.                                                                                                           |

| Hierarchical Channel | A hierarchical channel is a module, that is, it can contain processes and other modules, and it can directly access other channels.                                                                                                      |

| Event                | A process can suspend on, or be sensitive to, one or more events.<br>Events allow for resuming and activating processes.                                                                                                                 |

| Sensitivity          | The sensitivity of a process defines when this process will be resumed<br>or activated. A process can be sensitive to a set of events. Whenever<br>one of the corresponding events is triggered, the process is resumed or<br>activated. |

| Static Sensitivity   | The sensitivity of the process is declared statically; i.e., it is declared during elaboration and cannot be changed once simulation has started. A so-called sensitivity list is used to define the static set of events.               |

| Dynamic Sensitivity  | The sensitivity of a process can be altered during simulation.                                                                                                                                                                           |

| ІМС                  | Interface Method Call                                                                                                                                                                                                                    |

| RPC                  | Remote Procedure Call                                                                                                                                                                                                                    |

# **3. PROCESSES**

*Note*: In the SystemC 1.0 Users' Guide, the term "process" is used to denote an SC\_THREAD ("thread process"), SC\_METHOD ("method process"), or SC\_CTHREAD ("clocked thread process"). We will continue to use these terms, but we will also make the distinction between process (method) and its thread-of-execution more clear.

Processes play a central role in SystemC. They describe the functionality of the system, and allow expressing concurrency in the system. Processes are contained in modules, and they access external channel interfaces through the ports of a module. There are different types of processes, and different ways to activate processes. Before diving into the details, the terms related to processes are explained.

## 3.1 PROCESS TERMINOLOGY

To avoid any confusion in terminology, we first define the terms related to processes in Table 3-1.

| Thread               | A SystemC thread has its own thread of execution, but is not preemptive.         |

|----------------------|----------------------------------------------------------------------------------|

| Automatically        | Certain module methods (processes) are activated automatically when              |

| activated            | events occur that the processes are sensitive to.                                |

| ucmraita             | events occur that the processes are sensitive to.                                |

| Explicitly activated | Certain module methods must be called explicitly by other code in order to       |

| 1 5                  | be activated.                                                                    |

|                      |                                                                                  |

| wait()               | A method that suspends execution of a thread. The arguments passed to            |

|                      | wait() determine when execution of the thread is resumed.                        |

|                      |                                                                                  |

| Ok to call wait()    | SC_METHODS and the code that they call cannot call wait(), because they          |

|                      | don't have their own thread of execution. SC_THREADS and the code that           |

|                      | they call can call wait().                                                       |

|                      |                                                                                  |

| SC_THREAD            | A module method which has its own thread of execution, and which can             |

|                      | call code that calls wait(). SC_THREADS are automatically activated. Also        |

|                      | known as thread process.                                                         |

|                      |                                                                                  |

| SC_METHOD            | A module method which does not have its own thread of execution, and             |

|                      | which cannot call code that calls wait(). SC_METHODs are automatically           |

|                      | activated. Also known as method process.                                         |

|                      |                                                                                  |

| SC_CTHREAD           | A module method which has its own thread of execution, and which only            |

|                      | has a positive or negative clock edge event in its sensitivity list. It can call |

|                      | code that calls wait() with a restricted argument list. SC_CTHREADS are          |

|                      | code that cans wate() with a restricted argument list. SC_CTHREADS are           |

Table 3-1: Process terminology.

| automatically activated. Also known as clocked thread process. |

|----------------------------------------------------------------|

|                                                                |

*Note*: All forms of wait() need to dynamically check that the current process (i.e., the top level caller) is not an SC\_METHOD.

## 3.2 PROCESS INITIALIZATION

In SystemC 1.0, thread processes are not executed during the initialization phase of the simulation. Method processes are executed during the initialization phase of the simulation if they are made sensitive to input signals/ports. In VHDL, the initialization behavior is to execute them all during the initialization phase of the simulation.

The SystemC 2.0 scheduler will execute all thread processes and all method processes during the initialization phase of the simulation. If the behavior of a thread process is different between SystemC 1.0 and SystemC 2.0, insert one wait() statement before the infinite loop of the thread process.

## 4. MODEL OF TIME

In SystemC 1.0, a real-valued and relative model of time is employed, i.e., the global clock is of type double and its time units do not have any relationship to absolute time, such as seconds or nanoseconds. For IP exchange, is should be possible to specify absolute time. Furthermore, an integer-valued model of time has certain advantages over a real-valued model of time. SystemC 2.0 uses an absolute and integer-valued model of time.

## 4.1 ABSOLUTE TIME VS. RELATIVE TIME

In SystemC 1.0, we can create a clock as follows:

```

sc_clock clk( "clk", 20 );

```

This creates a clock with a period of 20 time units. The user can *interpret* this as 20 nanoseconds, or 20 seconds, etc. If there are other clocks in the system, the interpretation of the time unit should be the same. But SystemC does not enforce or check this, since the time unit is relative. It is not possible to deliver an IP block that has a clock with a period of, for example, exactly 20 nanoseconds, independent of the system it is integrated into.

What we want to be able to write is, for example

```

sc_clock clk( "clk", 20, SC_NS );

```

, or

```

sc_time t1( 20, SC_NS );

sc_clock clk( "clk", t1 );

```

, which in both cases creates a clock with a period of 20 nanoseconds.

#### 4.2 INTEGER-VALUED VS. REAL-VALUED

A real-valued model of time has the advantage that the (dynamic) range of time values is much larger than in an integer-valued model of time. But when we look at problems such as underflow, overflow, and rounding of time values when additions or conversions occur, an integer-valued model of time has clear advantages.

Underflow can occur, for example, when a very small time value is added to a very large time value. With real-valued time values, this results in the very large time value (i.e., the very small time value is "lost"). With integer-valued time values, underflow cannot occur.

Overflow occurs when the resulting time value cannot be represented by the underlying data type. With integer-valued time values this is more of a problem then with real-valued time values.

The last problem has to do with rounding. If time is represented as an integer, then models may try to wait for a period of time which does not exactly match integer time units. This will be particularly common if delays are computed by estimation or delay calculation tools.

The biggest problem is underflow, because it's difficult to detect and prevent. The overflow and rounding problems are easy to detect and easy to report to the user in a sensible way. Hence, the integer-valued model of time is preferred over the real-valued model of time, provided that the underlying integer data type can represent a sufficiently large range of time values.

## 4.3 <u>NEW MODEL OF TIME</u>

In SystemC 2.0, the underlying data type for time is a 64 bit unsigned integer<sup>2</sup>. The default *time resolution*<sup>3</sup> is 1 picosecond. The user can change the time resolution with function  $sc_set_time_resolution()$ . For example,

sc\_set\_time\_resolution( 10, SC\_PS );

The following restrictions apply to setting the time resolution.

- The time resolution must be a power of ten.

- The time resolution can only be specified before the start of simulation.

- The time resolution can only be specified once.

- The time resolution can only be specified before any sc\_time declaration.

For example,

```

sc_set_time_resolution( 10, SC_PS );

...

wait( 3.456, SC_NS );

```

rounds the time to wait to 3460 ps.

It is possible to get the current time resolution with function sc\_get\_time\_resolution(), which does not take any arguments and returns a value of type sc\_time. This function can be called anywhere in the code (i.e., before or after the start of simulation).

SystemC will provide a type **sc\_time** to specify time values. A variable of type sc\_time can be created with two arguments: an argument of type double and an argument of type sc\_time\_unit. Type sc\_time\_unit is an enumerated type with the following values.

- SC\_FS femtoseconds

- SC\_PS picoseconds

- SC\_NS nanoseconds

<sup>&</sup>lt;sup>2</sup> As in VHDL and Verilog.

<sup>&</sup>lt;sup>3</sup> Also known as minimum resolvable time unit.

- SC\_US microseconds

- SC\_MS milliseconds

- SC\_SEC seconds

Type sc\_time defines the copy constructor, the assignment operator, and the relational and equality operators.

For backward compatibility with SystemC 1.0, the *default time unit* is assumed to be 1 nanosecond. The default time unit can be changed by the user with function **sc\_set\_default\_time\_unit()**. To change the default time unit to 1 picosecond, for example, specify the following.

```

sc_set_default_time_unit( 1, SC_PS );

```

The following restrictions apply to setting the default time unit.

- The default time unit must be a power of ten.

- The default time unit must be larger than or equal to the time resolution.

- The default time unit can only be specified before the start of simulation.

- The default time unit can only be specified once.

For example,

```

sc_set_default_time_unit( 100, SC_PS );

...

sc_clock clk1( "clk1", 10 );

```

sets the clock period for clk1 to 1000 ps.

It is possible to get the current default time unit with function **sc\_get\_default\_time\_unit()**, which does not take any arguments and returns a value of type sc\_time. This function can be called anywhere in the code (i.e., before or after the start of simulation).

Although still legal, the following old forms of sc\_clock and sc\_start are discouraged.

```

sc_clock clk1( "clk1", 15 );

sc_start( 1000 );

```

Instead, the following new forms of sc\_clock and sc\_start should be used.

sc\_clock clk1( "clk1", 15, SC\_NS ); sc\_start( 1000, SC\_NS );

# 5. EVENTS AND DYNAMIC SENSITIVITY

With SystemC 1.0, processes can be sensitive to events on input signals/ports only. Process sensitivity is statically defined, i.e., it cannot change during simulation. In SystemC 2.0, dynamic sensitivity allows for making processes sensitive to events on e.g. both input and output ports. The dynamic sensitivity of a process can be altered during simulation.

To be able to implement dynamic sensitivity, we use the SystemC 1.0 scheduling paradigm with an extended notion of events. The latter is needed because events are supported to a limited extend in SystemC 1.0. This extension requires only minor changes in the SystemC 1.0 simulation kernel.

## 5.1 <u>WAIT() METHOD</u>

In SystemC 1.0, static sensitivity is supported with a sensitivity list for each process in a module. These sensitivity lists are defined in the constructor of a module. Consider the following example.

Example 5-1: Static sensitivity.

```

SC_MODULE( my_module )

{

// ports

sc_in<int> input;

sc_in_clk clock;

// processes

void proc_a();

void proc_b();

// constructor

SC_CTOR( my_module )

{

SC_THREAD( proc_a );

sensitive_pos << clock;</pre>

SC_THREAD( proc_b );

sensitive << input;</pre>

sensitive_neg << clock;</pre>

}

};

```

In the above example, there are two thread processes in the module. Process proc\_a is sensitive to the positive edge of the clock, whereas proceb is sensitive to a change in value on input and to a negative edge of the clock<sup>4</sup>. These sensitivity lists are static, i.e., they cannot change during simulation.

<sup>&</sup>lt;sup>4</sup> In SystemC 2.0, "sensitive <<" takes events as arguments. The ports that can be used as arguments in SystemC 1.0 (and 2.0) are a special case, for which the default event from the signal (or channel) attached to the port is actually used.

In some cases, we want a process to be sensitive to a specific event or a specific collection of events, and this may change during simulation. This dynamic sensitivity is possible by using the **wait()** method. This method has been extended to allow specifying one or more events or a collection of events to wait for. For example:

Example 5-2: Dynamic sensitivity with the wait() method.

// wait until event el has been notified

wait( el );

...

// wait until event el or event e2 has been notified

wait( el | e2 );

...

The wait() method can be called anywhere in the thread of execution of a thread process. When it is called, the specified events will temporarily overrule the sensitivity list, and the calling thread process will suspend. When one (or all) of the specified events is notified, the waiting thread process is resumed. The calling process is again sensitive to the sensitivity list.

When the wait() method is called without arguments, the calling thread process will suspend. When one of the events in the sensitivity list is notified, the waiting thread process is resumed. The static sensitivity of the calling thread process doesn't change. In SystemC 1.0, the wait() method without arguments is already supported.

In addition to events, it is also possible to wait for time. This can be used, for example, as a timeout when waiting for one or more events.

The following forms of wait() are supported.

```

// wait on events in sensitivity list (SystemC 1.0).

wait();

// wait on event el.

wait( e1 );

// wait on events e1, e2, or e3.

wait( e1 | e2 | e3 );

// wait on events e1, e2, and e3.

wait( e1 & e2 & e3 );

// wait for 200 ns.

wait( 200, SC_NS );

// wait on event el, timeout after 200 ns.

wait( 200, SC_NS, e1 );

// wait on events e1, e2, or e3, timeout after 200 ns.

wait( 200, SC_NS, e1 | e2 | e3 );

// wait on events e1, e2, and e3, timeout after 200 ns.

wait( 200, SC_NS, e1 & e2 & e3 );

sc_time t( 200, SC_NS );

```

// wait for 200 ns.

wait( t );

// wait on event el, timeout after 200 ns.

wait( t, el );

// wait on events el, e2, or e3, timeout after 200 ns.

wait( t, el | e2 | e3 );

// wait on events el, e2, and e3, timeout after 200 ns.

wait( t, el & e2 & e3 );

// wait for 200 clock cycles, SC\_CTHREAD only (SystemC 1.0).

wait( 200 );

// wait one delta cycle.

wait( 0, SC\_NS );

// wait one delta cycle.

wait( SC\_ZERO\_TIME );

The semantics of the wait() method with one or more event arguments, is that the method returns (i.e., thread of execution is resumed) either when at least one of the events is notified, or when all events are notified. The former is specified with the |-operator between event arguments, the latter is specified with the &-operator between event arguments. A mixture of |-operators and &-operators is not supported in SystemC 2.0.

## 5.2 <u>NEXT\_TRIGGER() METHOD</u>

The wait() method can only be used with SC\_THREAD processes. The equivalent function for SC\_METHOD processes is the next\_trigger() method. The next\_trigger() method takes the same arguments as the wait() method. The differences between next\_trigger() and wait() are as follows.

- The next\_trigger() method returns immediately, without passing control to another process.

- Multiple next\_trigger() calls are allowed in one activation of an SC\_METHOD process. The last next\_trigger() call determines the (dynamic) sensitivity for the next activation.

After this high level view on dynamic and static sensitivity, the next sections will go into some more details regarding the event type that is needed for supporting dynamic sensitivity, and the SystemC scheduler.

## 5.3 EVENT TYPE

SystemC 1.0 provides a fixed set of channels and corresponding events. To support userdefined channel types, i.e., an extendable set of channel types, the set of events must also be extendable. To that purpose, we introduce the event type **sc\_event**. The implementation and the behavior of this type in SystemC 2.0 are described next.

The event type sc\_event provides the following functionality.

Constructor – An event object can be created by calling the constructor without any arguments. For example,

```

sc_event my_event;

```

Notify – An event can be notified by calling the (non-const) notify() method of the event object. For example,

```

my_event.notify(); // notify immediately

my_event.notify( SC_ZERO_TIME ); // notify next delta cycle

sc_time t( 10, SC_NS );

my_event.notify( t ); // notify in 10 ns

```

In addition, functions are provided allowing a functional notation for notifying events. For example,

```

notify( my_event ); // notify immediately

notify( SC_ZERO_TIME, my_event ); // notify next delta cycle

sc_time t( 10, SC_NS );

notify( t, my_event ); // notify in 10 ns

```

Cancel – An event notification can be cancelled by calling the (non-const) cancel() method of the event object. For example,

```

my_event.cancel(); // cancel a delayed notification

```

• The copy constructor and assignment operator of the event type are disabled.

A channel can construct any number of event objects – one for each type of event it can generate. A channel can notify an event by calling one of the notify methods of the event object. However, creation and notification of events is not restricted to channels.

For a pseudo code description of the event type, see Appendix A.

## 5.4 SYSTEMC SCHEDULER

The scheduler's task is to determine the order of execution of processes within the design based on the event sensitivity of the processes and the event notifications which occur.

The SystemC scheduler has support for both software and hardware-oriented modeling.

Similar to VHDL and Verilog, the SystemC scheduler supports delta cycles. A delta cycle is comprised of separate evaluate and update phases, and multiple delta cycles may occur at a particular simulated time. Delta cycles are useful for modeling fully-distributed, time-synchronized computation as found for example in RTL hardware. In SystemC, using notify() with a zero time argument causes the event to be notified in the evaluate phase of the next delta cycle, while a call to request\_update() causes the update() method to be called in the update phase of the current delta cycle. Using these facilities, channels which model the behavior of hardware signals can be constructed.

SystemC also supports timed event notifications. Timed event notifications are specified using notify() with a time argument. A timed notification causes the specified event to be

notified at a specified time in the future. Timed notifications are found in both VHDL and Verilog and are also useful in modeling software systems.

Lastly, SystemC supports immediate event notifications, which are specified using notify() with no arguments. An immediate event notification causes processes which are sensitive to the event to be made immediately ready to run (i.e. ready to run in the current evaluate phase.) Immediate event notifications are useful for modeling software systems and operating systems, which lack the concept of delta cycles.

The following steps outline the execution of the SystemC scheduler. More detailed pseudocode for the scheduler is included in Appendix A of this document.

- 1) *Initialization Phase* Execute all processes (except SC\_CTHREADS) in an unspecified order.

- Evaluate Phase Select a process that is ready to run and resume its execution. This may cause immediate event notifications to occur, which may result in additional processes being made ready to run in this same phase.

- 3) If there are still processes ready to run, go to step 2.

- 4) Update Phase Execute any pending calls to update() resulting from request\_update() calls made in step 2.

- 5) If there are pending delayed notifications, determine which processes are ready to run due to the delayed notifications and go to step 2.

- 6) If there are no more timed notifications, simulation is finished.

- 7) Advance the current simulation time to the earliest pending timed notification.

- 8) Determine which processes are ready to run due to the events that have pending notifications at the current time. Go to step 2.

## 5.5 <u>SYSTEMC EXECUTION MODEL</u>

The SystemC simulation kernel relies on a co-routine execution model. Processes have independent threads of execution which have their own execution stack. Transfer of control from one thread of execution to another always happens at precisely identified points: threads can only suspend and resume execution when they call wait() (or, equivalently, when SC\_METHOD processes return control to the simulator). The SystemC simulation kernel will never pre-empt execution of a thread as an RTOS might – instead, an executing thread must always yield execution by calling wait().

Because transfer of control between threads only happens when a thread calls wait(), SystemC models can be written without concern that a thread may be pre-empted involuntarily. Specifically, the code within a thread delimited by two wait() statements can safely assume that no other threads have modified any variables which are also accessible to other threads. (This makes it much easier to write high level models for channels than would be the case if preemption were an issue.)

Like Verilog and VHDL, SystemC models the execution of code within a thread between two wait() statements as happening instantaneously. Simulated time can only advance once a wait() statement has been called.

The execution model described above does not prevent SystemC from being used to model pre-emptive software systems. In order to model a pre-emptive software system, the expected execution delay of the target architecture must be incorporated into the SystemC model. For example, if the inner body of a loop takes 1 millisecond to execute in a target architecture, then a SystemC model might be written as:

```

while( ... ) {

... // code for inner body of loop

wait( 1, SC_MS );

}

```

In this case, the execution delay of the loop is accounted for, and if other threads are ready to run in the design at the same time, it's possible that execution of the loop body might be pre-empted at the point where it calls wait().

## 5.6 NON-DETERMINISM IN SYSTEMC

Non-determinism is always a factor to consider when specifying and implementing concurrent systems. Often concurrent systems may have locally non-deterministic properties that are intentional, while still exhibiting deterministic global behavior. For example, at a very low level, individual packets transmitted over the internet may take unpredictable routes to reach their destination or may be lost altogether, but at a higher level reliable connections can be established over the internet. As another example, within a dataflow or process network model of computation, the order of execution of particular processes may be non-deterministic, but the overall result of the execution of such systems will always be deterministic.

Of course, it is also possible that local non-deterministic behavior may result in undesirable global non-deterministic behavior. A good example of this is when your PC boots fine one day but crashes the next day. A more specific example might be two threads which are scheduled to run at the same time and which both attempt to assign a global variable to a different value. In this case it is unpredictable what value the variable will have after the threads execute.

Just as in real software systems, non-determinism can be present in SystemC designs. In some cases this may be intentional because it is a property of the system that is being specified and modeled, while in other cases it may be undesirable because it represents a flaw in the design.

At a fundamental level, non-determinism in SystemC is introduced because the order of thread execution within a particular simulation phase (or part of a simulation delta cycle) is unspecified (or is "non-deterministic"). In a properly designed system, this aspect of SystemC will not affect the overall behavior of the system. But in an improperly designed system, it is possible that it might result in undesirable effects: the system might behave unpredictably from one simulation run to the next (assuming the design or the stimulus has changed), or, even worse, an implementation of the system derived from the specification might not work properly.

There are several things designers can do to control non-determinism in SystemC designs.

- First, they can use channels such as hardware signals (sc\_signal, etc) and fifos, which always result in globally deterministic behavior.

- Second, they should be aware that the order of thread execution within a particular simulation phase is unspecified.

- Third, they can use command line options to the SystemC simulator to randomize the order of execution of threads within each simulation phase. This feature is useful for detecting design flaws resulting from inadequate synchronization within design specifications.

As noted above, the order in which the scheduler selects threads to run within each simulation phase is unspecified and implementation-dependent. However, when the same design is simulated multiple times using the same stimulus and the same version of the simulator, the thread ordering between different runs will not vary.

# 6. INTERFACES, PORTS, AND CHANNELS

The necessary building blocks for process synchronization and communication refinement are (user-defined) interfaces, ports, and channels. An interface defines a set of methods, but does not implement these methods. It is a pure functional object without any data in order not to anticipate implementation details. A channel implements one or more interfaces. A port enables a module, and hence its processes, accessing a channel's interface. A port is defined in terms of an interface type, which means that the port can be used only with channels that implement that interface type.

With channels, we make a distinction between so-called *primitive channels* and *hierarchical channels*. Primitive channels do not exhibit any visible structure, do not contain processes, and cannot (directly) access other primitive channels. Hierarchical channels, on the other hand, are modules, which means they can have structure, they can contain other modules and processes, and they can (directly) access other channels.

The use of interfaces enables a very powerful scheme called *interface-method-call* (IMC). IMC refers to a process calling an interface method of a channel. The interface method is implemented in the channel, but it is executed in the context of the caller (the process). An example of an interface method is a blocking read method of a FIFO. When calling this interface method, the caller (process) can be suspended if there is not enough data available.

In the following chapters, the individual building blocks are addressed.

# 7. INTERFACES

An interface provides a set of method declarations, but provides no method implementations and no data fields. Interfaces are used to define sets of methods that channels must implement. Ports are connected to channels through interfaces. A port that is connected to a channel through an interface sees only those channel methods that are defined by the interface. A port is not able to access any other method or data field in the channel. SystemC 2.0 allows users to define their own interfaces.

## 7.1 INTERFACE EXAMPLES

Below, the implementations of three example interfaces are given. The first example interface defines a read interface. The second example interface defines a write interface. Both the read interface and the write interface derive from interface base class sc\_interface, which is described in the next section. The third example interface defines a read/write interface by deriving from the read interface and write interface. Note that all interface methods are pure virtual methods, i.e., they don't have an implementation.

*Example 7-1: A read, write, and read/write interface.*

```

// ------

// An example read interface: sc_read_if

// this interface provides a `read' method

// ------

template <class T>

class sc_read_if

: virtual public sc_interface

{

public:

// interface methods

virtual const T& read() const = 0;

};

// ------

// An example write interface: sc_write_if

// this interface provides a `write' method

// ------

template <class T>

class sc_write_if

: virtual public sc_interface

{

public:

// interface methods

virtual void write( const T& ) = 0;

};

// -----

```

```

// An example read/write interface: sc_read_write_if

// -----

template <class T>

class sc_read_write_if

: public sc_read_if<T>,

public sc_write_if<T>

{};

```

The read interface provides a read() method. The write interface provides a write() method. The read/write interface is derived from the read interface and the write interface. This allows, for example, hooking up a port with a read interface to a channel with a read/write interface, but not vice versa.

## 7.2 INTERFACE BASE CLASS

All interfaces are (directly or indirectly) derived from base class sc\_interface. This class defines a single method, register\_port(), which can be used by channels to do static design rule checking when binding ports to channels (see Section 8.2 and Section 9.3). The arguments to this method are (i) a reference to the port, and (ii) the type name of the interface that the port expects. The default behavior of this method is to do nothing. The implementation of the sc\_interface base class is depicted below (without details).

Figure 7-1: Pseudo code implementation of the interface base class.

```

class sc_interface

{

public:

// register a port with this interface; the default is NOP

virtual void register_port( sc_port_base&, const char* ) {}

// virtual destructor; the default is NOP

virtual ~sc_interface() {}

};

```

#### 7.3 LAYERED COMMUNICATION EXAMPLE

The concept of interfaces is very useful when we want to model layered communication. At present, this kind of communication is implemented, e.g., in the On Chip Bus (OCB) defined by VSIA. In such a communication model, there are several layers of abstraction. For instance, in the OCB backbone there are three levels: transaction, packet, and cell. Using interfaces, we can define three types as shown in Example 7-2. With this approach, we can define in an optimum way the information that must be considered at each level of abstraction. For instance, the information carried by "EOP<sup>5</sup>" is meaningful at packet level, but is not visible at transaction level. Hence, the user cannot specify this information when he is using the OCB\_trans\_if interface.

<sup>&</sup>lt;sup>5</sup> Denotes the end of the packet that has been transmitted.

```

// pseudo code; some parts are not shown

// -----

// INTERFACE : OCB_cell_if

// ------

template <class T>

class OCB_cell_if

: virtual public sc_interface

{

public:

// interface methods

. . .

virtual void set_eom( bool ) = 0;

virtual bool get_eom() = 0;

virtual void set_eop( bool ) = 0;

virtual bool get_eop() = 0;

};

// -----

// INTERFACE : OCB_packet_if

// -----

template <class T>

class OCB_packet_if

: public OCB_cell_if

{

public:

// interface methods

. . .

};

// ------

// INTERFACE : OCB_trans_if

// -----

template <class T>

class OCB_trans_if

: public OCB_packet_if

{

public:

// interface methods

. . .

virtual void set_eom( bool ) = 0;

virtual bool get_eom() = 0;

private:

// not to be defined

virtual void set_eop( bool );

virtual bool get_eop();

```

```

};

```

Looking at the implementation, all necessary methods are defined pure virtual inside the base class, OCB\_cell\_if. These methods are accessible both by OCB\_packet\_if and OCB\_trans\_if. Since some of the methods are meaningless at certain levels of abstraction, it is necessary to declare them private. For instance, the methods get\_eop() and send\_eop() are declared private in OCB\_trans\_if.

The layered approach, modeled in SystemC by using interfaces, allows also interconnecting a module at different levels of abstraction. In this way, we can attach either modules that need a very close control around the clock (i.e., at cell level), or modules that work at transaction level. Hence, the concept of interfaces provides all the necessary freedom to the user to model its intellectual property (IP) at different levels of abstraction.

# 8. PORTS

A port is an object through which a module, and hence its processes, can access a channel's interface. But modules can also access a channel's interface directly.

In SystemC 1.0, we have three basic port types: sc\_in<T>, sc\_out<T>, and sc\_inout<T>. They are all derived from the base class sc\_port. Each of these port types provides a set of interface methods, such as read() and write(). What these methods basically do is to call the corresponding interface method of the attached channel.

With other channel types, this simple scheme has to be extended, because the interfaces assumed by sc\_in<T>, sc\_out<T>, and sc\_inout<T>, are not sufficient for all channel types. Some channel types may require additional or altogether different interface methods. In general, different channels implement different interfaces. Hence, we need different types of ports in order to access these interfaces. Different interfaces can be created by refining predefined interface types, or by inheriting directly from sc\_interface. See Chapter 7 for details. Specialized ports can be created by refining port base class sc\_port or one of the predefined port types.

It is advisable to separate function and communication as much as possible in order to increase the reusability of components. Therefore, a good design style is to always select the "minimal" port type<sup>6</sup> that offers the required interface methods. Selecting the "minimal" port type translates directly into selecting the "minimal" interface type for a port. Using highly specialized ports and interfaces will limit the number of different channel types that a module can be connected to.

Of course, this separation is not always feasible. The more tightly coupled functionality and communication are, the more likely it is that specialized port types are required. Cases in which the use of specialized ports is advisable or mandatory are those where the access methods of the basic port classes are not sufficient. A few examples are:

- Addresses are used in addition to data, e.g., bus interface.

- One needs additional information on the channel's status, e.g., the number of samples available in a FIFO/LIFO.

- One needs higher forms of sensitivity such as wait\_for\_request() (see Section 9.2).

The concept of interfaces, ports, and channels bears strong similarity to the notion of *interfaces* and *channels* used in SpecC. In fact, a port type assumes a certain interface. A channel cannot be connected to a port if it doesn't implement the port's interface.

<sup>&</sup>lt;sup>6</sup> A "minimal" port type is a port type that requires the most general possible interface.

The question arises whether port objects are needed at all – one could argue that it would be sufficient to only have the notion of interfaces being implemented by channels. Basically, port objects serve a dual purpose. Firstly, they allow for the implementation and enforcement of (static) design rule checks. Secondly, they provide objects that can be attached attributes such as names or priorities.

## 8.1 <u>ATTACHING MULTIPLE INTERFACES</u>

A SystemC 1.0 port can be connected to one and only one channel/interface. SystemC 2.0 allows for connecting a port to multiple identical interfaces. This port behaves much the same as the SystemC 1.0 port, except that more than one interface/channel can be connected to it, and the subscript operator must be used to access an interface (but only if this interface is not the first).

Consider the following example, where multiple memory modules (channels) are attached to a bus module (channel).

Example 8-1: Attaching multiple memories to a bus using one port.

```

// pseudo code; some parts are not shown

// ------

// INTERFACE : simple_bus_if

// ------

class simple_bus_if

: virtual public sc_interface

{

public:

// methods return false if address out of range

virtual bool read_data( unsigned address, int& data ) = 0;

virtual bool write_data( unsigned address, int data ) = 0;

};

// ------

// INTERFACE : simple_mem_if

// ------

class simple_mem_if

: public simple_bus_if

{

public:

// methods to determine address range

virtual unsigned start_address() const = 0;

virtual unsigned end_address() const = 0;

};

// ------

// CHANNEL : simple_mem

// -----

class simple_mem

: public sc_module,

```

```

public simple_mem_if

{

public:

. . .

// interface methods

virtual bool read_data( unsigned address, int& data );

virtual bool write_data( unsigned address, int data );

virtual unsigned start_address() const;

virtual unsigned end_address() const;

• • •

};

// ------

// CHANNEL : simple_bus

// ------

class simple_bus

: public sc_module,

public simple_bus_if

{

public:

// a port to connect memories to (maximum 10 in this case)

sc_port<simple_mem_if,10> mem_port;

// interface methods

virtual bool read_data( unsigned address, int& data )

{

// inefficient, but illustrates the use model

for( int i = 0; i < mem_port.size(); i ++ )</pre>

if( ( address >= mem_port[i]->start_address() ) &&

( address <= mem_port[i]->end_address() ) )

return mem_port[i]->read_data( address, data );

return false;

}

virtual bool write_data( unsigned address, int data );

. . .

};

```

The clear advantage in the above example is that multiple memories can be attached to the bus, without having to instantiate a port for each memory. Hence, we don't have to change the bus code when we use it in designs where the number of memories is not known up front, or where the number of memories can differ.

#### 8.2 PORT BASE CLASS

A pseudo-code definition of the port base class  $sc_port < IF$ , N> is given below. Note that this port type is a template class that is parameterized over an interface type (IF) and the maximum number of interfaces that can be connected to it (N). The default value for N is one.

Figure 8-1: Pseudo code definition of the port base class.

```

// ------

// The port base class: sc_port

// ------

template <class IF, unsigned N = 1>

class sc_port

: public sc_port_guts<IF>

{

public:

// default constructor

sc_port();

// bind an interface to this port

void operator () ( IF& interface );

// bind a (parent module's) port to this port

void operator () ( sc_port_guts<IF>& port );

// access to FIRST interface

// allow to call methods provided by the first interface

IF* operator -> ();

const IF* operator -> () const;

// access to ALL interfaces

// number of connected interfaces

unsigned size() const;

// allow to call methods provided by the specified interface

IF* operator [] ( unsigned index );

const IF* operator [] ( unsigned index ) const;

... // rest not shown

protected:

unsigned

_num_interfaces;

vector<IF*> __interface_vec; // all interfaces

vector<sc_port_guts<IF>*> _parent_vec; // parent ports

vector<sc_port_guts<IF>*> _child_vec;

// child ports

// the first interface this port is connected to

// (maintain extra pointer for more efficient access)

IF* _interface;

... // rest not shown

};

```

Class sc\_port\_guts<IF> is derived from class sc\_port\_base.

A port of a module can be connected to

- zero or more interfaces at the same level of hierarchy,

- zero or more ports of its parent module,

- zero or more ports of its child modules.

Because of this, an sc\_port keeps track of all interfaces, parent ports, and child ports it is connected to. When a port is connected to a port of its parent module, the port stores the parent port, and then it will register itself with the parent port. This enables the parent port to store the registered port as a child port. When a port is connected to an interface, the port will pass the interface down to its child ports, such that during simulation these ports can access the interface directly. This is a recursive process. After elaboration (i.e. just before the simulation starts), each port must check that it doesn't have parent ports that are not connected to any interface.

In the most common case, where the maximum number of interfaces is one, an sc\_port is connected to one interface only, and it will have at most one parent port. The port can still have zero or more child ports.

In any case, it will be very difficult for static design rule checks to determine the actual number of drivers of a channel. Dynamic design rule checks are needed to deal with this problem. Static and dynamic design rule checking are explained in Section 9.3.

The port base class sc\_port allows accessing a channel's interface methods by using operator -> or operator []. With input an input port of a process, and read() an interface method of the attached channel, one can write, for example:

a = input->read(); // read from the first (or only) interface of input b = input[2]->read(); // read from the third interface of input

Specialized ports can be defined, which provide shortcuts to some of the channel's interface methods. In the next section, some examples are given.

## 8.3 **PORT EXAMPLES**

Below, the implementations of three example ports are given. These ports use the example interfaces described in Section 7.1.

Example 8-2: A read, write, and read/write port.

```

// ------

// An example read port: sc_read_port

// -----

template <class T>

class sc_read_port

: public sc_port<sc_read_if<T> >

{

public:

// a convenience function for reading a value

operator const T&() const

{ return (*this)->read(); }

};

// ------

// An example write port: sc_write_port

// ------

template <class T>

class sc_write_port

: public sc_port<sc_write_if<T> >

{

public:

// a convenience function for writing a value

sc_write_port<T>& operator = ( const T& elem )

{ (*this)->write( elem ); return *this; }

};

// -----

// An example read/write port: sc_read_write_port

// -----

template <class T>

class sc_read_write_port

: public sc_port<sc_read_write_if<T> >

{

public:

// a convenience function for reading a value

operator const T&() const

{ return (*this)->read(); }

// a convenience function for writing a value

sc_read_write_port<T>& operator = ( const T& elem )

{ (*this)->write( elem ); return *this; }

};

```

With the ports in Example 8-2, one could write channel access as follows.

```

SC_MODULE( my_module )

{

sc_read_port<int>

in;

sc write port<int>

out;

sc_read_write_port<int> inout;

void main_action() {

int a;

a = in;

a = in->read();

out = a_i

out->write( a );

a = inout;

a = inout->read();

inout = a;

inout->write( a );

. . .

}

. . .

};

```

#### 8.4 PORT-LESS CHANNEL ACCESS

Ports give modules and their processes access to channel interfaces. In order to facilitate IP reuse and exchange and to enable tool support, we define the following mandatory design style.

• For inter-module level communication, ports must be used to connect modules to channels.

Here, ports are handles for communicating with the "outside world", i.e., channels outside the module. These handles allow for design rule checking, attaching communication attributes, such as priorities, and from a software point-of-view they can be seen as a kind of smart pointers.

• For intra-module level communication<sup>7</sup>, direct access to channels is allowed, i.e., without the use of ports.

Although at intra-module level the notion of a port as an object is very helpful in general, one can access a channel's interface in a "port-less" way by directly calling the interface methods. In some cases – such as the mutex channel (see Section 10.5) – this seems to be the most natural way. Consider the following example.

<sup>&</sup>lt;sup>7</sup> Communication between methods of a module. The channels are instantiated within the context of the module.

```

Example 8-3: Port-less access for intra-module level communication.

```

```

// pseudo code

SC_MODULE( mod1 )

{

// port(s)

sc_in<int> in;

sc_out<int> out;

sc_mutex mutex; // channel; used to protect common resource `in'

int f( int );

int g( int );

// process(es)

void thread1()

{

while( true ) {

wait( 10, SC_NS );

// direct access to channel

mutex.lock();

wait( in.value_changed() );

out = f(in);

// direct access to channel

mutex.unlock();

}

}

void thread2()

{

while( true ) {

wait( 10, SC_NS );

// direct access to channel

mutex.lock();

wait( in.value_changed() );

out = g(in);

mutex.unlock();

// direct access to channel

}

}

// constructor

SC_CTOR( mod1 )

{

SC_THREAD( thread1 );

SC_THREAD( thread2 );

}

. . .

};

```

Note that direct access is not restricted to channel interfaces, i.e., other channel methods can also be called directly, e.g. for setting parameters and attributes.

## 9. CHANNELS

A channel implements one or more interfaces, and serves as a container for communication functionality. A channel is not necessarily a point-to-point connection; a channel may be connected to more than two modules. SystemC 2.0 allows users to create their own channel types enabling them, for instance, to develop efficient abstract bus models or to model proprietary communication protocols.

With channels, we make a distinction between so-called *primitive channels* and *hierarchical channels*. Primitive channels do not exhibit any visible structure, do not contain processes, and cannot (directly) access other primitive channels. Hierarchical channels, on the other hand, are modules, which means they can have structure, they can contain other modules and processes, and they can (directly) access other channels.

In this chapter, the common characteristics of primitive and hierarchical channels are described. The following two chapters focus on primitive channels and hierarchical channels, respectively.

The following example shows how ports are connected to a channel.

#### Example 9-1: Connecting ports to a channel.

// create a channel called `fifo' with a buffer size of 10 sc\_fifo<int> fifo( 10 ); // connect port `out' from module `mod\_a' to the channel; // this will register port `out' with channel `fifo' mod\_a.out( fifo ); // connect port `in' from module `mod\_b' to the channel; // this will register port `in' with channel `fifo' mod\_b.in( fifo ); // channel `fifo' cannot have more than two ports mod\_c.in( fifo ); // Error

#### 9.1 CHANNEL REFINEMENT

Refinement of channels is facilitated through the use of inheritance. All primitive channel types (directly or indirectly) inherit from base class sc\_prim\_channel; its API will be presented in Chapter 10. All hierarchical channel types (directly or indirectly) inherit from base class sc\_module. Inheritance can be used to put common functionality into base classes and specialized functionality in derived classes. It can also be applied to refine or modify a communication protocol.

Different channel types may have different interfaces. While sc\_signal<T> has a read() interface method without any function arguments, this will not be the case for a bus-like channel were we can expect an address to be required. For that reason, channels inherit (and implement) also one or more interfaces. Thus, inheritance is used to both modify the behavior of existing access methods as well as to add new, more specialized interfaces.

## 9.2 <u>SENSITIVITY</u>

Processes can be made sensitive to events on channels, which can be different for different channels. For example, if a process is sensitive to an sc\_signal<T>, then it will be triggered if the value of the signal changes. One can envision a different channel type sc\_buffer<T> that behaves just like sc\_signal<T>, with the exception that a process gets triggered whenever a value is assigned to that channel – even if the projected value is identical to the current one.

Additionally, channel types like sc\_fifo<T> can internally use events to implement blocking interface methods. Dynamic sensitivity also allows for creating more specific forms of sensitivity. To illustrate this, think of a channel type that supports addresses (e.g. generic\_bus<Addr,Data,Arbiter>). This channel type may offer interface methods such as:

void write( Data data, Addr address ); void read( Data& data, Addr address ); void wait\_for\_request( Addr start\_address, Addr end\_address );

Using wait\_for\_request(), a process might tell the channel to trigger it when there is a (read or write) request in the address range from start\_address to end\_address.

It is important to note that dynamic sensitivity allows for implementing such types of channels *without* having to change the underlying simulation engine. All the functionality that is required goes into the derived channel class.

#### 9.3 DESIGN RULES

Different channel types bring along different *design rules* (cf. Table 9-1). For instance, a FIFO channel may require that at most two ports are connected to it, one of which must be an input port, the other one an output port. One must not attach a bi-directional port to a FIFO.<sup>8</sup> Other channel types can have different design rules. A channel of type sc\_signal<T> for instance has a "not more than one driver" rule (it is a 1-to-many connection).

| sc_signal <t></t>    | • | No more than one driver, i.e., at most one output (sc_out <t>) or<br/>bi-directional port (sc_inout<t>) connected.<br/>Arbitrary number of input ports (sc_in<t>) can be connected.</t></t></t> |

|----------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sc_signal_rv <n></n> | • | Arbitrary number of input, output, and bi-directional ports can be connected.                                                                                                                   |

| Table 9-1: Design | rules for some | channel types. |

|-------------------|----------------|----------------|

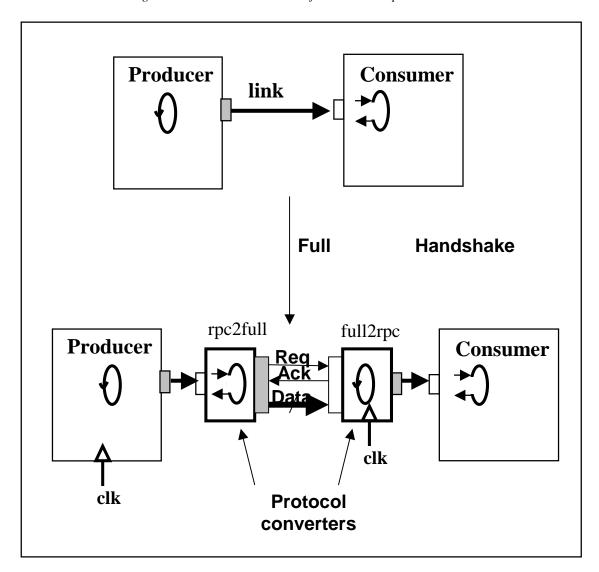

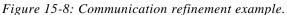

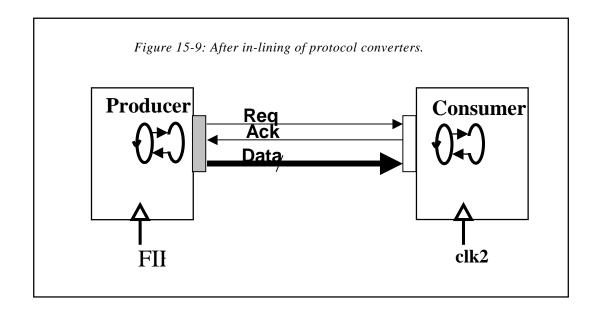

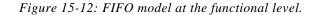

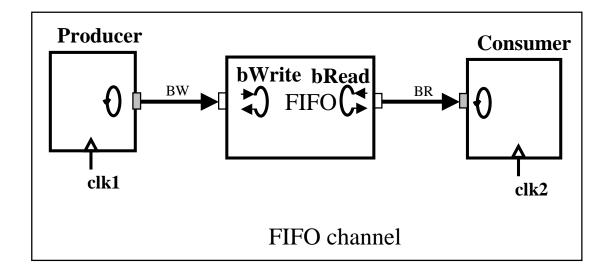

|-------------------|----------------|----------------|