© 2007 -- Don Bouldin

# **COURSE OUTLINE**

- Overview of FPGAs and ASICs

- Using Synthesis

- HDL Examples

- Simulation and Testing

- Physical Place and Route

- Testing ASICs

- Component Reuse

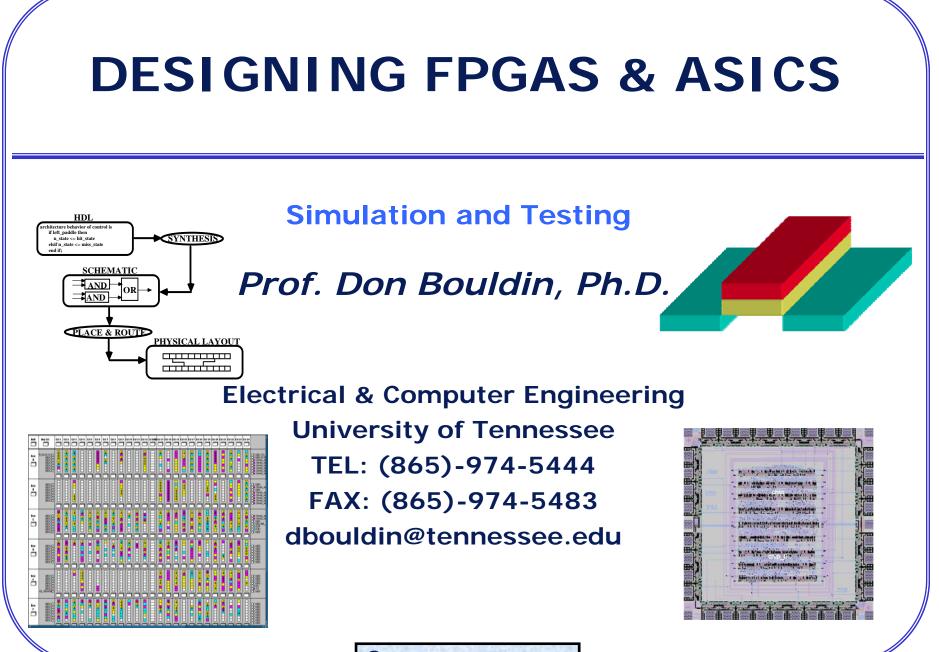

### SEMI-CUSTOM DESIGN FLOW OF DIGITAL FPGAS/ASICS

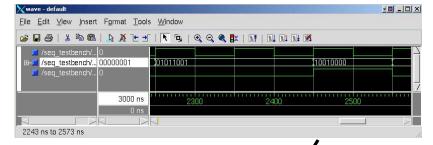

| PRE-SYNTHESIS SIMU<br>TECHNOLOGY-INDEP                                                               |      |

|------------------------------------------------------------------------------------------------------|------|

| Note the "zero" delay at 2450                                                                        | ns:  |

|                                                                                                      |      |

| 🗙 wave - default                                                                                     |      |

| <u>File E</u> dit <u>V</u> iew Insert Format <u>T</u> ools <u>W</u> indow                            |      |

| 😹 🖬 🚳   👗 🖻 🛍   📐 Ă Ҽ 🛨   📉 🖳   🍳 🍳 🌒   👫   🖽 E                                                      |      |

| ✓ /seq_testbench/       0         □ /seq_testbench/       00000001         ○ /seq_testbench/       0 |      |

| 3000 ns 2300 2400                                                                                    | 2500 |

|                                                                                                      |      |

### **POST-LAYOUT SIMULATION INCLUDES COMPONENT AND WIRING DELAYS** Note the "14ns" delay at 2464 ns: 🔀 wave - default - 🛛 \_ 🗆 × File Edit View Insert Format Tools Window 🚅 🖬 🚳 | 👗 🛍 | 📐 👗 🕑 - 🖌 💽 | 🍳 🍳 🕵 🕼 | 🖬 | 🔜 🖽 🕷 📁 /seg testbench alt/clock - Joeg testbench alt/monitor 10010000 01011001 10010000 📁 /seg testbench alt/reset 2470 3000 ns 2460 2450 2490 ns 2440 ns to 2480 ns

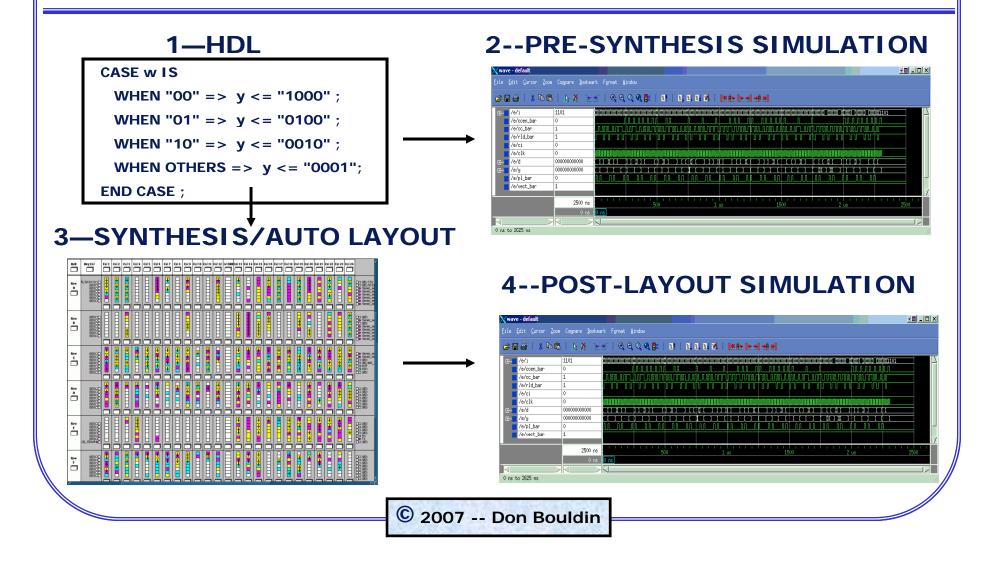

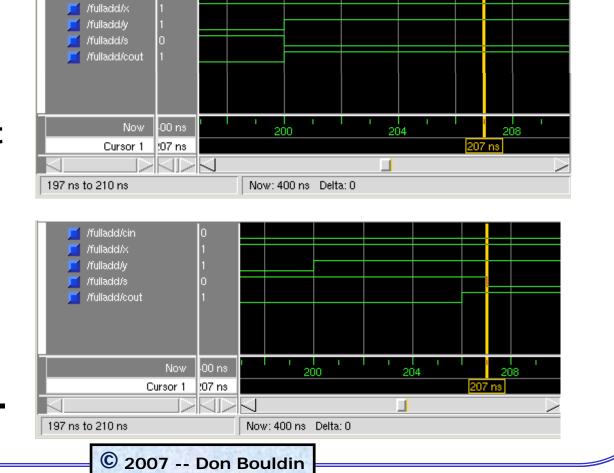

### Simulation of fulladd.vhd

/fulladd/cin

- Presynthesis: outputs change instantly at 200 ns.

- Postlayout: outputs change at 206-207 ns.

# RECOMMENDED METHOD FOR LEARNING VHDL

- Copy a known working file to use as a template with reserved words and syntax. Simulate it.

- Modify the VHDL source code to perform your intended operations and then simulate the revised code.

- Be wary of examples in textbooks and on the internet since not all VHDL code is synthesizable with a particular synthesis tool and software environment.

- Avoid use of the "FOR" statement which is confusing.

- Avoid using technology-dependent statements like "WAIT until 14 ns". Instead, use "WAIT\_CLOCK(16)".

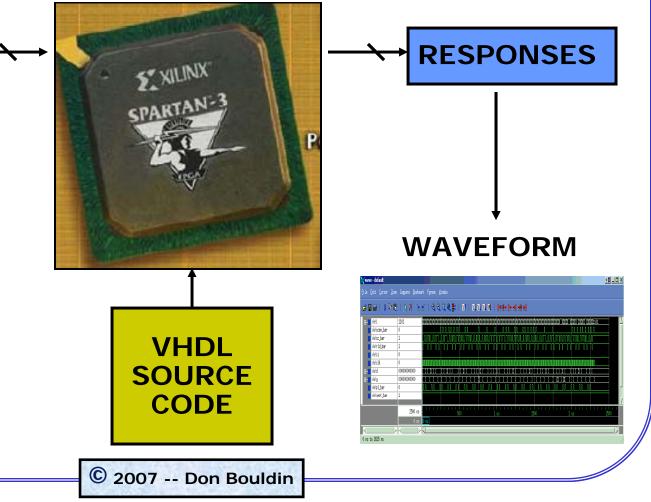

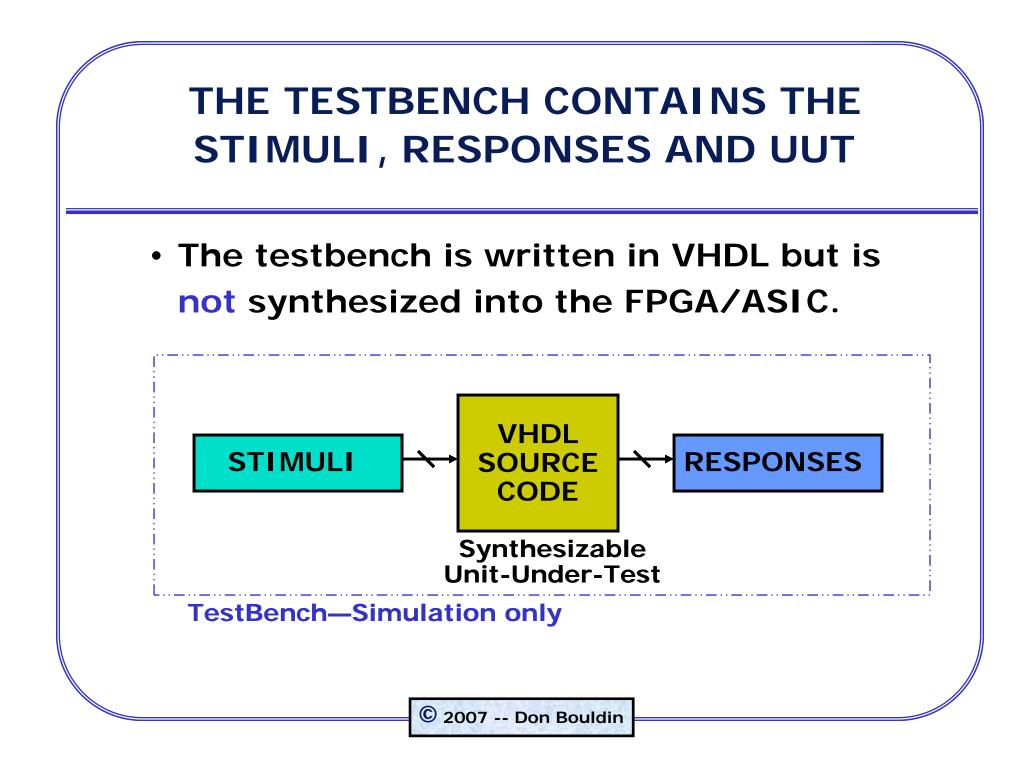

### SIMULATION SHOWS THE RESPONSES OF THE VHDL TO STIMULI

Functional stimuli are developed by the designer to mimic the system environment.

### EXPECTED RESPONSES ARE COMPARED TO ACTUAL ONES

"Failure" stops simulation while "warning" does not.

"Note" is used to document a correct response.

wait\_clock(16);

IF (left\_seg = X"6")

-- check second state of 7-segment display

THEN

ASSERT false

REPORT "Output signals set correctly (7-segment second state)"

SEVERITY note;

ELSE ASSERT false REPORT "Output not set correctly (7-segment second state)" SEVERITY warning;

END IF;

### ALL VHDL SOURCE LINES SHOULD BE TESTED

### The simulator can produce coverage reports.

| Pathname             | Lines     | Hits    | %         | Coverage | 12   |

|----------------------|-----------|---------|-----------|----------|------|

| leltech/bin//sunos5/ | 228       | 0       | 0.0       |          |      |

| leltech/bin//sunos5/ |           | ŏ       | ŏ:ŏl      |          |      |

| eltech/bin//sunos5/  | 50        | ŏ       | ŏ.ŏ       |          |      |

| y/bist_mod.vhd       | 126       | 104     | 82.5      |          |      |

| y/debounce.vhd       | 6         | 6       | 100.0     |          |      |

| y/mainlogic.vhd      | 198       | 17Ŏ     | 85.9      |          |      |

| y/out_7seg.vhd       | 71        | 43      | 60.6      |          |      |

| y/out_leds.vhd       | 42        | 30      | 71.4      |          |      |

| y/prng.vhd           | 24        | 22      | 91.7      |          |      |

| y/registers.vhd      | 13        | 13      | 100.0     |          |      |

| y/translate_pb.vhd   | 12        | 12      | 100.0     |          |      |

| ench/main_test.vhd   | 87        | 80      | 92.0      |          |      |

|                      |           |         |           |          |      |

|                      | 1359      | 480     | 35.3      |          |      |

| Lines with no covera | ae        |         |           |          |      |

|                      |           |         |           |          | 12A  |

| Select a source file | to displa | y lines | missing o | coverage |      |

|                      |           |         |           |          |      |

|                      |           |         |           |          |      |

|                      |           |         |           |          |      |

|                      |           |         |           |          | _    |

|                      |           |         |           |          |      |

|                      |           |         |           |          | 10.8 |

| Misses Excluded      |           |         |           |          | je.z |

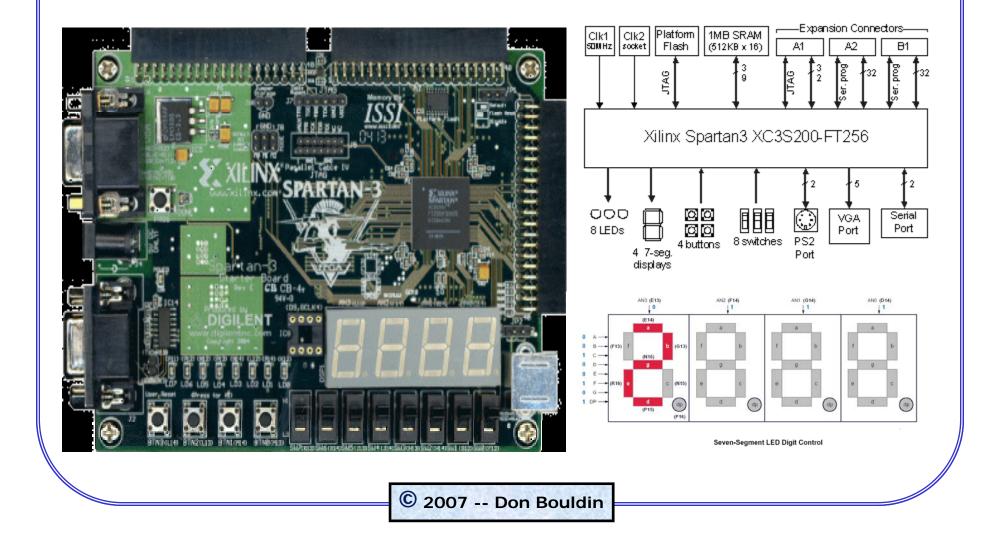

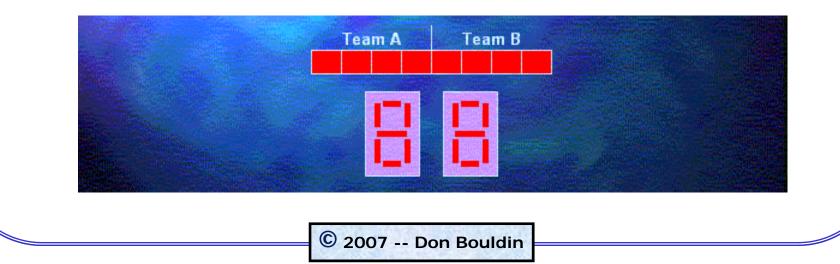

### FINAL VERIFICATION IS PERFORMED USING A PROTYPING BOARD

# XILINX TOOLS ARE FREE BUT TARGET ONLY XILINX PARTS

### Anyone can download Xilinx WebPACK tools for free from www.xilinx.com

### Free ISE WebPACK 7.1i

> Add to Cart

The free ISE WebPACK™ 7.1i is the most complete, easy-to-use software solution to complete a Xilinx CPLD or medium-density FPGA design

ISE WebPACK is the ideal downloadable desktop solution offering free software modules from ABEL and HDL synthesis to device fitting and JTAG programming. ISE WebPACK is a subset of our award winning ISE Foundation™ design tools providing instant access to the ISE tools at no cost. Xilinx has created a solution that allows convenient productivity by providing a design solution that is always up to date with error-free downloading and single file installation.

WebPACK includes a free version of ModelSim that works only for Xilinx parts but you must register at www.mentor.com

### ModelSim<sup>™</sup> Xilinx Edition-III

#### The Model Sim-III Family of Products

# **IMPLEMENTING A PROJECT**

- Determine I/O Requirements

- Partition into 5-9 submodules and test individually before combining.

- Use/Enhance Built-In Self-Test

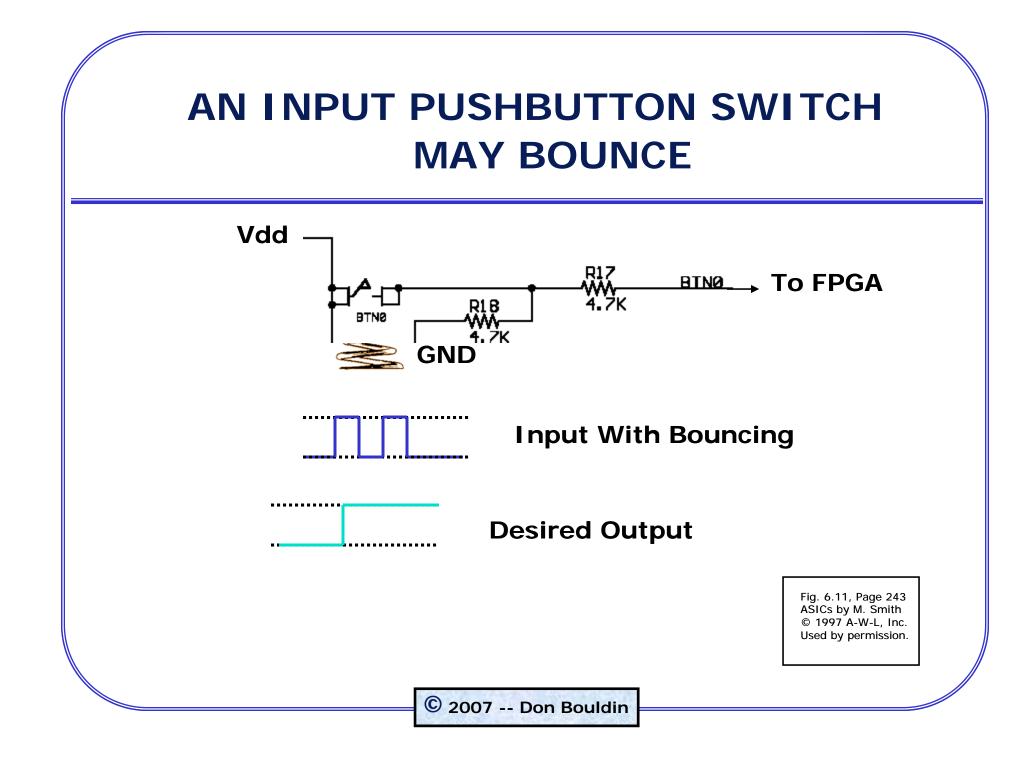

- Debounce Pushbutton Switches

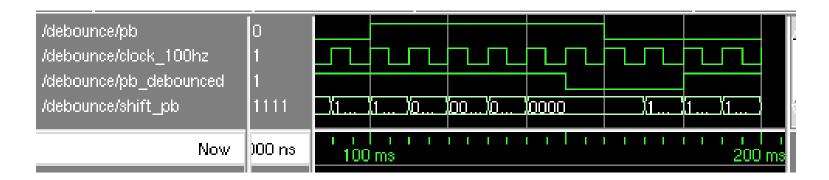

- Filter an Input to Produce a Single Pulse

- Use hierarchy with Submodule Components

- Synchronize Externally Clocked Inputs

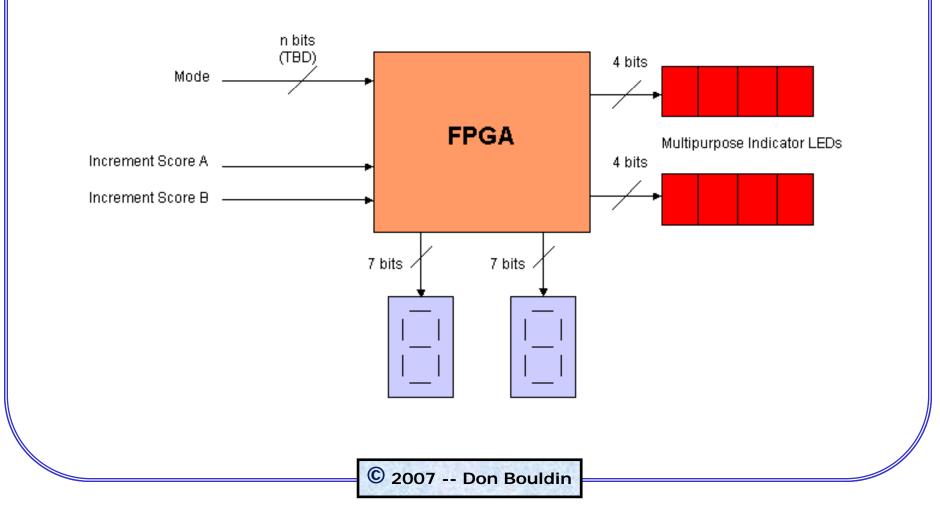

## DETERMINE SYSTEM I/O REQUIREMENTS

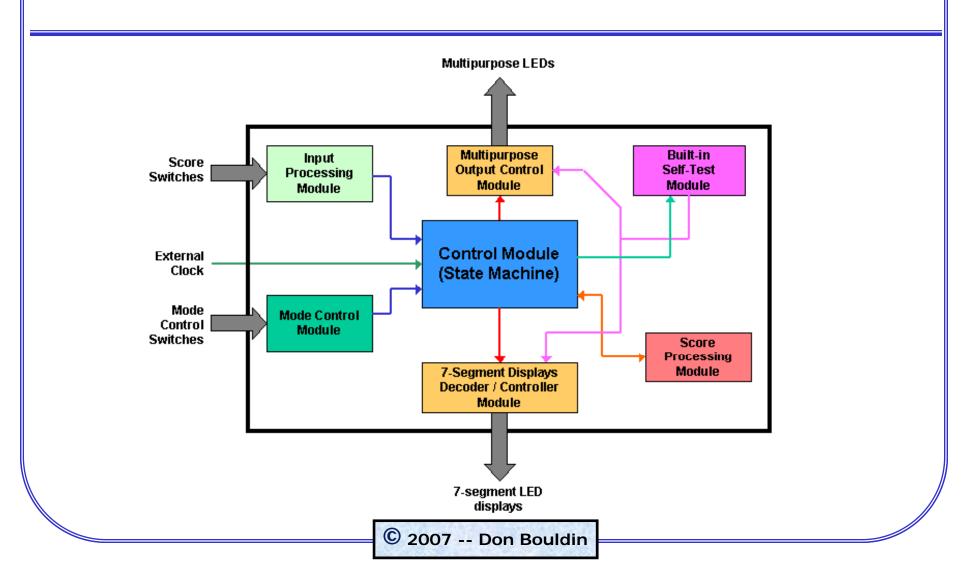

## DECOMPOSE EACH LEVEL INTO 7+/-2 SUBMODULES

# SIMULATE EACH SUBMODULE AND THEN INTEGRATE THEM

### Submodule#1

# Wave - default Image: Second sec

### Submodule#2

### Composite of #1 and #2

| _      | /e/i        | 1101        |           | <u> </u> |       |          |     |       |     |      |        |        |     |                                                |      |       |        |       | www  | www   |                                              |      | W.W |       | suviuv | 1101     |      |  |

|--------|-------------|-------------|-----------|----------|-------|----------|-----|-------|-----|------|--------|--------|-----|------------------------------------------------|------|-------|--------|-------|------|-------|----------------------------------------------|------|-----|-------|--------|----------|------|--|

|        | /e/ccen_bar | 0           | anonnonno | meme     |       |          |     |       |     |      |        |        | 1   | 11                                             | 1    |       |        |       | mmu  |       |                                              |      |     |       | 11     |          |      |  |

|        | /e/cc_bar   | 1           |           |          | ÚFÚ   |          |     |       | ML  | nnin | nnń    | лпг    | um  | nhn                                            | NL N | UNI   |        |       | Infi | лпл   | เกก                                          | UUT  | UUU | ווורו | Liún   |          |      |  |

|        | /e/rld_bar  | 1           |           |          |       |          |     |       |     |      |        |        |     | T                                              | Π    |       |        |       |      |       |                                              |      |     | П     |        |          |      |  |

|        | /e/ci       | 0           |           |          |       |          |     |       |     |      |        |        |     |                                                |      |       |        |       | _    |       |                                              |      |     |       | _      |          |      |  |

|        | /e/clk      | 0           | IUUUU     | ШПШП     | ΠШΠШΙ | ШТШТ     |     | TUTUT | ШТШ |      | IIIIII | TUITUT |     | ШIШ.                                           | TUTU | ТШПШТ | TWITWI | UTUT. |      | IUTUT | ШПШ                                          | ПШП  | ШШТ | ШТШТ  | TIMI   | I        |      |  |

| ±-     | /e/d        | 00000000000 |           | 11       |       |          | μĽ  |       | 1 X | L    |        | U      | ш   | <u>, i i i i i i i i i i i i i i i i i i i</u> |      | LIII  | Ĺ      |       | ᆜ    |       | <u>.                                    </u> | Щ    | LI  |       | φ      |          |      |  |

| ±-     | /e/y        | 00000000000 |           |          | ĻĻ    |          | μē  |       | 1   | ĻĻ   |        |        |     | 1                                              | Ц    | Ľ     | ĻĻ     |       | 9    |       | Ш.                                           | Щ    | 1_  | Ļ     | 1      | <u> </u> |      |  |

|        | /e/pl_bar   | 0           |           |          |       |          | μı  |       | Щ   |      |        |        |     |                                                |      |       |        |       | Ц    |       |                                              |      |     |       |        |          |      |  |

|        | /e/vect_bar | 1           |           |          |       |          |     |       |     |      |        |        |     |                                                |      |       |        |       |      |       |                                              |      |     |       |        |          |      |  |

|        |             | 2500 ns     | 1.1       | 1 1      | 1.1   | ا ا<br>ج | 100 | 1 1 1 |     |      | 1      | 1      | 1 1 |                                                | 1 1  | 1     | 500    | 1 1   | ı İ  | 1 1   | 1                                            | 2 us | 1 1 | 1 1   |        | 1 1 1    | 2500 |  |

|        |             | 0 ns        | 0 ns      |          |       |          |     |       |     |      | -      |        |     |                                                |      |       |        |       |      |       |                                              |      |     |       |        |          |      |  |

|        |             |             |           |          |       |          |     |       |     |      |        |        |     |                                                |      |       |        |       |      |       |                                              |      |     |       |        |          |      |  |

| 0 ne : | to 2625 ns  |             |           |          |       |          |     |       |     |      |        |        |     |                                                |      |       |        |       | _    |       |                                              |      | _   |       |        |          |      |  |

### **BUILT-IN SELF-TEST**

- Downloading hw3a (BIST) ensures the integrity of the connection between the CPU and the Spartan3 prototyping board AND then checks the input switches and the 7-segment displays.

- More thorough checks could be added to ensure the integrity of the board I/O for a specific project.

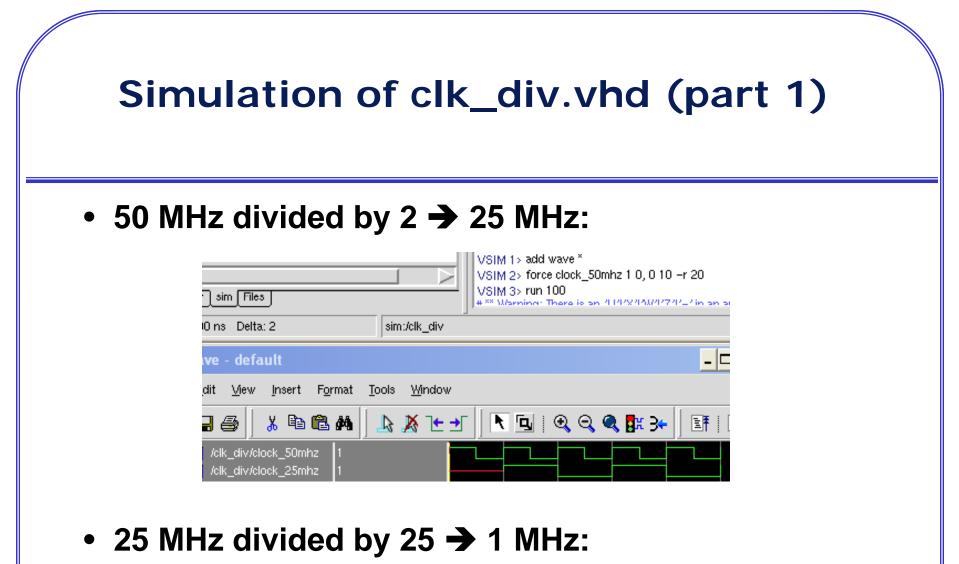

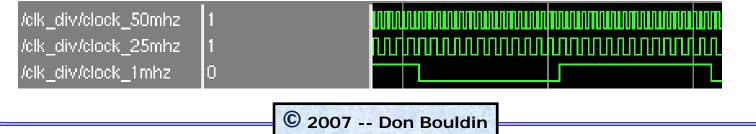

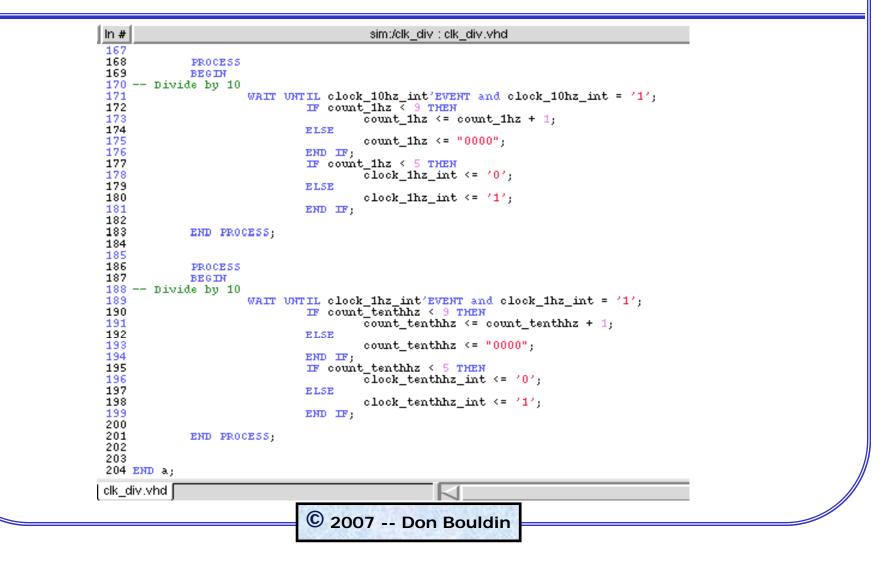

### INTERNAL FREQUENCIES CAN BE DERIVED FROM THE EXTERNAL CLOCK

- A crystal oscillator on the Spartan3 prototyping board produces a 50 MHz clock.

- Counters can be used to divide down a frequency into a slower synchronized one:

| <u>Divide By</u> | <b>Frequency</b> | <b>Duration</b> |

|------------------|------------------|-----------------|

| 1                | clock_50MHz      | 20 ns           |

| 2                | clock_25 MHz     | 40 ns           |

| 25               | clock_1MHz       | 1000 ns = 1us   |

| 10               | clock_100KHz     | 10 us           |

| 10               | clock_10KHz      | 100 us          |

| 10               | clock_1KHz       | 1000 us = 1 ms  |

| 10               | clock_100Hz      | 10 ms           |

| 10               | clock_10Hz       | 100 ms          |

| 10               | clock_1Hz        | 1000 ms = 1 s   |

| 10               | clock_tenthHz    | 10 s            |

© 2007 -- Don Bouldin

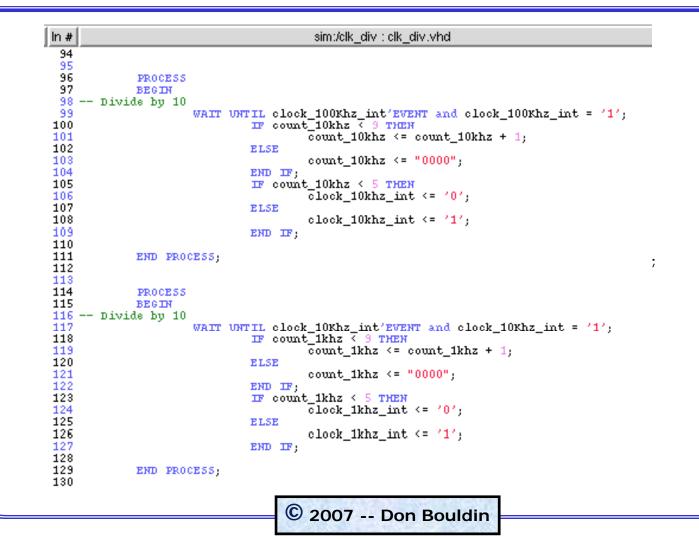

• 10 KHz divided by 10 → 1 KHz:

### clk\_div.vhd (part 1)

|     |   | al a |

|-----|---|------|

| ln. | # | L    |

|     |   |      |

sim:/clk\_div : clk\_div.vhd

```

1 -- original from Jim Hamblen at Georgia Tech

2 -- revised on 9/15/05 by Don Bouldin for 50MHz and TenthHz

3 LIBRARY IEEE:

4 USE IEEE.STD_LOGIC_1164.all;

5 USE IEEE.STD LOGIC ARITH.all:

6 USE IEEE.STD_LOGIC_UNSIGNED.all;

8 ENTITY clk_div IS

9

10

PORT

11

12

clock_50Mhz

: IN

STD_LOGIC;

13

14

15

clock 25Mhz

: OUT

STD LOGIC:

clock 1MHz

: OUT

STD_LOGIC;

clock 100KHz

: OUT

STD LOGIC:

16

clock_10KHz

: 0UT

STD LOGIC:

17

clock 1KHz

: OUT

STD LOGIC:

18

clock_100Hz

: OUT

STD LOGIC:

19

clock 10Hz

: OUT

STD LOGIC:

20

clock 1Hz

: OUT

STD LOGIC:

21

clock tenthHz

: OUT

STD_LOGIC);

22

23 END clk_div;

24

25 ARCHITECTURE a OF clk_div IS

26

27

SIGNAL count 25Mhz: STD LOGIC VECTOR(1 DOWNTO 0);

28

SIGNAL

count 1Mhz: STD LOGIC VECTOR(4 DOWNTO 0);

count_100Khz, count_10Khz, count_1Khz: STD_LOGIC_VECTOR(3 DOWNTO 0);

29

SIGNAL

30

count_100hz, count_10hz, count_1hz, count_tenthhz : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL

31

clock_25Mhz_int, clock_1Mhz_int, clock_100Khz_int, clock_10Khz_int, clock_1Khz_int: STD_LOGIC;

SIGNAL

clock 100hz int, clock 10Hz int, clock 1Hz int, clock tenthHz int : STD LOGIC;

32

SIGNAL

33 BEGIN

```

© 2007 -- Don Bouldin

### clk\_div.vhd (part 2)

```

ln #

sim:/clk_div_:clk_div.vhd

33 BEGIN

34

PROCESS.

35.

BEGIN

36 -- Divide by 2

37.

WAIT UNTIL clock 50 Mhz'EVENT and clock 50 Mhz = '1';

38

IF count 25Mhz < 1 THEN

count 25Mhz <= count_25Mhz + 1;

39

40

ELSE

count_25Mhz <= "00";

41

42

END IF:

IF count 25Mhz < 1 THEN

43

44

clock 25Mhz int <= '0';

45

ELSE

46

clock 25Mhz int <= '1';

47

END IF:

48

-- Ripple clocks are used in this code to save prescalar hardware

49

-- Sync all clock prescalar outputs back to master clock signal

50.

51

52

clock_25Mhz <= clock_25Mhz_int;</pre>

clock 1Mhz <= clock 1Mhz int;

53

clock 100Khz <= clock 100Khz int;

54

clock 10Khz <= clock 10Khz int;

55

clock 1Khz <= clock 1Khz int;

56

clock 100hz <= clock 100hz int;

57

clock 10hz <= clock 10hz int:

58

clock_1hz <= clock_1hz_int;

clock tenthhz <= clock tenthhz int;

59

60

END PROCESS:

сн.

© 2007 -- Don Bouldin

```

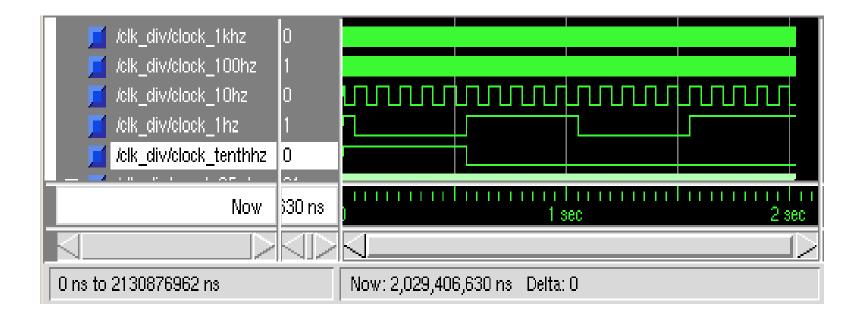

### clk\_div.vhd (part 3)

© 2007 -- Don Bouldin

### clk\_div.vhd (part 4)

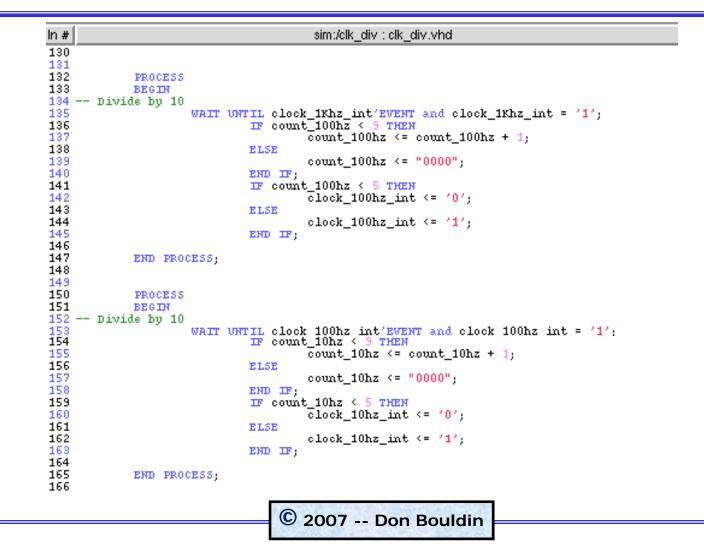

### clk\_div.vhd (part 5)

### clk\_div.vhd (part 6)

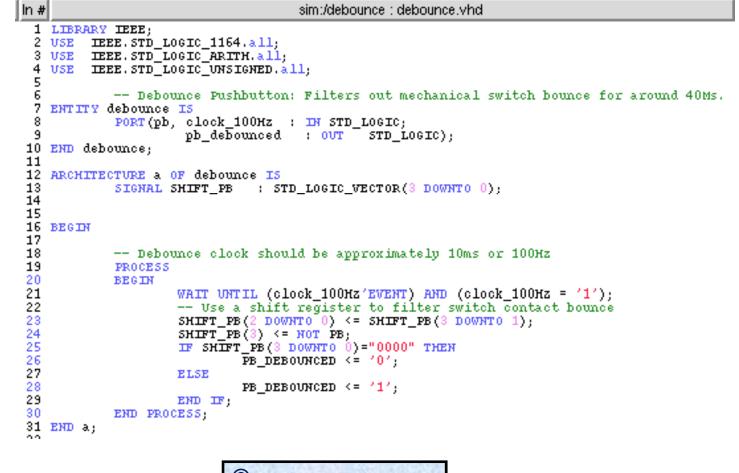

### debounce.vhd

© 2007 -- Don Bouldin

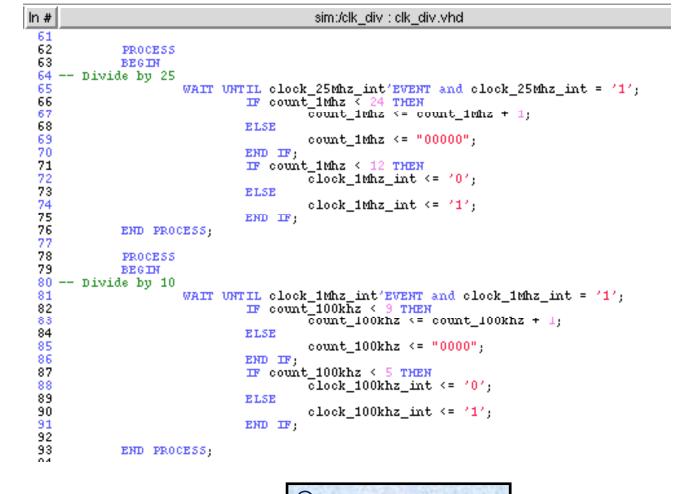

### Simulation of debounce.vhd (part 1)

PB has been 0 (inactive), then is 1 (active) but only for 10 ms (too short to be valid) so PB\_debounced stays 1 (inactive):

| _ 🗆  |

|------|

|      |

|      |

|      |

|      |

| 1101 |

|      |

### Simulation of debounce.vhd (part 2)

This time PB is 1 (active) for 60 ms (which is valid since it is at least 40ms) so PB\_debounced becomes 0 (active):

PB\_debounced has been 0 (active) for 100 ms but only a single 1 ms pulse is produced:

| 🗾 /onepulse/pb_debounced       |                  | 1                              |                 |     |     |            |   |           |

|--------------------------------|------------------|--------------------------------|-----------------|-----|-----|------------|---|-----------|

| 🗾 /onepulse/clock_1mhz         |                  | 1                              |                 |     |     |            |   |           |

| 🗾 /onepulse/pb_single_pulse    |                  | 0                              |                 |     |     |            |   |           |

| 🗾 /onepulse/pb_debounced_delay |                  | 1                              |                 |     |     |            |   | $\succ$   |

| 🗾 /onepulse/power_on           |                  | U                              |                 |     |     |            |   |           |

| No                             | w                | 00 ns                          |                 |     | 200 | IIII<br>MS |   |           |

| $\triangleleft$                | $\triangleright$ | $\triangleleft \triangleright$ | $\triangleleft$ |     |     |            |   | $\exists$ |

| 130 ms to 265 ms               | Nov              | w: 264 n                       | ns Delta        | : 2 |     |            |   |           |

|                                |                  |                                | _               |     |     |            |   |           |

| /onepulse/pb_debounced         | 0                |                                |                 |     |     |            | / |           |

| /onepulse/clock_1mhz           | 1                |                                | цпп             | плп |     |            |   | ப்பு      |

0

/onepulse/pb\_single\_pulse

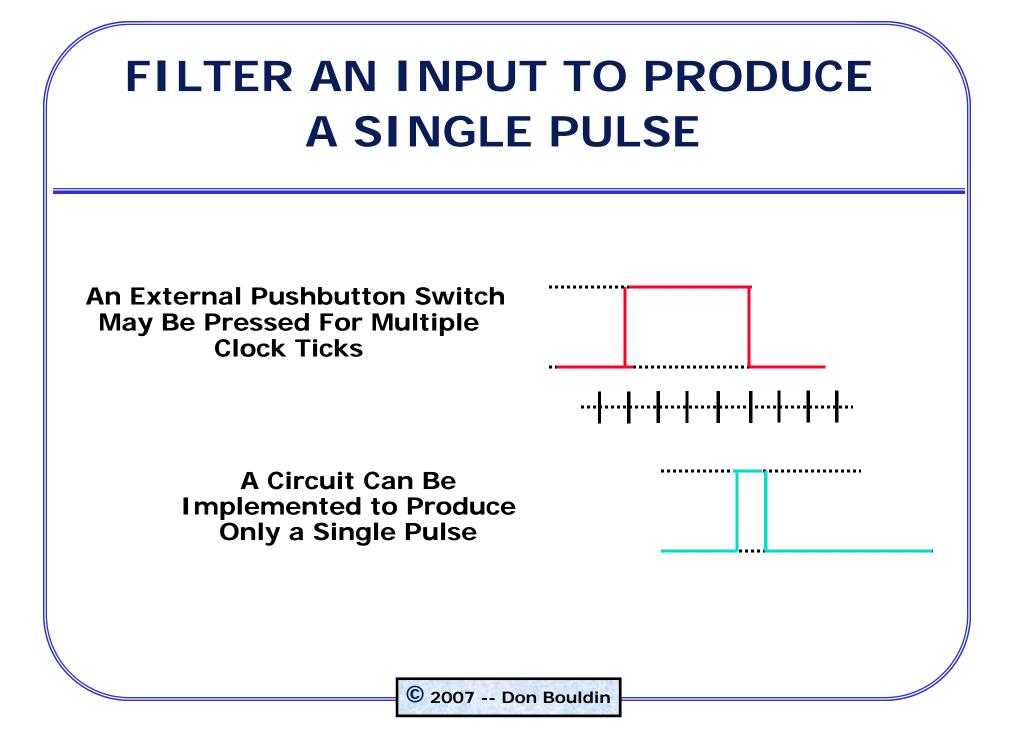

### onepulse.vhd (part 1)

```

sim:/onepulse : onepulse.vhd

ln #

1 LIBRARY IEEE:

2 USE IEEE.STD LOGIC 1164.all;

3 USE IEEE.STD LOGIC ARITH.all;

4 USE IEEE.STD LOGIC UNSIGNED.all;

5

6 -- Single Pulse circuit

-- the output will go high for only one clock cycle

7

8

9 ENTITY onepulse IS

10

11

PORT (PB debounced, clock 1MHz : IN STD LOGIC;

12

PB single pulse : OUT STD LOGIC);

13

14 END onepulse:

15

16

```

### onepulse.vhd (part 2)

```

16

17 ARCHITECTURE a OF onepulse IS

SIGNAL PB debounced delay, Power on : STD LOGIC;

18

19

20 BEGIN

21 PROCESS

22 BEGIN

23

WAIT UNTIL (CLOCK_1MHz'svent) AND (CLOCK_1MHz='1');

-- Power on will be initialized to '0' at power up

24

25

IF Power on='0' THEN

26

-- This code resets the critical signals once at power up

PB single pulse <= '0';

27.

28

PB debounced delay <= '1';

29

<= '1';

Power_on

30

31

ELSE.

32

-- A single clock cycle pulse is produced when the switch is hit

33

-- No matter how long the switch is held down

-- The switch input must already be debounced

34

IF PB_debounced = '1' AND PB_debounced_delay = '0' THEN

35

36

PB single pulse \langle = \frac{1}{1} \rangle;

37

ELSE.

38

PB_single_pulse <= '0';</pre>

39

END IF

40

PB_debounced_delay <= PB_debounced;</pre>

41

42

43

END IF :

44

45 END PROCESS:

46

47 END a;

```

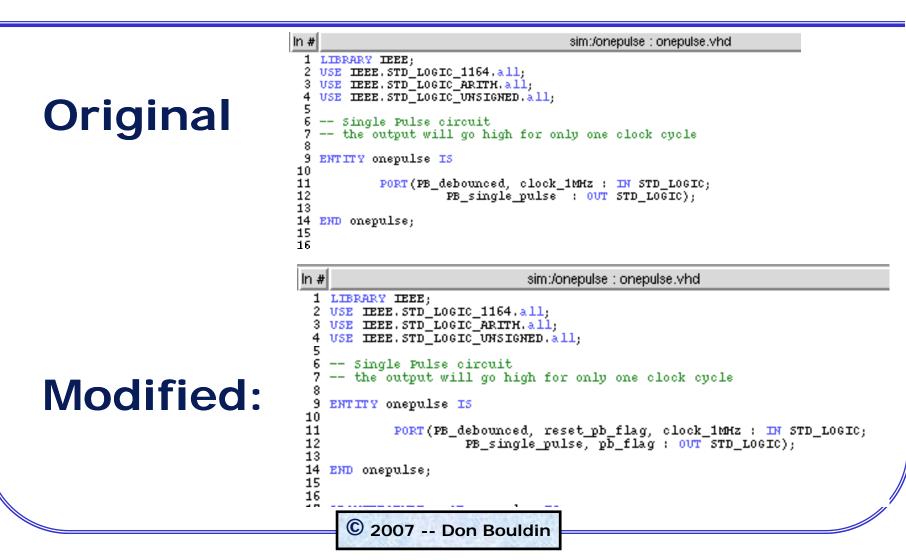

# onepulse.vhd (part 1) (modified)

# onepulse.vhd (part 2) (modified)

```

17 ARCHITECTURE a OF onepulse IS

18

SIGNAL PB_debounced_delay, Power_on : STD_LOGIC;

19

20 BEGIN

21 PROCESS

22

BEGIN

23

WAIT UNTIL (CLOCK_1MHz'event) AND (CLOCK_1MHz='1');

24

-- Power_on will be initialized to '0' at power up

25

IF Power on='0' THEN

26

-- This code resets the critical signals once at power up

27

28

<= 101;</pre>

PB_single_pulse

<= '0';

PB flag

29

PB_debounced_delay <= '1';</pre>

30

<= '1':

Power on

31

32

ELSE

33

-- A single clock cycle pulse is produced when the switch is hit

34

-- No matter how long the switch is held down

35

-- The switch input must already be debounced

36

IF PB_debounced = '1' AND PB_debounced_delay = '0' THEN

37

PB_single_pulse <= '1';

38

pb_flag <= '1';

39

ELSE

PB_single_pulse <= '0';

IF reset_pb_flag = '1' THEN pb_flag <= '0';</pre>

40

41

42

ELSE

43

END IF;

44

END IF:

45

46

PB_debounced_delay <= PB_debounced;</pre>

47

48

END IF:

49

50

END PROCESS;

51

52 END a;

```

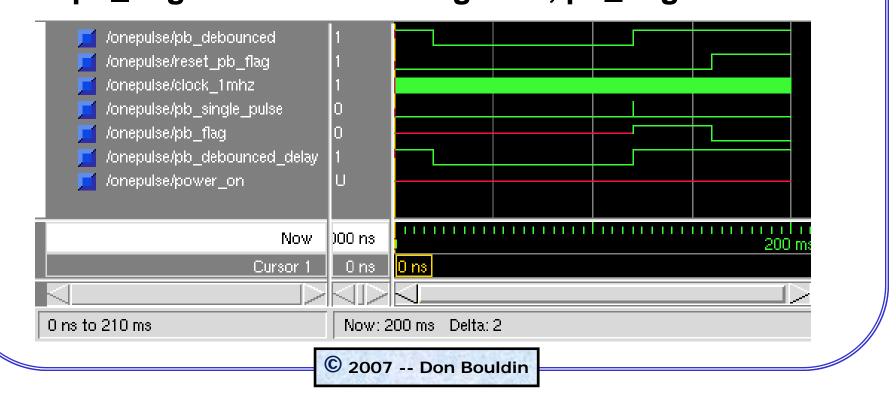

### Simulation of onepulse.vhd (modified)

PB\_debounced has been 0 (active) for 100 ms but only a single 1 ms pulse is produced and pb\_flag is set. After being read, pb\_flag is reset.

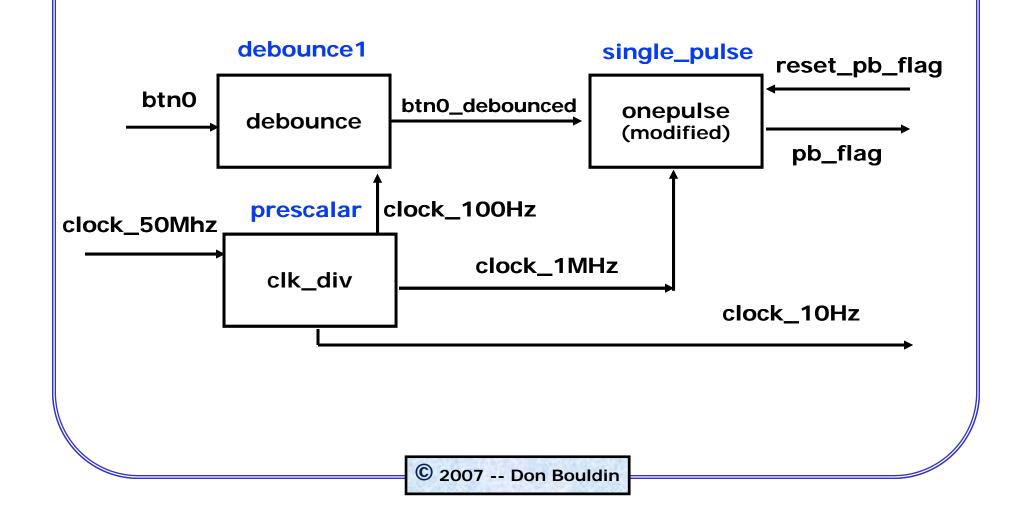

# HIERARCHY WITH SUBMODULE COMPONENTS

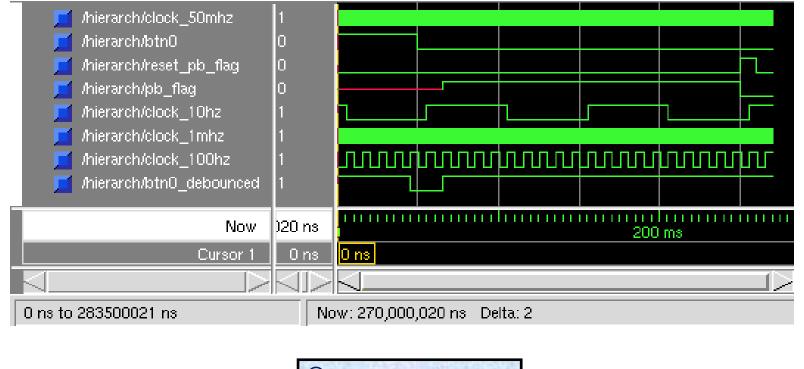

#### Simulation of hierarch.vhd

- A proper pressing of btn0 sets pb\_flag to HIGH.

- Once pb\_flag is read, it is reset to LOW.

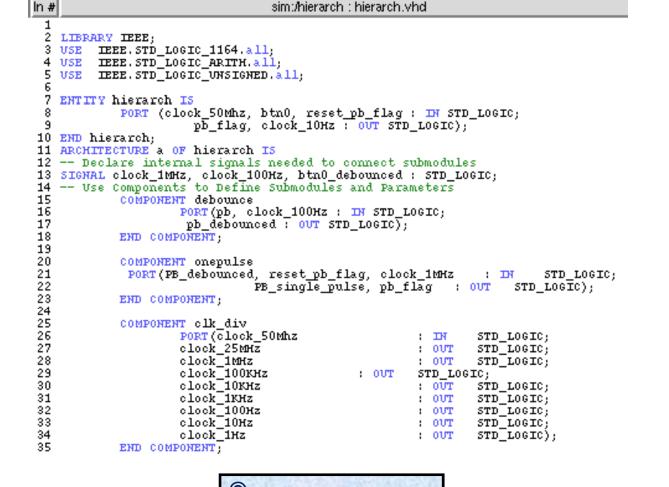

# hierarch.vhd (part 1)

# hierarch.vhd (part 2)

```

the second second second

36 BEGIN

37

38 -- Use Port Map to connect signals between components in the hiearchy

39 debounce1 : debounce PORT MAP (pb => btn0, clock 100Hz => clock 100Hz,

40

pb debounced => btn0 debounced);

41

42 prescalar : clk div PORT MAP (clock 50Mhz => clock 50Mhz, clock 1MHz => clock 1Mhz,

43

clock 100hz => clock 100hz, clock 10hz => clock 10hz);

44

45 single_pulse : onepulse PORT MAP (pb_debounced => btn0_debounced,

46

reset pb flag => reset pb flag,

pb_flag => pb_flag,

47

clock 1mHz => clock 1mHz);

48

49

50 END a;

51

👖 hierarch.vhd

© 2007 -- Don Bouldin

```

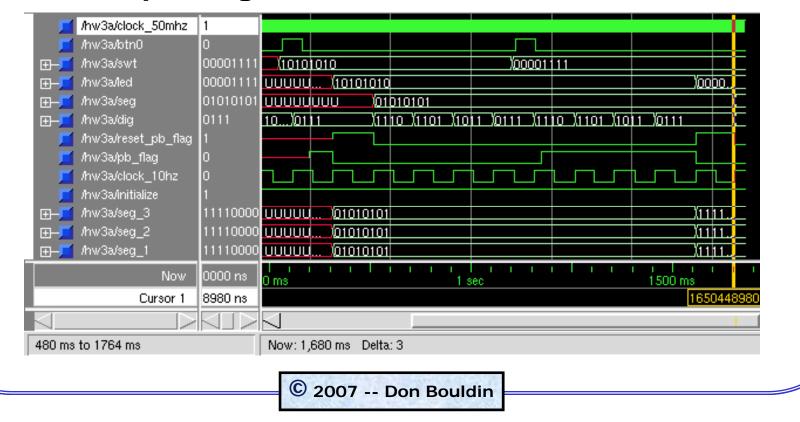

#### Simulation of hw3a.vhd

After btn0 is pressed (properly), the pb\_flag is set. Then while dig "0111" is displayed, swt<7:0> are read and pb\_flag is reset:

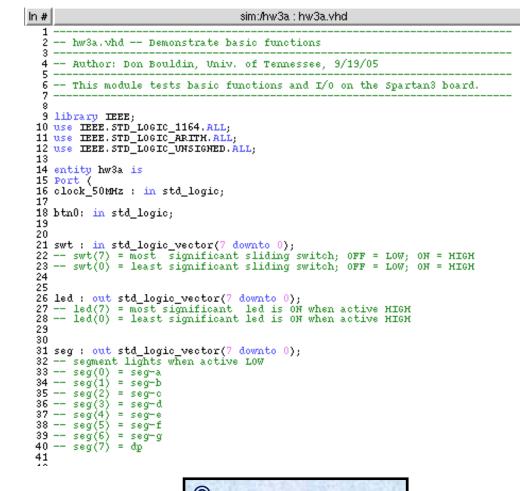

## hw3a.vhd (part 1)

## hw3a.vhd (part 2)

```

sim:/hw3a : hw3a.vhd

ln #

41

42

43 dig : out std_logic_vector(3 downto 0)

44 -- dig(3) = most significant digit is displayed when active LOW

45 -- dig(0) = least significant digit is displayed when active LOW

46

47);

48 end hw3a;

49

50 architecture Behavioral of hw3a is

51

52 SIGNAL reset_pb_flag, pb_flag, clock_10hz: std_logic;

53

54 SIGNAL initialize : STD_LOGIC;

55

56 SIGNAL seg_3 : std_logic_vector(7 downto 0);

57 SIGNAL seg_2 : std_logic_vector(7 downto 0);

58 SIGNAL seg_1 : std_logic_vector(7 downto 0);

59 SIGNAL seq 0 : std logic vector(7 downto 0);

60

61 COMPONENT hierarch

62

PORT (

63

clock_50Mhz, btn0, reset_pb_flag: IN STD_LOGIC;

64

pb_flag, clock_10Hz : OUT STD_LOGIC

65

\rangle_{i}

66 END COMPONENT:

67

68 -- Use Port Map to connect signals between components in the hiearchy

69

70 BEGIN

71

72 hw3a : hierarch PORT MAP (clock_50Mhz => clock_50Mhz,

73

btn0 => btn0.

74

reset pb flag => reset pb flag.

75

pb_flag => pb_flag,

76

clock_10hz => clock_10hz

77

) ÷

78

© 2007 -- Don Bouldin

```

## hw3a.vhd (part 3)

```

sim:/hw3a : hw3a.vhd

ln #

79 -- begin loop

80 PROCESS

81 BEGIN

82

83

-- initialize will be initialized to '0' at power up

IF initialize = '0' THEN

84

85

-- This code resets the critical signals once at power

86

87 reset_pb_flag <= '0';</pre>

88

89 led(7 downto 0) <= "00000000";</pre>

90

91 seg_3(7 downto 0) <= "11111111";

92 seg_2(7 downto 0) <= "11111111";

93 seg_1(7 downto 0) <= "111111111";

94 seg_0(7 downto 0) <= "11111111";

95

96 ELSE

97

initialize <= '1';

98

99 -- display each of the four digits for 0.1 second each forever

100

101

101

102 seg(7 downto 0) <= seg_0(7 downto 0) ;

--digit(0) is ON

104 -- now wait for 0.1 second

105 WAIT UNTIL clock_10hz'EVENT and clock_10hz = '1';

106

107 seg(7 downto 0) <= seg_1(7 downto 0) ;

108 dig(3 downto 0) <= "1101" ;</pre>

--digit(1) is ON

)

109 -- now wait for 0.1 second

110

WAIT UNTIL clock_10hz'EVENT and clock_10hz = '1';

111

112

113 seg(7 downto 0) <= seg_2(7 downto 0);

114 dig(3 downto 0) <= "1011";</pre>

--digit(2) is ON

÷.

115 -- now wait for 0.1 second

WAIT UNTIL clock_10hz'EVENT and clock_10hz = '1';

116

117

118 seg(7 downto 0) <= seg_3(7 downto 0);</pre>

119 dig(3 downto 0) <= "0111"

--digit(3) is ON

)

120 -- now wait for 0.1 second

121

WAIT UNTIL clock_10hz'EVENT and clock_10hz = '1';

122

123

```

# hw3a.vhd (part 4)

```

123

124 -- repeat display until USER sets sliding switches and then presses btn0

125

126 -- if btn0 pressed has NOT occurred then skip to repeat this loop,

127 -- else copy the switch settings and update the display

128

IF pb flag = '1' THEN

129

130

131 -- copy the sliding switch settings to the leds

132 led(7 downto 0) \langle =  swt(7 downto 0);

133

134 -- copy the sliding switch settings to the internal digit segments

135 seq 3(7 downto 0) \overline{\langle} = not (swt(7 downto 0)) ;

136 seq 2(7 downto 0) <= not (swt(7 downto 0));

137 seg_1(7 downto 0) <= not (swt(7 downto 0)) ;

138 seq 0(7 \text{ downto } 0) \leq \text{not } (\text{swt}(7 \text{ downto } 0));

139

140 reset pb flag <= '1';

141 -- now wait for 0.1 second

WAIT UNTIL clock 10hz'EVENT and clock 10hz = '1';

142

143 reset pb flag <= '0';

144 ELSE

145 END IF;

146

147 END IF:

148

149 -- repeat loop

150 END PROCESS:

151

152 END Behavioral;

153

```

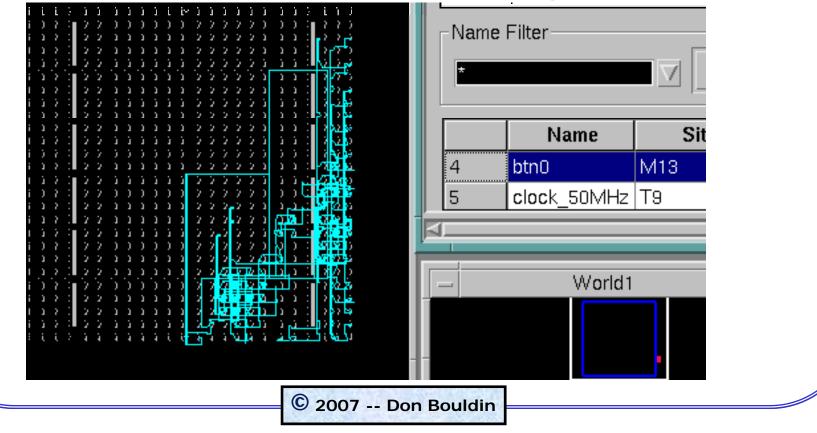

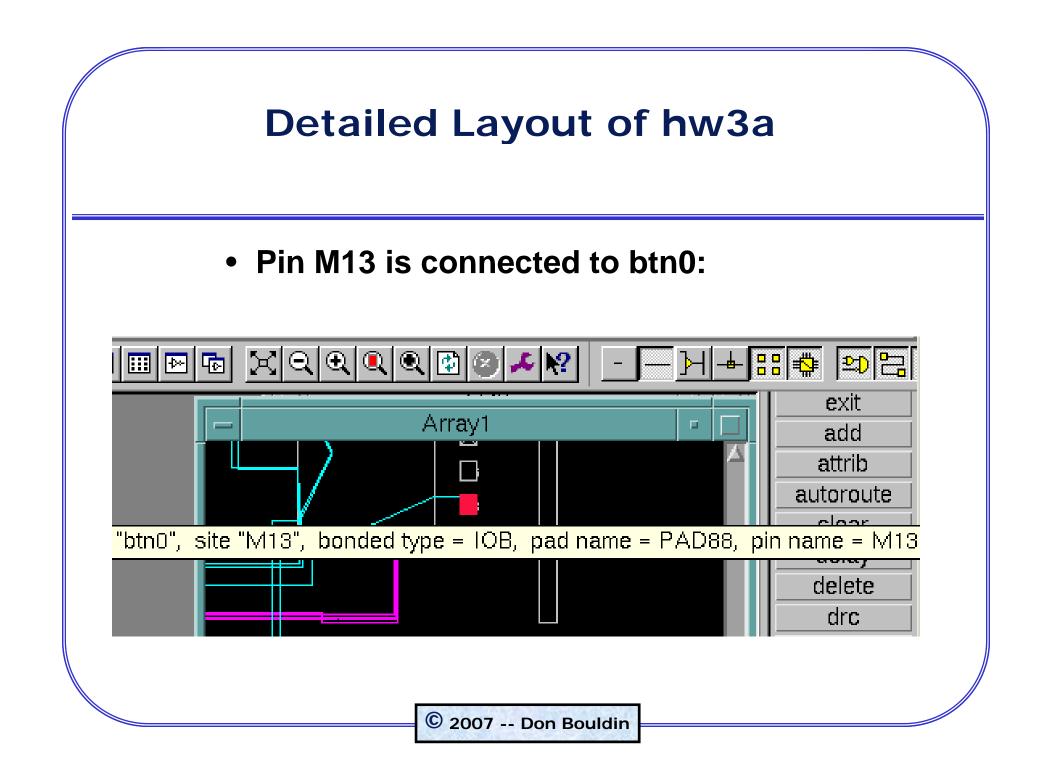

- Logic slices used: 58 out of 1920 = 3%

- The constraint file, hw3a.ucf, assigned the pins.

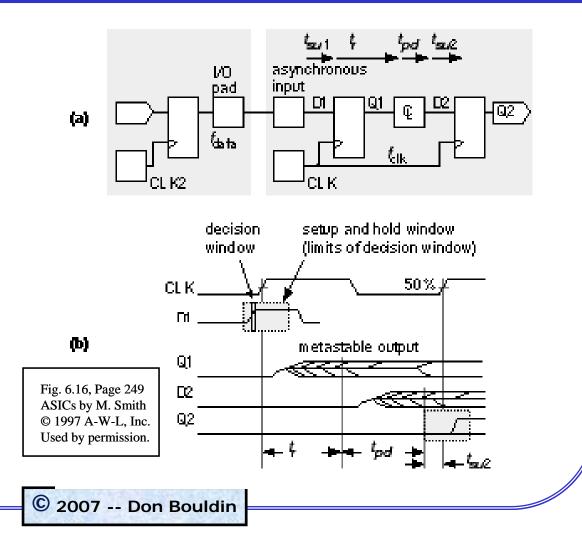

# SYNCHRONIZER REDUCES RISK OF METASTABILITY PROBLEMS

- Signals from external circuits whose clock is independent must be synchronized with our internal clock.

- If not, the external input may occur during the decision window of our flipflop and cause it to go into a metastable state.

- To reduce the likelihood of this occurring, the input can be doublebuffered.