# **SYNOPSYS**®

# DesignWare IBM PowerPC 405-S CPU Core

Design View coreKit User Guide

Database Release 1.1a December 2006

#### **Copyright Notice and Proprietary Information**

Copyright © 2006 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc., for the exclusive use of \_\_\_\_\_\_ and its employees. This is copy number

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks (®)**

Synopsys, AMPS, Cadabra, CATS, CRITIC, CSim, Design Compiler, DesignPower, DesignWare, EPIC, Formality, HSIM, HSPICE, iN-Phase, in-Sync, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Photolynx, Physical Compiler, PrimeTime, SiVL, SNUG, SolvNet, System Compiler, TetraMAX, VCS, and Vera are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

Active Parasitics, AFGen, Apollo, Astro, Astro-Rail, Astro-Xtalk, Aurora, AvanTestchip, AvanWaves, BOA, BRT, ChipPlanner, Circuit Analysis, Columbia, Columbia-CE, Comet 3D, Cosmos, CosmosEnterprise, CosmosLE, CosmosScope, CosmosSE, Cyclelink, DC Expert, DC Professional, DC Ultra, Design Advisor, Design Analyzer, Design Vision, DesignerHDL, DesignTime, Direct RTL, Direct Silicon Access, Discovery, Dynamic-Macromodeling, Dynamic Model Switcher, EDAnavigator, Encore, Encore PQ, Evaccess, ExpressModel, Formal Model Checker, FoundryModel, Frame Compiler, Galaxy, Gatran, HANEX, HDL Advisor, HDL Compiler, Hercules, Hercules-II. Hierarchical Optimization Technology, High Performance Option, HotPlace, HSIM<sup>plus</sup>, HSPICE-Link, iN-Tandem, Integrator, Interactive Waveform Viewer, i-Virtual Stepper, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, JVXtreme, Liberty, Libra-Passport, Library Compiler, Libra-Visa, Magellan, Mars, Mars-Rail, Mars-Xtalk, Medici, Metacapture, Milkyway, ModelSource, Module Compiler, Nova-ExploreRTL, Nova-Trans, Nova-VeriLint, Orion ec, Parasitic View, Passport, Planet, Planet-PL, Planet-RTL, Polaris, Power Compiler, PowerCODE, PowerGate, ProFPGA, ProGen, Prospector, Raphael, Raphael-NES, Saturn, ScanBand, Schematic Compiler, Scirocco, Scirocco-i, Shadow Debugger, Silicon Blueprint, Silicon Early Access, SinglePass-SoC, Smart Extraction, SmartLicense, Softwire, Source-Level Design, Star-RCXT, Star-SimXT, Taurus, TimeSlice, TimeTracker, Timing Annotator, TopoPlace, TopoRoute, Trace-On-Demand, True-Hspice, TSUPREM-4, TymeWare, VCS Express, VCSi, Verification Portal, VFormal, VHDL Compiler, VHDL System Simulator, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (SM)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license.

ARM and AMBA are registered trademarks of ARM Limited.

Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

Synopsys, Inc. 700 E. Middlefield Road Mountain View, CA 94043

www.synopsys.com

## Contents

| Preface                                        |

|------------------------------------------------|

| About This Manual                              |

| Related Documents                              |

| Manual Overview                                |

| Typographical and Symbol Conventions    6      |

| Getting Help 7                                 |

| Additional Information 8                       |

| Chapter 1                                      |

| Introduction                                   |

| PowerPC 405-S CPU coreKits                     |

| Synopsys coreConsultant 10                     |

| AMBA Support 11                                |

| Typical Design Flow    12                      |

| Finding Information                            |

| Chapter 2                                      |

| Getting Started 15                             |

| Installing the coreKit                         |

| Creating a Workspace                           |

| Installing the VMC Model 17                    |

| VMC Model Installation 17                      |

| Pointing to an Existing VMC Model Installation |

| PowerPC 405-S CPU Configuration    20          |

| Chapter 3                                      |

| Simulation – Basic                             |

| Verification Environment Overview              |

| Simulation Methods                             |

| Verification Through coreConsultant            |

| 64-Bit Mode Execution                          |

| General Simulation Options                     |

| Test Selection Options    26                   |

| Launching the Simulation                       |

| Checking Simulation Results                    |

| Simulation Log Files                           |

| Command Line Verification   | 30 |

|-----------------------------|----|

| Viewing VMC Model Signals 3 | 30 |

| Chapter 4                   |    |

| Integration                 | 33 |

|                             | 33 |

|                             | 33 |

| •                           | 34 |

|                             | 37 |

| Timing Model 3              | 38 |

| Chapter 5                   |    |

| Simulation – Advanced       | 39 |

| Testbench Details           | 39 |

| Vera Models 4               | 41 |

|                             | 41 |

| Vera Model Details 4        | 41 |

|                             | 17 |

|                             | 18 |

| •                           | 19 |

|                             | 19 |

|                             | 19 |

|                             | 50 |

## Preface

## **About This Manual**

This manual describes how to work with the DesignWare IBM PowerPC 405-S CPU Core Design View coreKit. The DesignWare IBM PowerPC 405-S CPU Core is a Synopsys DesignWare coreKit implementation of the PPC405F5 CPU core from International Business Machines (IBM) Corporation. Throughout this manual, the term PowerPC 405-S CPU refers to the DesignWare IBM PowerPC 405-S CPU Core.

The Design View coreKit includes a simulation model and a timing model for the PowerPC 405-S CPU, and a testbench for functional simulation. An Implementation View coreKit, which includes synthesizable RTL, is available for implementation purposes.

This manual is intended for use by chip designers who are considering the DesignWare IBM PowerPC 405-S CPU Core for integration into a chip-level design. Readers are assumed to be familiar with HDL-based chip design methodologies and tools. This manual provides setup and simulation procedures for the DesignWare IBM PowerPC 405-S CPU Core Design View coreKit.

## **Related Documents**

This manual is part of the DesignWare IBM PowerPC 405-S CPU Core document set. The complete documentation set resides in the doc directory of your coreConsultant workspace.

## **Manual Overview**

This manual contains the following chapters and appendixes:

| Preface                              | Describes the manual and lists the typographical conventions and symbols used in it; tells how to get technical assistance.                                           |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1<br>"Introduction"          | Provides a general description of the coreKits available<br>for the DesignWare IBM PowerPC 405-S CPU Core and<br>an introduction to the Synopsys coreConsultant tool. |

| Chapter 2<br>"Getting Started"       | Describes how to install the coreKit, create a coreConsultant workspace, and install the PowerPC 405-S CPU VMC model.                                                 |

| Chapter 3<br>"Simulation – Basic"    | Describes how to simulate the PowerPC 405-S CPU VMC model using the supplied testbench and test programs.                                                             |

| Chapter 4<br>"Integration"           | Describes how to instantiate the PowerPC 405-S CPU VMC model in an application-specific test environment and provides information about the timing model.             |

| Chapter 5<br>"Simulation – Advanced" | Provides information for modifying the testbench and simulating custom test programs.                                                                                 |

## **Typographical and Symbol Conventions**

The following conventions are used throughout this document:

| Convention                     | Description and Example                                                                                                                                                                                                      |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| %                              | Represents the UNIX prompt.                                                                                                                                                                                                  |  |  |

| Bold                           | User input (text entered by the user).<br>% cd \$LMC_HOME/hdl                                                                                                                                                                |  |  |

| Monospace                      | System-generated text (prompts, messages, files, reports).<br>No Mismatches: 66 Vectors processed: 66 Possible"                                                                                                              |  |  |

| <i>Italic</i> or <i>Italic</i> | Variables for which you supply a specific value. As a command<br>line example:<br>* setenv LMC_HOME prod_dir<br>In body text:<br>In the previous example, prod_dir is the directory where your<br>product must be installed. |  |  |

| Table 1: | Documentation | Conventions |

|----------|---------------|-------------|

|----------|---------------|-------------|

| Convention            | Description and Example                                                                                                                                                                       |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| (Vertical rule)       | Choice among alternatives, as in the following syntax example:<br>-effort_level low   medium   high                                                                                           |  |  |

| [ ] (Square brackets) | Enclose optional parameters:<br><i>pin1</i> [ <i>pin2 pinN</i> ]<br>In this example, you must enter at least one pin name ( <i>pin1</i> ), but<br>others are optional ([ <i>pin2 pinN</i> ]). |  |  |

| TopMenu > SubMenu     | Pulldown menu paths, such as:<br>File > Save As                                                                                                                                               |  |  |

Table 1: Documentation Conventions (Continued)

## **Getting Help**

For customer support:

- Logon to <a href="http://solvnet.synopsys.com">http://solvnet.synopsys.com</a> using your Solvnet ID and password

- a. Under Support Resources, Click Enter a Call to the support center located at the right top corner

- b. Select Designware STAR IP from product entry

- c. Select Processors from sub product category

- d. Specify the subject and details of issues/errors

- e. Fill in all relevant details and then click Submit

- Send an e-mail message to support\_center@synopsys.com.

- Telephone your local support center:

- United States:

Call 1-800-245-8005 from 7 AM to 5:30 PM Pacific Time, Monday through Friday.

o Canada:

Call 1-650-584-4200 from 7 AM to 5:30 PM Pacific Time, Monday through Friday.

• All other countries:

Find other local support center telephone numbers at the following URL:

http://www.synopsys.com/support/support\_ctr

## **Additional Information**

General information about Synopsys and its products is available at this URL:

http://www.synopsys.com

## 1 Introduction

The DesignWare IBM PowerPC 405-S CPU Core is a DesignWare version of IBM Corporation's PPC405F5 32-bit RISC CPU core.

Synopsys delivers the DesignWare IBM PowerPC 405-S CPU Core (referred to in this user guide as PowerPC 405-S CPU) as a DesignWare coreKit. Separate coreKits are available for evaluation (Design View coreKit) and implementation purposes (Implementation View coreKit).

This manual describes how to work with the Design View coreKit. If this is your first time working with a Design View coreKit, it is important to understand the following concepts before getting started:

- PowerPC 405-S CPU coreKits

- Synopsys coreConsultant

- AMBA Support

- Typical Design Flow

- Finding Information

## **PowerPC 405-S CPU coreKits**

There are two coreKits available for the PowerPC 405-S CPU:

- Design View coreKit Includes:

- o A cycle-accurate VMC model the PowerPC 405-S CPU

- A timing model for an example PowerPC 405-S CPU implementation

- An automated verification environment for functional simulation of the PowerPC 405-S CPU

The Design View coreKit is available to all DesignWare users to evaluate the PowerPC 405-S CPU for use in system-level applications.

• Implementation View coreKit – Includes synthesizable RTL source code for the PowerPC 405-S CPU, plus the same verification environment provided with the Design View coreKit. The Implementation View coreKit is available only to licensed users.

To purchase a license for the Implementation View coreKit, send email to designware@synopsys.com.

This user guide contains user procedures for the Design View coreKit.

The DesignWare IBM PowerPC 405-S CPU Core Implementation View coreKit User Guide, included in the Implementation View coreKit, contains detailed procedures, guidelines, and examples for:

- RTL simulation in an automated verification environment

- Synthesis, including physical synthesis and clock tree synthesis

- Scan/ATPG

- Formal verification

- Power analysis

- Integration

## Synopsys coreConsultant

coreConsultant is a Synopsys design reuse tool that automates the following design tasks for designs that have been packaged as coreKits:

- Installation

- Configuration (for configurable designs)

- Simulation using a verification environment that is packaged into the coreKit

- Synthesis by leveraging design knowledge packaged into the coreKit to directly drive Synopsys synthesis tools (Implementation View coreKits only)

coreConsultant provides a guided flow to execute the above tasks in a logical order. coreConsultant is available to all DesignWare users for use with DesignWare coreKits. Download instructions for the required version of coreConsultant are included in the email that was sent to you in response to your coreKit request. The procedures in this user guide are of the following types:

- General coreConsultant procedures that are built into coreConsultant and are common to all coreKits. This user guide refers you to the *coreConsultant User Guide* for information that is common to coreConsultant and not unique to the PowerPC 405-S CPU coreKit. You can access the *coreConsultant User Guide* by selecting Help > coreConsultant Tool Help > User's Guide in the coreConsultant console.

- Design-specific coreConsultant procedures that are unique to the PowerPC 405-S CPU coreKit. The PowerPC 405-S CPU automated simulation procedures are examples of design-specific coreConsultant procedures, and are explained fully in this user guide.

- Command line procedures that you execute directly from a UNIX command line, and not through coreConsultant. For example, this user guide includes procedures to run simulations directly from a UNIX command line using scripts and utilities included in the coreKit.

- Information to integrate the PowerPC 405-S CPU VMC model into an application-specific testbench.

## **AMBA Support**

The PowerPC 405-S CPU Design View coreKit includes a VMC simulation model for a PLB-to-AHB bidirectional bridge. You can use the PLB4XAHB bridge to connect the Processor Local Bus (PLB) to an AMBA high-performance bus (AHB).

The coreKit also includes an example verification environment that you can use both to test the bridge and as an example for integration. To use the bridge, follow the instructions in the *PLB4XAHB Bridge Application Note*, which is available in your *<workspace>/PLB4XAHB/docs directory* (filename: PLB4XAHB\_application\_note\_<version>.pdf).

#### J Note

Throughout this manual, *<workspace>* refers to the root directory of the coreConsultant workspace that you create using **File > New Workspace** menu in coreConsultant (for example, /usr/cores/ppc\_405/config1). To reload your workspace after quitting coreConsultant, restart coreConsultant and specify the workspace name, for example: coreConsultant config1.

## **Typical Design Flow**

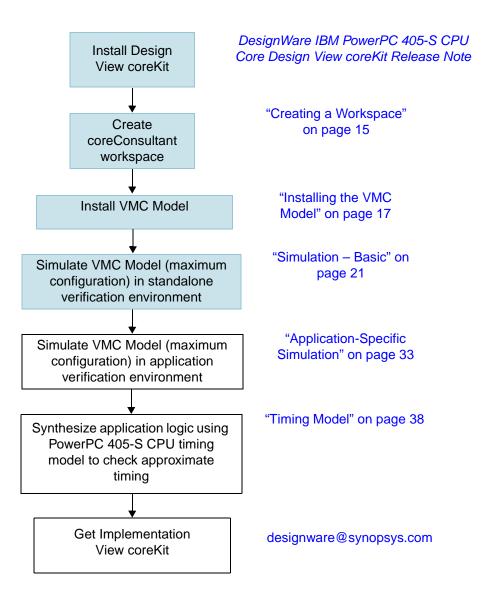

Figure 1 shows a typical evaluation task flow using the Design View coreKit for evaluation of the PowerPC 405-S CPU.

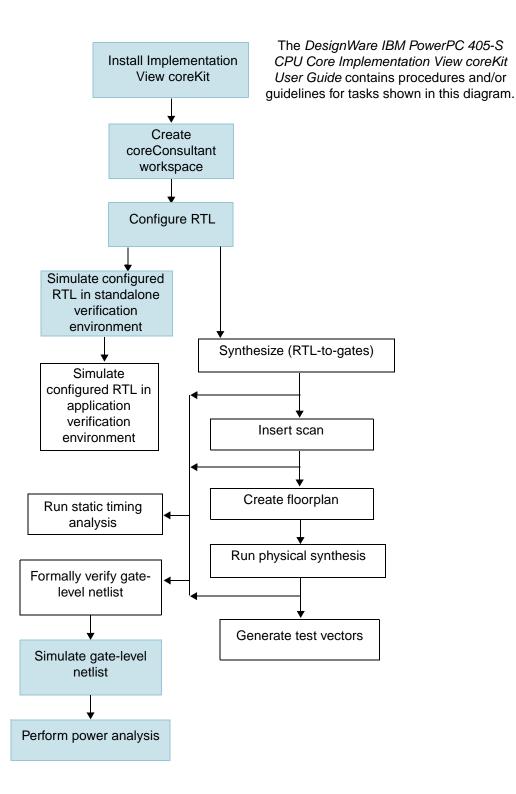

Figure 2 shows a typical implementation task flow using the Implementation View coreKit to implement the PowerPC 405-S CPU in a system-level design.

In both diagrams, the shaded blocks indicate tasks that are automated through coreConsultant. For the non-shaded tasks, the coreKit includes guidelines and/or example scripts.

Figure 1: Typical Evaluation Flow with Design View coreKit

## **Finding Information**

Both of the DesignWare IBM PowerPC 405-S CPU Core coreKits include complete documentation sets to support various hardware and software design tasks. The complete documentation set resides in the doc directory of your coreConsultant workspace.

#### Figure 2: Typical Implementation Flow with Implementation View coreKit

## **2** Getting Started

This chapter gets you started working with the PowerPC 405-S CPU Design View coreKit. The topics are:

- Installing the coreKit

- Creating a Workspace

- Installing the VMC Model

- PowerPC 405-S CPU Configuration

## Installing the coreKit

To install the Design View coreKit, follow the installation instructions that Synopsys sent to you in response to your coreKit request.

For additional information regarding supported tool versions, environment variable settings, new features, and known problems and limitations, refer to the *DesignWare DesignWare IBM PowerPC 405-S CPU Core Design View coreKit Release Note*.

## **Creating a Workspace**

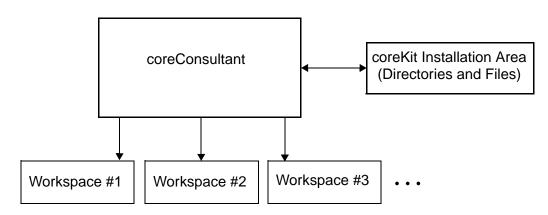

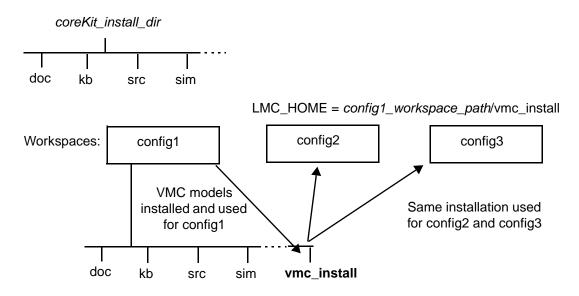

A coreConsultant workspace is a local, modifiable copy of your coreKit installation in which you work with the deliverables included in the coreKit. After you install the coreKit, you must create a workspace to begin working. You can create several workspaces so that you can experiment with different design alternatives, as shown in Figure 3.

To create a workspace:

- 1. Invoke coreConsultant:

- % coreConsultant

- 2. Select **File > New Workspace** in the coreConsultant console, then enter the requested information in the New Workspace dialog. See the *coreConsultant User Guide* for details.

#### Figure 3: coreKit and Workspaces

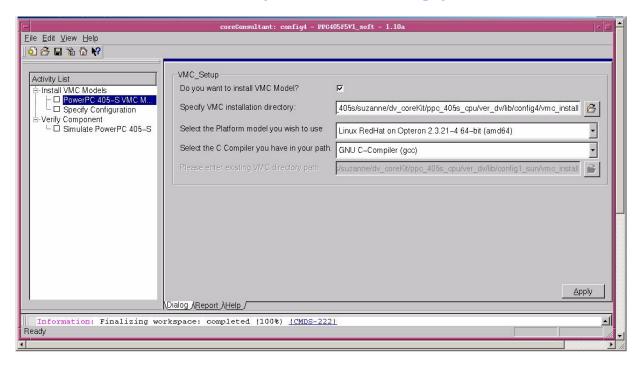

At the completion of workspace creation, coreConsultant displays the Activity List. For the Design View coreKit (Figure 4), the first activity to execute is PowerPC 405-S VMC Model Installation. Go to "Installing the VMC Model" on page 17 to continue.

Figure 4: Design View coreKit VMC\_Setup Activity

## **Installing the VMC Model**

The Design View coreKit includes a cycle-accurate VMC model for the DesignWare IBM PowerPC 405-S CPU Core. The VMC model is a SWIFT R41-compliant model that is compatible with the most commonly used HDL simulation tools. By default, the testbench in the Design View coreKit instantiates the VMC model, encapsulated in the SWIFT template required for your simulator.

If you want to create more than one workspace, you can save disk space by installing the VMC model once for the first workspace, then pointing to that installation in additional workspaces.

When you install the VMC model for the PowerPC 405-S CPU, coreConsultant also installs the VMC models for two of the models used in the testbench:

- IBM PLB slave

- IBM PLB Nebula arbiter

The above models represent IP for PLB-compatible designs and are delivered as VMC models to protect that IP.

## **VMC Model Installation**

To install the VMC models, go to the PowerPC 405 VMC Model page of the coreConsultant Activity List (Figure 4), then select the following installation options (see Table 2 for details):

- **Do you want to install VMC Model?** Select this option to install the VMC models.

- **Specify VMC installation directory** The absolute path to where you want to install the VMC models. Either enter the path name or use the [...] button to navigate and select and directory.

- Select the Platform model you wish to use Select your platform from the list of supported platforms.

#### J Note

coreConsultant must be currently invoked and operating on the platform you select.

• Select the C Compiler you have in your path – Choose the C compiler in your path.

After you select your installation options, click **Apply** to complete the VMC Model Installation activity. coreConsultant installs the VMC models for the platform you selected into your selected directory.

#### Kote-

The automated verification procedures automatically set LMC\_HOME to point to your VMC model installation directory. It also automatically sets LD\_LIBRARY\_PATH to \$LMC\_HOME/lib/<platform>.lib. To use the VMC models in a different context, you need to explicitly set LMC\_HOME to point to your VMC model installation directory. and LD\_LIBRARY\_PATH to the LMC\_HOME shared libraries

| Option                                    | Definition                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Do you want to install VMC<br>Model?      | Specifies whether to install the VMC models or use previously installed VMC models, and enables the corresponding option below.                                                                                                                                                                                                     |

| Specify VMC installation directory        | If you choose to install the VMC models, specify the directory into which you want to install them. The default path is <i><workspace>/vmc_install.</workspace></i>                                                                                                                                                                 |

| Select the Platform model you wish to use | Whether you are installing the VMC models or pointing to a previously installed version, select the platform you are using from the supported list.                                                                                                                                                                                 |

| Please enter existing VMC directory path  | If you choose to point to previously installed VMC models, enter<br>the path to the existing installation directory. For example, if you<br>previously installed the VMC models into the vmc_install<br>subdirectory of workspace config1, select<br><config1_workspace_path>/vmc_install for this option.</config1_workspace_path> |

#### Table 2: VMC Model Installation Options

## Pointing to an Existing VMC Model Installation

If you want to set up your workspace to point to previously installed VMC models instead of creating an additional installation:

- Go to the PowerPC 405 VMC Model page in the coreConsultant Activity List (Figure 4), then select the following installation options:

- Do you want to install VMC Model? Do not select this option.

- Select the Platform model you wish to use Select the platform from the list of supported platforms.

#### 了 Note-

coreConsultant must be currently invoked and operating on the platform you select.

- Select the C Compiler you have in your path Select the compiler in your path.

- Please enter existing VMC directory path The absolute path to the existing VMC model installation (for example, <*config1\_workspace\_path>/* vmc\_install. Either enter the path name or use the [...] button to navigate and select a directory. If you set the LMC\_HOME environment variable before invoking coreConsultant, this path will become the default.

After you select your installation options, click **Apply** to complete the VMC Model Installation activity. coreConsultant sets up your workspace to point to the selected VMC model installation directory.

Figure 5 shows an example setup where the user chooses to install the VMC models in the vmc\_install subdirectory of the config1 workspace, then uses that installation for additional workspaces (config2 and config3).

**NOTE:** This example shows the VMC models installed in the vmc\_install directory of config1. However, this is not a requirement. You can install the VMC models anywhere.

#### Figure 5: Using a Single VMC Model Installation for Multiple Workspaces

## **PowerPC 405-S CPU Configuration**

The PowerPC 405-S CPU VMC model in the Design View coreKit is not configurable. The Specify Configuration step appears in the coreConsultant activity flow for the PowerPC 405-S CPU Design View coreKit, but does not allow you to change any configuration parameters.

# **3** Simulation – Basic

The PowerPC 405-S CPU Design View coreKit includes a functional verification environment that enables you to quickly evaluate the PowerPC 405-S CPU core by running the provided test programs. The verification environment is intended as an example platform for running simulation of the PowerPC 405-S CPU in a simple testbench, not as an extensive environment for full functional verification.

A similar verification environment is included in the Implementation View coreKit. In the Design View coreKit, the device under test is the PowerPC 405-S CPU VMC model; in the Implementation View coreKit, the device under test is the RTL source code for the PowerPC 405-S CPU.

This chapter describes how to perform automated simulation procedures using the supplied verification environment. The topics are:

- Verification Environment Overview

- Simulation Methods

- Verification Through coreConsultant

- Simulation Log Files

- Command Line Verification

- Viewing VMC Model Signals

For information about how to perform more advanced simulation tasks, such as customizing the testbench and executing custom test programs, refer to "Simulation – Advanced" on page 39.

## **Verification Environment Overview**

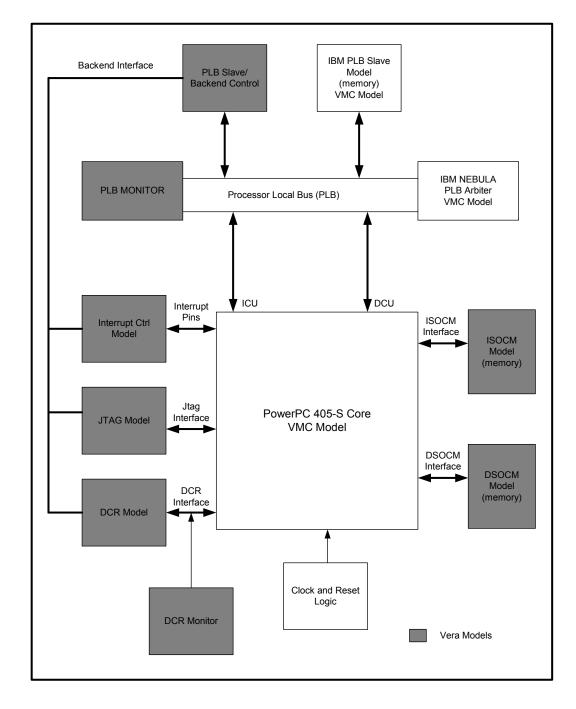

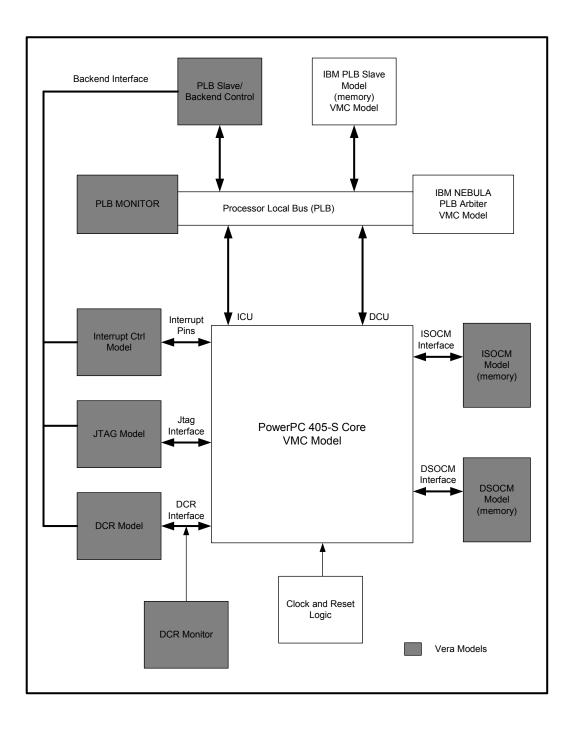

The verification environment consists of:

- A testbench (Figure 6) that instantiates the PowerPC 405-S CPU VMC model as the device under test, plus the models listed in Table 3 attached to the PowerPC 405-S CPU interfaces.

- A set of test programs to verify the functionality of the PowerPC 405-S CPU. Each of the tests is self-checking and returns a pass or fail status.

- Scripts to automatically run the selected test programs on your HDL simulator.

You can run simulation either through the coreConsultant GUI or directly from the UNIX command line using the supplied scripts.

## **Simulation Methods**

There are two ways to run simulations with the PowerPC 405-S CPU verification environment:

- Verification Through coreConsultant involves running simulations through the coreConsultant GUI. coreConsultant prompts you for simulation options, including which test programs you want to run, then automatically generates a script to run the simulation according to your selections. coreConsultant also invokes the run script, displays simulation status during the simulation, and displays the results when the simulation is complete.

- Command Line Verification involves executing the run script from the UNIX command line. Before you can run command line verification, you must run at least one simulation through coreConsultant to set up the verification environment in your coreConsultant workspace.

Figure 6: Testbench Block Diagram

| Model                       | Format    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLB slave/device controller | Vera      | Controls the PLB monitor, interrupt controller<br>model, JTAG model, and DCR model. Test<br>programs running on the PowerPC 405-S CPU<br>VMC model write to memory-mapped registers<br>in the PLB slave/device controller to control the<br>operation of the models connected through the<br>control interface.<br>The slave/device controller model does not<br>support the complete set of PLB transactions. It<br>only uses the PLB transactions needed to<br>provided the necessary control functions. |

| IBM PLB slave model         | VMC model | IBM PLB slave model that supports the<br>complete set of PLB transactions, used for<br>functional testing of PLB operation. The IBM<br>PLB slave model also contains the instruction<br>and data memory for the PowerPC 405-S CPU.                                                                                                                                                                                                                                                                         |

| IBM PLB Nebula arbiter      | VMC model | IBM PLB Nebula arbiter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PLB monitor                 | Vera      | Logs PLB transactions and detects PLB protocol errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt controller model  | Vera      | Generates interrupt signals to the PowerPC 405-<br>S CPU, as controlled by the test program<br>through the PLB slave/device controller model.                                                                                                                                                                                                                                                                                                                                                              |

| JTAG model                  | Vera      | Stimulates the JTAG interface pins to the<br>PowerPC 405-S CPU, as controlled by the test<br>program through the PLB slave/device controller<br>model.                                                                                                                                                                                                                                                                                                                                                     |

| DCR model                   | Vera      | Provides a simple DCR model to exercise the <b>mfdcr</b> and <b>mtdcr</b> instructions.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DCR monitor                 | Vera      | Logs transactions occurring on the DCR interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Clock logic                 | Verilog   | Accepts SystemClock from top-level testbench<br>and provides all necessary clocks to the<br>PowerPC 405-S CPU. The clock logic also<br>includes the logic to generate the clock enable<br>signals used for sleep mode control.                                                                                                                                                                                                                                                                             |

| Reset logic                 | Vera      | Logic to drive the reset signals to the PowerPC 405-S CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 3: Models Used in the Testbench

| Model       | Format | Function                                                                        |

|-------------|--------|---------------------------------------------------------------------------------|

| ISOCM Model | Vera   | The Instruction Side On-Chip Memory<br>(ISOCM) only supports single cycle mode. |

| DSOCM Model | Vera   | The Data Side On-Chip Memory (DSOCM) only supports single cycle mode.           |

Table 3: Models Used in the Testbench

## Verification Through coreConsultant

To run the simulation through coreConsultant, go to the Simulate PowerPC 405 page of the coreConsultant Activity List (Figure 8), then select simulation options and execute the simulation as described in the following sections.

## 64-Bit Mode Execution

The PowerPC 405-S verification environment supports 64-bit mode execution of the supported simulators. To enable 64-bit mode:

- Make sure you have the appropriate environement variables and your path is pointing to your 64-bit simulator prior to running coreConsultant.

- In coreConsultant, select Tool Installation Roots from the Edit pull-down menu at top left.

- Check the "64-bit" box for your simulator and Vera.

See Figure 7 for details.

| -                                                                                  | Set tool installation roots                      |                             |

|------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------|

| Specify tool installation directories f<br>If the 64 bit version of the tool is de |                                                  |                             |

| Design Compiler (dc_shell)                                                         | /global/apps2/syn_2006.06-SP1                    | ⊏ 64 Bit?                   |

| Physical Compiler (psyn_shell)                                                     | /global/apps2/syn_2006.06-SP1                    | I‴ 64 Bit?                  |

| PrimeTime (pt_shell)                                                               | 6                                                | I‴ 64 Bit?                  |

| Formality (fm_shell)                                                               | 6                                                | ⊏ 64 Bit?                   |

| DC FPGA (fpga_shell)                                                               | 6                                                | ⊏ 64 Bit?                   |

| TetraMax (tmax)                                                                    | /global/apps2/syn_2006.06-SP1                    | I‴ 64 Bit?                  |

| VCS (vas)                                                                          | /global/apps2/vcs_2006.06                        | I⊽ 64 Bit?                  |

| VCSi (vosi)                                                                        | /global/apps2/vcs_2006.06                        | r⊏ 64 Bit?                  |

| Vera (vera)                                                                        | apps2/vera_2005.06-SP1/vera_vX-2005.06-SP1_amd64 | I⊽ 64 Bit?                  |

| MTI ModelSim (vsim)                                                                | 6                                                | r⊏ 64 Bit?                  |

| NC Verilog/VHDL (ncsim)                                                            | 6                                                | I‴ 64 Bit?                  |

|                                                                                    | <u></u> K                                        | <u>C</u> ancel <u>H</u> elp |

Figure 7: coreConsultant Tool Installation Roots Selection Page

## **General Simulation Options**

The first two pages of simulation options are standard simulation options provided by coreConsultant:

- Simulator options Options to select and set up your simulation tool. These options are common to several DesignWare coreKits. Use the coreConsultant online help for more information about individual options.

- Execution options Options related to simulation launch and execution. These options are also common to several DesignWare coreKits. Use the coreConsultant online help for more information about individual options.

#### J Note

Do not click **Apply** in the Simulate PowerPC 405 dialog (Figure 8) until you have confirmed your selections on all three pages of the dialog.

| Eile Edit ⊻iew Help |                                                  |                                                                                                                                                                                                                               | 1                                                                           |

|---------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Activity List       | Simulator<br>Execution Optio<br>Select Testsuite | Simulator<br>Select Simulator<br>Simulator                                                                                                                                                                                    | ▲                                                                           |

|                     |                                                  | Simulator Setup<br>Root Directory of Cadence Installation (formerly \$CDS_INST_DIR)<br>MTI Include Directory<br>Vera Install Area (\$VERA_HOME)<br>Vera .vro file cache directory<br>C Compiler (for Vera PLI)<br>Waves Setup | /global/apps/vera_6.4.0/v<br>v_071305/ppc_405s_cpu/<br>GNU C-Compiler (gcc) |

|                     | SYNOPSYS<br>Dialog (Report (Help                 | Previous Next                                                                                                                                                                                                                 | Apply Default                                                               |

Figure 8: Simulate Dialog – Simulator Options

## **Test Selection Options**

Using the coreConsultant test selection dialog (Figure 9), you can select to either run all of the provided test programs (the default selection) or just execute selected individual tests (**Run\_User\_Specified\_Tests** option).

| Eile Edit View Help                                               |                                      |                        |                                                                    |

|-------------------------------------------------------------------|--------------------------------------|------------------------|--------------------------------------------------------------------|

|                                                                   | Simulator                            |                        | Select Testsuite                                                   |

| Activity List                                                     | -Execution Optio<br>Select Testsuite | Select Testsuite       | ₢ Run_All_Tests                                                    |

| PowerPC 405–S<br>☑ Specify Configur                               |                                      |                        | C Run_User_Specified_Tests                                         |

| E Specify Conligui<br>E-Verify Component<br>└──□ Simulate IBM 405 |                                      | User Testsuite Filenam | spse/pri/ppc_405s/vikasg/405_071305/ppc_405s_cpu/ver_dv/lib/config |

| Simulate IBM 403                                                  |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      |                        |                                                                    |

|                                                                   |                                      | [+]                    |                                                                    |

|                                                                   | SYNOPSYS <sup>®</sup>                |                        | Previous Next Apply Default                                        |

|                                                                   | Dialog (Report (Help                 |                        |                                                                    |

#### Figure 9: Simulate Dialog – Test Selection

The recommended strategy for test execution is:

- 1. Select and run a single test to make sure that your simulation is set up properly and the test can run without encountering any simulator setup errors.

- 2. Select and run all tests to verify that all tests pass.

- 3. If any test fails, contact support\_center@synopsys.com. There is no known reason for any test to fail.

To select individual tests:

1. Make an editable copy of the supplied testlist file (*<workspace>/sim/testcase.list*). For example:

```

% cd <workspace>/sim

```

```

% cp testcase.list userlist

```

You can choose any name and location for the editable test list file. The default user test list is *<workspace>/sim/userlist*, but you can specify a different path and file name.

2. Edit your copy of the test list file. Insert a semicolon (;) at the beginning of the line for each test that you do not want to execute, as shown in the following example:

```

fvt.exe.1

;fvt.exe.2

;fvt.icu.1

;fvt.icu.2

;fvt.icb.1

...

```

In the above example, the only test selected for execution is fvt.exe.1.

3. In the Testsuite Selection dialog (Figure 9), select **Run\_User\_Specified\_Tests** and enter the file name (including full path) of your custom test list file. The default is <*workspace*>/sim/userlist.

## Launching the Simulation

After you select your simulation options and tests, click **Apply** to launch the simulation. If you selected the **Do Not Launch Simulation** option, coreConsultant will not invoke the simulation; go to your *<workspace>/*sim directory and execute run.scr to run the simulation.

### **Checking Simulation Results**

After you click **Apply** to start the simulation, the Simulate Report page appears (Figure 10) to display the status of the simulation job: running, done, or killed.

To update the status information in Figure 10, click the Reload (<sup>(2)</sup>) button. When the simulation is complete, clicking the Reload button causes the simulation report (Figure 11) to appear below the status information.

Figure 11 shows an example of the simulation report. The simulation report includes pass/fail status for each test in the most recent simulation run.

The report also contains links to the simulation log for each completed test. See "Simulation Log Files" on page 30 for information about the contents of the log files.

| 🔄 🔊 🕱 🕅 File: td:sAd::showReportPage |                |                                     |                                            |                                                                                         |                                                                                                              |

|--------------------------------------|----------------|-------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Job Stat                             | us             |                                     |                                            |                                                                                         |                                                                                                              |

| Run Style                            | Execution Host | Job Id                              | Job Status                                 | Results File                                                                            |                                                                                                              |

| local                                | kilo2          | 18954                               | running <u>(kill)</u>                      | report/simulation.html                                                                  |                                                                                                              |

|                                      | Job Stat       | Job Status Run Style Execution Host | Job Status Run Style Execution Host Job Id | Job Status           Run Style         Execution Host         Job Id         Job Status | Job Status           Run Style         Execution Host         Job Id         Job Status         Results File |

Figure 10: Simulate Status Dialog

|                                          | Simu                                                           | lation Resul                                   | lts                         |                                 |

|------------------------------------------|----------------------------------------------------------------|------------------------------------------------|-----------------------------|---------------------------------|

| Simulation<br>dir: /spse/prj/ppc_40      | orj/ppc_405s/arulmani/corekit<br>05s/arulmani/corekit_build/pp | c_405s_cpu/ver_dv/lib/cc                       | onfig2/sim                  | Simulation Sum<br>Simulation De |

| Start: 13:38:39 (03//<br>Passed: 2 Faile | d: 0 Expected Fail: 1                                          | 가슴 옷을 하는 것 같은 것을 수 있는 것을 하는 것을 하는 것이다.         | olved: 0                    |                                 |

| 것 ~~~ ~ 말 ~ 것 ~~~ ~ 말 말 것 않는 ~           | d: 0 Expected Fail: 1                                          | Timeout: 0 Unreso                              | olved: 0                    | 1                               |

| Passed: 2 Faile                          | d: 0 Expected Fail: 1<br>Simu                                  | Timeout: 0 Unreso                              | slved: 0                    |                                 |

| Passed: 2 Faile<br>Testcase              | d: 0 Expected Fail: 1<br>Simu<br>Sim_Log                       | Timeout: 0 Unreso<br>Ilation Summary<br>Status | sived: 0<br>Y<br>Statistics | -                               |

#### Figure 11: Simulate Report

An fvt.fail testcase failure is expected.

## **Simulation Log Files**

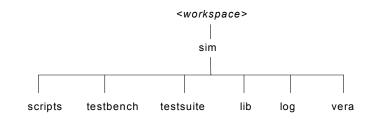

Simulation of one or more test programs, creates the following log files in your <*workspace*>/sim/log/<*testname*> directory, where <*testname*> is a test name as it appears in the test list file:

- <workspace>/sim/log/<testname>./<testname>.log Simulation execution messages for <testname>. This is the log file that is linked to the simulation summary results (Figure 11). If a test fails, examine the <testname>.log file to determine the cause of the failure. If there is a problem invoking your selected simulation tool, the corresponding error messages will appear in <testname>.log.

- <*workspace*>/sim/test.log Log file similar to <*testname*>.log, but includes log messages for all tests executed.

## **Command Line Verification**

To run a simulation directly from the UNIX command line, perform the following steps:

- Run at least one simulation through coreConsultant to set up your workspace for simulation, select tests, and generate a simulation run script (run.scr). Select the "Do Not Launch Simulations" option to generate run.scr without running the simulation. If you want to execute only selected tests, be sure to select the Run\_User\_Specified\_Tests and enter the file name (including full path) of your custom test list file.

- 2. Run the simulation. To do so, go to your *<workspace>/*sim directory and execute the run script:

- % cd <workspace>/sim

% ./run.scr

The run.scr script performs the following tasks:

- Invokes Vera to re-compile the testbench configuration files.

- Invokes your selected simulator to compile the testbench files, generate a simulator executable, and run the simulation.

- 3. Check the simulation results by examining the following log files for each test that you selected:

- *«workspace»/sim/test.log PASSED or FAILED status for <testname».*

- <workspace>/sim/log/<testcase\_name>/<testcase\_name>.log Detailed messages about test execution (see "Simulation Log Files" on page 30).

To change your selection of tests to be executed or any other simulation parameter, use coreConsultant to make your selections in GUI mode. Select **Do Not Launch Simulation**, and click **Apply**. coreConsultant generates a new run.scr, which you can then execute from the UNIX command line as described above.

If you had previously selected the **Run\_User\_Specified\_Tests** option, you do not need to return to the GUI to change your test selection. Just edit the test list file and execute run.scr.

## Viewing VMC Model Signals

When simulating the VMC model on a Verilog simulator, the contents of several internal registers and internal signals are available through VMC model windows. Table 4 lists the internal SFRs and GPRs.

The windows listed in Table 4 are enabled by default in the supplied testbench and are available for viewing if you create a dump file by choosing the **Generate 'waves' file** option in coreConsultant. To enable the VMC model windows for viewing in an application-specific simulation environment, see "Enabling VMC Model Register Windows" on page 37.

| Register    | Description                            |

|-------------|----------------------------------------|

| dcdAddr     | Decode Address                         |

| dcdData     | Decode Data                            |

| exeFull     | Instruction fetch full                 |

| exeAddr     | Instruction fetch Address              |

| exeAReg     | Execution A Register                   |

| exeBReg     | Execution B Register                   |

| exeResult   | Execution Result                       |

| GPR0-GPR31  | GPR Register 0-31                      |

| CR          | Condition Register                     |

| CTR         | Count Register                         |

| DAC1-DAC2   | Data Address Compare 1-2               |

| DVC1-DVC2   | Data Value Compare 1-2                 |

| XER         | Fixed Point Exception Register         |

| DBCR0-DBCR1 | Debug Control Register 0-1             |

| DBSR        | Debug Status Register                  |

| DBDR        | Debug Data Register                    |

| DCCR        | Data Cache Cachability Register        |

| DEAR        | Data Error Address Register            |

| DCWR        | Data Cache Write through Register      |

| ICCR        | Instruction Cache Cachability Register |

Table 4: VMC Model Windows – Internal Registers

| Register  | Description                           |

|-----------|---------------------------------------|

| SLER      | Stroage Little Endian Register        |

| SUOR      | Storage User-defined 0 Register       |

| SGR       | Storage Guarded Register              |

| ZPR       | Zone protection Register              |

| PID       | Process ID                            |

| CCR0-CCR1 | Core Configuration Register           |

| ICDBDR    | Instruction Cache Debug Data Register |

| IAC1-4    | Instruction Address Compare 1-4       |

| LR        | Link Register                         |

| EVPR      | Exception Vector Prefix Register      |

| SPRG0-7   | SPR General 0-7                       |

| SRR0-3    | Save/Restore Register 0-3             |

| MSR       | Machine State Register                |

| PVR       | Processor Version Register            |

| ESR       | Exception Syndrome Register           |

| PIT       | Programmable Interval Timer           |

| ТВН       | Timer Base Higher                     |

| TBL       | Timer Base Low                        |

| TSR       | Timer Status Register                 |

| TCR       | Timer Control Register                |

| Table 4: | VMC Model | Windows - | - Internal | Registers |

|----------|-----------|-----------|------------|-----------|

|----------|-----------|-----------|------------|-----------|

# 4 Integration

This chapter provides information and guidelines for the following integration-related topics:

- Application-Specific Simulation

- Timing Model

## **Application-Specific Simulation**

Simulation of the PowerPC 405-S CPU VMC model in an application-specific verification environment involves:

- Instantiating the VMC Model

- Simulator Requirements for the VMC Model

- Enabling VMC Model Register Windows

## Instantiating the VMC Model

To instantiate the VMC model in an application-specific testbench, you need to instantiate the HDL wrapper module defined in the SWIFT template for VMC model. Follow these steps to instantiate the VMC model:

- 1. Execute the Simulate VMC Model activity at least once to set up the verification environment. See "Verification Through coreConsultant" on page 25.

- 2. Instantiate the HDL module PPC405F5V1\_soft in your application-specific testbench. Follow the example in the supplied testbench file (*<workspace>/sim/* testbench/p405s\_test\_top.v). In the Verilog testbench, the instance name for PPC405F5V1\_soft is dut.

- 3. Include the SWIFT template file for the VMC model in your simulation file list:

- For VCS, use <*workspace*>/src/vmc/p405s\_vmcmodel\_vcs.v

- For NC-Verilog, use <workspace>/src/vmc/p405s\_vmcmodel\_nc.v

- o For MTI-Verilog, use <workspace>/src/vmc/p405s\_vmcmodel\_mti.v

- 4. Set the following environment variables before you run the simulation:

- LMC\_HOME Point to the existing VMC model installation directory. For example:

- % setenv LMC\_HOME <config1\_workspace\_path>/vmc\_install

- 5. Include the simulator-specific variables and options as described in Simulator Requirements for the VMC Model below when you run your simulation.

## Simulator Requirements for the VMC Model

Include the required LD\_LIBRARY\_PATH and options for the SWIFT PLIs when you execute your simulator-specific compile and run commands. Table 5 shows some examples for the supported simulators. For more complete information about how to use VMC models with your simulator, refer to:

- Your simulator documentation

- *Simulator Configuration Guide for Synopsys Models* (available at www.synopsys.com/products/designware/docs/doc/smartmodel/manuals/simcfg.pdf

#### Table 5: Simulator-Specific Command Switches for 32-Bit Sun Solaris

| Simulator           | Required Compile/Run Options                                                                                                                                                                                           |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCS                 | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sun4Solaris.lib<br>setenv LMC_USE_32BIT 1<br>vcs command: Include -lmc-swift                                                                                                   |

| NC-Verilog          | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sun4Solaris.lib<br>setenv LMC_USE_32BIT 1<br>ncvlog command: Include +loadpli1=swiftpli:swift_boot<br>+incdir+\$LMC_HOME/sim/pli/src+ncaccess+r+w                              |

| ModelSim<br>Verilog | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sun4Solaris.lib<br>setenv LMC_USE_32BIT 1<br>vlog command: Include +incdir+\$LMC_HOME/sim/pli/src<br>vsim command: Include -pli \$LMC_HOME/lib/sun4Solaris.lib/swiftpli.mti.so |

| Table 6: S | Simulator-S | pecific Command | Switches for | or 64-Bit Sun Solaris |

|------------|-------------|-----------------|--------------|-----------------------|

|------------|-------------|-----------------|--------------|-----------------------|

| Simulator           | Required Compile/Run Options                                                                                                                                                         |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCS                 | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sparc64.lib<br>vcs command: Include -lmc-swift -full64                                                                                       |  |

| NC-Verilog          | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sparc64.lib<br>ncvlog command: Include +loadpli1=swiftpli:swift_boot<br>+incdir+\$LMC_HOME/sim/pli/src+ncaccess+r+w                          |  |

| ModelSim<br>Verilog | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/sparc64.lib<br>vlog command: Include +incdir+\$LMC_HOME/sim/pli/src<br>vsim command: Include -pli \$LMC_HOME/lib/sparc64.lib/swiftpli.mti.so |  |

# Table 7: Simulator-Specific Command Switches for Red Hat EnterpriseLinux v.3 Operating System for 64-Bit Opteron Processor

| Simulator             | <b>Required Compile/Run Options</b>                                                                                                                                          |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCS                   | SHLIB_PATH: Include \$LMC_HOME/lib/amd64.lib<br>vcs command: Include -lmc-swift -full64                                                                                      |  |

| NC-Verilog            | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/amd64.lib<br>ncvlog command: Include +loadpli1=swiftpli:swift_boot<br>+incdir+\$LMC_HOME/sim/pli/src+ncaccess+r+w                    |  |

| ModelSim<br>(Verilog) | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/amd64.lib<br>vlog command: Include +incdir+\$LMC_HOME/sim/pli/src<br>vsim command: Include -pli \$LMC_HOME/lib/amd64/swiftpli_mti.sl |  |

# Table 8: Simulator-Specific Command Switches for Red Hat EnterpriseLinux v.3 Operating System for 32-bit Processors

| Simulator  | <b>Required Compile/Run Options</b>                                                                                                                                                 |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VCS        | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/linux.lib setenv<br>LMC_USE_32BIT 1<br>vcs command: Include -lmc-swift                                                                      |  |

| NC-Verilog | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/linux.lib setenv<br>LMC_USE_32BIT 1<br>ncvlog command: Include +loadpli1=swiftpli:swift_boot<br>+incdir+\$LMC_HOME/sim/pli/src+ncaccess+r+w |  |

# Table 8: Simulator-Specific Command Switches for Red Hat EnterpriseLinux v.3 Operating System for 32-bit Processors

| Simulator             | <b>Required Compile/Run Options</b>                                         |  |

|-----------------------|-----------------------------------------------------------------------------|--|

| ModelSim<br>(Verilog) | LD_LIBRARY_PATH: Include \$LMC_HOME/lib/linux.lib setenv<br>LMC_USE_32BIT 1 |  |

|                       | vlog command: Include +incdir+\$LMC_HOME/sim/pli/src                        |  |

|                       | vsim command: Include -pli \$LMC_HOME/lib/linux.lib/swiftpli_mti.so         |  |

# **Enabling VMC Model Register Windows**

As described in "Viewing VMC Model Signals" on page 30, there are several internal registers signals of the PowerPC 405-S CPU VMC model that are available for viewing through register windows if you are using a Verilog simulator.

To view VMC model register window signals, you must explicitly enable the register windows as required for your simulation tool. In the PowerPC 405-S CPU Design View coreKit, the register windows are enabled by default using the following mechanisms:

• For VCS, the top-level testbench file (*<workspace>/sim/testbench/* p405s\_test\_top\_tb.v) includes the following line:

```

initial $swift_window_monitor_on("dut.PPC405D4")

```

The above line globally enables the register windows for the dut instance of PPC405F5V1\_soft in the testbench.

• For MTI-Verilog and NC-Verilog, each register window must be enabled individually. The simulator-specific SWIFT template file (*<workspace>/src/vmc/* p405s\_vmcmodel\_*<simulator>.v*) for each supported simulator includes a line in the following format for each register window:

\$lm\_monitor\_vec\_map(<register>, <instance\_path\_to\_vmc\_model>, "<window\_signal>");

For example:

```

initial

begin

$lm_monitor_vec_map(GPR0,dut.PPC405D4,"GPR0");

$lm_monitor_vec_map(GPR1,dut.PPC405D4,"GPR1");

$lm_monitor_vec_map(GPR2,dut.PPC405D4,"GPR2");

$lm_monitor_vec_map(GPR3,dut.PPC405D4,"GPR3");

$lm_monitor_vec_map(GPR4,dut.PPC405D4,"GPR4");

$lm_monitor_vec_map(GPR5,dut.PPC405D4,"GPR5");

$lm_monitor_vec_map(GPR6,dut.PPC405D4,"GPR6");

$lm_monitor_vec_map(GPR7,dut.PPC405D4,"GPR7");

$lm_monitor_vec_map(GPR8,dut.PPC405D4,"GPR8");

```

\$lm\_monitor\_vec\_map(GPR9,dut.PPC405D4,"GPR9");

end

To view the VMC model window signals, you must enable the register windows in a similar manner in your application-specific testbench.

# **Timing Model**

The Design View coreKit also includes a Stamp timing model that you can use to derive approximate timing numbers for an example PowerPC 405-S CPU implementation. The timing model is in the stamp\_model directory of your coreConsultant workspace for the Design View coreKit.

#### Jar Note-

The timing model provided with the Design View coreKit contains timing information only. It is not synthesizable and contains no functional logic.

The timing model files in *<workspace>/*stamp\_model are:

- PPC405F5V1.lib Library timing model

- PPC405F5V1\_constr.pt Timing exception file

# **5** Simulation – Advanced

This chapter provides additional information you can use for working with the testbench and simulation scripts, modifying the testbench, and running custom test programs. The topics are:

- Testbench Details

- Simulation Scripts

- Assembling Test Programs

# **Testbench Details**

The PowerPC 405-S CPU verification environment is intended as a starting point for a designer to evaluate, simulate, and start designing and writing software for a PowerPC 405-S CPU based system. The testbench for functional simulation (Figure 11) includes a VMC model for the PowerPC 405-S CPU core, functional models connected to the various interfaces of the PowerPC 405-S CPU, the IBM PLB Nebula arbiter and PLB slave model (both provided as VMC models), and a set of test programs that exercise different functional blocks and core interfaces. These test programs serve both as post-installation checks and as sample code for developing your own custom test programs.

#### Figure 11: Testbench Block Diagram

# **Vera Models**

The functional Vera models are memory mapped. Test programs control the Vera models by executing writes to the PLB slave/device control model, which, in turn, sends the appropriate commands to the Vera models through the control interface. The PLB slave model does not support the full set of PLB transactions that the PLB compliance checklist specifies. It only uses those transactions required to provide the necessary control functions for the Vera models.

Each Vera model has its own range of memory locations that are allocated as control registers. Controlling any model is then a matter of writing to specific locations in memory.

There are also two Vera blocks that serve as monitors: the DCR monitor and the PLB monitor. The DCR monitor checks transactions on the DCR bus and the PLB monitor checks transactions on the PLB.

The testbench execution flow logic resides partly in the PLB slave model and partly in the main Vera program for the testbench. The testbench execution flow logic performs the following functions:

- Parses test programs and loads them into the memory model.

- Starts the simulation by allowing the clock and reset logic to start.

- Stops the simulation when appropriate (test time-out, test pass, or test fail).

## **IBM PLB Models**

# **Vera Model Details**

The following sections provide more detail about the function of the Vera models used in the testbench.

# PLB Slave Model

The PLB slave model connects to the IBM PLB Nebula arbiter as a PLB 4.X slave that controls the execution of the testbench and other Vera models. It is essentially a memory controller that controls a memory space that maps other Vera models through a control interface and a pass/fail mechanism.

The control interface to the Vera models communicates CPU commands to the Vera models (JTAG, DCR, EIC). This is a simple interface that is synchronous to the main clock and consists of a 10-bit address bus, read and write commands (strobes), and 32-bit data-in and data-out buses. The entire address space of this interface is 1024 bytes and can be configured to reside in any 1024-byte boundary of the PLB memory space.

By default, this space is initially mapped to the address range 0x000000000 – 0x00000003FF in the PLB memory space. This can be changed by editing the p405s\_config.vrh configuration file (*<workspace>/sim/vera/src/p405s\_config.vrh*) and changing the SLAVE\_ADDR\_HI and SLAVE\_ADDR\_LO definitions. This configuration file also contains the locations of the memory-mapped registers of the other Vera models. The default values are listed in Table 9.

| Model                | Register         | Default Address | Address Parameter<br>Name |

|----------------------|------------------|-----------------|---------------------------|

| Interrupt Controller | Control Register | 0x0B0           | INTR_CTRL_REG             |

| Interrupt Controller | Data Register    | 0x0B4           | INTR_DATA_REG             |

| DCR                  | Control Register | 0x0F0           | DCR_BD_ADDR               |

| JTAG                 | Control Register | 0x030           | JTAG_CMD_REG              |

| JTAG                 | Data Register    | 0x040           | JTAG_DATA_REG             |

Table 9: Default PLB Addresses for Vera Models

By default, the pass/fail result of any test is posted at offset 0x010 of this address space. Pass is indicated by the value 0xC00DF00D, and fail by the value 0xDEADBEEF. Care should be taken so that this region does not overlap (in address decoding) with any other region(s) in the address space required by the program.

Note that program code and data reside in the IBM PLB slave model, not the Vera PLB slave model.

### **PLB Monitor**

The PLB monitor is connected to all the devices that are connected to the PLB Nebula arbiter. Its inputs are the PLB pins, both instruction-side and data-side PLB. Its single output is the *testbench\_terminate* signal. This signal allows the monitor to request a simulation termination of the main Vera program. Whenever an activity occurs on the bus, the monitor writes pertinent information from that activity into the *<testname>.*log file. The monitor also checks for protocol violations on the master PLB 3.X bus and slave PLB 4.X bus. When a protocol error occurs, the monitor writes error information to an error log file and stops simulation execution.

The PLB monitor checks all transactions occurring on all devices connected to the arbiter. These devices are the ICU read, DCU read, DCU write (masters that are part of the PowerPC 405-S CPU), and the PLB slave models. When other devices are connected to the arbiter, the monitor will also check the transactions of those devices.

The PLB monitor is coded such that when you replace the PLB model with real logic, the monitor can still serve as a valuable debugging tool. The functionality of the PLB monitor is based on the IBM PLB monitor.

### Instruction Side On Chip Memory(ISOCM) Model

The instruction side on-chip memory (ISOCM) model is connected to the ISOCM interface of PPC405-S core. The ISOCM model supports the ISOCM protocol specified in the "PPC405F5 Core Support Manual". The ISOCM model only supports the Single Cycle mode.

When a request is presented across the interface, the ISOCM model will respond in the next clock cycle

If the address is not in the ISOCM address space, the request is not serviceable by ISOCM model and it will respond with default values.

If the address is in the ISOCM address space, the request is serviceable but the ISOCM model and it will asserts the appropriate signals.

The ISOCM model by default supports the 1KB boundaries. The ISOCM Vera model by default is configured to be at address range 0x0000\_0400 to 0x0000\_07FF. These default values can be changed by editing the p405s\_config.vr configuration file and changing the ISOCM\_ADDR\_HI and ISOCM\_ADDR\_LO definitions.

Note: The Software must ensure the each instruction address has a single access path into the PPC405-S core for given software process.Each instruction address that is requested should be found in either the ISOCM address space or in instruction side PLB (ISPLB) space, but not in both.

# Data Side On Chip Memory (DSOCM) Model

The Data side on-chip memory (DSOCM) model is connected to the DSOCM interface of PPC405-S core. The DSOCM model supports the DSOCM protocol specified in the "PPC4055 Core Support Manual". The DSOCM model only supports the Single Cycle mode. Only two state pipeline is implemented in the DSOCM model for the Store Operations.

When a request is presented across the interface, the DSOCM model will responds in the next clock cycle

If the address is not in the DSOCM address space, the request is not serviceable by ISOCM model and it will respond with default values.

If the address is in the DSOCM address space, the request is serviceable by the ISOCM model and it will asserts the appropriate signals.