## THE UNIVERSITY OF TENNESSEE

# **HOMEWORK – USING ASSERTS -- Prof. Don Bouldin**

Purpose: Perform pre-synthesis simulation with *ModelSim* using Asserts.

#### Part B

Download: <a href="http://www.ece.utk.edu/~bouldin/protected/551-hw6b.tar.gz">http://www.ece.utk.edu/~bouldin/protected/551-hw6b.tar.gz</a>

Or copy the files on ada3.eecs.utk.edu:

- 1. cp ~bouldin/webhome/protected/551-hw6b.tar.gz .

- 2. gunzip 551-hw6b.tar.gz

- 3. tar -xvf 551-hw6b.tar

Now, move down to the subdirectory:

4. cd 551-hw6b

Now, perform pre-synthesis simulation by typing:

5. **./presynth\_sim**

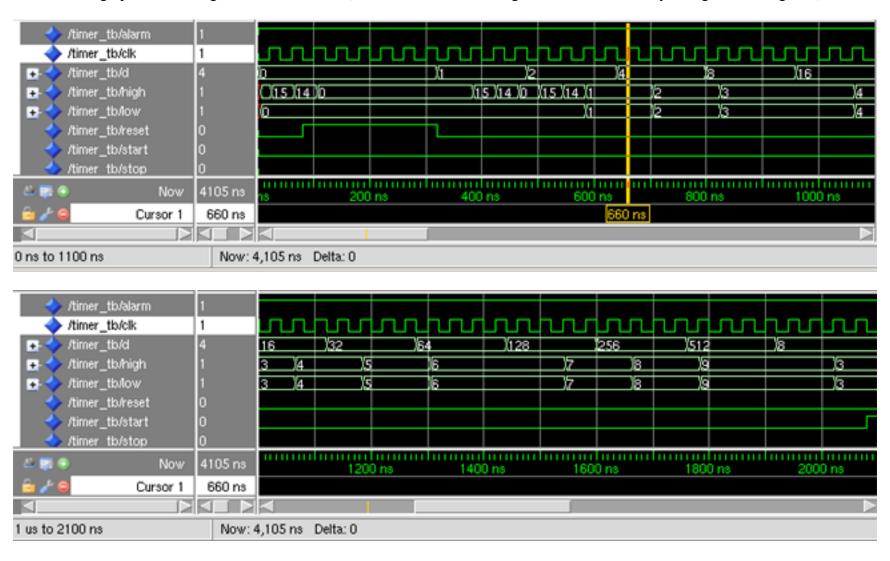

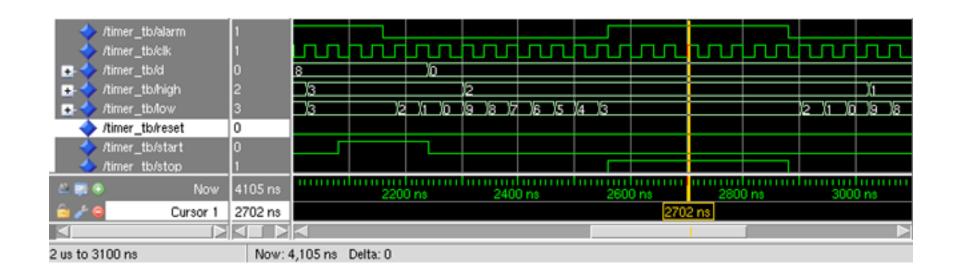

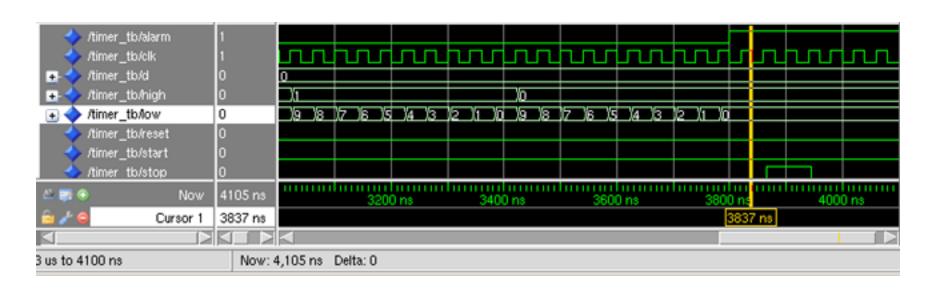

This will bring up the following waveform window (with the radix of "d", "high" and "low" manually changed to "unsigned"):

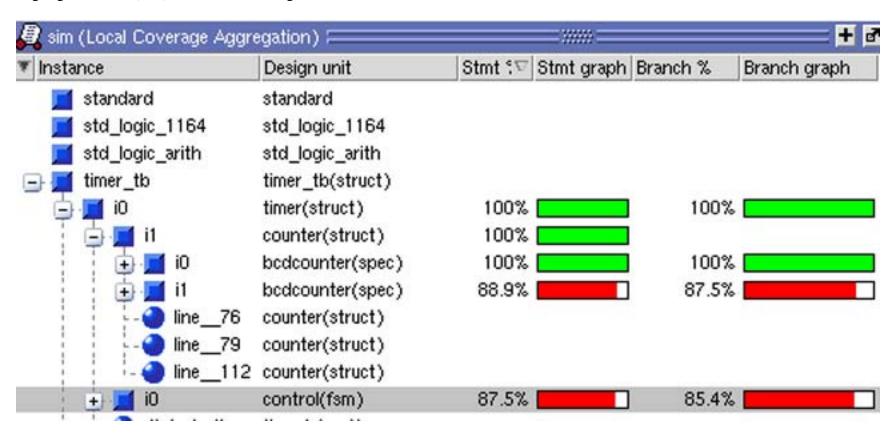

Highlight "control(fsm)" to see the coverage:

Highlight "control(fsm)" to see the statements missed:

Highlight "bcdcounter." to see the statements missed:

```

Missed Statements

- H bcdcounter.vhd

- X 45 ) THEN int_count := "1001" ;

```

The transcript window shows which "asserts" were printed:

```

Transcript F

1 - 🚅 🗐 🐾 🏐 📗

# Loading std.standard

# Loading ieee.std logic 1164(body)

# Loading ieee.std logic arith(body)

# Loading work.timer_tb(struct)#1

# Loading work.timer(struct)#1

# Loading work.control(fsm)#1

# Loading work.counter(struct)#1

# Loading work.bcdcounter(spec)#1

# Loading work.timer_tester(test)#1

# do stim.do

# .main pane.structure.interior.cs.body.struct

# ** Note: Count suspended correctly

# Time: 2720 ns Iteration: 0 Instance: /timer_tb/i1

# ** Note: Alarm asserted correctly

Time: 3865 ns. Iteration: 0. Instance: /timer_tb/i1

# ** Failure: timer test completed

Time: 4105 ns. Iteration: 0. Process: /timer_tb/i1/monitor_File: timer_tester.vhd

# Break in Process monitor at timer_tester.vhd line 111

# Simulation Breakpoint: Break in Process monitor at timer tester.vhd line 111

# MACRO ./stim.do PAUSED at line 3

VSIM(paused)>

```

Modify the testbench and the assert statements to achieve near 100% coverage with no missed statements and capture the new figures.

### presynth\_sim

#!/bin/csh -f

vlib work

vcom -cover bcescf -work work bcdcounter.vhd

vcom -cover bcescf -work work counter.vhd

vcom -cover bcescf -work work control.vhd

vcom -cover bcescf -work work timer.vhd

vcom -cover bcescf -work work timer\_tester.vhd

vcom -cover bcescf -work work timer\_tester.vhd

vcom -cover bcescf -work work timer\_tb.vhd

vsim -coverage -do stim.do timer\_tb

#### stim.do

view structure add wave \* run 5000