## **DESIGNING FPGAS & ASICS**

HDL

Prof. Don Bouldin, Ph.D.

#### **Electrical & Computer Engineering**

University of Tennessee TEL: (865)-974-5444 FAX: (865)-974-5483 dbouldin@tennessee.edu

## **COURSE OUTLINE**

- Overview of FPGAs and ASICs

- Using Synthesis

- HDL Examples

- Simulation and Testing

- Physical Place and Route

- Testing ASICs

- Component Reuse

## **TESTING ASICS**

- Functional Tests

- Manufacturing Tests

- Fault Coverage

- Test Pattern Generation

- Internal Scan

- Boundary Scan

- Built-In Self-Test

## **FUNCTIONAL TEST STIMULI**

- Functional test stimuli validate that the circuit exhibits the required <u>behavior</u> at the desired <u>speed</u>.

- It is too time-consuming to develop and to apply an exhaustive set of functional stimuli so usually the designer tests only <u>favorite</u> <u>cases</u> and <u>expected trouble spots</u> like overflow, etc.

- CAD tools to assist in this process generally take equations and generate 1's and 0's.

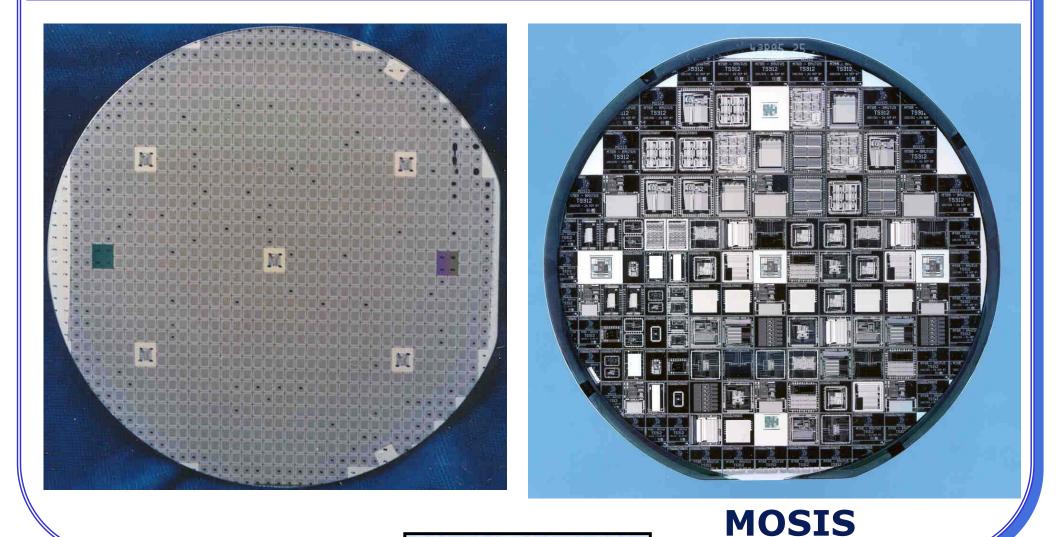

#### MANUFACTURING TEST STIMULI ARE NECESSARY BUT COSTLY

- Manufacturing has far less than 100% yield so each part must be tested to determine whether the circuit you desired was actually manufactured.

- First, known test structures are probed on the wafer to determine its acceptance.

- Then, each die on the wafer is probed and tested at d.c.

- Packaged parts are tested individually by the vendor at low speed (usually 1 MHz).

- The designer may then screen parts individually at full speed and under various environmental conditions.

#### SHARING MULTI-PROJECT MASKS AND WAFERS SAVES MONEY

#### MANUFACTURING TEST STIMULI AND FAULT COVERAGE

- Manufacturing test stimuli should provide sufficient coverage to achieve the <u>desired</u> <u>quality</u>.

- The more demanding the coverage, the fewer defective parts that will be shipped.

- Fault grading can be applied at the logic-level or at the MOS switch-level. Vendors encourage toggling of all logic nodes from 0 to 1 and 1 to 0 whether used or not.

- A minimum set of stimuli that can <u>detect</u> (not locate) faults is used for screening production parts to minimize time on the tester and its per-pin memory requirements.

### DEFECTIVE PARTS AS A FUNCTION OF FAULT COVERAGE PERCENTAGE

| <b>Defective Parts</b> | Fault Coverage |

|------------------------|----------------|

| 227                    | 50.00%         |

| 133                    | 90.00%         |

| 90                     | 99.00%         |

| 3                      | 99.99%         |

| Out of 10,000 Parts    |                |

Table 14.24, Page 795 ASICs by M. Smith © 1997 A-W-L, Inc. Used by permission.

#### GENERATING TEST STIMULI FOR LOGIC FAULT COVERAGE

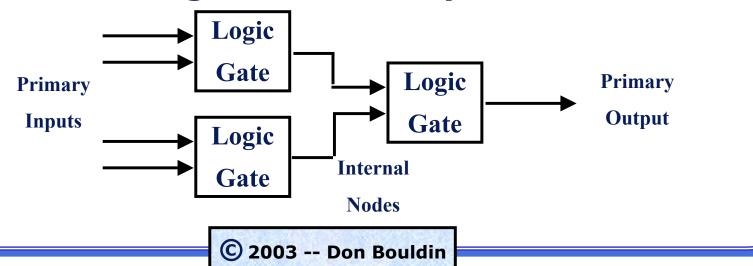

- Stimuli must be applied to primary inputs and cause the internal nodes to toggle. Responses must be observable from the primary outputs.

- Manufacturing test stimuli are generated <u>before</u> <u>fabrication</u> since the circuit can still be modified to enhance controllability and observability. This is called "design for testability".

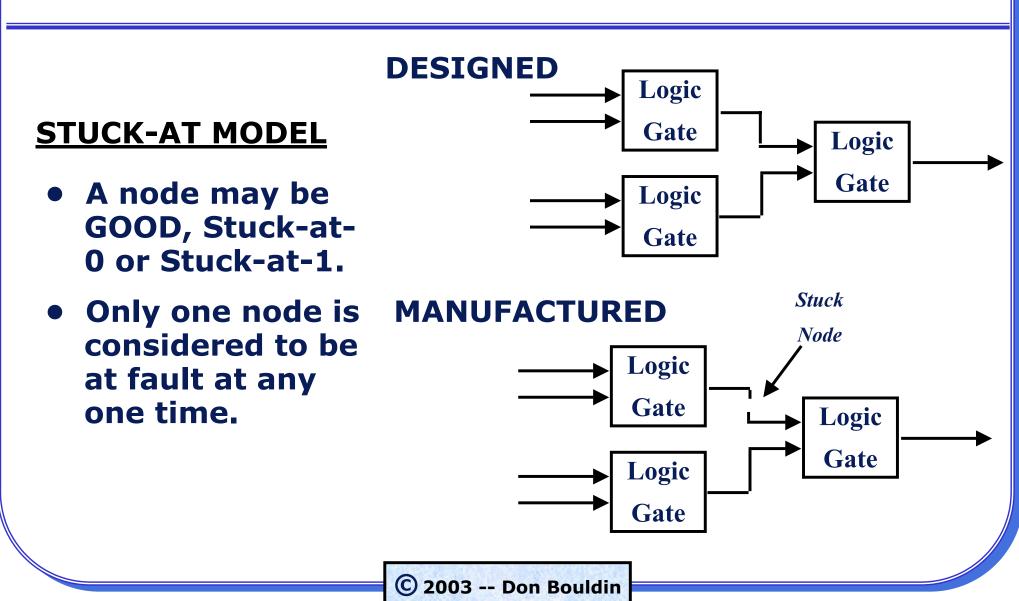

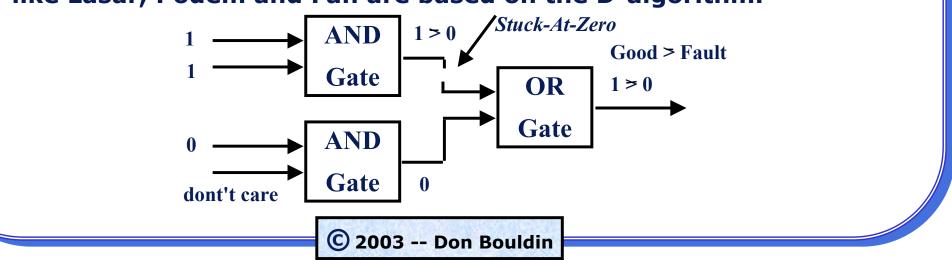

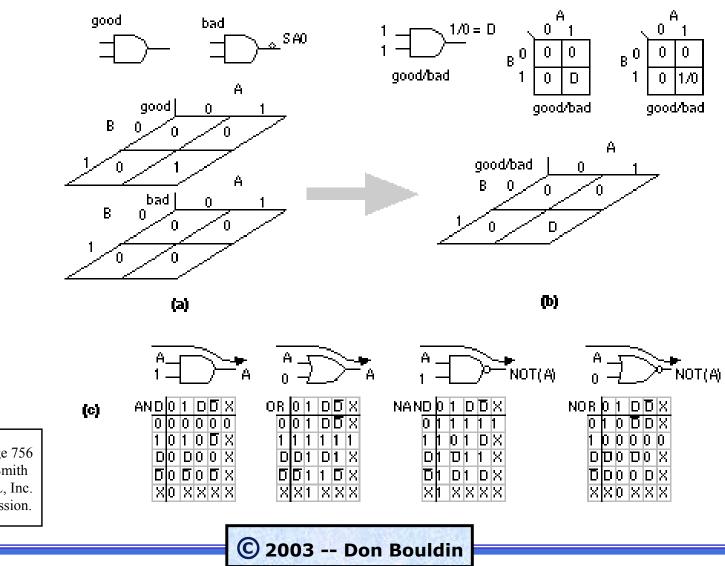

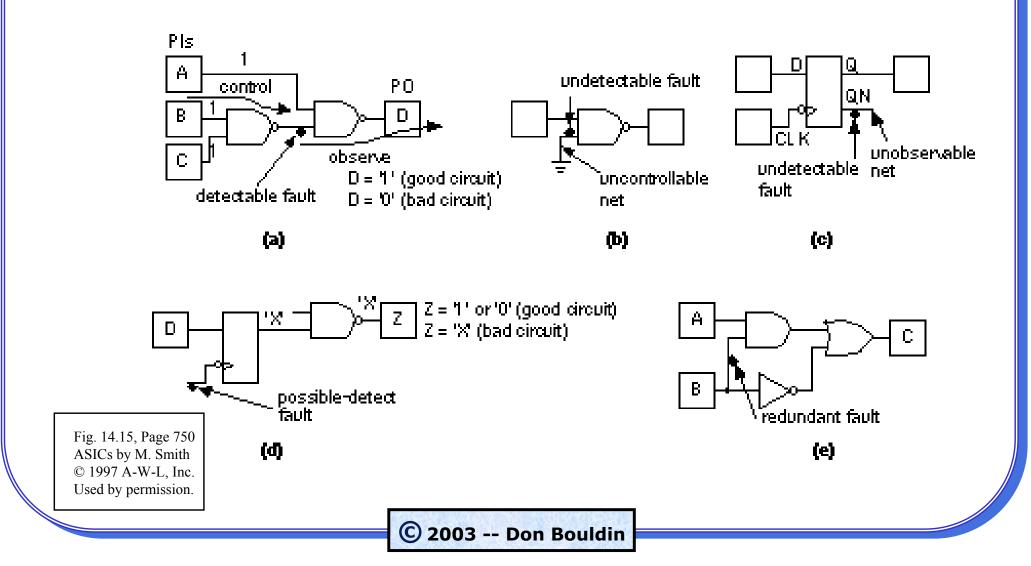

#### FAULT COVERAGE IS BASED ON THE STUCK-AT MODEL

## **DETECTION OF STUCK-AT FAULTS**

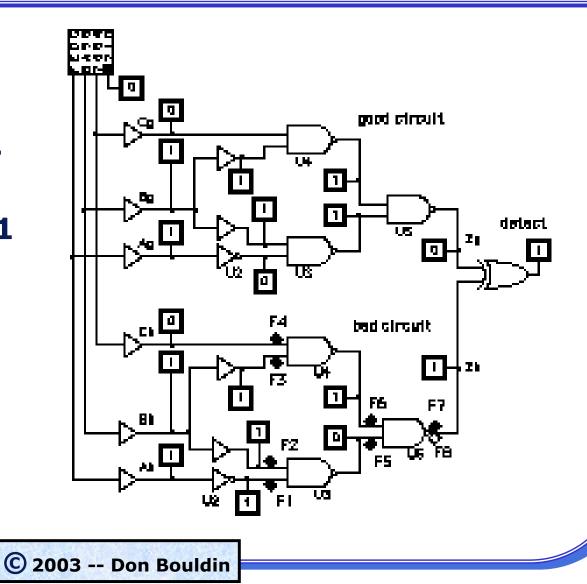

#### To detect whether F1 at the output of U2 is s-a-1, apply an input of C = 0, B =1 and A=1.

Fig. 14.16, Page 752 ASICs by M. Smith © 1997 A-W-L, Inc. Used by permission.

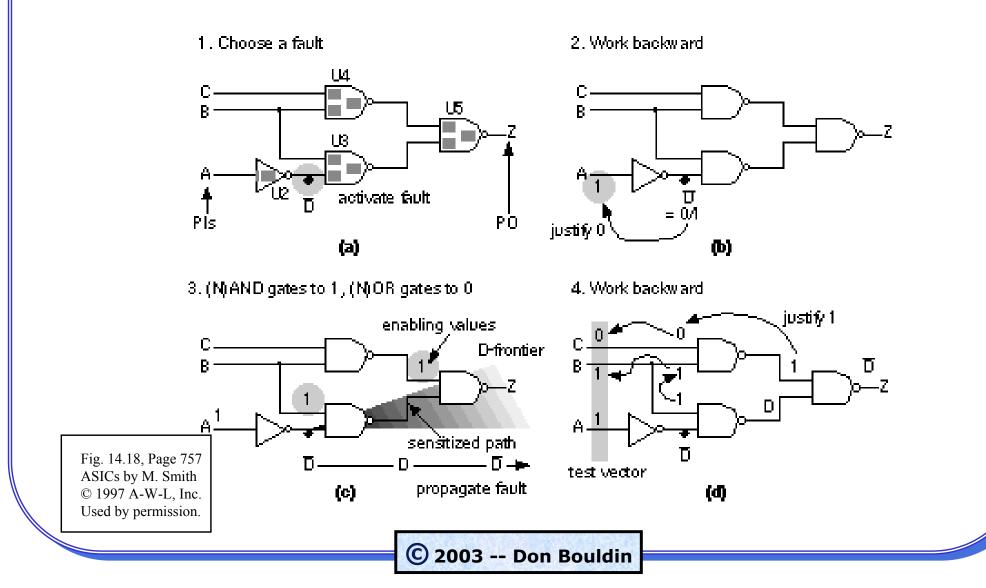

#### JUSTIFICATION AND PROPAGATION FOR FAULT DETECTION

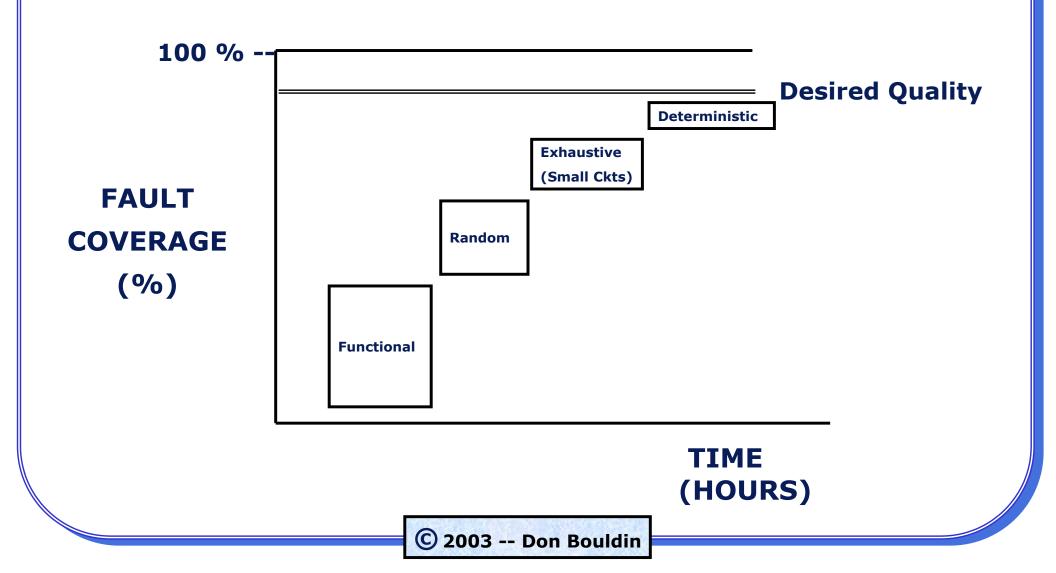

#### GENERATION OF TEST STIMULI FOR STUCK-AT FAULTS

- FUNCTIONAL--generated as a byproduct of verifying the intended operation.

- EXHAUSTIVE--too time-consuming for large, practical circuits but okay for small ones. Can use a counter to generate all possible 1's and 0's on the fly.

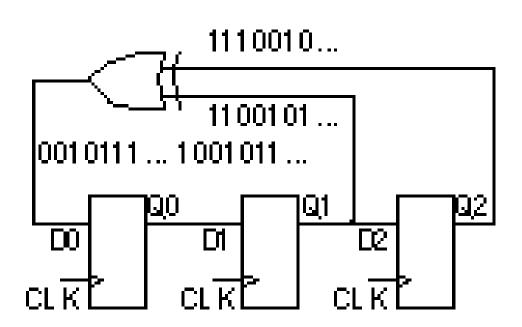

- RANDOM--easily generated on the fly using a linear feedback shift register.

- DETERMINISTIC--can be guaranteed to be generated if a test exists. However, this process may require substantial computing resources. Automatic Test Pattern Generator (ATPG) programs like Lasar, Podem and Fan are based on the D-algorithm.

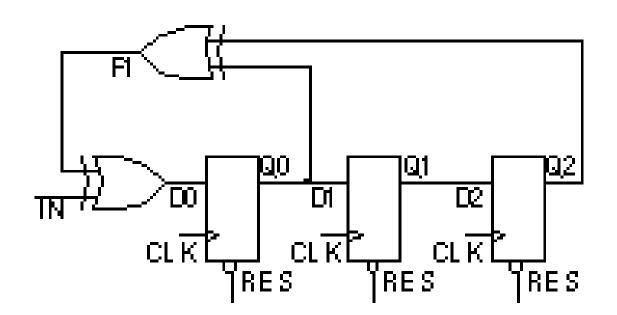

#### **RANDOM PATTERN GENERATION**

A Linear Feedback Shift Register (LFSR) can produce a Pseudo-Random Binary Sequence (PBRS).

Fig. 14.23, Page 766 ASICs by M. Smith © 1997 A-W-L, Inc. Used by permission.

#### STRATEGY FOR GENERATING TEST STIMULI

#### DETERMINISTIC ALGORITHM FOR DETECTING FAULTS

Fig. 14.17, Page 756 ASICs by M. Smith © 1997 A-W-L, Inc. Used by permission.

## CONTROLLABILITY AND OBSERVABILITY FOR FAULT DETECTION

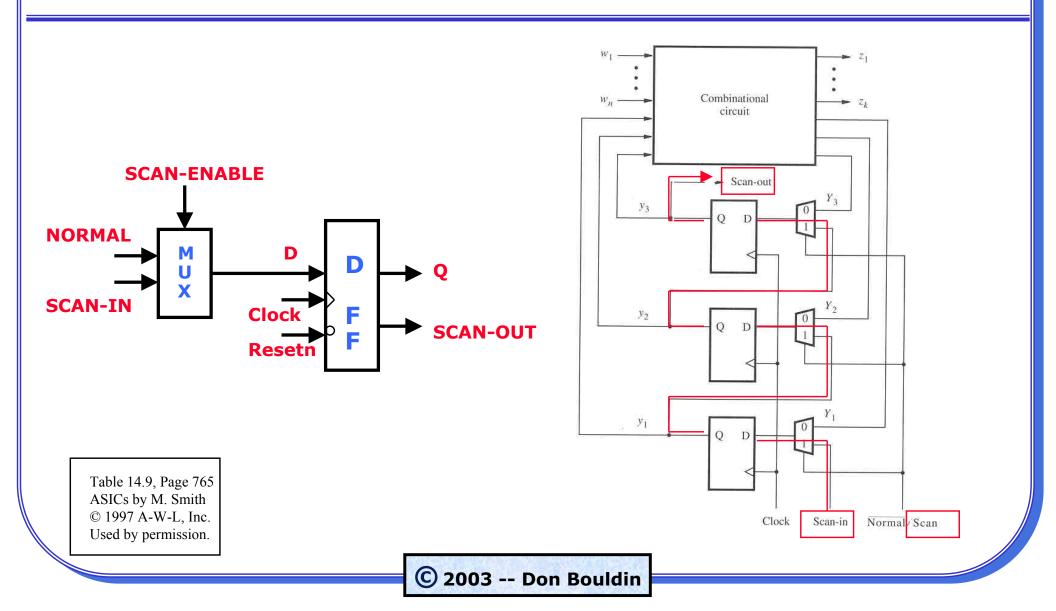

## MULTIPLEXED FLIP-FLOPS ARE USED FOR INTERNAL SCAN TESTING

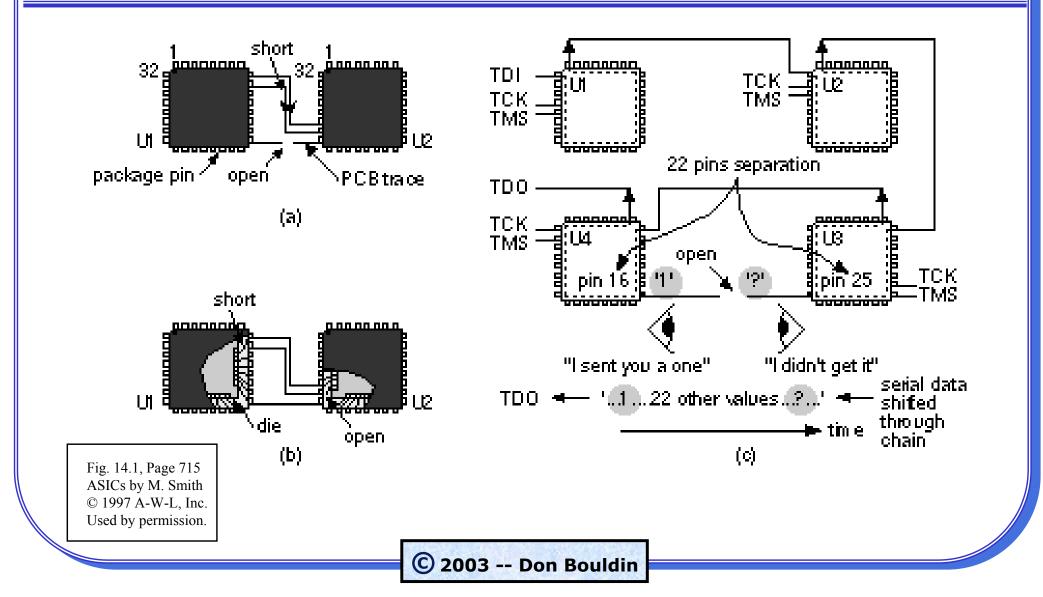

### **BOUNDARY SCAN CAN DETECT BOARD FAULTS AND PIN-POINT DEFECTIVE ICS**

## ADVANTAGES OF BOUNDARY SCAN TESTING

- Provides a standard protocol for invoking BIST in I.C.s after assembly onto P.C. boards.

- Allows I.C.s to be tested thoroughly in their complete, interconnected environment at any time during the life of the system.

- Provides standardized basis for thorough testing of all interconnect including system backplanes.

- Needs less expensive test equipment.

- Simplifies system-level diagnostic software.

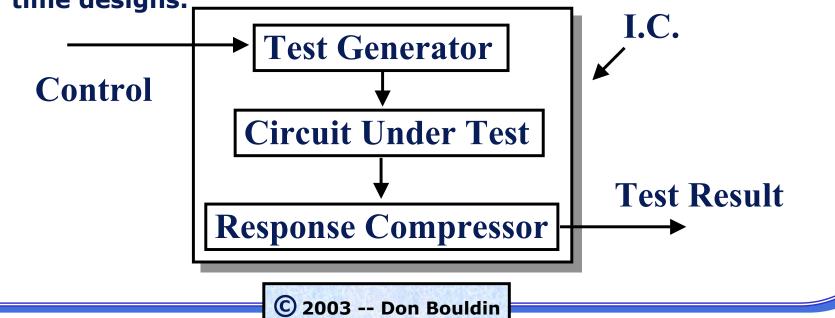

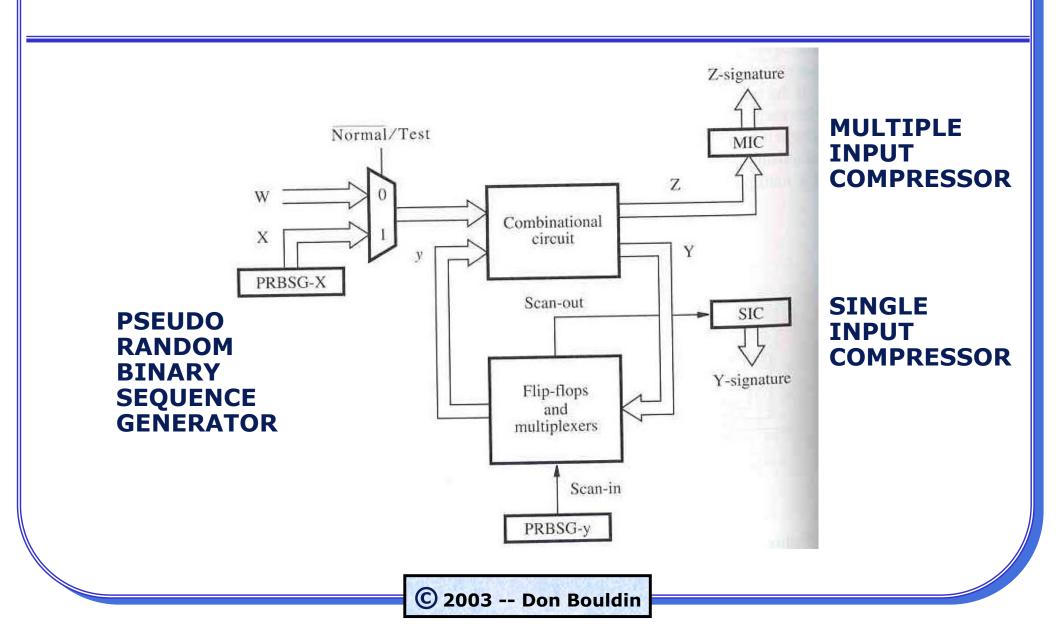

#### **ADVANTAGES OF BUILT-IN SELF-TEST**

- Eliminates the need to generate and apply a large set of test vectors externally via the I/O pins.

- Permits testing at speed under real-world conditions.

- Improves access to internal nodes.

- Assures that test issues are addressed early in the development cycle which results in higher quality, firsttime designs.

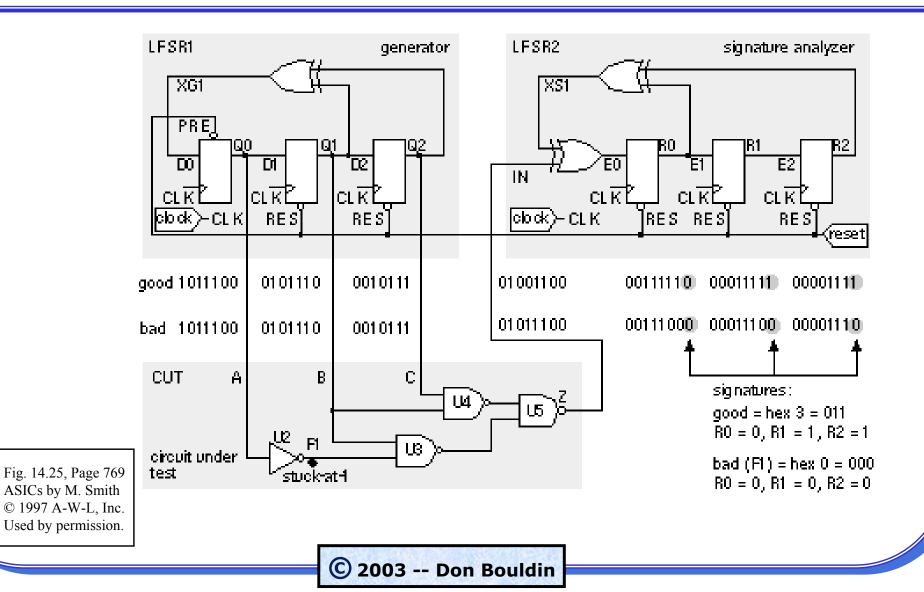

#### SINGLE-INPUT SIGNATURE COMPRESSOR

A Linear Feedback Shift Register (LFSR) can compress a serial input into a residual signature.

Fig. 14.24, Page 767 ASICs by M. Smith © 1997 A-W-L, Inc. Used by permission.

#### **BUILT-IN SELF-TEST (BIST)**

#### **BUILT-IN SELF-TEST (BIST)**

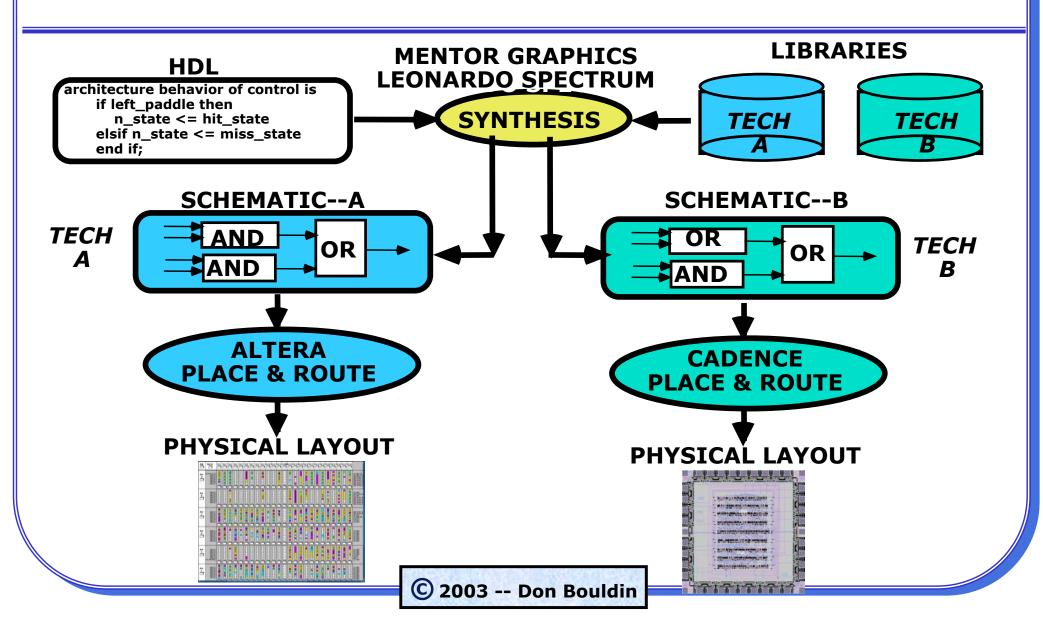

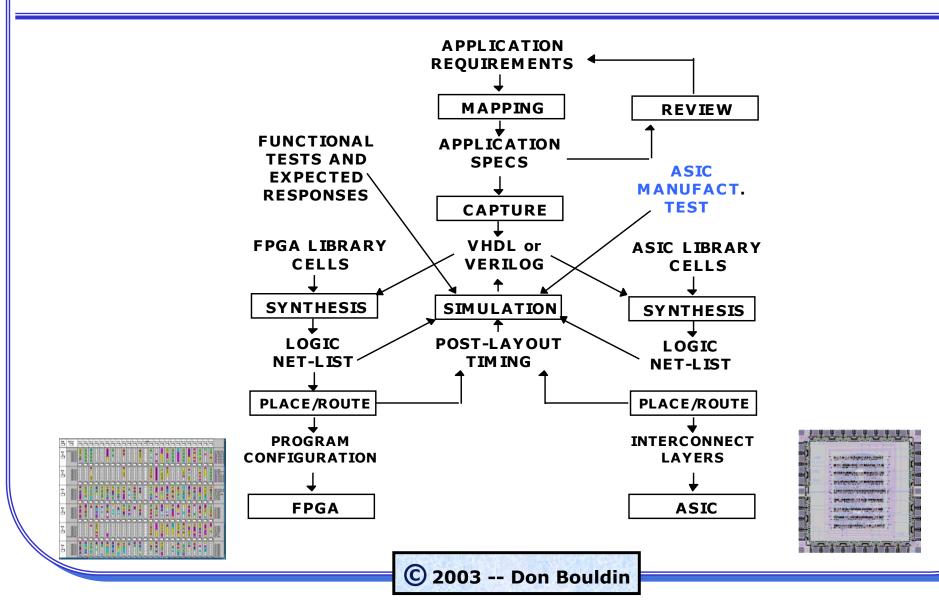

## DESIGN FLOW FOR FPGAS AND ASICS

## COMPARISON OF PRODUCT DEVELOPMENT

| <ul> <li><u>Design Stage</u></li> </ul>    | <u>FPGA (weeks)</u> | <u>ASIC (weeks)</u> |

|--------------------------------------------|---------------------|---------------------|

| <ul> <li>Design Specification</li> </ul>   | 1.0                 | 1.0                 |

| <ul> <li>Design Entry</li> </ul>           | 1.6                 | 1.6                 |

| <ul> <li>Functional Simulation</li> </ul>  | 2.4                 | 4.0                 |

| <ul> <li>Test Vector Generation</li> </ul> | า 0.0               | 6.4                 |

| • Vendor Interface                         | 0.0                 | 1.6                 |

| <ul> <li>Prototype Test</li> </ul>         | 1.6                 | 1.6                 |

| <ul> <li>Prototype Lead Time</li> </ul>    | 0.0                 | 2.0                 |

| <ul> <li>Production Lead Time</li> </ul>   | 0.0                 | 6.0                 |

| • Total Design Cycle                       | 7.0                 | 24.0                |

## **COMPARISON OF PRODUCT COSTS**

| • <u>EXPENSE</u>                          | <u>FPGA</u> | <u>ASIC</u> |

|-------------------------------------------|-------------|-------------|

| <ul> <li>Raw unprogrammed part</li> </ul> | 8.00        | 4.00        |

| <ul> <li>Design/Simulation</li> </ul>     | 3.15        | 7.92        |

| <ul> <li>Mfgr. Test Vectors</li> </ul>    | 0           | 2.88        |

| <ul> <li>Place/Route/Masks</li> </ul>     | 0           | 2.20        |

| • Final part                              | 11.15       | 17.00       |

**Costs in \$/part assuming quantity < 200,000 copies**

# HDL DESIGNS CAN BE TARGETED TO MULTIPLE LAYOUTS