## **Cadabra User Guide**

Version C-2009.09, September 2009

# **SYNOPSYS**<sup>®</sup>

### **Copyright Notice and Proprietary Information**

Copyright © 2009 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

| "This document is duplicated with the permission of S | ynopsys, Inc., for the exclusive use of |  |

|-------------------------------------------------------|-----------------------------------------|--|

|                                                       | and its employees. This is copy number" |  |

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### **Registered Trademarks (®)**

Synopsys, AMPS, Astro, Behavior Extracting Synthesis Technology, Cadabra, CATS, Certify, CHIPit, Design Compiler, DesignWare, Formality, HDL Analyst, HSIM, HSPICE, Identify, iN-Phase, Leda, MAST, ModelTools, NanoSim, OpenVera, PathMill, Physical Compiler, PrimeTime, SCOPE, Simply Better Results, SiVL, SNUG, SolvNet, Syndicated, Synplicity, the Synplicity logo, Synplify, Synplify Pro, Synthesis Constraints Optimization Environment, TetraMAX, UMRBus, VCS, Vera, and YIELDirector are registered trademarks of Synopsys, Inc.

#### Trademarks (™)

AFGen, Apollo, Astro-Rail, Astro-Xtalk, Aurora, AvanWaves, BEST, Columbia, Columbia-CE, Confirma, Cosmos, CosmosLE, CosmosScope, CRITIC, CustomExplorer, CustomSim, DC Expert, DC Professional, DC Ultra, Design Analyzer, Design Vision, DesignerHDL, DesignPower, DFTMAX, Direct Silicon Access, Discovery, Eclypse, Encore, EPIC, Galaxy, Galaxy Custom Designer, HANEX, HAPS, HapsTrak, HDL Compiler, Hercules, Hierarchical Optimization Technology, High-performance ASIC Prototyping System, HSIM<sup>plus</sup>, i-Virtual Stepper, IICE, in-Sync, iN-Tandem, Jupiter, Jupiter-DP, JupiterXT, JupiterXT-ASIC, Liberty, Libra-Passport, Library Compiler, Magellan, Mars, Mars-Rail, Mars-Xtalk, Milkyway, ModelSource, Module Compiler, MultiPoint, Physical Analyst, Planet, Planet-PL, Polaris, Power Compiler, Raphael, Saturn, Scirocco, Scirocco-i, Star-RCXT, Star-SimXT, System Compiler, System Designer, Taurus, TotalRecall, TSUPREM-4, VCS Express, VCSi, VHDL Compiler, VirSim, and VMC are trademarks of Synopsys, Inc.

#### Service Marks (sm)

MAP-in, SVP Café, and TAP-in are service marks of Synopsys, Inc.

SystemC is a trademark of the Open SystemC Initiative and is used under license. ARM and AMBA are registered trademarks of ARM Limited. Saber is a registered trademark of SabreMark Limited Partnership and is used under license. All other product or company names may be trademarks of their respective owners.

|    | Intended Audience                                              | xxi      |

|----|----------------------------------------------------------------|----------|

|    | Revision History                                               | xxi      |

|    | Conventions                                                    | xxii     |

|    | Related Publications                                           | xxiii    |

|    | Customer Support                                               | xxiii    |

| 1. | Introducing Cadabra                                            | 1        |

|    | Introduction to Cadabra Workflow                               | 3        |

|    | Working with Cadabra Workflow       Define Target Architecture | 3<br>3   |

|    | Build a technology                                             | 3        |

|    | Build an architecture.                                         | 4        |

|    | Initialize the Library                                         | 6        |

|    | Migrate and Create Cells                                       | 6        |

|    | Migrate cells                                                  | 7        |

|    | Create cells                                                   | 7<br>7   |

|    | Migrate and create cells                                       | 7        |

|    | Export the layouts                                             | 7        |

| 2. | Launching Cadabra                                              | 9        |

|    | Environment Variables                                          | 9        |

|    | Launching Options                                              | 11       |

|    | To launch Cadabra                                              | 12       |

| 3. | Setting Architectures                                          | 13       |

|    | Setting a Technology                                           | 16       |

|    | To create a new technology                                     | 17       |

|    | To open a technology                                           | 18<br>18 |

| Without an architecture                                                                                                                                                                            | 18                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| To open a Milkyway technology                                                                                                                                                                      | 19                   |

| To edit technology properties                                                                                                                                                                      | 19                   |

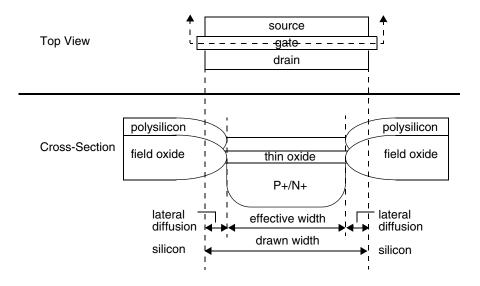

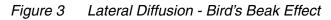

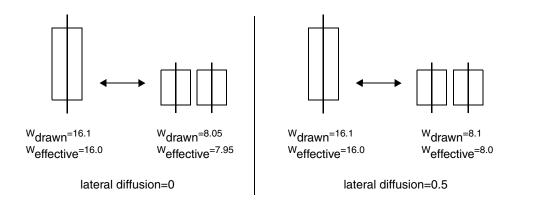

| Technology Properties Options<br>Lateral Diffusion<br>Why set this option?<br>Lateral Diffusion Option Details                                                                                     | 20<br>20<br>20<br>20 |

| To add a new layer                                                                                                                                                                                 | 22                   |

| To edit a layer                                                                                                                                                                                    | 22                   |

| Add/Edit Layer Options         Stipple         Why set this option?                                                                                                                                | 22<br>23<br>23       |

| To customize a layer color                                                                                                                                                                         | 24                   |

| To delete a layer                                                                                                                                                                                  | 25                   |

| Predefined Layers                                                                                                                                                                                  | 25                   |

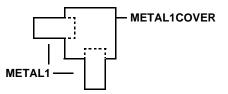

| Representative Layers    To set representative layers      To unset representative layers    To unset representative layers      To set the layer drawing order    To set the layer drawing order  | 26<br>27<br>27<br>28 |

| Design Rules                                                                                                                                                                                       | 29                   |

| Area Rule       To add an area design rule         To edit an area design rule       To edit an area design rule         Add/Edit Area Design Rule Options       Add/Edit Area Design Rule Options | 30<br>30<br>31<br>31 |

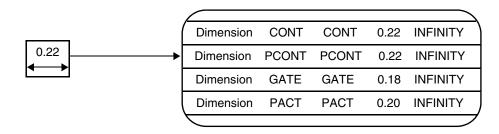

| Dimension Rule                                                                                                                                                                                     | 32<br>32<br>33       |

| Separation Rule       To add a separation design rule         To edit a separation design rule       Add/Edit Separation Design Rule Options                                                       | 34<br>34<br>35<br>35 |

| Overlap Rule<br>To add an overlap design rule<br>To edit an overlap design rule<br>Add/Edit Overlap Design Rule Options                                                                            | 36<br>37<br>37<br>38 |

| Enclosed Separation Rule                                | 38 |

|---------------------------------------------------------|----|

| To add an enclosed separation design rule               | 39 |

| To edit an enclosed separation design rule              | 39 |

| Add/Edit Enclosed Separation Design Rule Options        | 40 |

| Net Separation Rule                                     | 41 |

| To add a net separation design rule                     | 41 |

| To edit a net separation design rule                    | 42 |

| Add/Edit Net Separation Design Rule Options             | 42 |

| Extension Rule                                          | 43 |

| To add an extension design rule                         | 44 |

| To edit an extension design rule                        | 44 |

| Add/Edit Extension Design Rule Options                  | 45 |

| Contact Extension Rule                                  | 46 |

| To add a contact extension design rule                  | 47 |

| To edit a contact extension design rule                 | 47 |

| Add/Edit Contact Extension Design Rule Options          | 48 |

| Minimum Edge Length Rule                                | 49 |

| To add a minimum edge length design rule                | 49 |

| To edit a minimum edge length design rule               | 50 |

| Add/Edit Minimum Edge Length Design Rule Options        | 50 |

| Enclosed Area Rule                                      | 51 |

| To add an enclosed area design rule                     | 52 |

| To edit an enclosed area design rule                    | 52 |

| Add/Edit Enclosed Area Design Rule Options              | 53 |

| Concave Corner Edge Length Rule                         | 53 |

| To add a concave corner edge length design rule         | 54 |

| To edit a concave corner edge length design rule        | 54 |

| Add/Edit Concave Corner Edge Length Design Rule Options | 55 |

| Convex Corner Edge Length Rule                          | 55 |

| To add a convex corner edge length design rule          | 55 |

| To edit a convex corner edge length design rule         | 56 |

| Add/Edit Convex Corner Edge Length Design Rule Options  | 57 |

|                                                         | 57 |

| To add a connectivity design rule                       | 58 |

| To edit a connectivity design rule                      | 58 |

| Add/Edit Connectivity Design Rule Options               | 58 |

| Net Avoidance Rule                                            | 59 |

|---------------------------------------------------------------|----|

| To add a net avoidance design rule                            | 59 |

| To edit a net avoidance design rule                           | 60 |

| Add/Edit Net Avoidance Design Rule Options                    | 60 |

| Avoidance Rule                                                | 60 |

|                                                               | 61 |

| To edit an avoidance design rule                              | 61 |

| Add/Edit Avoidance Design Rule Options                        | 62 |

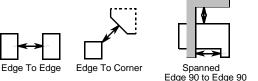

| Spanned Edge Rule                                             | 62 |

| Radial Distance at Corners Rule                               | 62 |

| Minimum/Maximum Bend Length Rule                              | 63 |

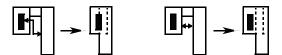

| Gate-to-Gate Separation                                       | 63 |

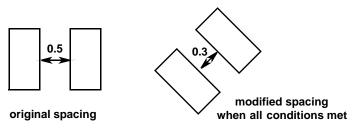

| Preferred Rule                                                | 64 |

| Why set this option?                                          | 65 |

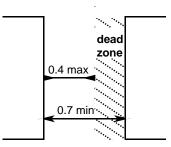

| Dead Zone Interval                                            | 65 |

| To filter design rules for viewing                            | 66 |

| To sort design rules for viewing                              | 67 |

| To delete a design rule                                       | 67 |

| Design Rule Conditions                                        | 67 |

| Simple Condition                                              | 68 |

| Configuration Conditions                                      | 68 |

| Orientation Conditions                                        | 69 |

| To add a simple design rule condition                         | 69 |

| To edit a simple design rule condition                        | 70 |

| Add/Edit Simple Condition Options                             | 70 |

| Common Run Condition.                                         | 71 |

| To add a common run design rule condition                     | 71 |

| To edit a common run design rule condition                    | 72 |

| Add/Edit Common Run Condition Options                         | 72 |

| Width Dependent Condition                                     | 73 |

| To add a width-dependent design rule condition                | 74 |

| To edit a width-dependent design rule condition               | 74 |

| Add/Edit Width Dependent Condition Options                    | 75 |

| Common Run and Width Dependent Condition                      | 75 |

| To add a common run and width-dependent design rule condition | 76 |

| To edit a common run width-dependent design rule condition Add/Edit Common Run and Width Dependent Condition Options                                                              | 77<br>77                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| To delete a design rule condition                                                                                                                                                 | 78                               |

| To verify a technology                                                                                                                                                            | 78                               |

| Verification Conditions                                                                                                                                                           | 78                               |

| To view a technology report                                                                                                                                                       | 79                               |

| To save a technology                                                                                                                                                              | 79                               |

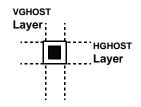

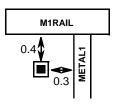

| Optimizing Your Technology.Asymmetrical Extension RulesNegative Net Separation RulesNegative Spanned Edge RulesRules on Ghost Layers.Different LayersRules for Wells and Implants | 80<br>80<br>81<br>81<br>82<br>82 |

| Setting an Architecture. Architecture Exploration Editing the Technology                                                                                                          | 83<br>84<br>85                   |

| Using the Architecture Builder                                                                                                                                                    | 85                               |

| To create a new architecture                                                                                                                                                      | 86                               |

| To open an architecture                                                                                                                                                           | 87                               |

| To rename an architecture                                                                                                                                                         | 87                               |

| To set the active path for the architecture                                                                                                                                       | 88                               |

| Setting Cell Architecture                                                                                                                                                         | 88                               |

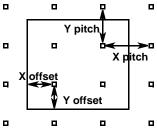

| IO Grid<br>To add the IO grid<br>IO Grid Options<br>Pitch<br>Offset                                                                                                               | 90<br>91<br>91<br>91<br>92       |

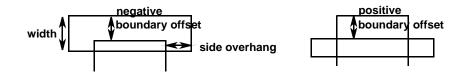

| Boundary                                                                                                                                                                          | 92                               |

| To add the boundary                                                                                                                                                               | 92                               |

| Boundary Options                                                                                                                                                                  | 93                               |

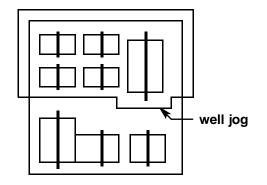

| N-Well                                                                                                                                                                            | 93                               |

| To add the N-well                                                                                                                                                                 | 93                               |

| N-Well Options                                                                                                                                                                    | 94<br>95                         |

| Power Rail                          | 95  |

|-------------------------------------|-----|

| To add a power rail                 | 96  |

| Power Rail Options                  | 97  |

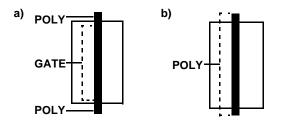

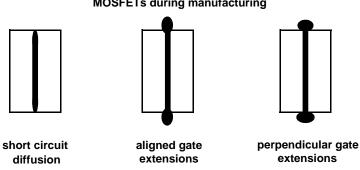

| MOSFET                              | 97  |

| To add a MOSFET                     | 98  |

| MOSFET Options                      | 98  |

| General tab.                        | 99  |

| Gate Characteristics tab.           | 100 |

| Gate Extensions tab                 | 101 |

| Wire                                | 102 |

| To add a wire                       | 102 |

| Wire Options                        | 103 |

| Contact.                            | 104 |

| To add a contact                    | 104 |

|                                     | 104 |

| Contact Options                     |     |

| Port                                | 106 |

| To add a port                       | 106 |

| Port Options                        | 107 |

| Diode                               | 108 |

| To add a diode                      | 108 |

| Diode Options                       | 109 |

|                                     |     |

| Reserved Track                      | 109 |

| To add a reserved track             | 109 |

| Reserved Track Options              | 110 |

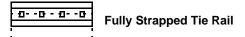

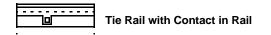

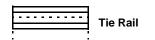

| Well and Substrate Tie              | 110 |

| To add a well/substrate tie         | 111 |

| Tie Strategy Options                | 112 |

| Required Rules for Tie Strategies   | 115 |

| Implants                            | 120 |

| To add implants                     | 120 |

|                                     | 121 |

| Implant Options                     | 121 |

| P-Implant and N-Implant tabs        | 121 |

| Diode Implant tab                   | 121 |

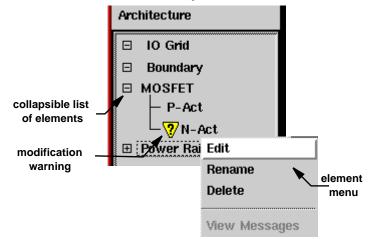

| Architecture Status.                | 122 |

|                                     |     |

| To view element messages            | 122 |

| Working with Architectural Elements | 123 |

| To edit an architectural element                                                                                                                                 | 124                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| To rename an architectural element                                                                                                                               | 124                      |

| To delete an architectural element                                                                                                                               | 125                      |

| Architecture Details                                                                                                                                             | 125                      |

| Architecture Details: Properties                                                                                                                                 | 127                      |

| Architecture Details: Functions                                                                                                                                  | 128                      |

| Architecture Details: Layout Style Rules         To add a new Layout Style Rule         To edit an existing Layout Style Rule         Layout Style Rules Options | 129<br>129<br>129<br>130 |

| To integrate custom AL files                                                                                                                                     | 130                      |

| To manage design steps, callbacks, and exporters                                                                                                                 | 131                      |

| To manage design steps:                                                                                                                                          | 132                      |

| To manage callbacks:                                                                                                                                             | 132                      |

| To manage exporters:                                                                                                                                             | 132                      |

| Setting Layout Options                                                                                                                                           | 133                      |

| To set the optimization goal                                                                                                                                     | 133                      |

| Working with Placement Styles                                                                                                                                    | 133                      |

| To set placement style                                                                                                                                           | 134                      |

| Placement Style Options                                                                                                                                          | 134                      |

| General tab.                                                                                                                                                     | 134                      |

| Vertical Conditioning tab.                                                                                                                                       | 138                      |

| Working with Routing Styles                                                                                                                                      | 138                      |

| To set routing style                                                                                                                                             | 138                      |

| Routing Style Options                                                                                                                                            | 139<br>139               |

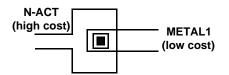

| Power Costs tab                                                                                                                                                  | 139                      |

| Contact/Port Costs tab                                                                                                                                           | 139                      |

| Scenarios tab                                                                                                                                                    | 140                      |

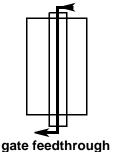

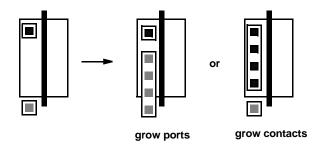

| Gate Feedthroughs tab                                                                                                                                            | 142                      |

| Penalties tab                                                                                                                                                    | 143                      |

| Working with Compaction Styles                                                                                                                                   | 144                      |

| To set compaction style                                                                                                                                          | 144                      |

| Compaction Style Options                                                                                                                                         | 144                      |

| Layout Style tab                                                                                                                                                 | 144<br>146               |

| Objectives tab                                                                                                                                                   | 140                      |

| Preservation Options tab                                                                                                                                         | 147                      |

| Layer Based Align Edges Tab                                                                                                                                      | 149                      |

|    | Relaxation Styles Tab                                                                                                                                                                       | 150                                           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|    | Working with Electromigration Styles.         To set electromigration style.         Electromigration Style Options.                                                                        | 151<br>151<br>152                             |

|    | Working with Text Annotation<br>To set text annotation<br>Text Annotation Options<br>Ports tab<br>Rails tab<br>Cell Name tab.                                                               | 153<br>153<br>153<br>153<br>154<br>154        |

|    | To set path layers                                                                                                                                                                          | 155                                           |

|    | Working with Measurement Metrics       To set measurement metrics         Measurement Metrics       Measurement Metrics                                                                     | 155<br>155<br>156                             |

|    | Working with Importers                                                                                                                                                                      | 156<br>157<br>157<br>157<br>158<br>158        |

|    | Working with Exporters         To set the exporter         Export Options         Export GDSII         Export OpenAccess         Export Milkyway         Export Netlist         Export Plib | 158<br>159<br>159<br>160<br>160<br>160<br>161 |

|    | To save an architecture                                                                                                                                                                     | 162                                           |

| 4. | Initializing Libraries                                                                                                                                                                      | 163                                           |

|    | To set the active path for the library                                                                                                                                                      | 164                                           |

|    | To create a new library                                                                                                                                                                     | 164                                           |

|    | To open a library                                                                                                                                                                           | 165                                           |

|    | To update a library                                                                                                                                                                         | 167                                           |

| To save a library                                               | 167                      |

|-----------------------------------------------------------------|--------------------------|

| Library File Structure                                          | 168                      |

| To close a library                                              | 170                      |

| To add cells                                                    | 170                      |

| To convert SPICE to AL                                          | 171                      |

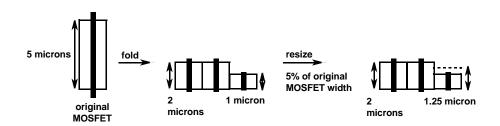

| SPICE to AL Options<br>Unfold MOSFETs<br>Why set this option?   | 171<br>172<br>173<br>173 |

| Also Set                                                        | 173                      |

| Why set this option?         To set a mapping:         Also Set | 173<br>173<br>173        |

| Nets                                                            | 174                      |

| Why set this option?                                            | 174<br>174               |

| Scale MOSFET sizes                                              | 174                      |

| Why set this option?                                            | 174<br>174               |

| To convert SPICE to AL from a terminal window                   | 175                      |

| Command Options                                                 | 176                      |

| About access modes                                              | 178<br>179               |

| To copy a cell                                                  | 180                      |

| To rename a cell                                                | 181                      |

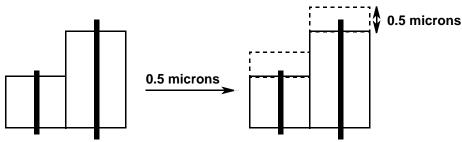

| To scale a cell                                                 | 182                      |

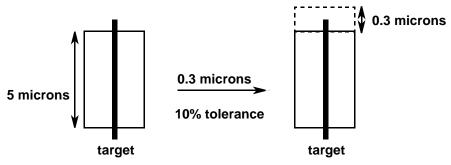

| To change cell height                                           | 183                      |

| To save a cell                                                  | 183                      |

| To delete a cell                                                | 184                      |

| To add source layouts                                           | 184                      |

| Read-in Layouts Options                                         | 185                      |

| To rename a source layout                                       | 186                      |

| To remove a source layout                                       | 186                      |

| To map cells to source layouts                                  | 187<br>187               |

| Using Auto-Map                           | 187 |

|------------------------------------------|-----|

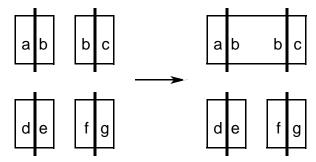

| Mapping Cells to Source Layouts.         | 188 |

| Edit Cell-to-Layout Mapping Options      | 188 |

| To change a cell-to-layout mapping       | 189 |

| To remove a cell-to-layout mapping       | 190 |

| To get a netlist description             | 190 |

| To export a description file             | 191 |

| Cell Modifiers                           | 192 |

| To create a cell modifier                | 193 |

| To add cell modifiers                    | 194 |

| To associate cell modifiers              | 195 |

| To edit a cell modifier                  | 195 |

| Customizing a Cell Modifier              | 197 |

| Reference Settings                       | 197 |

| Reference Cells                          | 198 |

| Reference Clones                         | 199 |

| To automatically set cell references     | 200 |

| To manually set clone or cell references | 201 |

| Set Reference Options                    | 201 |

| Reference Clones                         | 201 |

| Reference Cells                          | 202 |

| To remove a clone or cell reference      | 203 |

| Cell Properties                          | 203 |

| Built-in Cell Properties                 | 204 |

| Cell Optimality                          | 208 |

| Cell Status                              | 208 |

| Job Status                               | 209 |

| To add a cell property                   | 210 |

| To edit a cell property                  | 210 |

| Add/Edit Property Options                | 211 |

| To show or hide a cell property          | 211 |

|    | To save display settings                                                                                                                         | 212                      |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|    | To delete a cell property                                                                                                                        | 212                      |

|    | To import cell properties                                                                                                                        | 212                      |

|    | Import Cell Properties Options                                                                                                                   | 213                      |

|    | Cell Properties Input File                                                                                                                       | 213                      |

|    | To export cell properties.                                                                                                                       | 214                      |

| 5. | Migrating Libraries and Creating Cells                                                                                                           | 215                      |

|    | Migration Prerequisites                                                                                                                          | 216                      |

|    | To run Migrate-ATL                                                                                                                               | 218                      |

|    | Migrate-ATL Options                                                                                                                              | 218                      |

|    | To run Migrate GDS                                                                                                                               | 219                      |

|    | Migrate GDS Options                                                                                                                              | 220                      |

|    | To run ATL                                                                                                                                       | 220                      |

|    | ATL Options                                                                                                                                      | 221                      |

|    | To run Import                                                                                                                                    | 222                      |

|    | Import Options                                                                                                                                   | 222                      |

|    | To place a cell                                                                                                                                  | 223                      |

|    | Place Options                                                                                                                                    | 224                      |

|    | Customizing Options for Placing Cells<br>customFilterDesignPoints.al File<br>customAddSizeBasedCost.al File<br>customAddRoutingBasedCost.al File | 224<br>224<br>225<br>225 |

|    | To route a cell                                                                                                                                  | 226                      |

|    | Route Options                                                                                                                                    | 227                      |

|    | Customizing Routing of CellscellRouterPenalties.al File                                                                                          | 228<br>228               |

|    | To compact a cell                                                                                                                                | 230                      |

|    | Compact Options                                                                                                                                  | 231                      |

|    | To finalize a layout                                                                                                                             | 232                      |

|    | Finalize Options                                                                                                                                 | 232                      |

|    | To measure cell optimality                                                                                                                       | 233                      |

-----

| To export a cell, netlist, or clone             | 233        |

|-------------------------------------------------|------------|

| To export multiple cells to a single GDSII file | 235        |

| Export Options                                  | 236        |

| Clone                                           | 236        |

| GDSII                                           | 236        |

| OpenAccess                                      | 237        |

| Milkyway                                        | 237        |

| Netlist                                         | 237        |

| PLib                                            | 238        |

| To export from the Cell Browser.                | 238        |

| Export from the Cell Browser Options            | 239        |

| Clone                                           | 239        |

| GDSII                                           | 239        |

|                                                 | 240<br>240 |

| Milkyway<br>Netlist                             | 240<br>240 |

| PLib                                            | 240        |

| ECO Migration                                   | 241        |

| Advanced Operations                             | 242        |

| To import a layout.                             | 244        |

|                                                 |            |

| Import Layout Options                           | 244        |

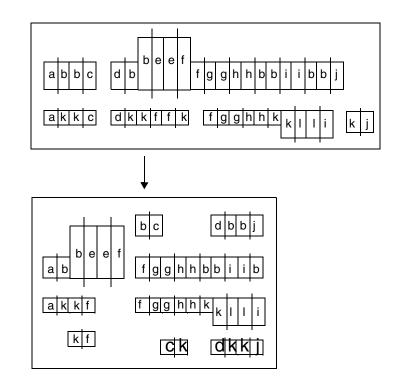

| To fold MOSFETs                                 | 245        |

| Fold MOSFETs Options                            | 246        |

| Selectors                                       | 247        |

| Operators                                       | 248        |

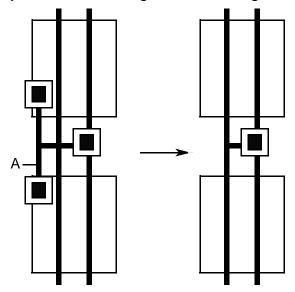

| Principal vs. Secondary MOSFETs                 | 253        |

| Example                                         | 254        |

| To extract hierarchy                            | 254        |

| Extract Hierarchy Options                       | 255        |

| To select a configuration                       | 259        |

| To edit a configuration                         | 260        |

| To fold tiles                                   | 260        |

| Fold Tiles Options                              | 261        |

| To merge tiles                                  | 261        |

| Merge Tiles Options                                  | 262        |

|------------------------------------------------------|------------|

| To place tiles                                       | 262        |

| Place Tiles Options                                  | 263        |

| To optimize a placement                              | 265        |

| Optimize Placement Options                           | 267        |

| To align MOSFETs                                     | 269        |

| Align MOSFETs Options                                | 270<br>271 |

|                                                      | 271        |

| To generate compaction geometries                    | 272        |

| To use the Cell Compact design step                  | 273        |

| Compaction Options                                   | 274        |

| To set the constraints to be relaxed                 | 280        |

| To create a combined objective                       | 281        |

| Configure Objective Options                          | 282        |

| To generate routing geometries                       | 283        |

| To generate a layout.                                | 284        |

| To use the Connect Tie Rail design step              | 284        |

| To use the Update Boundary design step               | 285        |

| To use the Prepare Abutments design step             | 285        |

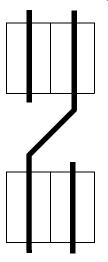

| To use the Add Multiple Gate Bends design step       | 285        |

| To use the Jog at Gates design step                  | 286        |

| To use the Jog Wires Around Contacts design step     | 286        |

| To use the Match MOSFET Sizes design step            | 287        |

| To use the Optimize Horizontal Wires design step     | 287        |

| To use the Selectively Pregrow Diffusion design step | 287        |

| To use the Add Layout Ties design step               | 288        |

| To use the Add Implants design step                  | 288        |

| To use the Fill Notches design step                  | 289        |

| To use the Merge Shapes design step                  | 289        |

| To use the Reshape Gates design step                 | 289        |

|    | To use the Adjust Overlapping Tie Diffusions design step                                                           | 290               |

|----|--------------------------------------------------------------------------------------------------------------------|-------------------|

|    | To use the Path Shapes design step                                                                                 | 290               |

|    | To use the Text Annotation design step                                                                             | 291               |

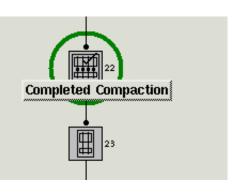

|    | Compaction Browser                                                                                                 | 291               |

|    | Browsing Compaction Constraints<br>Device Edge Details<br>Constraint Details                                       | 292<br>292<br>293 |

|    | To browse compaction constraints                                                                                   | 294               |

|    | To filter constraints                                                                                              | 295               |

|    | Browsing Compaction Objectives Objective Details                                                                   | 295<br>296        |

|    | To browse compaction objectives                                                                                    | 296               |

|    | Viewing the Critical Path                                                                                          | 297               |

|    | To view the critical path                                                                                          | 297               |

|    | Viewing Infeasibilities                                                                                            | 298               |

|    | To view infeasibilities                                                                                            | 298               |

|    | Submitting Jobs                                                                                                    | 299               |

|    | To submit jobs<br>To submit jobs from the Cadabra window<br>To submit jobs from the Cell View or Cell Edit windows | 300<br>300<br>301 |

|    | To submit a job on a design point                                                                                  | 302               |

|    | Job Scheduler Options                                                                                              | 303               |

|    | LSF Scheduler Configuration Options                                                                                | 306               |

|    | SGE Configuration Options                                                                                          | 308               |

|    | To clear job status                                                                                                | 308               |

|    | To terminate jobs                                                                                                  | 309               |

| 6. | Viewing Results                                                                                                    | 311               |

|    | Cadabra Window                                                                                                     | 312               |

|    | Library Statistics                                                                                                 | 313               |

|    | To view library statistics                                                                                         | 314               |

|    | Cell Browser.                                                                                                      | 315               |

| To open a cell                                                             | 316               |

|----------------------------------------------------------------------------|-------------------|

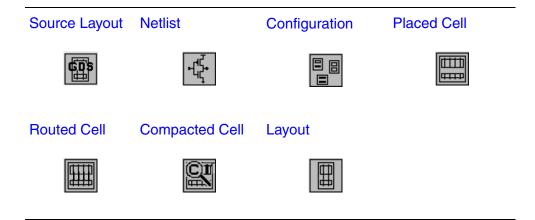

| Design Steps                                                               | 317               |

| Design Points                                                              | 317               |

| Source Layout Design Point                                                 | 318               |

| Netlist Design Point                                                       | 318               |

| Configuration Design Point                                                 | 319               |

| Placed Cell Design Point                                                   | 320               |

| Routed Cell Design Point                                                   | 321               |

| Compacted Cell Design Point                                                | 322               |

| Layout Design Point                                                        | 323               |

| To open a design point                                                     | 324               |

| To view multiple design points                                             | 325               |

| To delete a design point                                                   | 325               |

| To prune the design tree                                                   | 326               |

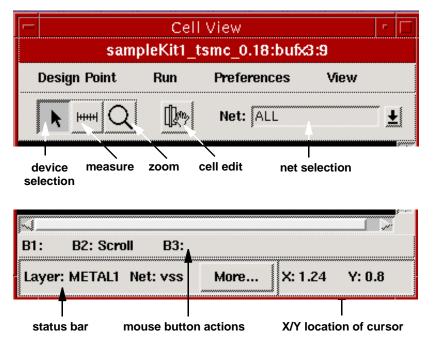

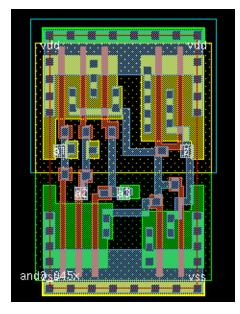

| Cell View Window                                                           | 326               |

| View Window                                                                | 328<br>329        |

| To view or compare design points                                           | 330               |

| To view or compare source layouts                                          | 331               |

| To compare a design point to a source layout                               | 331               |

| To compare a design point to an optimal layout                             | 332               |

| To compare a design point to a reference layout                            | 333               |

| To export a clone from the Cell View window                                | 334               |

| Export Clone Options                                                       | 336               |

| Clone View Window                                                          | 336               |

| To view a clone                                                            | 337               |

| To view text labels                                                        | 337               |

| Design Point Tags<br>Standard Design Point Tags<br>Using Design Point Tags | 338<br>338<br>339 |

| To tag a design point                                                      | 339               |

-

|    | To remove design point tags                      | 340 |

|----|--------------------------------------------------|-----|

|    | Cell Marker                                      | 341 |

|    | To mark a layout                                 | 341 |

|    | To print a layout                                | 342 |

|    | Print Options                                    | 342 |

|    | To zoom in the Compaction Browser                | 342 |

|    |                                                  |     |

| 7. | Hand-Editing Layouts                             | 345 |

|    | To hand-edit a layout                            | 346 |

|    | Editing Devices                                  | 347 |

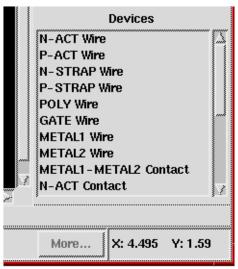

|    | To add a device                                  | 348 |

|    | To add a wire device                             | 349 |

|    | To change layers                                 | 350 |

|    | Modified Routing Geometries                      | 351 |

|    | To update routing geometries                     | 351 |

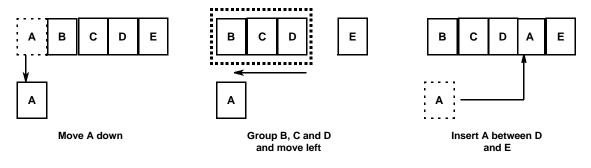

|    | Group Editing                                    | 352 |

|    | To group devices                                 | 352 |

|    | To modify device properties                      | 353 |

|    | To move a device                                 | 353 |

|    | To reshape a device                              | 354 |

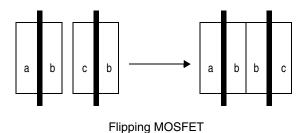

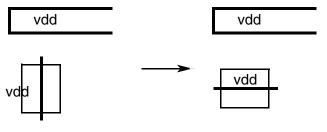

|    | To flip a device                                 | 354 |

|    | To rotate a device                               | 355 |

|    | To rip up a device                               | 356 |

|    | To make a device unrippable                      | 356 |

|    | To merge MOSFETs                                 | 357 |

|    | To fold MOSFETs                                  | 358 |

|    | To unfold MOSFETs.                               | 358 |

|    | Fold/Unfold MOSFETs Options                      | 359 |

|    | To resize MOSFETs                                | 360 |

|    | Resize MOSFETs Options                           | 361 |

|    | To resize wires, contact covers, and port covers | 364 |

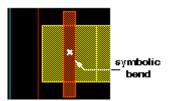

| To add a gate bend               | 365 |

|----------------------------------|-----|

| To move a gate bend              | 366 |

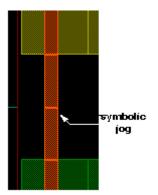

| To add a wire jog                | 366 |

| Allowing 45 <sup>0</sup> wires   | 367 |

| Snapping Devices to a Grid       | 368 |

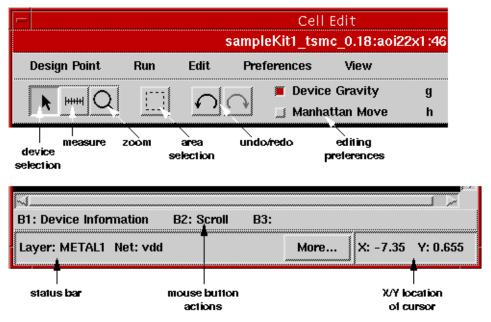

| Device Gravity                   | 368 |

| Manhattan Move                   | 369 |

| Show Detailed Routing Geometries | 369 |

| To delete a device               | 370 |

| To export a clone                | 370 |

| To clone part of a layout        | 371 |

| Export Clone Options             | 373 |

| To zoom                          | 374 |

| Using the Zoom Button            | 374 |

| Using the View menu              | 374 |

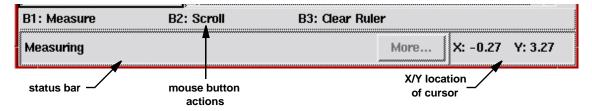

| To measure on the canvas         | 374 |

| Measuring to the Nearest Edge    | 375 |

| Measuring 45 <sup>0</sup> Angles | 376 |

| Measuring Delta X/Y              | 377 |

| Snapping Ruler to a Grid         | 377 |

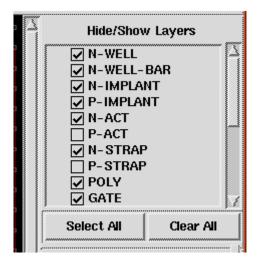

| To show/hide layers              | 377 |

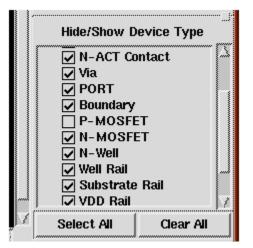

| To show/hide device types        | 378 |

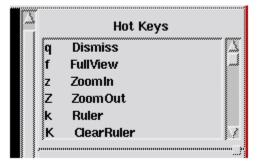

| To view a list of hot keys       | 379 |

| To view a list of nets           | 380 |

| To view a list of devices        | 380 |

| To view unrouted nets            | 380 |

| To annotate nets                 | 382 |

| To view the I/O Grid             | 382 |

| To view device information       | 382 |

| To show routing conflicts        | 383 |

| Glossary | 385 |

|----------|-----|

| Index    | 405 |

This manual provides task-based instructions for working with Cadabra.

The following sections in this chapter provide a guide to this manual, as well as the other documents that comprise Cadabra's documentation suite.

### **Intended Audience**

In order to address the manuals to the correct audience, the roles of the users of Cadabra is defined as follows:

Design Engineer

This role covers users who design standard cell libraries. Design engineers should be extensively familiar with layout design and SPICE netlists.

CAD Administrator

This role covers users who install and administer Cadabra. CAD administrators should be competent with and have requisite privileges for performing administrative tasks, such as installation, administration, and configuration, on UNIX systems.

This manual is intended for design engineers.

### **Revision History**

This section contains a history of this document's revision history:

| Revision Date  | Description                                            |

|----------------|--------------------------------------------------------|

| September 2009 | Initial publication of document for Cadabra C-2009.09. |

### Conventions

The following conventions are used in Synopsys documentation.

| Convention  | Description                                                                                                                                                                                                           |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Courier     | Indicates command syntax.                                                                                                                                                                                             |  |

| Italic      | Indicates a user-defined value, such as object_name.                                                                                                                                                                  |  |

| Purple      | <ul> <li>Within an example, indicates information of special interest.</li> <li>Within a command-syntax section, indicates a default value, such as: <ul> <li>include_enclosing = true   false</li> </ul> </li> </ul> |  |

| Bold        | <ul> <li>Within syntax and examples, indicates user input—text you type verbatim.</li> <li>Indicates a graphical user interface (GUI) element that has an action associated with it.</li> </ul>                       |  |

| []          | Denotes optional parameters, such as:<br>write_file [-f <i>filename</i> ]                                                                                                                                             |  |

|             | Indicates that parameters can be repeated as many times as necessary:<br>pin1 pin2 pinN                                                                                                                               |  |

| Ι           | Indicates a choice among alternatives, such as<br>low   medium   high                                                                                                                                                 |  |

| ١           | Indicates a continuation of a command line.                                                                                                                                                                           |  |

| /           | Indicates levels of directory structure.                                                                                                                                                                              |  |

| Edit > Copy | Indicates a path to a menu command, such as opening the Edit menu and choosing Copy.                                                                                                                                  |  |

| Ctrl+C      | Indicates a keyboard combination, such as holding down the Ctrl key and pressing the C key.                                                                                                                           |  |

### **Related Publications**

For additional information about Cadabra, see

- The documentation installed with the Cadabra software and available through the Cadabra Help menu

- The Cadabra Release Notes, available on SolvNet (see Accessing SolvNet)

- Documentation on the Web, which provides HTML and PDF documents and is available on SolvNet (see Accessing SolvNet)

You might also want to refer to the documentation for the following related Synopsys products:

- Synopsys Common Licensing

- Milkyway

### **Customer Support**

Customer support is available through SolvNet online customer support and through contacting the Synopsys Technical Support Center.

### **Accessing SolvNet**

SolvNet includes an electronic knowledge base of technical articles and answers to frequently asked questions about Synopsys tools. SolvNet also gives you access to a wide range of Synopsys online services, which include downloading software, viewing Documentation on the Web, and entering a call to the Support Center.

To access SolvNet:

- 1. Go to the SolvNet Web page at http://solvnet.synopsys.com.

- 2. If prompted, enter your user name and password. (If you do not have a Synopsys user name and password, follow the instructions to register with SolvNet.)

If you need help using SolvNet, click Help on the SolvNet menu bar.

### **Contacting the Synopsys Technical Support Center**

If you have problems, questions, or suggestions, you can contact the Synopsys Technical Support Center in the following ways:

- Open a call to your local support center from the Web by going to http://solvnet.synopsys.com/EnterACall (Synopsys user name and password required).

- Send an e-mail message to your local support center.

- E-mail support\_center@synopsys.com from within North America.

- Find other local support center e-mail addresses at http://www.synopsys.com/support/support\_ctr.

- Telephone your local support center.

- Call (800) 245-8005 from within the continental United States.

- Call (650) 584-4200 from Canada.

- Find other local support center telephone numbers at http://www.synopsys.com/support/support\_ctr.

Describes the basic concepts of Cadabra, and introduces you to the overall Cadabra workflow.

Cadabra provides an automated solution for migrating and creating custom standard cell layouts. Cadabra allows you to migrate custom standard cell libraries to new process technologies, transistor sizes, or architectures, and create LVS and DRC correct cell layouts.

Cadabra provides three main automated processes: Migrate-GDS, ATL (Automated Transistor Layout), and Migrate-ATL.

| Automated Process | Description                                                                                                                                                          |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

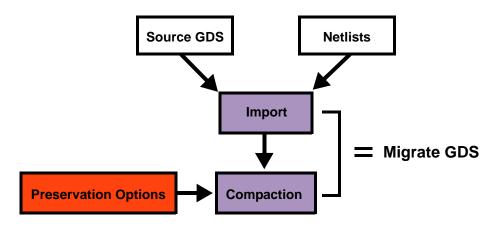

| Migrate-GDS       | Using cell netlists, GDSII files, and a target architecture and technology as input, Migrate GDS imports, compacts, finalizes, and exports cell layouts in one step. |  |

| ATL               | Using cell netlists and an architecture and technology as input,<br>ATL places, routes, compacts, finalizes, and exports cell layouts<br>in one step.                |  |

| Automated Process | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Migrate-ATL       | Using cell netlists, GDSII files, and a target architecture and<br>technology as input, Migrate-ATL combines the functionality of<br>Migrate GDS and ATL in one step. Migrate-ATL runs the Migrate<br>GDS process first, then based on your specifications, runs ATL<br>ATL can always be run, or run only on those cells that fail<br>migration, or are sub-optimal after migration.                                                                                      |  |

|                   | The Migrate-ATL process should be used if:                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                   | <ul> <li>The source layouts for some cells in a library are not compatible with the target architecture and/or cell netlists.</li> <li>The Migrate GDS process on its own provides sub-optimal confeasible results.</li> <li>You want to compare a migration methodology to an ATL methodology.</li> <li>Cadabra also allows you to run the individual steps of each automated process (import, place, route, compact, finalize, and export) for finer control.</li> </ul> |  |

|                   | All three processes allow you to view the results as the layouts<br>are generated. Cadabra also provides the functionality for han-<br>editing layouts individually.                                                                                                                                                                                                                                                                                                       |  |

|                   | Cadabra has an easy-to-use graphical user interface (GUI).<br>Advanced users also have the option of using Cadabra's own<br>Application Language (AL) to run the tool.                                                                                                                                                                                                                                                                                                     |  |

|                   | Cadabra provides the Generic Portfolio, which contains a set of<br>built-in files that are the foundation for creating cell architecture<br>in any process. You can use the provided templates and<br>customize the property values. Cadabra's Architecture Builder<br>can be used to configure and register devices, custom design<br>steps, callbacks, and exporters that are contained within the<br>Generic Portfolio.                                                 |  |

|                   | Migration refers to converting existing GDSII layouts to new GDSII layouts by mapping the original layout to new technolog process rules or architectures. Migration applies to GDSII formatted libraries only.                                                                                                                                                                                                                                                            |  |

- This section covers the following topics:

- Introduction to Cadabra Workflow

- Working with Cadabra Workflow

### Introduction to Cadabra Workflow

Using Cadabra to migrate and/or create cell layouts involves three stages: defining the target architecture, initializing the library, and migrating and/or creating the cells. Defining the architecture requires entering the design rules for your target technology and specifying the cell architecture and layout options for your target architecture. Initializing the library requires adding cell netlists. If using migration, you must also add GDSII layouts and map them to the netlists. Migrating and/or creating the cells requires running one of three processes: Migrate GDS, Automated Transistor Layout (ATL), or Migrate-ATL.

Cadabra automatically migrates and/or creates a final layout and displays cell completion and quality data. The cells can then be saved as a Cadabra-formatted library or exported to GDSII files.

### Working with Cadabra Workflow

When working with Cadabra, Synopsys recommends the following workflow:

- Define Target Architecture

- Initialize the Library

- Migrate and Create Cells

### **Define Target Architecture**

This section covers the following topics:

- Build a technology

- Build an architecture

### **Build a technology**

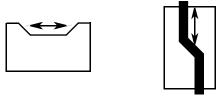

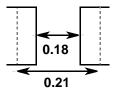

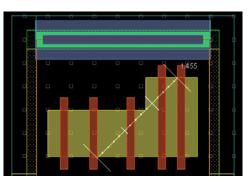

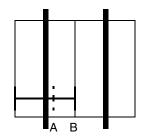

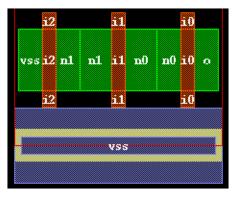

Build a target technology by setting up your layers and process design rules through the Technology Builder. The physical and electrical design rules govern the behavior of the layout features. Cadabra's Technology Builder provides an easy-to-use graphical user interface for entering your design rules.

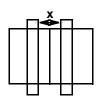

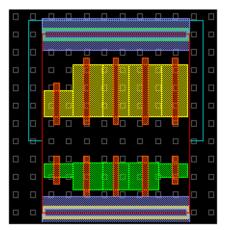

Figure 1 Sample Technology Builder Interface

**Note:** You can use the PLAN utility to define the technology and architecture. This allows you to explore architectures without acquiring a synthesis license.

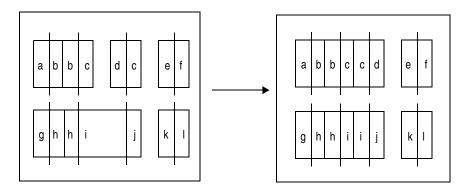

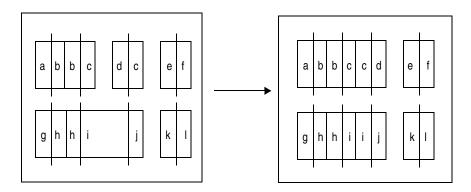

### **Build an architecture**

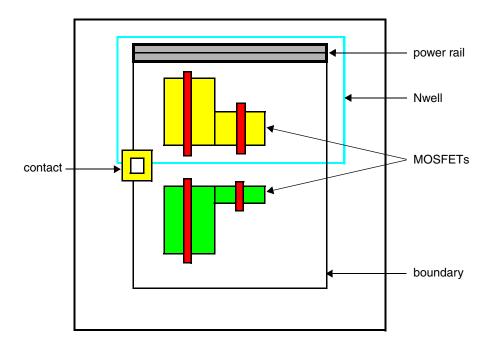

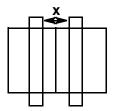

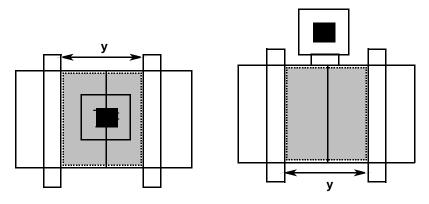

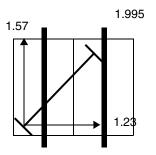

Build an architecture by setting up your cell architecture elements, layout styles, importer and exporter options through the Architecture Builder. The architecture is based on your technology, which can be edited and exported into the architecture with any late changes. The architecture describes the behavior of the devices in the layout and the style preferences for cell migration and creation.

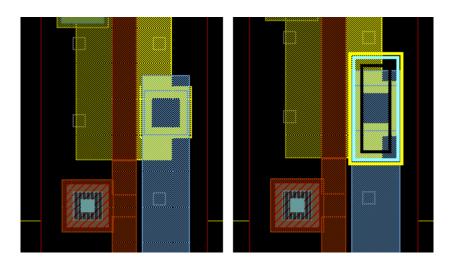

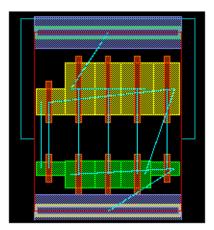

The Architecture Builder provides graphical feedback of the cell architecture by displaying a view of the layout features (such as the position of the well, the cell boundary size, the position of power rails, or the shape of various contacts).

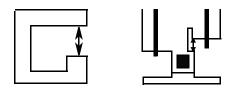

Figure 2 Sample Architecture Builder Interface

All cells in a library are based on the same architecture.

### **Initialize the Library**

From the Cadabra main window, create an empty library file based on a target architecture file. Then add the cells to the library, either individually by entering a netlist filename, or as a set by specifying a directory which contains all the netlists for the cells to be added.

If you are migrating a library, input a GDSII formatted cell library file and add the GDSII layouts that are to be mapped to the cells. Layouts can be added individually, or as a set by specifying the directory in which the GDSII files reside. Finally, map the cells to their corresponding GDSII layouts.

Note: More than one cell can be mapped to the same GDSII layout. However, a cell can only be mapped to one layout at any given time.

| cada                                                                                                                 | Edit Cell-to-Layout Mapping r<br>cadabra1_tsmc_0.13 |  |

|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| ell/Layout Mapping                                                                                                   |                                                     |  |

| Cell                                                                                                                 | Source Layout                                       |  |

| an2d1                                                                                                                | an2d1                                               |  |

| an2d2                                                                                                                | an2d2                                               |  |

| an2d3                                                                                                                | an2d3                                               |  |

| an2d4                                                                                                                | an2d4                                               |  |

| an2d5                                                                                                                | an2d5                                               |  |

| an3d1                                                                                                                | an3d1                                               |  |

| an3d2                                                                                                                | an3d2                                               |  |

| an3d3                                                                                                                | an3d3                                               |  |

| an3d4                                                                                                                | an3d4                                               |  |

| an3d5                                                                                                                | an3d5                                               |  |

| an4d1                                                                                                                | an4d1                                               |  |

| an4d2                                                                                                                | an4d2                                               |  |

| an4d3                                                                                                                | an4d3                                               |  |

| an5d1                                                                                                                | an5d1                                               |  |

| Auto - Map                                                                                                           | Clear All                                           |  |

| to-Map Criteria<br>Map all cells<br>Map cells with no mapp<br>Atch <cell> to <source la<="" th=""/><th>-</th></cell> | -                                                   |  |

| Prefix Pos                                                                                                           | tfix                                                |  |

| Prefix Pos                                                                                                           |                                                     |  |

|                                                                                                                      | Mite Mapping To File ng Reset To Default Mapping    |  |

### **Migrate and Create Cells**

This section covers the following topics:

- Migrate cells

- Create cells

- Migrate and create cells

- View the results

- Export the layouts

### Migrate cells

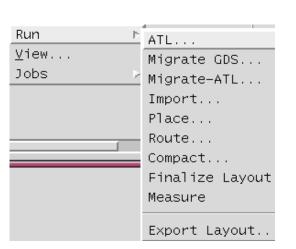

Run the cells through the entire migration flow by selecting the Migrate GDS process or its individual steps (Import, Compact, and Finalize Layout) by selecting each process separately.

### Create cells

Run the cells through the automated transistor layout flow by selecting ATL or its individual steps (Place, Route, Compact, and Finalize Layout) by selecting each process separately.

### Migrate and create cells

Run the cells through the entire migration and automated transistor layout flows by selecting Migrate-ATL. Depending on your specifications, ATL may not always be run.

Multiple users can access and work on cells in the same library simultaneously. Locks on individual cells prevent any user conflict.

#### View the results