# **ProGenesis Guide**

11.20.07

Prolific, Inc. 39899 Balentine Drive Suite 380 Newark CA 94560

510/252-0490 www.prolificinc.com

# **Table of Contents**

Notices 1

Usage 2

Getting Started With ProGenesis 3

ProGenesis Tool Overview 6

ProGenesis Tutorial Overview 10

Library Construction Guide 31

Folding Control FAQ 39

Navigating ProTech 44

Setting Up A Technology Area 110

ProTech FAQ 113

ProGen Guide 114

Expeditions 204

ProGen FAQ 213

ProGenesis Design for Manufacturability 216

ProSpin Guide 226

ProSpin Reference Guide 234

ProSpin FAQ 256

ProPPR Guide 259

Selecting, Configuring and Using ProPPR 285

ProPPR FAQ 295

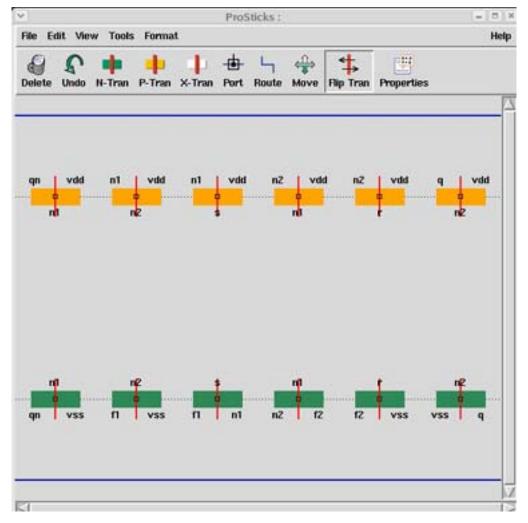

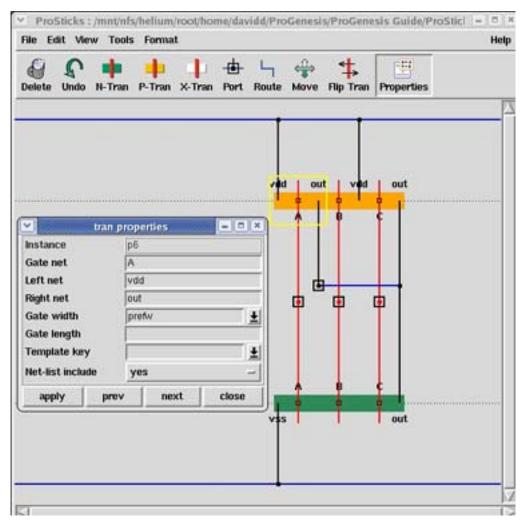

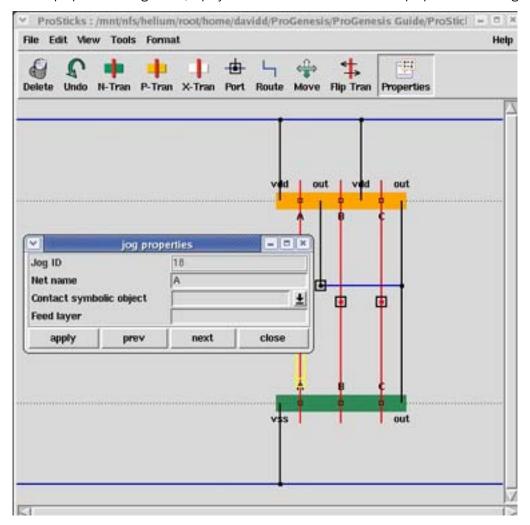

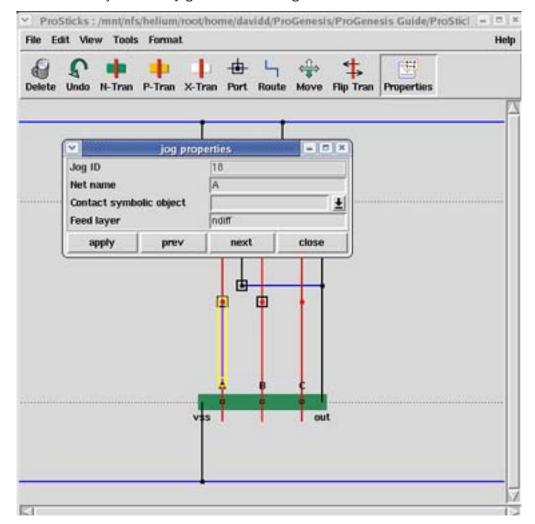

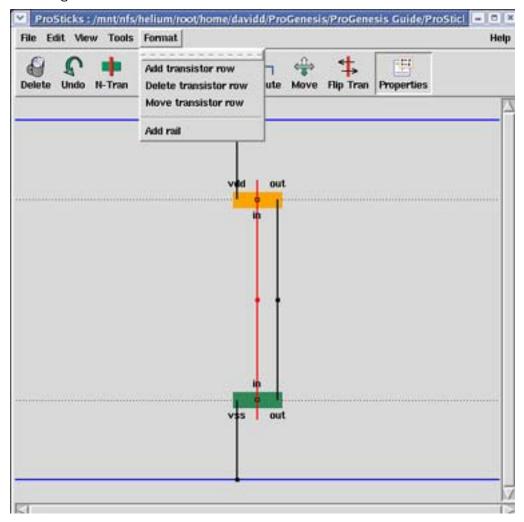

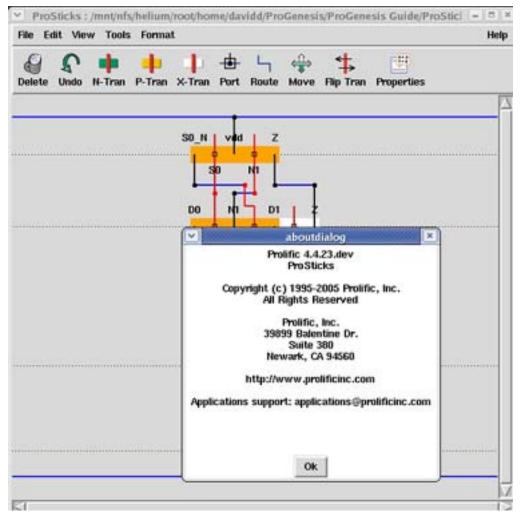

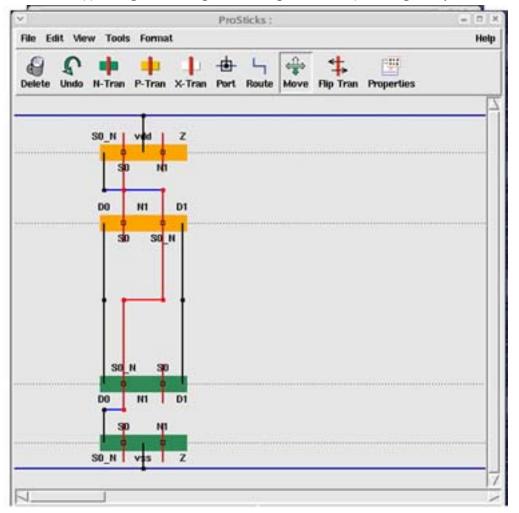

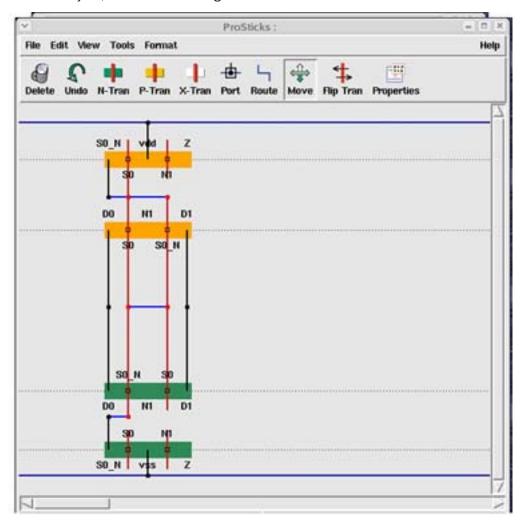

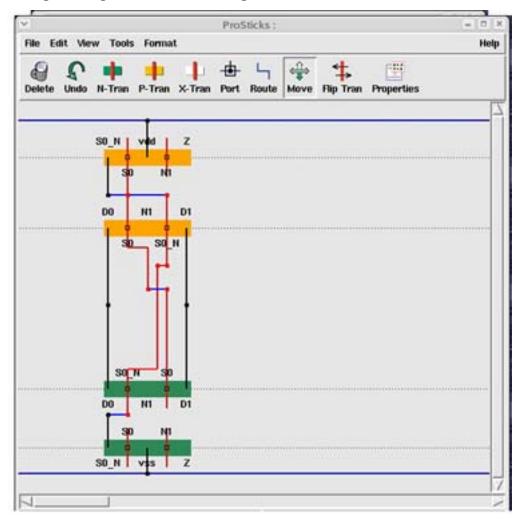

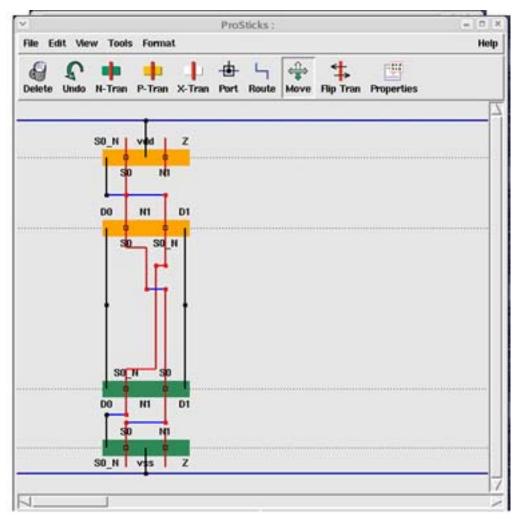

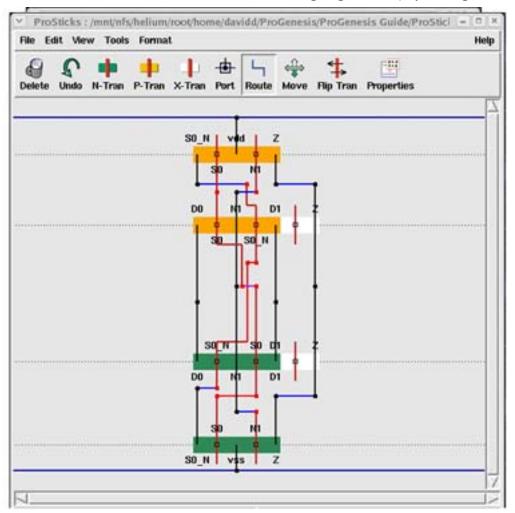

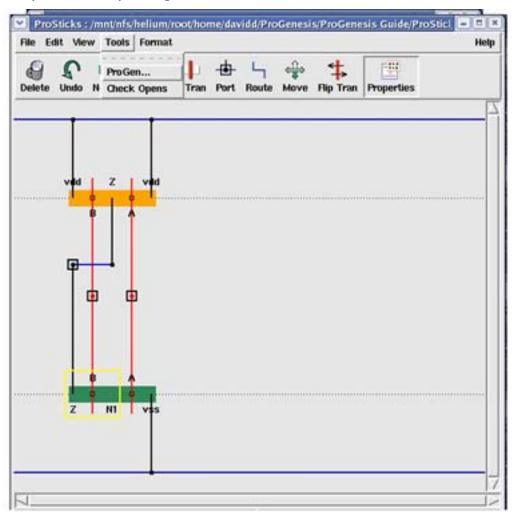

ProSticks Introduction 296

ProSticks Hotkeys 297

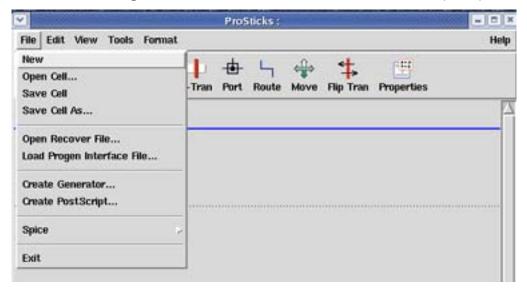

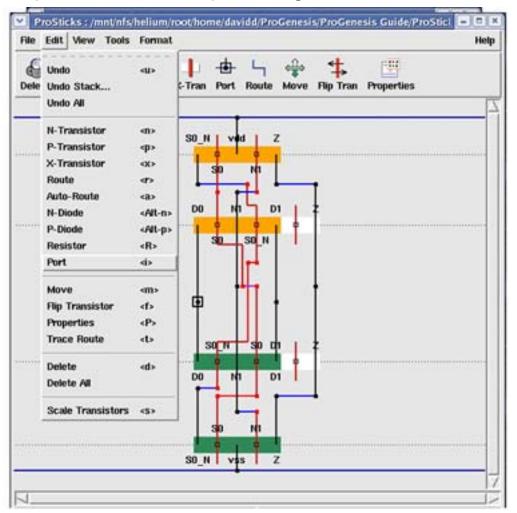

ProSticks Menus 302

ProSticks Technology File 315

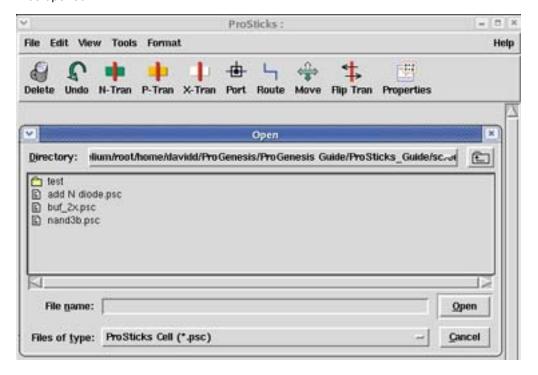

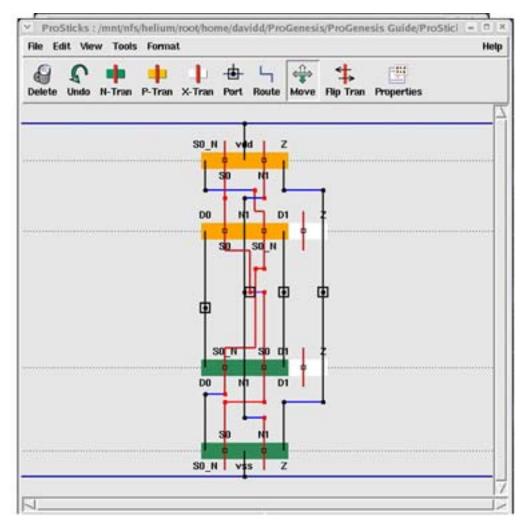

Navigating ProSticks 324

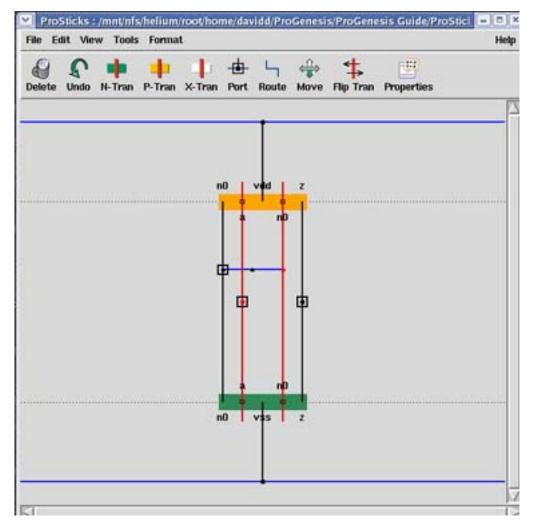

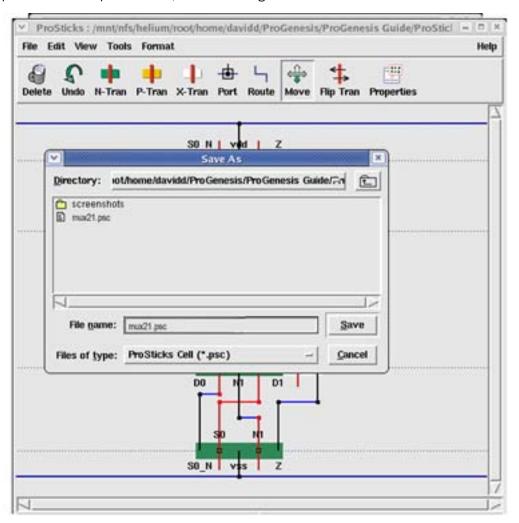

ProSticks Guide 375

ProSticks FAQ 437

ProAssemble Reference 439

Post-Processing Application Note 455

## **Notices**

ProGenesis Guide

Copyright © 2002-2006 by Prolific, Inc.

Revision for 2006.1 release.

Every effort has been made to supply complete and accurate information. However, Prolific, Inc. assumes no responsibility for errors or omissions, or for damages resulting from the use of the information contained herein.

This document is considered Prolific Confidential.

No part of this publication may be stored in a retrieval system, transmitted, or reproduced, in any form or by any means, including but not limited to electronic, magnetic, mechanical, photocopying, recording, or otherwise, without the prior agreement and written permission of Prolific, Inc.

ProGenesis® is a registered trademark of Prolific, Inc.

ProTiming<sup>™</sup> and ProPower<sup>™</sup> are trademarks of Prolific, Inc.

PrimeTime® and Design Compiler® are registered trademarks of Synopsys, Inc.

Liberty<sup>™</sup> and Library Compiler<sup>™</sup> are trademarks of Synopsys, Inc.

Sun™ and Solaris™ are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. or other countries.

Linux® is a registered trademark of Linus Torvalds.

All other trademarks and copyrights referred to are the property of their respective owners.

# Usage

Throughout the ProGenesis Guide's text, items which you will need to type directly into the command lines will appear in Courier font.

Variables you will need to input will appear in Courier italic.

# Getting Started With ProGenesis

#### Install ProGenesis on your system

Download the gzip'd file corresponding to your operating system.

The examples below are for release version 4.4.36. Other versions have similar organization, but the version number is changed.

| Operating System             | File                  |

|------------------------------|-----------------------|

| HP-UX 11.00                  | 20061_HPUX11.tar.gz   |

| Linux RedHat 6.x, 7.x        | 20061_Linux6.tar.gz   |

| Linux RedHat 9.x             | 20061_Linux9.tar.gz   |

| Linux RedHat Enterprise 3, 4 | 20061_LinuxRE3.tar.gz |

| Solaris                      | 20061_Solaris.tar.gz  |

Table 1

Please write to applications@prolificinc.com for upload instructions.

## Unpacking

The commands you use to unpack the software archive files depend on the type of file you downloaded and your operating environment. Typical commands are:

```

gunzip 20061_Solaris.tar.gz

tar xvf 20061_Solaris.tar

```

The file will unpack into the directory "4.4.34" which is the suite release number for the Prolific tools. Typical installations place it under the "prolific" directory and then have a logical link to it:

| File                                          | Description                     |

|-----------------------------------------------|---------------------------------|

| <install_path>/prolific/2006.1</install_path> | specific release directory      |

| <install_path>/prolific/prod</install_path>   | logical link to prolific/2006.1 |

Table 2

Of course, this configuration is completely up to you.

#### **Multiple Operating Systems**

To use multiple operating system releases just unpack each of the system specific archive files into the same directory tree. For example, the following unpacks the Solaris, HPUX1100 and Linux6 trees:

```

cd <install_path>/prolific

tar xvf 20061_Solaris.tar

tar xvf 20061_HPUX1100.tar

tar xvf 20061_Linux6.tar

```

The Prolific tools determine which operating system they are running on and invoke the appropriate executable.

#### **License Management - Existing Customer**

Your existing license file will continue to work with the 4.4.36 release of the tools. Simply install your existing license file in the 4.4.36 tree as defined in the next section (License Management - New Customer).

#### **License Management - New Customer**

If you have not already sent your license server host-id to Prolific please do so as soon as possible. This information is needed so that we can create a license file. The FLEXIm license file will be emailed to the license manager and should be installed in the following directory with the name <install\_path>/prolific/2006.1/lib/prolicense/prolific.lic.

This file may need to be edited depending on your site license management strategies. The FLEXIm license manager (Imgrd), vendor daemon (prolific), and license management utility program (Imutil) are in the OS-specific directory <install\_path>/prolific/2006.1/bin/<os>.

#### Set-Up

To run any of the tools the environment variable PROLIFIC must be set to the software install directory. Using the above path in csh you would set:

```

setenv PROLIFIC <install path>/prolific/prod

```

Then add the \$PROLIFIC/bin directory to you path. Again, in csh:

```

set path=($path $PROLIFIC/bin)

rehash

```

Configuring the environment is easy: the PROLIFIC environment variable must point to the directory where the software has been installed.

For example, if the software were installed in /usr/local/prolific/4.4.36, then you could use the following command to set the environment using the Bourne shell:

```

sh% PROLIFIC=/usr/local/prolific/2006.1

sh% export PROLIFIC

```

For non-Bourne shells, use the syntax appropriate to the shell. For example: using csh, set the PROLIFIC environment variable this way:

```

csh% setenv PROLIFIC /usr/local/prolific/2006.1

```

To check the environment variable, use the following command:

```

csh% echo $PROLIFIC

```

From now on, we'll refer to the PROLIFIC installation directory as \$PROLIFIC. All of the tools reside in the \$PRO-LIFIC/bin directory, so an easy way to run them is to add the \$PROLIFIC/bin directory to the path. It is most convenient to do this in the shell configuration files. For example: in the csh configuration file, .cshrc, the following command can be added:

```

set path = (

$PROLIFIC/bin \

$path \

)

```

Note that if you have multiple architecture binaries installed, the Prolific tools will automatically execute the appropriate version for your machine.

## **ProGenesis Tool Overview**

The basic ProGenesis tool flow is shown in Figure 1, below. ProGenesis is the suite of tools that generates standard cell layout from Spice input. ProGenesis includes three main tools used to create layout from netlists: Pro-Tech, ProSpin, and ProGen. Although other tools are included in the ProGenesis suite, these are the three we'll focus on to get started.

#### **ProTech**

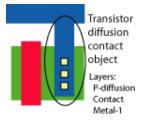

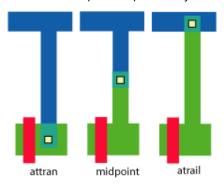

ProTech is the tool used to configure fabrication technology specifications, design styles, and layer information. ProTech is used to enter or modify the following types of information:

- Design Options: Transistor layout, compaction and routing options

- Design Rules: Mandatory and preferred rules specified by the fab

- Layer Data: Specify GDS layer data and text

- Cell Template: Cell height, well tie behavior, and rail and well sizes.

- Router Configuration: Number of routing tracks, layers, and costs.

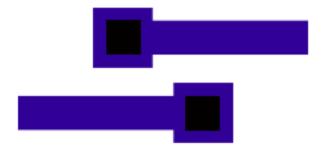

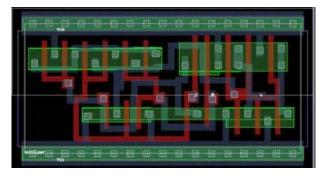

Figure 1: ProTech Flow

#### **ProSpin**

ProSpin reads Spice netlists describing individual cells and produces corresponding CEL files to be read by the ProGen tool. A CEL file specifies the generators that should be called to create the final layout data and contains cell-specific information such as transistor sizes and node names.

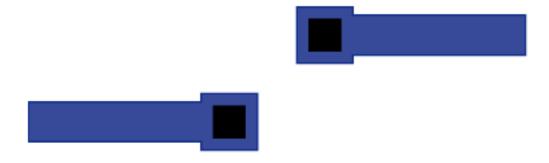

Figure 2: ProSpin Flow

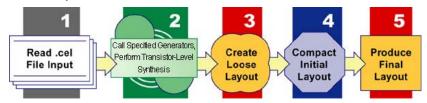

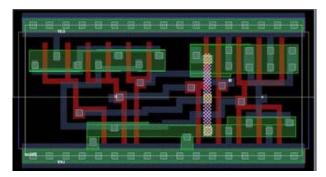

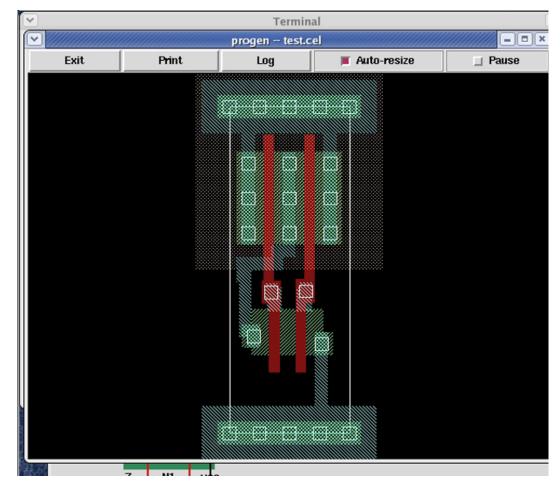

#### **ProGen**

ProGen reads in CEL files and produces physical layout based on the cell characteristics, the generators specified, and the technology-specific information created using ProTech. After reading the CEL file, ProGen invokes the proper generators and performs transistor-level synthesis to produce a loose physical layout. ProGen then compacts this initial layout to produce a final cell that is as small as possible while conforming to all design

#### rules and layout constraints.

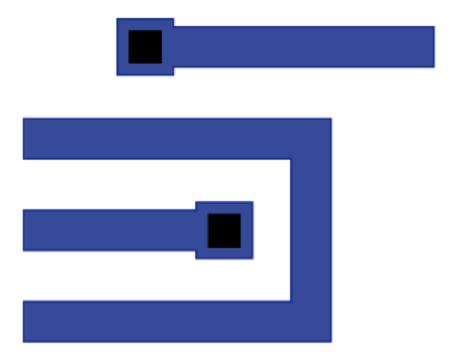

Figure 3: ProGen Flow

## **Demonstration Data**

The software bundle contains a demonstration area which contains everything you need to run the ProGenesis tools. All of the examples in this section use data from the demonstration area \$PROLIFIC/demo. The demo area contains the following types of data:

- Demonstration CMOS technology

- Cell Spice netlists

- Sample layout AGD (ASCII GDS, the output from ProGen) data

- Sample ProSticks layout, generators, cells, and output AGD data

#### **Generating Cell Layout From a Netlist**

This section describes how to generate an inverter cell from a Spice netlist. This process involves these steps:

- 1. Create or move to a working directory

- 2. Run ProSpin to convert the Spice netlist to a CEL file

- 3. Run ProGen to generate the cell and compact it

- 4. View AGD data

- 5. Convert between AGD and GDS

#### Step 1: Move to a working directory

The ProGenesis flow results in many files being created, so it is wise to run the tools from an appropriate working directory. We suggest creating a parent directory for each library project, with subdirectories for netlist input, CEL files, and process technology information. See "Prepare to Run Tutorial Data" for details.

#### Step 2: Use ProSpin to convert the netlist to a CEL file

In this step, we run ProSpin from the command line to create a cell description file named inv.cel from a Spice netlist named inv.sp. Use the following command:

```

csh% prospin -l inv $PROLIFIC/demo/spice/inv.sp

```

This should produce the inv.cel file in your working directory. ProSpin automatically creates CEL files to match each subcircuit name requested. For more information, consult the ProSpin Reference Guide.

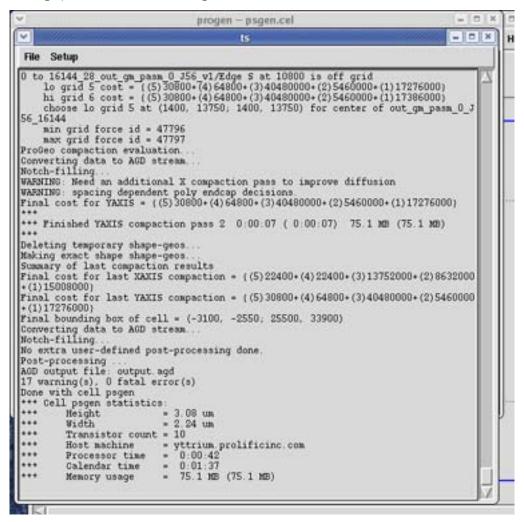

### Step 3: Use ProGen to generate and compact the cell

Now that there's a CEL file corresponding to the inverter cell, we run ProGen to create the cell layout:

```

csh% progen -t $PROLIFIC/demo/tech/demo.db -i inv.cel -o inv.agd

```

This command produces the inv.agd cell file, which contains the layout in AGD format. For more information on ProGen, consult the ProGen Reference Guide.

#### Step 4: Viewing AGD data

While this step isn't necessary for generating cell layout, it is useful for viewing the layout created in the first three steps. The ProGenesis tools produce AGD (ASCII-GDS) cell data. AGD is an ASCII representation of the standard GDSII data file format. PROLIFIC provides an AGD data file viewer called ProView.

```

csh% proview -t $PROLIFIC/demo/tech/demo.db inv.agd

```

This starts the ProView viewer and loads the AGD file inv.agd. Further information on options available in ProView is available in the ProView Reference Guide.

#### Step 5: Converting between AGD and GDS

Moving the data from ASCII GDS to a binary GDS file is easy. PROLIFIC provides two easy-to-use utilities for converting layout between AGD and GDS formats. To convert AGD data to GDS, use a2gds:

```

csh% a2gds < inv.agd > inv.gds

```

To convert GDS data to AGD, use gds2a:

```

csh% gds2a < inv.gds > inv.agd

```

GDS output can be generated directly from progen by specifying:

```

type agds

```

# **ProGenesis Tutorial Overview**

The ProGenesis suite allows designers to quickly and accurately create optimized standard cells. ProGenesis includes the tools shown below.

| Tool      | Description                        |

|-----------|------------------------------------|

| ProTech   | Design rule and configuration tool |

| ProSpin   | Netlist analysis tool              |

| ProGen    | Cell creation and compaction tool  |

| ProSticks | Topology editing and creation tool |

Table 1

#### **ProGenesis Flow**

ProGenesis can create and manage any number of cells, and can handle cells as part of a library or individually. ProGenesis requires the inputs shown below to create GDS-II output:

| Input                    | Description                                      |

|--------------------------|--------------------------------------------------|

| Netlist                  | Single, multiple, or hierarchical HSpice netlist |

| Design rules             | From design rule document                        |

| Cell template definition | User-defined cell architecture                   |

Table 2

The cell creation process follows these steps:

1. Define setup information in ProTech design rules and cell template definitions.

| Input | Enter design rules and cell architecture settings                                     |

|-------|---------------------------------------------------------------------------------------|

|       | A database (.db) file containing design rules, cell template, and library option data |

Table 3

2. Use ProSpin to analyze netlists and match their contents to cell generators.

| Input  | Spice netlists                                                       |

|--------|----------------------------------------------------------------------|

| Output | .cel files containing the generator calls corresponding to each cell |

Table 4

3. Run ProGen to create and compact cells.

| Input | Output from the previous steps (.cel files and .db file) |

|-------|----------------------------------------------------------|

Table 5

|  | Output | GDS-II layout |

|--|--------|---------------|

|--|--------|---------------|

Table 5

#### **ProGenesis Approach**

ProGenesis recognizes the basic hierarchical building blocks in a cell, such as NAND, AOI, and TRI-INV. These blocks are represented within the ProGenesis flow as "generators" which can include descriptions of transistor placement, routing configurations, and other layout details.

In general, more layout information contained in a generator results in more predictable GDS-II output. However, it is also possible to include too much information in a generator, which can overconstrain the cell creation process, ruling out desirable solutions. Walk through the ProGenesis Tutorial Guide to see how generators are used.

## **ProGenesis Tutorial Guide**

In the first part of this tutorial, the use of the products is described. In the second part of the tutorial is data that can be used to practice walking through the tools. Sample tutorial data should be included with the ProGenesis tools; the data are also available in the section called "Tutorial Data."

#### **Prepare To Run Tutorial Data**

Ensure that the environment and tools are ready:

• Create a working directory you can use without worrying:

```

% mkdir temp

```

• Create a subdirectory structure for data and output:

```

% cd temp

% mkdir agd cel net tech

```

• Check that the environment variable is set correctly:

```

% echo $PROLIFIC

```

## **Setting the Environment Variable**

If the PROLIFIC environment variable is not set, or points to the wrong directory, follow the setup instructions in the Getting Started guide.

• Check that ProGen runs properly:

```

% progen -h

```

• Make a local work directory and copy the tutorial data there:

```

% cp -r $PROLIFIC/tutorial work

```

#### **Starting ProTech**

Start ProTech from the command line:

```

% protech

```

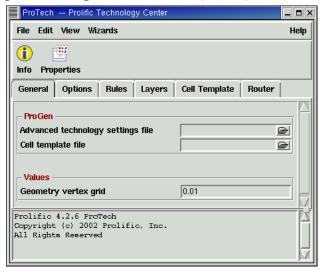

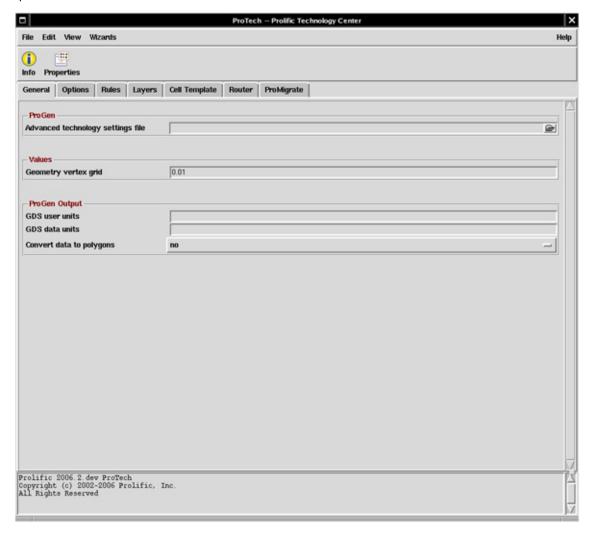

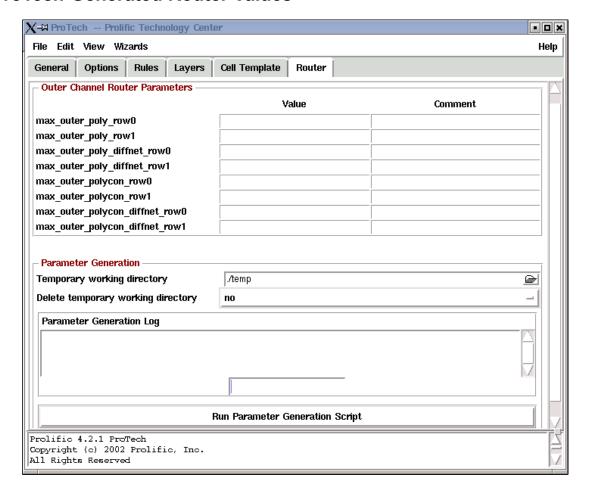

The ProTech graphical interface will appear on the screen (see Figure 1). Its tabbed region identifies the different categories of configuration information (Table 1):

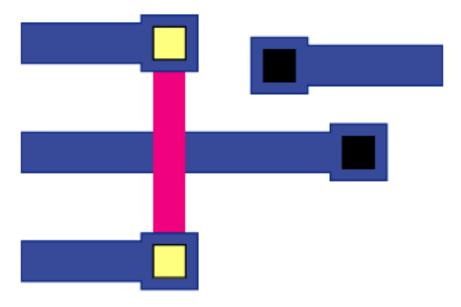

Figure 1: ProTech Interface

| Tab           | Description                                                        |

|---------------|--------------------------------------------------------------------|

| General       | Set manufacturing vertex grid. Set path to advanced settings file. |

| Options       | Configure library-wide options and layout style preferences.       |

| Rules         | Enter design rules.                                                |

| Layer         | Define layer-to-GDS mappings.                                      |

| Cell Template | Select cell template style.                                        |

| Router        | Calibrates router for cell template definition.                    |

Table 1: ProTech tabs

## **Entering Setup Data**

The first time you use ProTech, follow these steps:

Click on the General tab. In the Geometry vertex grid field, enter the manufacturing grid size in microns. For this tutorial, enter 0.005.

You can skip the other General settings and the Options settings. When you initially create cells, you do not have to alter these settings, but on subsequent iterations they may help you to tailor the layout to your needs and preferences.

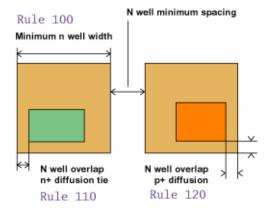

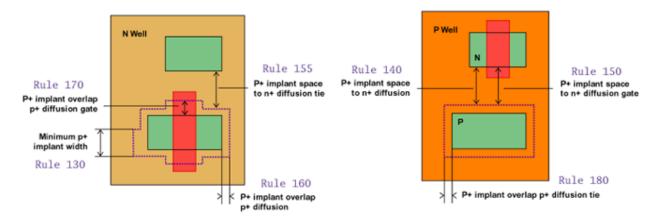

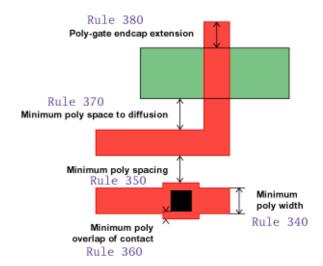

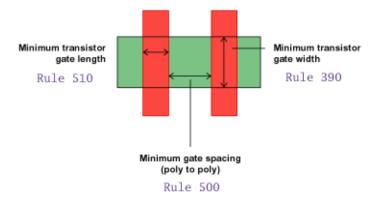

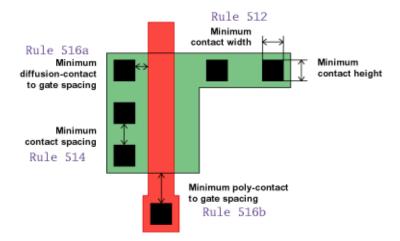

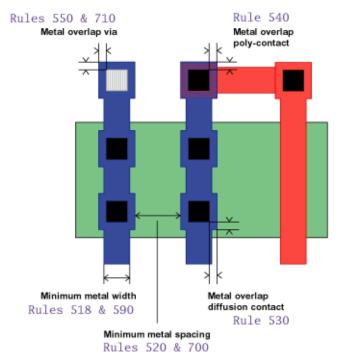

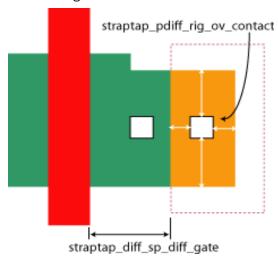

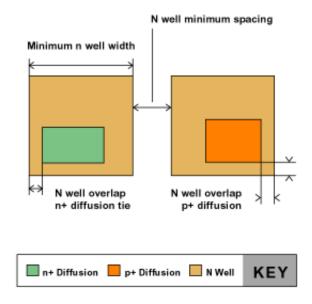

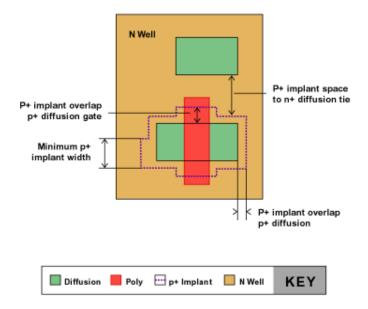

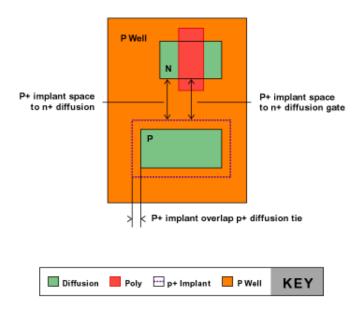

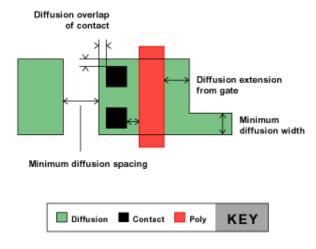

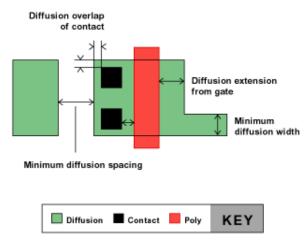

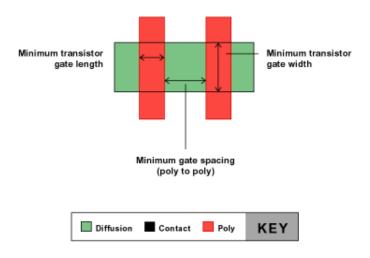

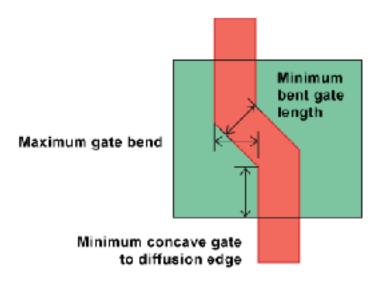

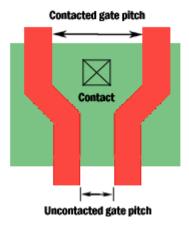

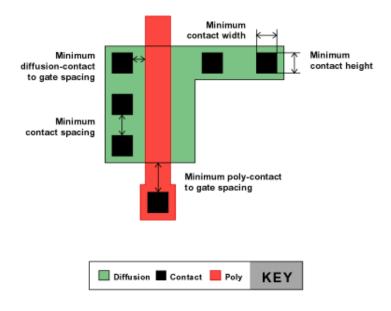

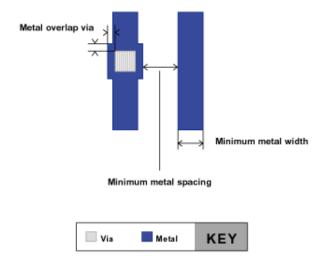

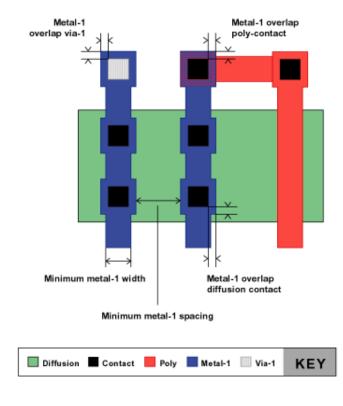

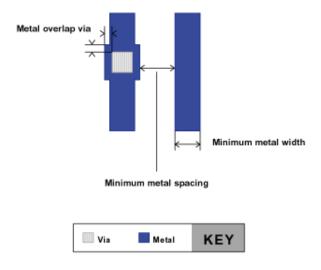

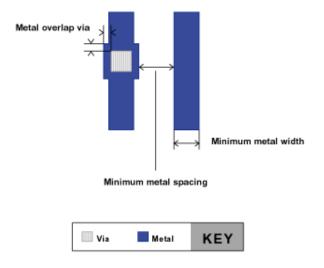

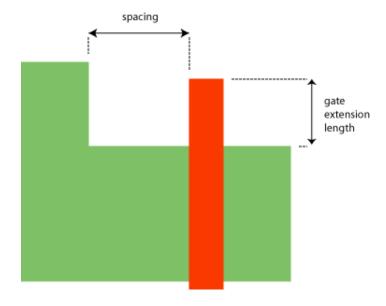

Click on the Rules tab to enter design rules from a design rule document. For this tutorial, enter the values shown in Table 4. If you want to know more about a particular design rule entry, click on the Info button, then click on the name of any rule for a description and illustration of that rule.

| n-well overlap N+ diffusion tie n-well overlap P+ diffusion  Minimum P+ implant width  P+ implant space to N+ diffusion  P+ implant space to N+ diffusion gate  P+ implant space to N+ diffusion gate  P+ implant space to N+ diffusion tie  P+ implant overlap P+ diffusion gate  P- implant overlap P+ diffusion gate  Diffusion overlap of contact  Minimum diffusion spacing  Diffusion overlap of contact  Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  N- diffusion space to n-well  N- diffusion space to diffusion  N- diffusion overlap of contact  Minimum poly width  D.1  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  D.05  Poly-gate endcap extension  Minimum transistor gate width  D.12  Minimum poly-to-poly gate spacing  Minimum transistor gate length  D.1  Minimum contact width  D.12  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  D.12  Minimum Metal-1 spacing  Metal-1 overlap poly-contact  D.0 0.025 0.0 0.05  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  D.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Rule Name                                 | Value to Enter        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|

| Minimum P+ diffusion  Minimum P+ implant width  P+ implant space to N+ diffusion  P+ implant space to N+ diffusion gate  P+ implant space to N+ diffusion gate  P+ implant space to N+ diffusion gate  P+ implant space to N+ diffusion tie  0.02  P+ implant overlap P+ diffusion  P+ implant overlap P+ diffusion gate  0.22  P+ implant overlap P+ diffusion gate  0.02  Minimum diffusion width  0.11  Minimum diffusion spacing  0.14  Diffusion overlap of contact  0.05  Diffusion extension from gate  Minimum width butted diffusions  0.11  N+ diffusion space to n-well  0.22  Minimum poly width  0.1  Minimum poly spacing  0.14  Minimum poly space to diffusion  0.05  Poly-gate endcap extension  0.16  Minimum transistor gate width  0.12  Minimum transistor gate length  0.14  Minimum contact width  0.12  Minimum contact width  0.12  Minimum diffusion-contact to gate spacing  0.14  Minimum diffusion-contact to gate spacing  0.14  Minimum diffusion-contact to gate spacing  0.14  Minimum Metal-1 width  0.12  Minimum Metal-1 width  0.12  Metal-1 overlap poly-contact  0.0 0.025 0.0 0.025  Metal-1 overlap poly-contact  Metal-1 minimum area  0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Min n-well width                          | 0.62                  |

| Minimum P+ implant width P+ implant space to N+ diffusion P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion tie 0.02 P+ implant overlap P+ diffusion P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion tie 0.02 Minimum diffusion width 0.11 Minimum diffusion spacing 0.14 Diffusion overlap of contact 0.05 Diffusion extension from gate Minimum width butted diffusions 0.11 N+ diffusion space to n-well 0.22 Minimum poly width 0.1 Minimum poly spacing 0.14 Minimum poly spacing 0.14 Minimum poly overlap of contact 0.03 0.05 0.03 0.05 Minimum poly space to diffusion 0.05 Poly-gate endcap extension 0.16 Minimum transistor gate width 0.12 Minimum transistor gate length 0.14 Minimum contact width 0.12 Minimum contact spacing 0.14 Minimum contact spacing 0.14 Minimum diffusion-contact to gate spacing 0.14 Minimum diffusion-contact to gate spacing 0.14 Minimum Metal-1 width 0.12 Minimum Metal-1 width 0.12 Minimum Metal-1 spacing 0.10 Metal-1 overlap poly-contact 0.0 0.025 0.0 0.025 Metal-1 overlap poly-contact 0.005 0.05 0.005 Metal-1 minimum area 0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | n-well overlap N+ diffusion tie           | 0.17                  |

| P+ implant space to N+ diffusion P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion tie 0.02 P+ implant overlap P+ diffusion P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion gate 0.22 P+ implant overlap P+ diffusion tie 0.02 Minimum diffusion width 0.11 Minimum diffusion spacing 0.14 Diffusion overlap of contact 0.05 Diffusion extension from gate 0.16 Minimum width butted diffusions 0.11 N+ diffusion space to n-well 0.22 Minimum poly width 0.1 Minimum poly spacing 0.14 Minimum poly spacing 0.14 Minimum poly overlap of contact 0.03 0.05 0.03 0.05 Minimum poly space to diffusion 0.05 Poly-gate endcap extension 0.16 Minimum transistor gate width 0.12 Minimum poly-to-poly gate spacing 0.15 Minimum transistor gate length 0.1 Minimum contact width 0.12 Minimum contact width 0.12 Minimum contact spacing 0.14 Minimum diffusion-contact to gate spacing 0.14 Minimum diffusion-contact to gate spacing 0.14 Minimum Metal-1 width 0.12 Minimum Metal-1 width 0.12 Minimum Metal-1 spacing 0.00 Metal-1 overlap diffusion-contact 0.0 0.025 0.0 0.025 Metal-1 overlap Via-1 0.005 Metal-1 minimum area 0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | n-well overlap P+ diffusion               | 0.22                  |

| P+ implant space to N+ diffusion gate P+ implant space to N+ diffusion tie P+ implant overlap P+ diffusion P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion tie O.02 Minimum diffusion width O.11 Minimum diffusion spacing O.14 Diffusion overlap of contact O.05 Diffusion extension from gate O.16 Minimum width butted diffusions O.11 N+ diffusion space to n-well O.22 Minimum poly width O.1 Minimum poly spacing O.14 Minimum poly spacing O.15 Minimum poly space to diffusion O.05 Poly-gate endcap extension O.16 Minimum transistor gate width O.12 Minimum poly-to-poly gate spacing O.15 Minimum contact width O.12 Minimum contact width O.12 Minimum contact spacing O.14 Minimum diffusion-contact to gate spacing O.08 Minimum Metal-1 width O.12 Minimum Metal-1 spacing O.12 Metal-1 overlap diffusion-contact O.0 0.025 0.0 0.025 Metal-1 overlap poly-contact Metal-1 verlap poly-contact O.005 Metal-1 minimum area O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Minimum P+ implant width                  | 0.24                  |

| P+ implant space to N+ diffusion tie  P+ implant overlap P+ diffusion  P+ implant overlap P+ diffusion gate  P+ implant overlap P+ diffusion gate  P+ implant overlap P+ diffusion tie  0.02  Minimum diffusion width  0.11  Minimum diffusion spacing  0.14  Diffusion overlap of contact  0.05  Diffusion extension from gate  Minimum width butted diffusions  0.11  N+ diffusion space to n-well  0.22  Minimum poly width  0.1  Minimum poly spacing  Minimum poly spacing  Minimum poly space to diffusion  0.05  Poly-gate endcap extension  Minimum transistor gate width  0.12  Minimum poly-to-poly gate spacing  Minimum contact width  0.12  Minimum contact width  0.12  Minimum contact spacing  Minimum diffusion-contact to gate spacing  0.14  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  0.12  Minimum Metal-1 width  0.12  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  0.0 0.05 0.0 0.05  Metal-1 overlap poly-contact  Metal-1 overlap poly-contact  0.005 0.05 0.005  Metal-1 minimum area  0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P+ implant space to N+ diffusion          | 0.13                  |

| P+ implant overlap P+ diffusion P+ implant overlap P+ diffusion gate O.22 P+ implant overlap P+ diffusion tie O.02 Minimum diffusion width O.11 Minimum diffusion spacing O.14 Diffusion overlap of contact O.05 Diffusion extension from gate O.16 Minimum width butted diffusions O.11 N+ diffusion space to n-well O.22 Minimum poly width O.1 Minimum poly spacing O.14 Minimum poly spacing O.14 Minimum poly spacing O.14 Minimum poly space to diffusion O.05 Poly-gate endcap extension O.16 Minimum transistor gate width O.12 Minimum poly-to-poly gate spacing Minimum transistor gate length O.1 Minimum contact width O.12 Minimum contact width O.12 Minimum diffusion-contact to gate spacing O.14 Minimum diffusion-contact to gate spacing O.14 Minimum diffusion-contact to gate spacing O.14 Minimum Metal-1 width O.12 Minimum Metal-1 width O.12 Minimum Metal-1 spacing O.14 Minimum Metal-1 overlap diffusion-contact O.0 0.05 0.0 0.05 Metal-1 overlap poly-contact O.0 0.05 0.0 0.05 Metal-1 verlap poly-contact O.005 0.05 0.005 Metal-1 minimum area O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P+ implant space to N+ diffusion gate     | 0.22                  |

| P+ implant overlap P+ diffusion gate P+ implant overlap P+ diffusion tie  0.02  Minimum diffusion width 0.11  Minimum diffusion spacing 0.14  Diffusion overlap of contact 0.05  Diffusion extension from gate 0.16  Minimum width butted diffusions 0.11  N+ diffusion space to n-well 0.22  Minimum poly width 0.1  Minimum poly spacing 0.14  Minimum poly overlap of contact 0.03 0.05 0.03 0.05  Minimum poly space to diffusion Poly-gate endcap extension 0.16  Minimum transistor gate width 0.12  Minimum poly-to-poly gate spacing 0.15  Minimum contact width 0.12  Minimum contact width 0.12  Minimum diffusion-contact to gate spacing 0.14  Minimum diffusion-contact to gate spacing 0.14  Minimum Metal-1 width 0.12  Minimum Metal-1 spacing 0.12  Metal-1 overlap diffusion-contact 0.0 0.05 0.0 0.05  Metal-1 overlap poly-contact Metal-1 overlap poly-contact 0.005 0.05  Metal-1 overlap Via-1 0.005  Metal-1 minimum area 0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | P+ implant space to N+ diffusion tie      | 0.02                  |

| P+ implant overlap P+ diffusion tie  Minimum diffusion width  Minimum diffusion spacing  Diffusion overlap of contact  Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  N+ diffusion space to n-well  Minimum poly width  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap poly-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Monos  Metal-1 overlap Via-1  O.059  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | P+ implant overlap P+ diffusion           | 0.13                  |

| Minimum diffusion width  Minimum diffusion spacing  Diffusion overlap of contact  Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  N+ diffusion space to n-well  Minimum poly width  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  O.12  Minimum contact width  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 overlap Via-1  Monimum diffusion-contos  Metal-1 overlap Via-1  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P+ implant overlap P+ diffusion gate      | 0.22                  |

| Minimum diffusion spacing  Diffusion overlap of contact  Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  N+ diffusion space to n-well  O.22  Minimum poly width  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  O.12  Minimum contact width  O.12  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  O.12  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  O.0 0.025 0.0 0.025  Metal-1 overlap Via-1  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | P+ implant overlap P+ diffusion tie       | 0.02                  |

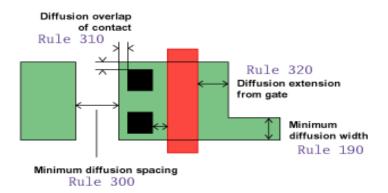

| Diffusion overlap of contact  Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  N+ diffusion space to n-well  O.22  Minimum poly width  O.1  Minimum poly spacing  Minimum poly overlap of contact  O.03  0.05  0.03  0.05  Minimum poly space to diffusion  Poly-gate endcap extension  O.16  Minimum transistor gate width  O.12  Minimum poly-to-poly gate spacing  Minimum transistor gate length  O.1  Minimum contact width  O.12  Minimum contact spacing  O.14  Minimum contact spacing  O.14  Minimum diffusion-contact to gate spacing  O.10  Minimum Metal-1 width  O.12  Minimum Metal-1 spacing  O.12  Metal-1 overlap diffusion-contact  O.0 0.025  0.0 0.025  Metal-1 overlap Via-1  O.005  0.05  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Minimum diffusion width                   | 0.11                  |

| Diffusion extension from gate  Minimum width butted diffusions  N+ diffusion space to n-well  0.22  Minimum poly width  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  O.05  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  O.12  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  O.12  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Minimum diffusion spacing                 | 0.14                  |

| Minimum width butted diffusions  N+ diffusion space to n-well  0.22  Minimum poly width  0.1  Minimum poly spacing  0.14  Minimum poly overlap of contact  0.03 0.05 0.03 0.05  Minimum poly space to diffusion  Poly-gate endcap extension  0.16  Minimum transistor gate width  0.12  Minimum poly-to-poly gate spacing  Minimum transistor gate length  0.1  Minimum contact width  0.12  Minimum contact width  0.12  Minimum diffusion-contact to gate spacing  0.14  Minimum diffusion-contact to gate spacing  0.14  Minimum Metal-1 width  0.12  Minimum Metal-1 spacing  0.1  Minimum Metal-1 spacing  0.12  Metal-1 overlap diffusion-contact  0.0 0.05 0.0 0.05  Metal-1 overlap Via-1  0.005 0.05 0.005 0.05  Metal-1 minimum area  0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Diffusion overlap of contact              | 0.05                  |

| Minimum poly width  Minimum poly spacing  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact width  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Diffusion extension from gate             | 0.16                  |

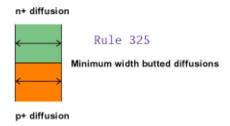

| Minimum poly width  Minimum poly spacing  Minimum poly overlap of contact  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum width butted diffusions           | 0.11                  |

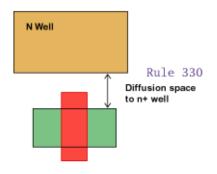

| Minimum poly spacing  Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | N+ diffusion space to n-well              | 0.22                  |

| Minimum poly overlap of contact  Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum diffusion-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.03 0.05 0.03 0.05  0.05  0.16  0.12  0.14  0.04  0.08  0.08  0.12  0.09  0.12  0.12  0.005 0.00 0.05  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Minimum poly width                        | 0.1                   |

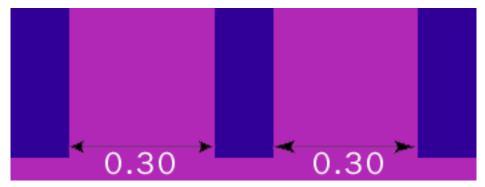

| Minimum poly space to diffusion  Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Minimum poly spacing                      | 0.14                  |

| Poly-gate endcap extension  Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.16  O.12  O.15  O.14  O.12  O.08  O.1  O.10  O.12  O.12  O.12  O.12  O.13  O.14  O.15  O.15  O.16  O.16  O.17  O.18  O.19  O | Minimum poly overlap of contact           | 0.03 0.05 0.03 0.05   |

| Minimum transistor gate width  Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum poly space to diffusion           | 0.05                  |

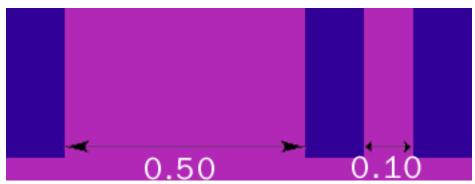

| Minimum poly-to-poly gate spacing  Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Poly-gate endcap extension                | 0.16                  |

| Minimum transistor gate length  Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.12  O.005 O.05 O.005  O.005 O.005  O.005 O.005  O.005 O.005  O.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Minimum transistor gate width             | 0.12                  |

| Minimum contact width  Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.12  O.0 0.05 0.0 0.05  O.005 0.005  O.005 0.005  O.005 0.005  O.005 0.005  O.005 0.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Minimum poly-to-poly gate spacing         | 0.15                  |

| Minimum contact spacing  Minimum diffusion-contact to gate spacing  Minimum poly-contact to gate spacing  Minimum Metal-1 width  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  0.14  0.08  0.12  0.12  0.012  0.025  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005  0.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Minimum transistor gate length            | 0.1                   |

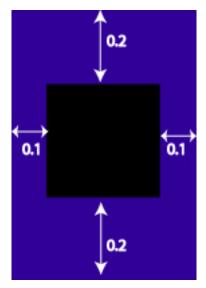

| Minimum diffusion-contact to gate spacing 0.08  Minimum poly-contact to gate spacing 0.1  Minimum Metal-1 width 0.12  Minimum Metal-1 spacing 0.12  Metal-1 overlap diffusion-contact 0.0 0.05 0.0 0.05  Metal-1 overlap poly-contact 0.0 0.025 0.0 0.025  Metal-1 overlap Via-1 0.005 0.05 0.005 0.05  Metal-1 minimum area 0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Minimum contact width                     | 0.12                  |

| Minimum poly-contact to gate spacing  Minimum Metal-1 width  O.12  Minimum Metal-1 spacing  Metal-1 overlap diffusion-contact  Metal-1 overlap poly-contact  Metal-1 overlap Via-1  Metal-1 minimum area  O.12  O.0 0.05 0.0 0.05  O.0 0.05  O.0 0.025  O.0 0.025  O.005  O.005  O.005  O.005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Minimum contact spacing                   | 0.14                  |

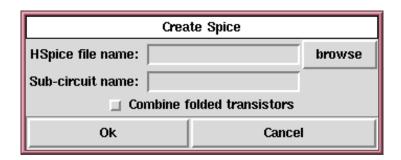

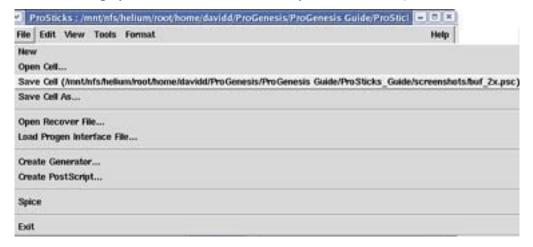

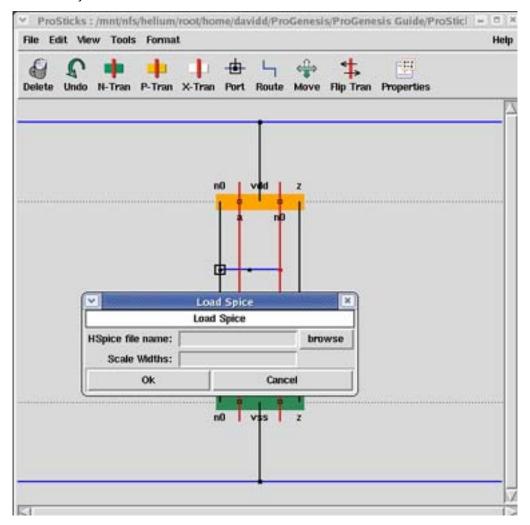

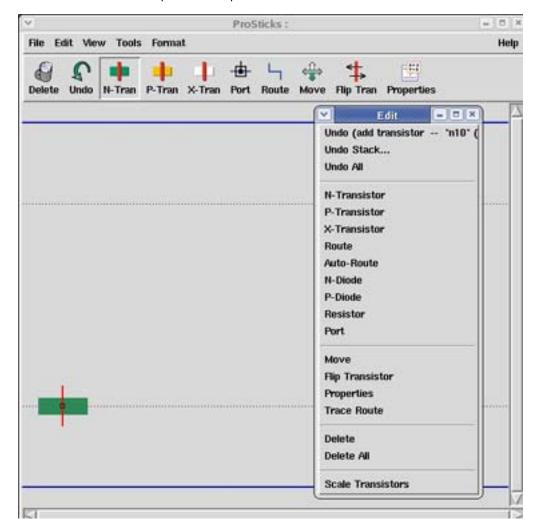

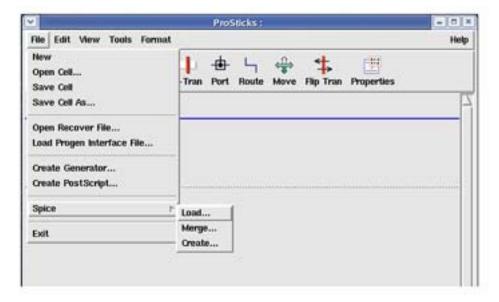

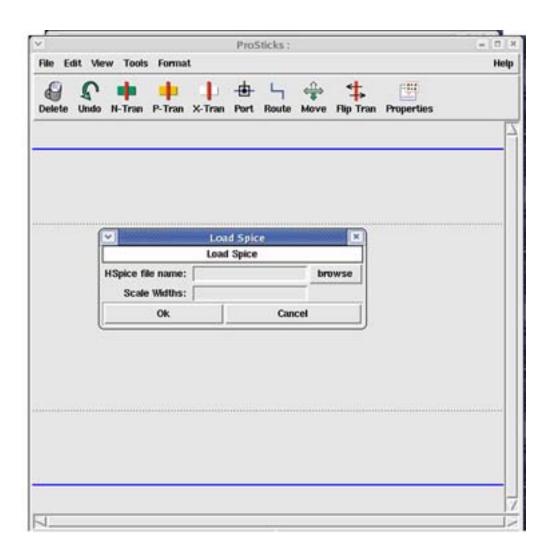

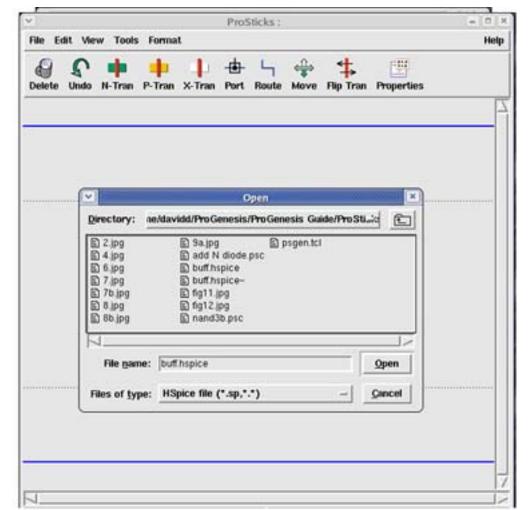

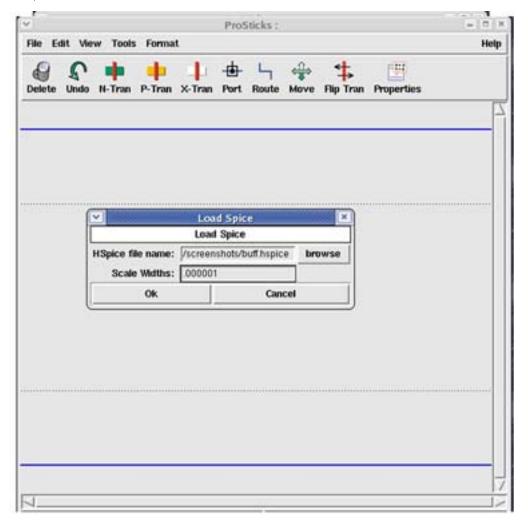

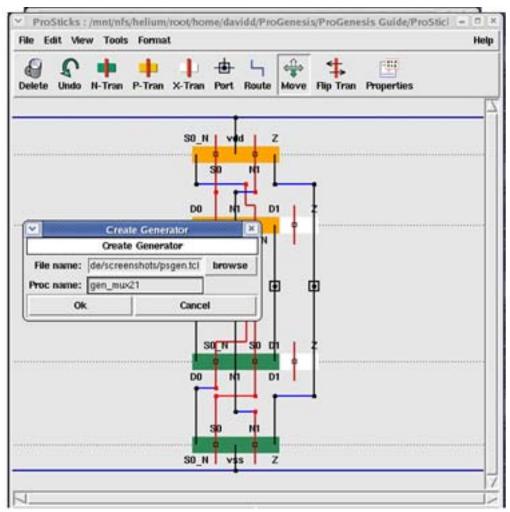

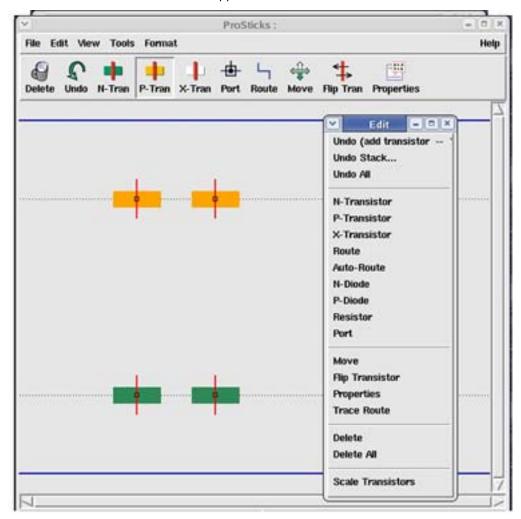

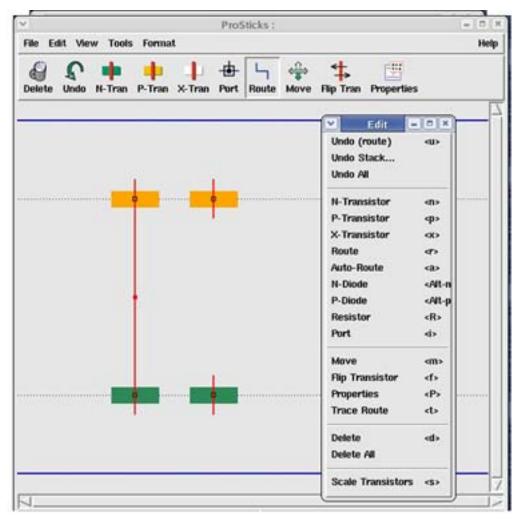

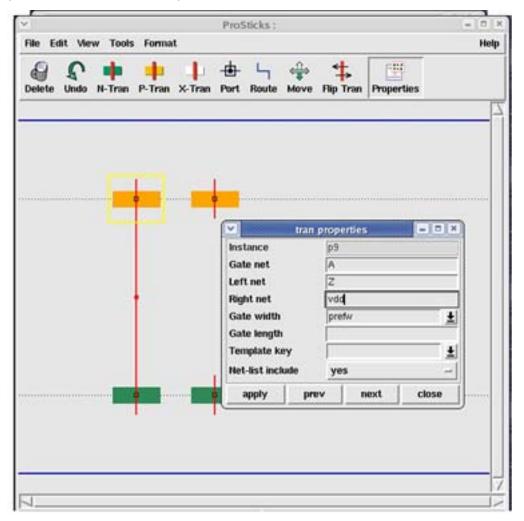

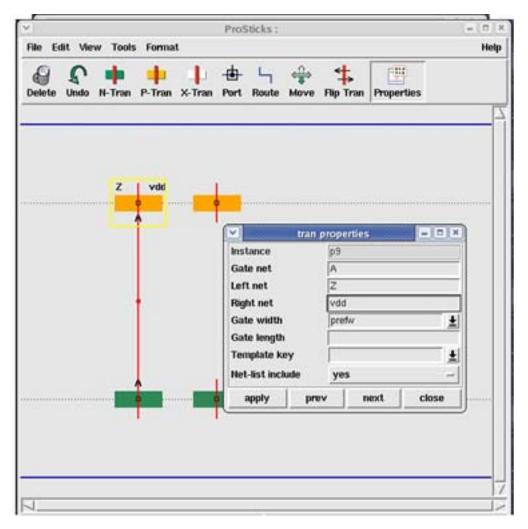

| Minimum Metal-1 width       0.12         Minimum Metal-1 spacing       0.12         Metal-1 overlap diffusion-contact       0.0 0.05 0.0 0.05         Metal-1 overlap poly-contact       0.0 0.025 0.0 0.025         Metal-1 overlap Via-1       0.005 0.05 0.005 0.05         Metal-1 minimum area       0.059                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Minimum diffusion-contact to gate spacing | 0.08                  |