**Simply Better Results**

# Synplicity ASIC Synthesis

5.0 Tutorial

September 2005

Synplicity, Inc. 600 West California Avenue Sunnyvale, CA 94086, USA (U.S.) +1 408 215-6000 direct (U.S.) +1 408 990-0263 fax www.synplicity.com

## Copyright and License Agreement

#### **Disclaimer of Warranty**

Synplicity, Inc. makes no representations or warranties, either expressed or implied, by or with respect to anything in this material, and shall not be liable for any implied warranties of merchantability or fitness for a particular purpose of for any indirect, special or consequential damages.

### **Copyright Notice**

Copyright © 1994-2005 Synplicity, Inc. All Rights Reserved.

Synplicity software products contain certain confidential information of Synplicity, Inc. Use of this copyright notice is precautionary and does not imply publication or disclosure. No part of this material may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form by any means without the prior written permission of Synplicity, Inc. While every precaution has been taken in the preparation of this material, Synplicity, Inc. assumes no responsibility for errors or omissions. This material and the features described herein are subject to change without notice.

#### Trademarks

Synplicity, the Synplicity "S" logo, Amplify, Certify, Synplify, Synplify Pro, Synplify ASIC, Amplify ASIC, RealPower, HDL Analyst, SCOPE, Behavior Extracting Synthesis Technology, Embedded Synthesis, Simply Better Synthesis, Simply Better Results, and Synthesis Constraint Optimization Environment are registered trademarks, and BEST, DST, Direct Synthesis Technology, MultiPoint, Partition-Driven Synthesis, PowerPlanner, Physical Synthesis, Synplify Lite, and Total Optimization Physical Synthesis are trademarks of Synplicity, Inc. Verilog is a registered trademark of Cadence Design Systems, Inc. IBM and PC are registered trademarks of International Business Machines Corporation. Microsoft is a registered trademark of Microsoft Corporation. Sun, SPARC, Solaris, and SunOS are trademarks of Sun Microsystems, Inc. UNIX is a registered trademark of X/Open Corporation. All other product names mentioned herein are the trademarks or registered trademarks of their respective owners.

#### **Restricted Rights Legend**

Government Users: Use, reproduction, release, modification, or disclosure of this commercial computer software, or of any related documentation of any kind, is restricted in accordance with FAR 12.212 and DFARS 227.7202, and further restricted by the Synplicity Software License Agreement. Synplicity, Inc., 600 West California Avenue, Sunnyvale, CA 94086, U. S. A.

September 2005

#### Synplicity Software License Agreement

Important! READ CAREFULLY BEFORE PROCEEDING

BY INDICATING YOUR ACCEPTANCE OF THE TERMS OF THIS AGREEMENT, YOU ("LICENSEE") ARE REPRESENTING THAT YOU HAVE THE RIGHT AND AUTHORITY TO LEGALLY BIND YOUR-SELF OR YOUR COMPANY, AS APPLICABLE, AND CONSENTING TO BE LEGALLY BOUND BY ALL OF THE TERMS OF THIS AGREEMENT. IF YOU DO NOT AGREE TO ALL THESE TERMS DO NOT INSTALL OR USE THE SOFTWARE, AND RETURN THE SOFTWARE TO THE LOCATION OF PURCHASE FOR A REFUND. This is a legal agreement governing use of the software program provided by Synplicity, Inc. ("Synplicity") to you (the "SOFTWARE"). The term "SOFTWARE" also includes related documentation (whether in print or electronic form), any authorization keys, authorization codes, and license files, and any updates or upgrades of the SOFTWARE provided by Synplicity, but does <u>not</u> include certain "open source" software licensed by third party licensors and made available to you by Synplicity under the terms of such third party license is a participant in the University Program or has been granted an Evaluation License or Subscription License, then some of the following terms and conditions may not apply (refer to the sections entitled, respectively, **Evaluation License** and **Subscription License**, below).

License. Synplicity grants to Licensee a non-exclusive right to install the SOFTWARE and to use or authorize use of the SOFTWARE by up to the number of nodes for which Licensee has a license and for which Licensee has the security key(s) or authorization code(s) provided by Synplicity or its agents for the purpose of creating and modifying Designs (as defined below). If Licensee has obtained the SOFTWARE under a node-locked license, then a "node" refers to a specific machine, and the SOFTWARE may be installed only on the number of "nodes" or machines authorized, must be used only on the machine(s) on which it is installed, and may be accessed only by users who are physically present at that node or machine. A node-locked license may only be used by one user at a time running one instance of the software at a time. If Licensee has obtained the SOFT-WARE under a "floating" license, then a "node" refers to a concurrent user or session, and the SOFTWARE may be used concurrently by up to the number of users or sessions indicated. All SOFTWARE must be used within the country for which the systems were licensed and at Licensee's Site (contained within a one kilometer radius); however, if Licensee has a floating license then remote use is permitted by employees who work at the site but are temporarily telecommuting to that same site from less than 50 miles away (for example, an employee who works at a home office on occasion), but the maximum number of concurrent sessions or nodes still applies. In addition, Synplicity grants to Licensee a non-exclusive license to copy and distribute internally the documentation portion of the SOFTWARE in support of its license to use the program portion of the SOFTWARE. For purposes of this Agreement the "Licensee's Site" means the location of the server on which the SOFTWARE resides, or when a server is not required, the location of the client computer for which the license was issued.

**Evaluation License**. If Licensee has obtained the SOFTWARE pursuant to an evaluation license, then, in addition to all other terms and conditions herein, the following restrictions apply: (a) the license to the SOFT-WARE terminates after 20 days (unless otherwise agreed to in writing by Synplicity); and (b) Licensee may use the SOFTWARE only for the sole purpose of internal testing and evaluation to determine whether Licensee wishes to license the SOFTWARE on a commercial basis. Licensee shall not use the SOFTWARE to design any integrated circuits for production or pre-production purposes or any other commercial use including, but not limited to, for the benefit of Licensee's customers. If Licensee breaches any of the foregoing

restrictions, then Licensee shall pay to Synplicity a license fee equal to Synplicity's perpetual list price plus maintenance for the commercial version of the SOFTWARE.

**Subscription (Time-Based) License**. If Licensee has obtained a Subscription License to the SOFTWARE, the, in addition to all other terms and conditions herein, the following restrictions apply: (a) Licensee is authorized to use the SOFTWARE only for a limited time (which time is indicated on the quotation or in the purchase confirmation documents); (b) Licensee's right to use the SOFTWARE terminates on the date the subscription term expires as set forth in the quotation or the purchase confirmation documents, unless Licensee has renewed the license by paying the applicable fees.

**Project Based License**. If Licensee has obtained a Project-Based License to the SOFTWARE, in addition to all other terms and conditions herein, the terms of Exhibit A will apply.

**Copy Restrictions**. This SOFTWARE is protected by United States copyright laws and international treaty provisions and Licensee may copy the SOFTWARE only as follows: (i) to directly support authorized use under the license, and (ii) in order to make a copy of the SOFTWARE for backup purposes. Copies must include all copyright and trademark notices.

**Use Restrictions**. This SOFTWARE is licensed to Licensee for internal use only. Licensee shall not (and shall not allow any third party to): (i) decompile, disassemble, reverse engineer or attempt to reconstruct, identify or discover any source code, underlying ideas, underlying user interface techniques or algorithms of the SOFT-WARE by any means whatever, or disclose any of the foregoing; (ii) provide, lease, lend, or use the SOFT-WARE for timesharing or service bureau purposes, on an application service provider basis, or otherwise circumvent the internal use restrictions; (iii) modify, incorporate into or with other software, or create a derivative work of any part of the SOFTWARE; (iv) disclose the results of any benchmarking of the SOFTWARE, or use such results for its own competing software development activities, without the prior written permission of Synplicity; or (v) attempt to circumvent any user limits, maximum gate count limits or other license, timing or use restrictions that are built into the SOFTWARE.

**Transfer Restrictions/No Assignment**. The SOFTWARE may only be used under this license at the designated locations and designated equipment as set forth in the license grant above, and may not be moved to other locations or equipment or otherwise transferred without the prior written consent of Synplicity. Any permitted transfer of the SOFTWARE will require that Licensee executes a "Software Authorization Transfer Agreement" provided by Synplicity. Further, Licensee shall not sublicense, or assign this Agreement or any of the rights or licenses granted under this Agreement, without the prior written consent of Synplicity.

**Security**. Licensee agrees to take all appropriate measures to safeguard the SOFTWARE and prevent unauthorized access or use thereof. Suggested ways to accomplish this include: (i) implementation of firewalls and other security applications, (ii) use of FLEXIm options file that restricts access to the SOFTWARE to identified users; (iii) maintaining and storing license information in paper format only; (iv) changing TCP port numbers every three (3) months; and (v) communicating to all authorized users that use of the SOFTWARE is subject to the restrictions set forth in this Agreement.

**Ownership of the SOFTWARE**. Synplicity retains all right, title, and interest in the SOFTWARE (including all copies), and all worldwide intellectual property rights therein. Synplicity reserves all rights not expressly granted to Licensee. This license is not a sale of the original SOFTWARE or of any copy.

**Ownership of Design Techniques**. "Design" means the representation of an electronic circuit or device(s), derived or created by Licensee through the use of the SOFTWARE in its various formats, including, but not

limited to, equations, truth tables, schematic diagrams, textual descriptions, hardware description languages, and netlists. "Design Techniques" means the data, circuit and logic elements, libraries, algorithms, search strategies, rule bases, techniques and technical information incorporated in the SOFTWARE and employed in the process of creating Designs. Synplicity retains all right, title and interest in and to Design Techniques incorporated in the SOFTWARE, including all intellectual property rights embodied therein, provided that to the extent any Design Techniques are included as part of or embedded within Licensee's Designs, Synplicity grants Licensee a personal, nonexclusive, nontransferable license to reproduce the Design Techniques and distribute such Design Techniques solely as incorporated into Licensee's Designs and not on a standalone basis. Additionally, Licensee acknowledges that Synplicity has an unrestricted, royalty-free right to incorporate any Design Techniques disclosed by Licensee into its software, documentation and other products, and to sublicense third parties to use those incorporated design techniques.

**Protection of Confidential Information**. "Confidential Information" means (i) the SOFTWARE, in object and source code form, and any related technology, idea, algorithm or information contained therein, including without limitation Design Techniques, and any trade secrets related to any of the foregoing; (ii) either party's product plans, Designs, costs, prices and names; non-published financial information; marketing plans; business opportunities; personnel; research; development or know-how; (iii) any information designated by the disclosing party as confidential in writing or, if disclosed orally, designated as confidential at the time of disclosure and reduced to writing and designated as confidential in writing within thirty (30) days; and (iv) the terms and conditions of this Agreement; provided, however that "Confidential Information" will not include information that: (a) is or becomes generally known or available by publication, commercial use or otherwise through no fault of the receiving party; (b) is known and has been reduced to tangible form by the receiving party at the time of disclosure and is not subject to restriction; (c) is independently developed by the receiving party without use of the disclosure; and (e) is released for publication by the disclosing party in writing.

Each party will protect the other's Confidential Information from unauthorized dissemination and use with the same degree of care that each such party uses to protect its own like information. Neither party will use the other's Confidential Information for purposes other than those necessary to directly further the purposes of this Agreement. Neither party will disclose to third parties the other's Confidential Information without the prior written consent of the other party.

**Third Party Software**. Licensee understands and agrees that, although provided to Licensee by Synplicity, Licensee's use of each component library or module comprising the Third Party Software shall be governed by the relevant terms and conditions of the third party's license agreements.

**Termination**. Synplicity may terminate this Agreement immediately if Licensee breaches any provision, including without limitation, failure by Licensee to implement adequate security measures as set forth above. Upon notice of termination by Synplicity, all rights granted to Licensee under this Agreement will immediately terminate, and Licensee shall cease using the SOFTWARE and return or destroy all copies (and partial copies) of the SOFTWARE and documentation.

**Limited Warranty and Disclaimer**. Synplicity warrants that the program portion of the SOFTWARE will perform substantially in accordance with the accompanying documentation for a period of 90 days from the date of receipt. Synplicity's entire liability and Licensee's exclusive remedy for a breach of the preceding limited warranty shall be, at Synplicity's option, either (a) return of the license fee, or (b) providing a fix, patch, work-around, or replacement of the SOFTWARE. In either case, Licensee must return the SOFTWARE to Synplicity with a copy of the purchase receipt or similar document. Replacements are warranted for the

remainder of the original warranty period or 30 days, whichever is longer. Some states/jurisdictions do not allow limitations, so the above limitation may not apply. EXCEPT AS EXPRESSLY SET FORTH ABOVE, NO OTHER WARRANTIES OR CONDITIONS, EITHER EXPRESS, IMPLIED, STATUTORY OR OTH-ERWISE, ARE MADE BY SYNPLICITY OR ITS LICENSORS WITH RESPECT TO THE SOFTWARE AND THE ACCOMPANYING DOCUMENTATION, AND SYNPLICITY EXPRESSLY DISCLAIMS ALL WARRANTIES AND CONDITIONS NOT EXPRESSLY STATED HEREIN, INCLUDING BUT NOT LIM-ITED TO THE IMPLIED WARRANTIES OR CONDITIONS OF MERCHANTABILITY, NONINFRINGE-MENT, AND FITNESS FOR A PARTICULAR PURPOSE. SYNPLICITY AND ITS LICENSORS DO NOT WARRANT THAT THE FUNCTIONS CONTAINED IN THE SOFTWARE WILL MEET LICENSEE'S REQUIREMENTS, BE UNINTERRUPTED OR ERROR FREE, OR THAT ALL DEFECTS IN THE PRO-GRAM WILL BE CORRECTED. Licensee assumes the entire risk as to the results and performance of the SOFTWARE. Some states/jurisdictions do not allow the exclusion of implied warranties, so the above exclusion may not apply.

Limitation of Liability. IN NO EVENT SHALL SYNPLICITY OR ITS LICENSORS OR THEIR AGENTS BE LIABLE FOR ANY INDIRECT, SPECIAL, CONSEQUENTIAL OR INCIDENTAL DAMAGES WHATSOEVER (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF BUSINESS PROF-ITS, BUSINESS INTERRUPTIONS, LOSS OF BUSINESS INFORMATION, OR OTHER PECUNIARY LOSS) ARISING OUT OF THE USE OF OR INABILITY TO USE THE SOFTWARE, EVEN IF SYNPLIC-ITY AND/OR ITS LICENSORS HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. FURTHER, IN NO EVENT SHALL SYNPLICITY'S LICENSORS BE LIABLE FOR ANY DIRECT DAM-AGES ARISING OUT OF LICENSEE'S USE OF THE SOFTWARE. IN NO EVENT WILL SYNPLICITY OR ITS LICENSORS BE LIABLE TO LICENSEE FOR DAMAGES IN AN AMOUNT GREATER THAN THE FEES PAID FOR THE USE OF THE SOFTWARE. Some states/jurisdictions do not allow the limitation or exclusion of incidental or consequential damages, so the above limitations or exclusions may not apply.

Intellectual Property Right Infringement. Synplicity will defend or, at its option, settle any claim or action brought against Licensee to the extent it is based on a third party claim that the SOFTWARE as used within the scope of this Agreement infringes or violates any US patent, copyright, trade secret or trademark of any third party, and Synplicity will indemnify and hold Licensee harmless from and against any damages, costs and fees reasonably incurred that are attributable to such claim or action; provided that Licensee provides Synplicity with (i) prompt written notification of the claim or action; (ii) sole control and authority over the defense or settlement thereof (including all negotiations); and (iii) at Synplicity's expense, all available information, assistance and authority to settle and/or defend any such claim or action. Synplicity's obligations under this subsection do not apply to the extent that (i) such claim or action would have been avoided but for modifications of the SOFTWARE, or portions thereof, other than modifications made by Synplicity after delivery to Licensee; (ii) such claim or action would have been avoided but for the combination or use of the SOFT-WARE, or portions thereof, with other products, processes or materials not supplied or specified in writing by Synplicity; (iii) Licensee continues allegedly infringing activity after being notified thereof or after being informed of modifications that would have avoided the alleged infringement; or (iv) Licensee's use of the SOFTWARE is not strictly in accordance with the terms of this Agreement. Licensee will be liable for all damages, costs, expenses, settlements and attorneys' fees related to any claim of infringement arising as a result of (i)-(iv) above.

If the SOFTWARE becomes or, in the reasonable opinion of Synplicity is likely to become, the subject of an infringement claim or action, Synplicity may, at Synplicity's option and at no charge to Licensee, (a) obtain a license so Licensee may continue use of the SOFTWARE; (b) modify the SOFTWARE to avoid the infringement; (c) replace the SOFTARE with a compatible, functionally equivalent, and non-infringing product, or (d)

refund to Licensee the amount paid for the SOFTWARE, as depreciated on a straight-line 5-year basis, or such other shorter period applicable to Subscription Licenses.

THE FOREGOIN PROVISIONS OF THIS SECTION STATE THE ENTIRE AND SOLE LIABILITY AND OBLIGATIONS OF SYNPLICTY, AND THE EXCLUSIVE REMEDY OF LICENSEE, WITH RESPECT TO ANY ACTUAL OR ALLEGED INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHTS BY THE SOFTWARE (INCLUDING DESIGN TECHNIQUES) AND DOCUMENTATION.

**Export**. Licensee warrants that it is not prohibited from receiving the SOFTWARE under U.S. export laws; that it is not a national of a country subject to U.S. trade sanctions; that it will not use the SOFTWARE in a location that is the subject of U.S. trade sanctions that would cover the SOFTWARE; and that to its knowledge it is not on the U.S. Department of Commerce's table of deny orders or otherwise prohibited from obtaining goods of this sort from the United States.

**Miscellaneous**. This Agreement is the entire agreement between Licensee and Synplicity with respect to the license to the SOFTWARE, and supersedes any previous oral or written communications or documents (including, if you are obtaining an update, any agreement that may have been included with the initial version of the Software). This Agreement is governed by the laws of the State of California, USA excluding its conflicts of laws principals. This Agreement will not be governed by the U. N. Convention on Contracts for the International Sale of Goods and will not be governed by any statute based on or derived from the Uniform Computer Information Transactions Act (UCITA). If any provision, or portion thereof, of this Agreement is found to be invalid or unenforceable, it will be enforced to the extent permissible and the remainder of this Agreement will not constitute a waiver of the right to enforce rights with respect to the same or any other breach.

**Government Users**. If the SOFTWARE is licensed to the United States government or any agency thereof, then the SOFTWARE and any accompanying documentation will be deemed to be "commercial computer software" and "commercial computer software documentation", respectively, pursuant to DFAR Section 227.7202 and FAR Section 12.212, as applicable. Any use, reproduction, release, performance, display or disclosure of the SOFTWARE and accompanying documentation by the U.S. Government will be governed solely by the terms of this Agreement and are prohibited except to the extent expressly permitted by the terms of this Agreement.

June 2005

# Contents

| Amplify ISSP Pro Tutorial Overview2Tutorial Design2Prerequisites4Required Time4Task Outline4Download the Tutorial Files5Directory Structure6 |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Physical Synthesis Design Flow                                                                                                               |

| Start the Amplify ISSP Pro GUI                                                                                                               |

| Create Project                                                                                                                               |

| Set Implementation Options                                                                                                                   |

| Verify Timing Constraints                                                                                                                    |

| Run Constraint Check                                                                                                                         |

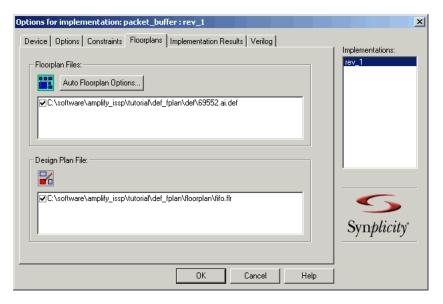

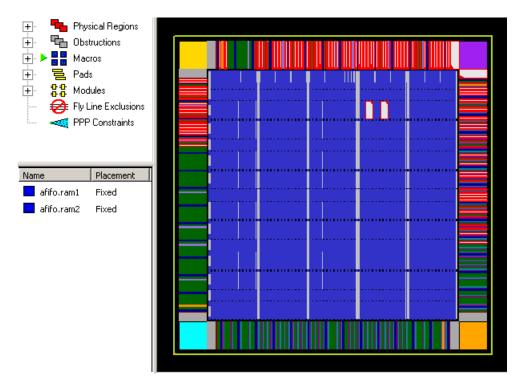

| View the Floorplan                                                                                                                           |

| Synthesize the Design                                                                                                                        |

| Analyze Results40Results Files41Reports41Physical Synthesis Reports49HDL Analyst Views51Physical Analyst View54                              |

| For More Information                                                                                                                         |

Preface

# Amplify ISSP Pro Tutorial for ISSP-90

| • | Amplify ISSP Pro Tutorial Overview    2 |

|---|-----------------------------------------|

| • | Physical Synthesis Design Flow 10       |

| • | Start the Amplify ISSP Pro GUI 12       |

| • | Create Project                          |

| • | Set Implementation Options              |

| • | Verify Timing Constraints               |

| • | Run Constraint Check                    |

| • | View the Floorplan                      |

| • | Synthesize the Design                   |

| • | Analyze Results                         |

| • | For More Information                    |

## Amplify ISSP Pro Tutorial Overview

The goal of this tutorial is to familiarize you with the main features of the Amplify ISSP Pro physical synthesis tool so that you can use it to achieve optimal results for your own designs.

## **Tutorial Design**

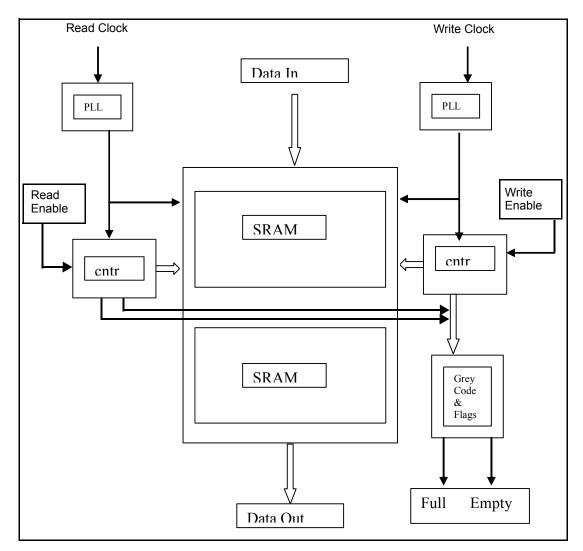

This tutorial uses a FIFO design which is configured to support independent read and write clock signals. The depth and width of the FIFO are configured by setting a parameter in the RTL code. The FIFO used in this tutorial is configured and optimized for a  $1023 \times 32$  bit data buffer. FIFO circuits can be used in the following types of applications: processors, controllers, and various communications circuits.

See Figure 1 on page -3 for a graphical view of the FIFO architecture. For more information about the operation and functionality of the FIFO, see the vendor design specification documentation.

Figure 1: FIFO Design

#### **Prerequisites**

To complete the tutorial example in the following sections:

- You need a working knowledge of logic design synthesis and basic window operations.

- You should read Chapter 1, *Getting Started* of the User Guide, which presents a brief introduction to the Synplify ASIC and Amplify ASIC family of tools. Also, read through Chapter 2, *User Interface Overview* of the Reference Manual, which covers features and views of the Amplify ASIC Physical Synthesis UI.

- Create a local copy of the tutorial directory and be sure to delete the packet\_buffer.prj file so you can create your own. See the *Directory Structure* on page 2-6 for information.

#### **Required Time**

The tutorial should take about 2 to 3 hours to complete.

## Task Outline

Tasks in this tutorial include the following:

- Bring up the Amplify ISSP Pro GUI

- Open the project

- Check Implementation Options

- Check Timing Constraints

- Run Constraint Check

- View Floorplan

- Synthesize the Design

- Analyze Results

#### **Download the Tutorial Files**

You can download the tutorial design and project files along with the tutorial instructions from the Synplicity Technical Resource Center.

- 1. To access the Synplicity Technical Resource Center:

- Select WEB->Go to Resource Center from the Project menu. Then, go to the Tutorial section within the Technical Resource Center.

- Go to http://trc.synplicity.com/tutorials/index.html

- 2. Find the Amplify ISSP Pro tutorial for the applicable release and download these files for the platform you desire.

- 3. Unzip the tutorial files.

- On a PC, use Winzip to extract the tutorial files.

- On a UNIX platform, type the following at the command line:

```

gunzip amplify issp.tar.gz

```

Then, to extract the tutorial files, type this at the command line:

```

tar -xvf amplify issp.tar

```

- 4. Copy the amplify\_issp/tutorial directory to your working area. Keep the directory structure, because the tutorial is based on this structure. Refer to *Directory Structure* on page 2-6. When you work on your own designs, you can set up the structure as you want.

- **Note:** The tutorial instructions are contained in the tutorial.pdf, which is also located in this directory. Open this file when you are ready to begin the tutorial.

- 5. Make sure you have read and write privileges for the project files.

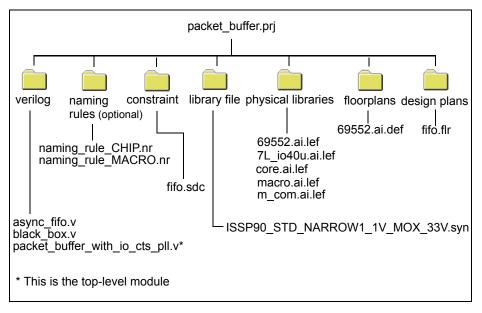

#### **Directory Structure**

This section contains the directory structure for tutorial, located at:

```

install directory/amplify issp/tutorial

```

where *install\_directory* is the path to where your Amplify ISSP Pro tutorial files and instructions are located.

Figure 2 shows the tutorial directory in the Project view of the UI that reflects the virtual directory structure that is automatically created by the tool as you build your design project.

#### Figure 2: Tutorial Directory Structure

However, with your own designs, you can create any directory structure that works best.

**Note:** You can delete or rename the packet\_buffer.prj and the fifo.sdc files in this directory so you can create your own as part of the tutorial exercises.

#### **Input Files**

Here is a brief description of the input files:

- .v contains the HDL source files. packet\_buffer\_with\_io\_cts\_pll.v is the top level module.

- constraint:fifo.sdc user-specified constraint file, contains the timing constraints.

- packet\_buffer.prj packet\_buffer project file, contains all the information required to complete a design. This file contains references to source files, and specifications for the target ASIC technology.

- physical libraries:69552.ai.lef, core.ai.lef, 7L\_io40u.ai.lef, m\_com.ai.lef, macro.ai.lef — physical cell library information that includes process layers, design rules associated with interconnect layers, via cells and parasitics per layer. The libraries also include size, symmetry, and pin characteristics of standard cells and blockages of each macro.

- floorplans:69552.ai.def device floorplan file which contains information such as die size, rows and sites, pin locations, macro locations and orientation, or obstructions.

- design plans:fifo.flr device floorplan editor file which contains floorplan information and allows you to place, move, or change the orientation of macros, draw soft and hard placement obstructions, define regions constraints for instances of RTL modules, and create top-level bounding box constraints.

- library:ISSP90\_STD\_NARROW1\_1V\_MOX\_33V.syn ISSP-90 technology library in Synplicity internal format. This file contains the merged .sel files, which describe the parameters and specifications for the target technology.

- naming rules:naming\_rule\_CHIP.nr and naming\_rule\_MACRO.nr includes a naming rules file for the chip and the macros such that the rules are defined and applied during synthesis.

#### **Output Files**

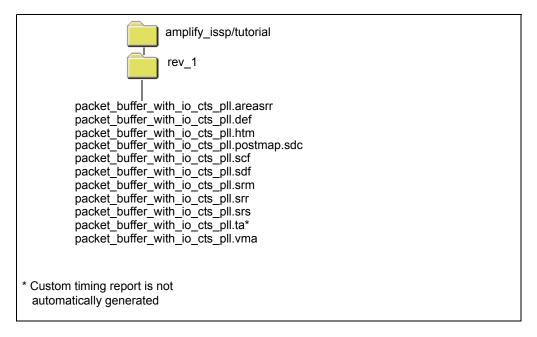

Figure 3 shows the directory structure for the results files, given the default name rev\_1. You specify the directory for the results when you define implementation options for the project.

Figure 3: Results Directory Structure

Here is a brief description of the result files that are written to the implementation during synthesis:

- .areasrr a hierarchical report containing area information for each of the modules in the design.

- .def output floorplan file, contains updated information for any of the following: die size, rows and sites, pin locations, macro locations and orientation, or obstructions.

- .htm HTML format of the log file containing the synthesis results. See the .srr file for a description of its contents.

- \_ilm\_lib.v verilog file containing black box description of all library cells.

- .postmap.sdc timing constraint file that is automatically created for in-place optimization.

- .scf Synopsys-style timing constraint file, used for forward annotation in place-and-route tools. See Appendix C, *Translating Synopsys Constraints* of the *Reference Manual* for information using these constraints in the Amplify ISSP Pro environment.

- .sdf standard delay format file containing pin-to-pin timing delay values for nets and instances and timing requirements for sequential elements.

- .srm output by the mapper stage of the process, contains the actual technology-specific mapped design. This is the representation displayed through the technology view in HDL Analyst and the floorplan view in Physical Analyst.

- .srr log file containing the synthesis results. The *project\_name.srr* file contains all warnings and errors encountered during synthesis as well as performance information such as clock frequency, critical paths and run times. There is also information on area, cell usage and FSM extraction. To view this file, click on the View Log button in the Project view.

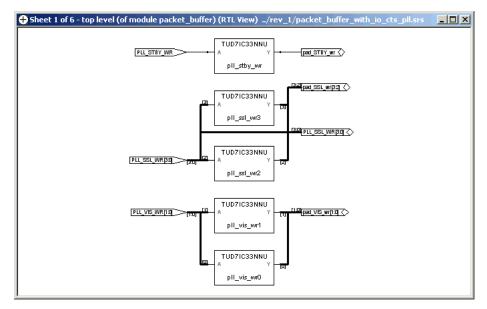

- .srs output by the compiler stage of the process, contains the RTL level (schematic) view of the design. This is the representation displayed through the RTL view in HDL Analyst and the Floorplan Viewer.

- .ta customized timing report (not generated by default). This file is created when you generate a special timing report using the Timing Report->Generate command.

- .vma structural Verilog design netlist for place and route and verification.

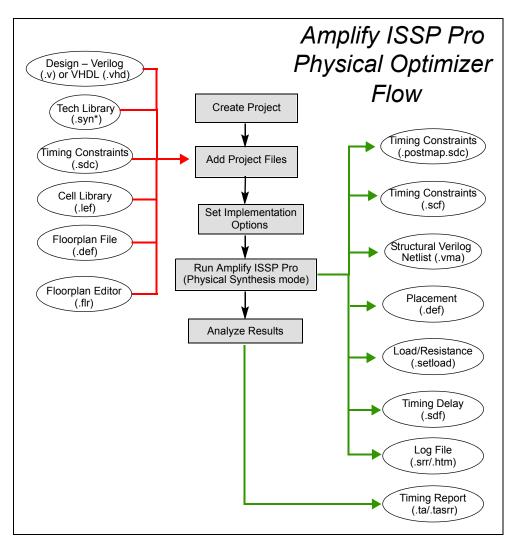

## Physical Synthesis Design Flow

The typical flow for Amplify ISSP Pro Physical Optimizer is shown in the following figure.

- 1. Start the Amplify ISSP Pro GUI.

- 2. Create Project:

- Add source files

- Specify top-level module/entity

- 3. Set Implementation Options:

- Choose target technology

- Specify operating conditions and wire load model

- Set optimization switches

- Specify results directory

- 4. Verify Timing Constraints:

- Compile the design before creating the constraints to initialize SCOPE

- Set timing constraints through SCOPE

- Modify timing constraints as appropriate to improve results

- 5. Run Constraint Check.

- 6. View the Floorplan.

- 7. Synthesize the Design.

- Click Run.

- 8. Analyze Results:

- Output Files

- Area Report

- Timing Report

- Physical Analyst

- Log File Warnings

- 9. When design goals are met, go on to place and route and/or verification.

## Start the Amplify ISSP Pro GUI

How you start the tool depends on your environment.

- To start the software from a Windows platform, select Programs->Synplicity-> Amplify ISSP Pro from the Start menu.

- To start the software from a UNIX command line, type:

```

install directory/bin/amplify issp pro

```

where: *install\_directory* is the path to where your Amplify ISSP Pro software is installed.

For more details on bringing up the tool, installation and licensing, see:

- Installation and Licensing in Chapter 1, Getting Started of the User Guide

- Getting Help in Chapter 1, Get Started of the Reference Manual

- Starting the ASIC Synthesis Tools in Chapter 1, Get Started of the Reference Manual

## **Create Project**

Before synthesizing a design, you need to create a project for it. The project contains all the elements required to run synthesis on a design such as technology library, design files, constraint files, and so on. A project can have one or more associated revisions, also called implementations. Each time you change options, libraries, constraints, or optimization switches to enhance performance, you should create a new implementation for the project. This way you can compare the results of each of your implementations to determine the best combination of files and settings that yield the most optimum results for the design.

To open the project:

- 1. From the Project view, do one of the following:

- Click on the Open Project button

- Click on the project button in the toolbar (**P**)

- Select File->Open Project

| Open Project                                     |                 | × |

|--------------------------------------------------|-----------------|---|

| Existing Project<br>New Project<br>New Workspace | Recent Projects |   |

| OK<br>Cancel                                     |                 |   |

Figure 4: Create Project

2. Click on New Project.

This creates a new project with an associated revision in the project view; default names are proj and rev\_1.

| C:\software\ampli  | ify_issp\tutorial\proj.prj *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |       |      | _ 🗆 X    |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------|------|----------|

| Open Project       | Bun Amplify <sup>®</sup> ISSP Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |       |      |          |

| Close Project      | Tech Lib: <not selected=""></not>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |       |      |          |

| Add File           | C:\software\amplify_issp\tutorial\rev_1<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | rev_1 | Туре | Modified |

| Change File        | international i |  |       |      |          |

| New Impl           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |       |      |          |

| Impl Options       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |       |      |          |

| View Log           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |       |      |          |

| Physical Synthesis |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |       |      |          |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | •     |      | Þ        |

Figure 5: Create Project

Add the design files to the project.

3. Click on the Add File button.

| Select Files to Add to Project                 |           | ? ×           |

|------------------------------------------------|-----------|---------------|

| Look in: 🔁 tutorial                            | - 🔶 🖻     | ) 💣 🎟 -       |

| Constraints                                    |           |               |

| def_fplan                                      |           |               |

| ISSP_DEMO_lib                                  |           |               |

|                                                |           |               |

|                                                |           |               |

|                                                |           |               |

| -                                              |           |               |

| File name:                                     |           |               |

| Files of type: Verilog Files (*.v;*.vma;*.vmd) | ▼         |               |

| VHDL Library:                                  |           |               |

| Files To Add To Project: 🔽 Use Relat           | ive Paths |               |

|                                                |           | <- Add All    |

|                                                |           | <- Add        |

|                                                |           | Remove All -> |

|                                                |           | Remove ->     |

|                                                |           | ОК            |

|                                                |           | Cancel        |

|                                                |           |               |

- 4. Open the rtl\_sims folder. Make sure Files of type field is showing either All Files (\*) or Verilog Files (\*.v).

- 5. For this exercise, add all the Verilog files in the folder. Click on the <-Add All button, then click OK.

| Select Files to Add to Project                                   | ? ×           |

|------------------------------------------------------------------|---------------|

| Look in: 🧰 rtl_sims 💌 🗲 🕻                                        | • 🖬 📩         |

| async_fifo.v     black_box.v     packet_buffer_with_io_cts_pll.v |               |

| File name:                                                       | j             |

| Files of type: Verilog Files (*.v;*.vma;*.vmd)                   | ]             |

| VHDL Library:                                                    |               |

| Files To Add To Project: 🔽 Use Relative Paths                    |               |

| .\rtl_sims\async_fifo.v<br>.\rtl_sims\black_box.v                | <- Add All    |

| . \rtl_sims\packet_buffer_with_io_cts_pll.v                      | <- Add        |

|                                                                  | Remove All -> |

|                                                                  | Remove ->     |

|                                                                  | ОК            |

|                                                                  | Cancel        |

Figure 6: Add Verilog Files

A virtual design directory structure is created in the Project view. Figure 7 shows the UI after adding the design files.

| C:\software\ampli  | ify_issp\tutorial\proj.prj *                                        |        |      |          |  |

|--------------------|---------------------------------------------------------------------|--------|------|----------|--|

| Open Project       | Bun Amplify <sup>®</sup> IS                                         | SP Pro |      |          |  |

| Close Project      | Tech Lib: <not selected=""></not>                                   |        |      |          |  |

| Add File           | C:\software\amplify_issp\tutorial\rev_1                             | rev_1  | Туре | Modified |  |

| Change File        | En terilog<br>En terilog<br>En terilog                              |        |      |          |  |

| New Impl           | i async_nu.v<br>i black_box.v<br>ii packet_buffer_with_io_cts_pll.v |        |      |          |  |

| Impl Options       |                                                                     |        |      |          |  |

| View Log           |                                                                     |        |      |          |  |

| Physical Synthesis |                                                                     |        |      |          |  |

| ,                  |                                                                     |        |      | Þ        |  |

|                    | J                                                                   |        |      |          |  |

Figure 7: Add Source Files

6. Specify the top-level module.

| C:\software\ampli  | fy_issp\tutorial\pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oj.prj *            |   |           |      |      | _ 🗆 🗙    |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---|-----------|------|------|----------|

| Open Project       | Bun Amplify <sup>®</sup> ISSP Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |   |           |      |      |          |

| Close Project      | Tech Lib: <not selected=""></not>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |   |           |      |      |          |

| Add File           | C:\software\amplify_i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | issp\tutorial\rev_1 |   | ev_1      | Туре |      | Modified |

| Change File        | Figure 1 (project)     Veriog     Seriog     Figure 2 (project)     Figure 2 (project) |                     |   | top-level |      |      |          |

| New Impl           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |   |           |      |      |          |

| Impl Options       | • rev_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     | ľ |           | mod  | lule |          |

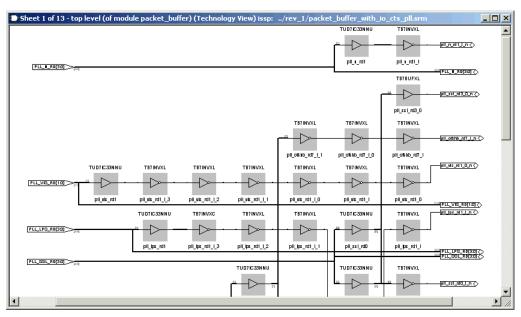

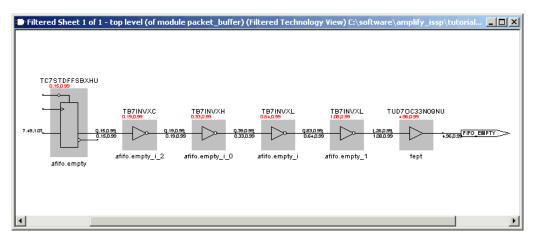

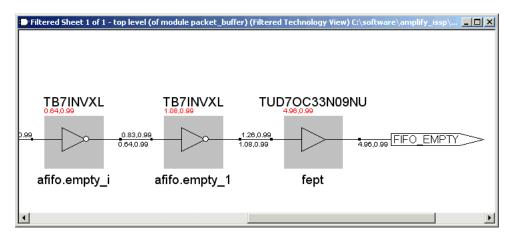

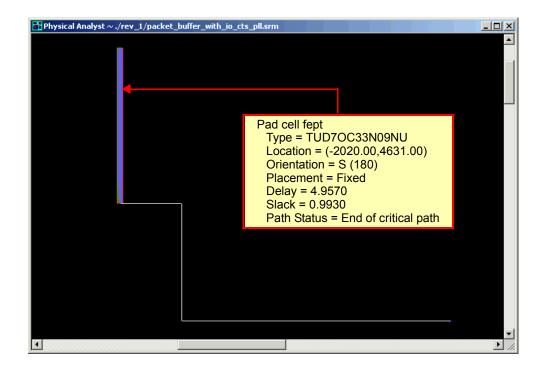

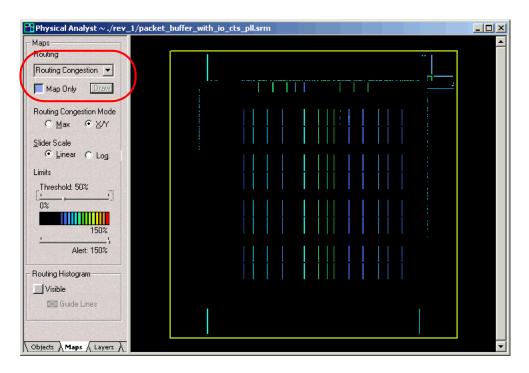

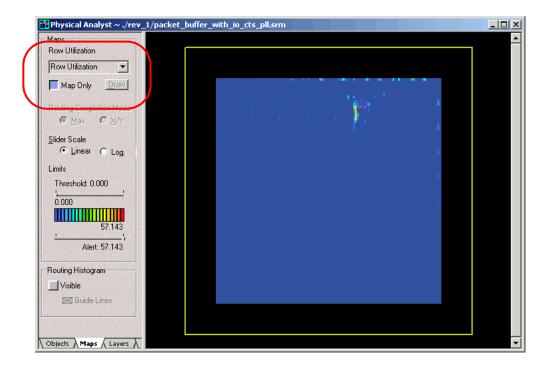

| View Log           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |   |           |      |      |          |