Tutorial : Path Delay Fault Testing of ASIC's - Leon SoC

By Karthik Sundaramurthy, ECE 599 - Summer 2007, Submitted on 08/10/2007

ATPG Testing Slides with Notes (pdf)

Path Delay Testing Slides with Notes (pdf)

Introduction

This tutorial is intended to give a basic introduction into path delay fault testing of integrated circuits.

Path delay fault tests use a fault model where the defects may occur at one or more points along a path, usually a critical timing path.

For path delay fault tests, the propagation path is fully specified to ensure that the complete path is tested. The target

paths for path delay fault tests are usually provided by a STA tool like PrimeTime. The tutorial is comprised of 3

important steps and has to be performed with three separate tools from Synopsys.

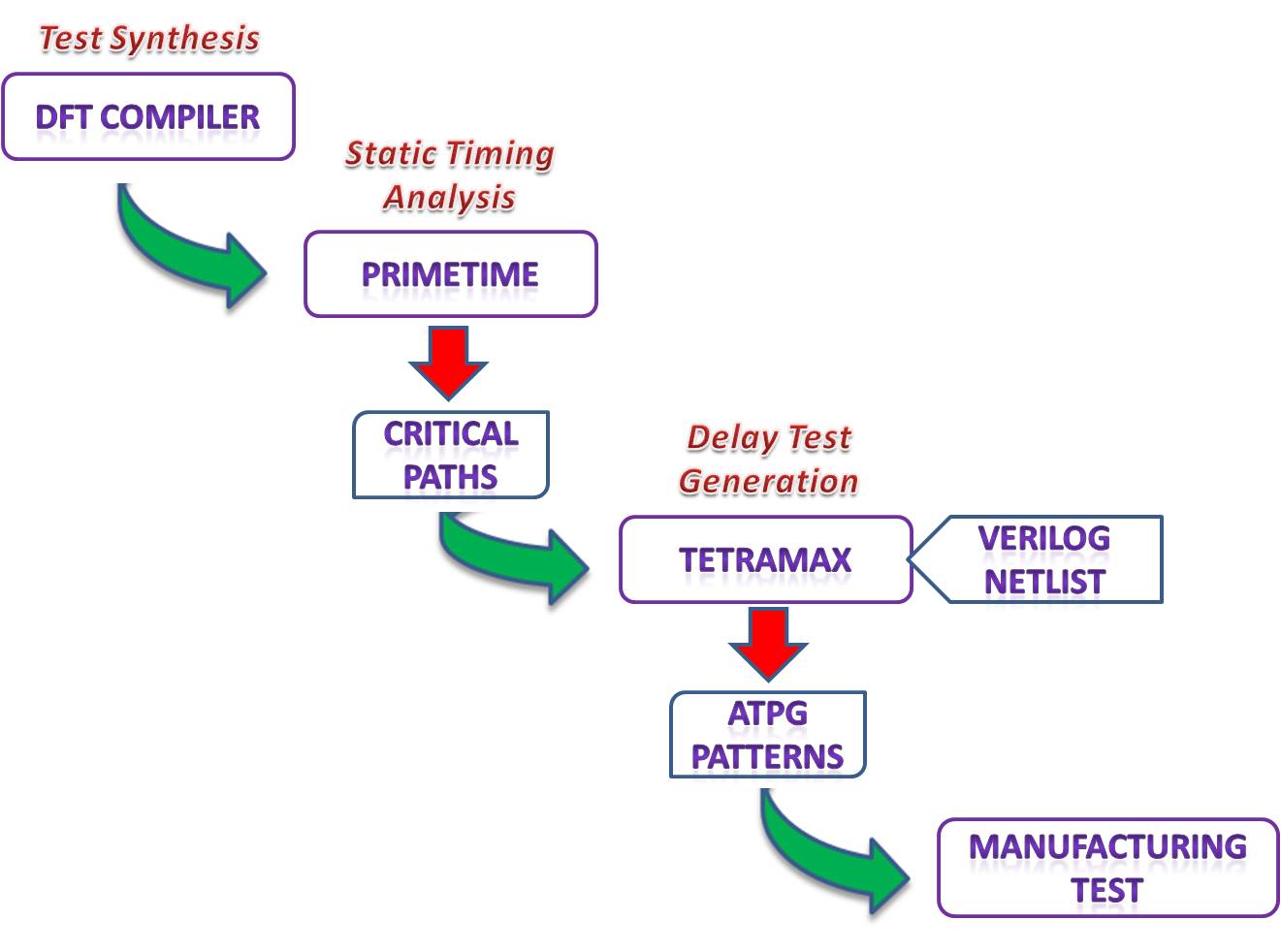

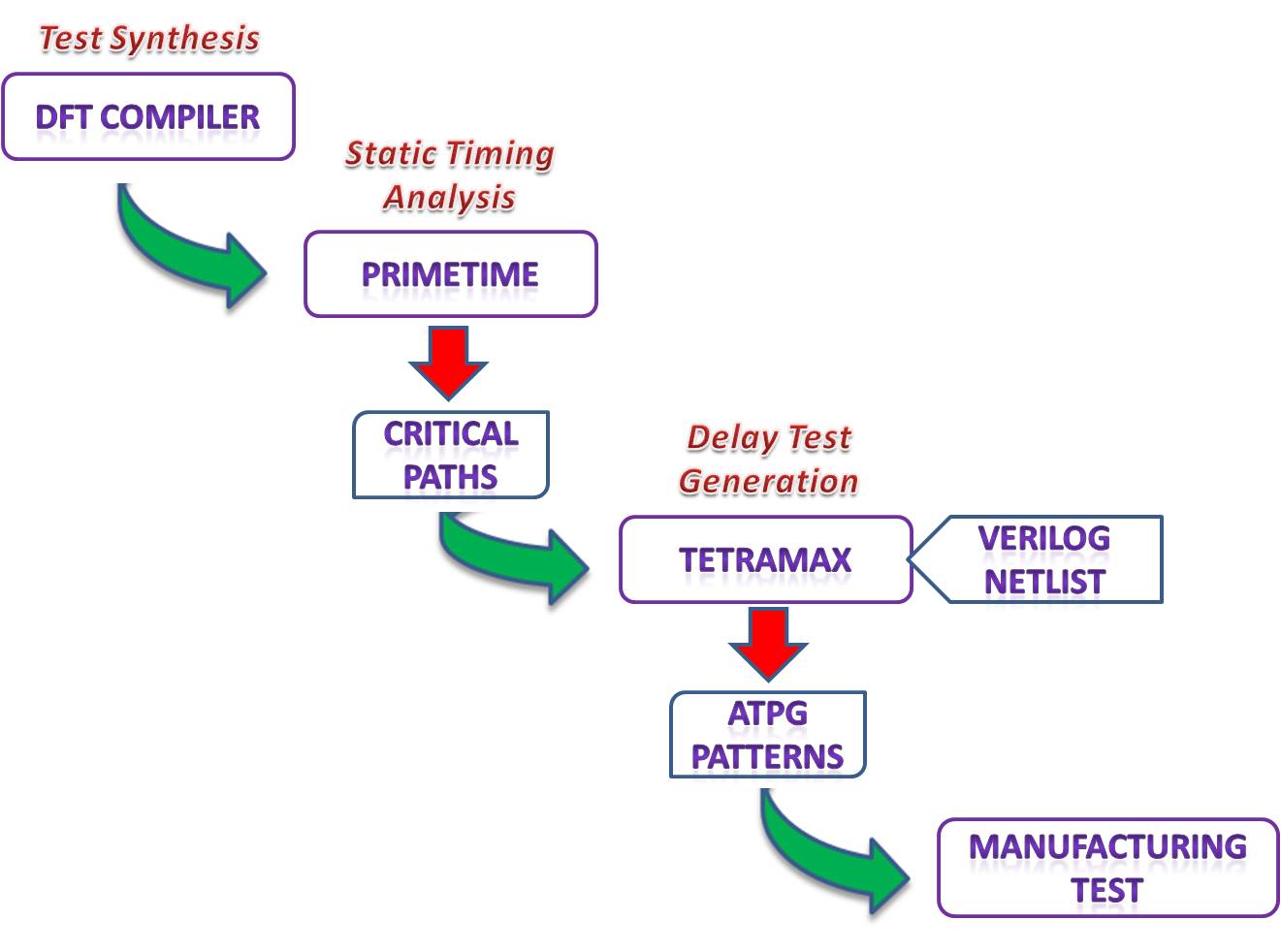

Figure : Path Delay Fault Testing Flow

As shown in the figure above, the tools that will be used for this tutorial are:

* Synopsys Design Compiler to synthesize the design.

* Synopsys Primetime to perform static timing analysis and determine the most critical paths.

* Synopsys TetraMax to generate vectors to perform manufacturing tests.

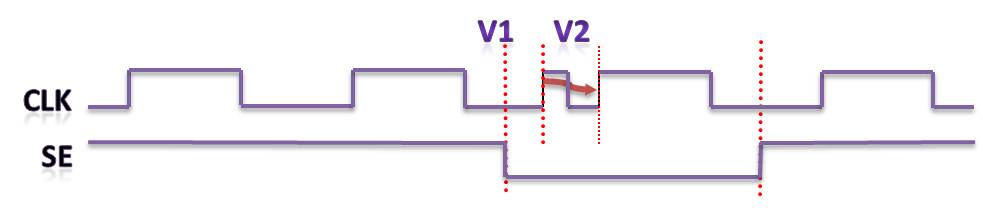

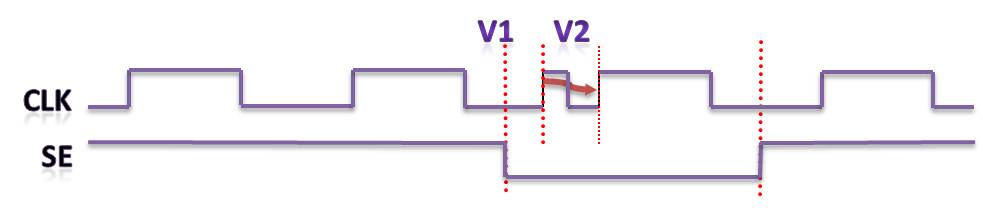

Path delay tests are in general two-pattern tests. The first vector sensitizes the path by applying non-controlling

values to the off-state inputs. The second vector propagates the transiton through the combinational path under test.

Figure : Path Delay Fault Testing vector pattern

1. Create a working directory and copy over the files

cp -R /usr/cad/course/path_delay_testing soc_test

cd soc_test

2. Extract the tar'ed files and invoke ModelSim

tcsh

source setup.csh

mentor_tools

cmd_1a

This command extracts all the zipped files and compiles them using Modelsim. This command also sets up the directory structure

and files required for the following steps.

3. Setting up Synopsys environment and synthesizing the Leon Soc design files

synopsys_latest_tools

start_synth

The first two commands set up the Synopsys environment. The command leon_synth_scan perfroms synthesis of the

Leon SoC with test. All the flip-flops in the design are replaced with scan type or multiplexed flip-flops.

The scan structure thus inserted during synthesis leads to a increase in the overall area of the design. Thus the

design has to be optimized using the compile command.

Note: The synthesis step could take anywhere from 50 - 65 minutes. This is due to the large number of files associated with

the design.

A detailed explanation of the steps used during synthesis has been provided here

4. Static timing analysis using Synopsys PrimeTime

start_primetime

This command performs static timing analysis on the synthesized verilog netlist to obtain the most critical paths in the design.

Primtime can be configured to output the critical paths in a text format. However, TetraMax (ATPG tool) requires the paths

in a different format. So, a TCL procedure (write_delay_paths) has been supplied by TetraMax to produce the PrimeTime output in

a TetraMax acceptible format. This has been defined in the file pt2tmax.tcl

An executable file has been created for this step. A detailed explanation has been provided here

A sample file which shows the critical path is shown here

5. Automatic Delay Test Pattern Generation using Synopsys TetraMax

start_tmax

This step is used to generate ATPG patterns for the delay test for the most critical paths generated by PrimeTime.

The critical paths are read into TetraMax during pattern generation.

A detailed explanation of the steps used during pattern generation has been provided here