## Graphical Design Tutorial for HDL Author and HDL Designer

Software Version 2003.1

7 May 2003

Copyright © Mentor Graphics Corporation 1996-2003. All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

Contractor/manufacturer is: Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Web site: http://www.hdldesigner.com

This is an unpublished work of Mentor Graphics Corporation.

### **Table of Contents**

| About This Manual                        | viii |

|------------------------------------------|------|

| Introduction                             | viii |

| Other Documentation                      |      |

| Copying Text From the Acrobat Viewer     |      |

| Example Designs                          |      |

| Typographic Conventions                  | i-xi |

| Chapter 1                                |      |

| VHDL Timer Exercise                      | 1-1  |

| Specification                            | 1-1  |

| Set Library Mapping                      | 1-2  |

| Set the Default Language                 | 1-4  |

| Create a Block Diagram                   |      |

| Edit the Title Block Template            | 1-7  |

| Add Blocks                               | 1-8  |

| Add Embedded Blocks                      | 1-9  |

| Add Ports and Signals                    | 1-10 |

| Add a Bundle and Global Connector        |      |

| Save the Block Diagram                   | 1-13 |

| Edit the Block and Signal Names          |      |

| Add an Embedded HDL Text View            | 1-19 |

| Add a Panel and Edit the Title Block     | 1-21 |

| Create a Child State Diagram             | 1-23 |

| Add States and Transitions.              |      |

| Save the State Diagram                   | 1-27 |

| Edit the States                          | 1-28 |

| Edit the Transitions                     |      |

| Create a Hierarchical State Diagram      | 1-32 |

| Complete the Hierarchical State Diagram  | 1-34 |

| Editing State Machine Properties         |      |

| Set Generation Properties.               |      |

| Set Checks for HDL Generation            |      |

| Generate HDL for the State Machine       |      |

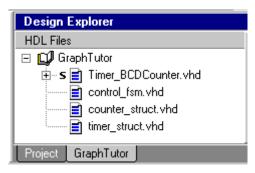

| Display HDL Files in the Design Explorer | 1-43 |

| Import the BCDCounter Design Unit | 1-44 |

|-----------------------------------|------|

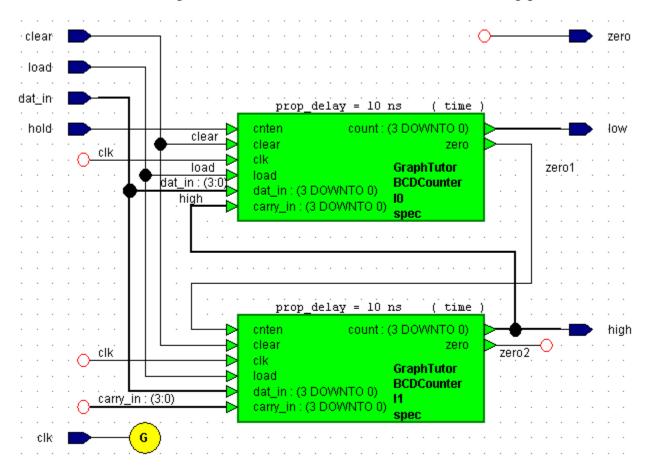

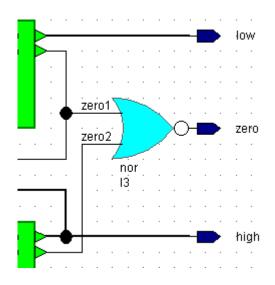

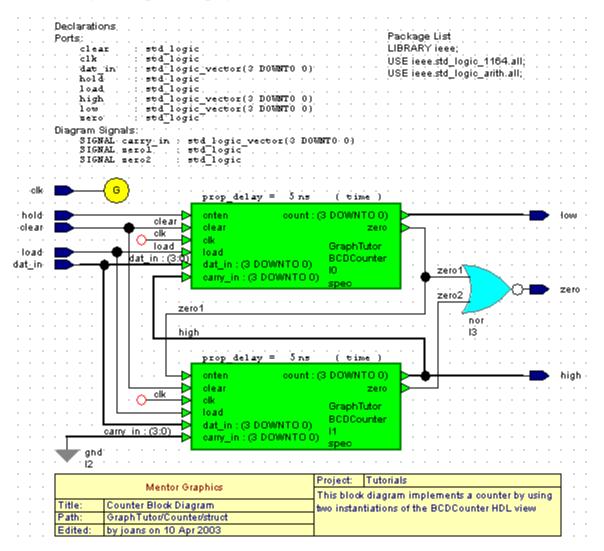

| Create a Child Block Diagram      | 1-46 |

| Edit the Generic Mapping          |      |

| Add ModuleWare Components         | 1-53 |

| Add a User Declaration            | 1-55 |

| Create a Truth Table              | 1-57 |

| Edit the Truth Table              | 1-58 |

| Set Truth Table Properties        | 1-60 |

| Browse the Timer Design           |      |

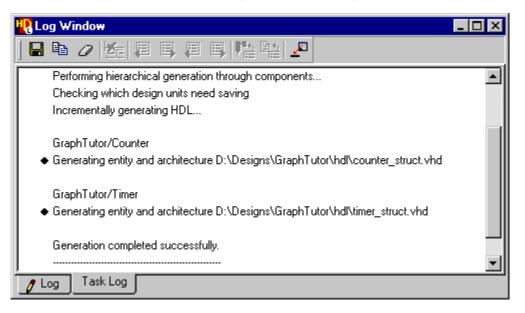

| Generate HDL for the Hierarchy    | 1-62 |

| Edit the Timer Symbol.            | 1-64 |

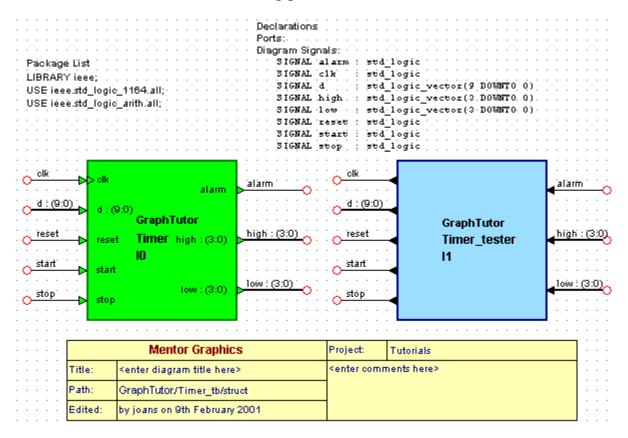

| Create a Test Bench               |      |

| Import the Tester Design Unit     | 1-67 |

| Instantiate the Imported Tester   | 1-68 |

| Generate HDL for the Test Bench   | 1-70 |

| Browse the Completed Design       | 1-72 |

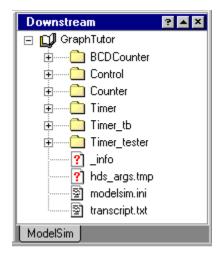

| Setup the Downstream Tools        | 1-73 |

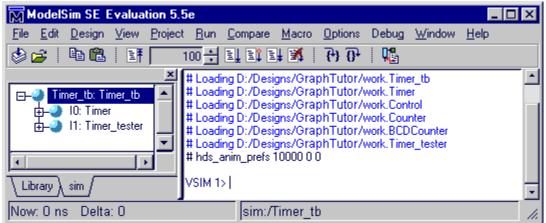

| Run the ModelSim Flow             | 1-74 |

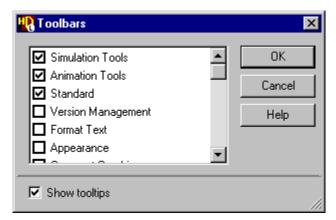

| Setup the Simulator Windows       | 1-76 |

| Add Simulation Probes             | 1-77 |

| Enable Animation                  | 1-78 |

| Simulate the Design               | 1-80 |

| Review the Animation              | 1-82 |

| Debugging From ModelSim           | 1-83 |

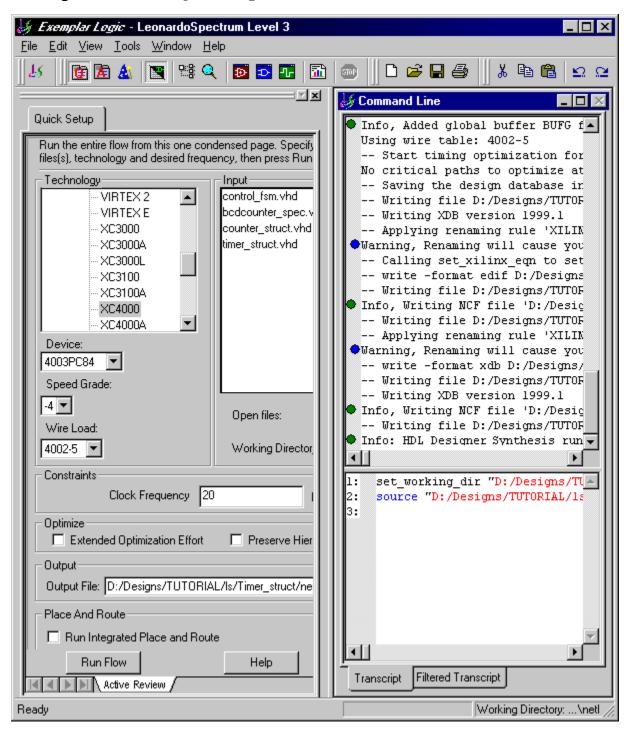

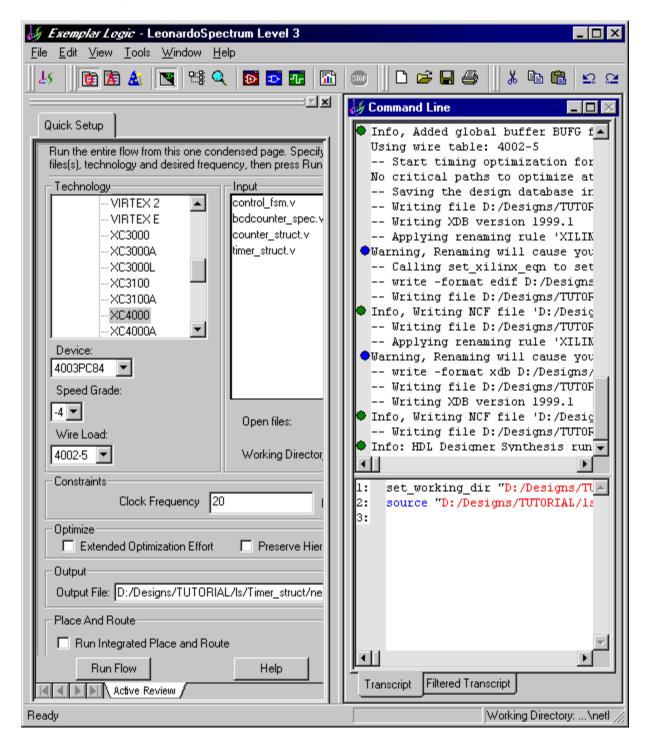

| Run the LeonardoSpectrum Flow     | 1-85 |

| Using the Example VHDL Design     | 1-89 |

|                                   |      |

| Chapter 2                         | 0.1  |

| Verilog Timer Exercise            |      |

| Specification                     |      |

| Set Library Mapping               |      |

| Set the Default Language          |      |

| Create a Block Diagram            |      |

| Edit the Title Block Template     |      |

| Add Blocks                        |      |

| Add Embedded Blocks                      | 2-9  |

|------------------------------------------|------|

| Add Ports and Signals                    | 2-10 |

| Add a Bundle and Global Connector        | 2-12 |

| Save the Block Diagram                   | 2-13 |

| Edit Block and Signal Names              | 2-15 |

| Add an Embedded HDL Text View            | 2-19 |

| Add a Panel and Edit the Title Block     | 2-21 |

| Create a Child State Diagram             | 2-23 |

| Add States and Transitions               | 2-26 |

| Save the State Diagram                   | 2-27 |

| Edit the States                          | 2-28 |

| Edit the Transitions                     | 2-30 |

| Create a Hierarchical State Diagram      | 2-32 |

| Complete the Hierarchical State Diagram  | 2-34 |

| Editing State Machine Properties         |      |

| Set Generation Properties                | 2-39 |

| Set Checks for HDL Generation            | 2-41 |

| Generate HDL for the State Machine       | 2-42 |

| Display HDL Files in the Design Explorer | 2-43 |

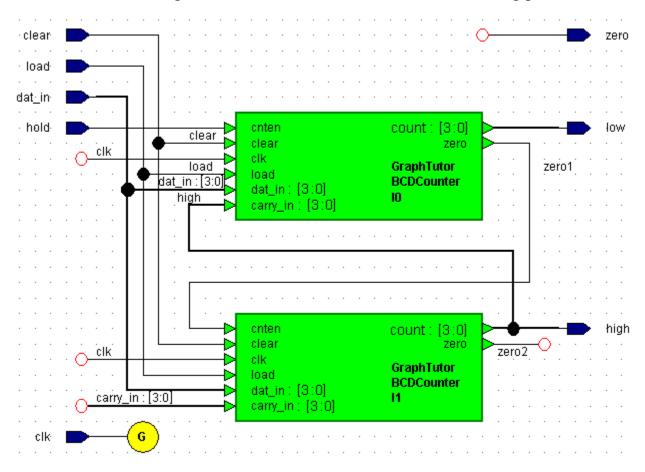

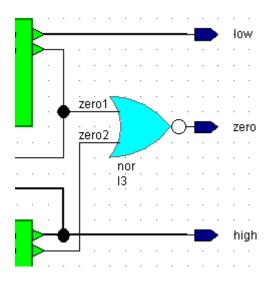

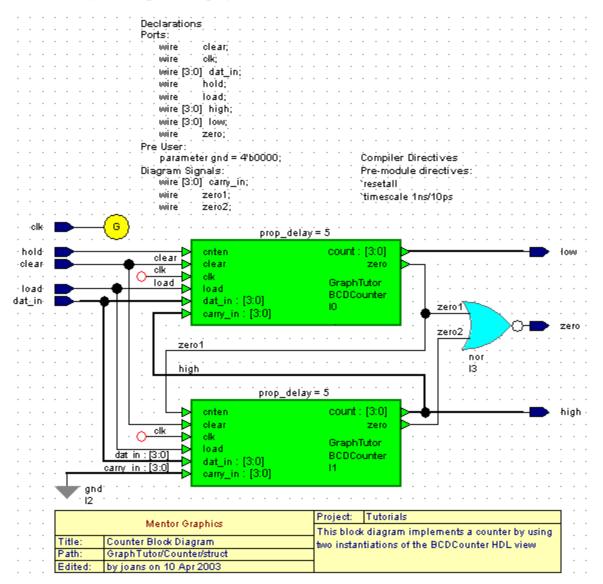

| Import the BCDCounter Design Unit        | 2-44 |

| Create a Child Block Diagram             | 2-46 |

| Edit the Parameter Mapping               | 2-52 |

| Add ModuleWare Components                | 2-53 |

| Add a User Declaration                   | 2-55 |

| Create a Truth Table                     |      |

| Edit the Truth Table                     | 2-58 |

| Set Truth Table Properties               | 2-59 |

| Add a Module Declaration                 | 2-61 |

| Browse the Timer Design                  | 2-62 |

| Generate HDL for the Hierarchy           | 2-63 |

| Edit the Timer Symbol                    | 2-65 |

| Create a Test Bench                      | 2-66 |

| Import the Tester Design Unit            | 2-68 |

| Instantiate the Imported Tester          | 2-69 |

| Generate HDL for the Test Bench          | 2-71 |

| Browse the Completed Design                  |        |

|----------------------------------------------|--------|

| Setup the Downstream Tools                   |        |

| Run the ModelSim Flow                        |        |

| Setup the Simulator Windows                  |        |

| Add Simulation Probes                        |        |

| Enable Animation                             |        |

| Simulate the Design                          |        |

| Review the Animation                         |        |

| Debugging From ModelSim                      |        |

| Run the LeonardoSpectrum Flow                |        |

| Using the Example Verilog Design             |        |

| Chapter 3                                    |        |

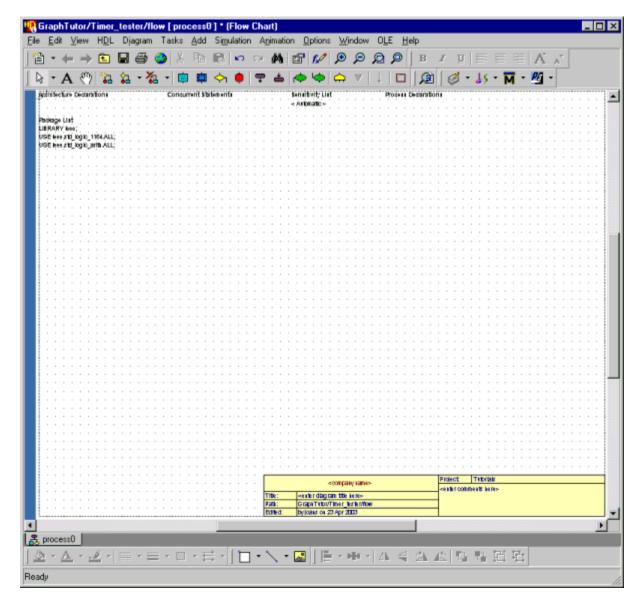

| Creating a VHDL Flow Chart                   |        |

| Introduction                                 | 2 1    |

| Introduction<br>Create the Tester Flow Chart |        |

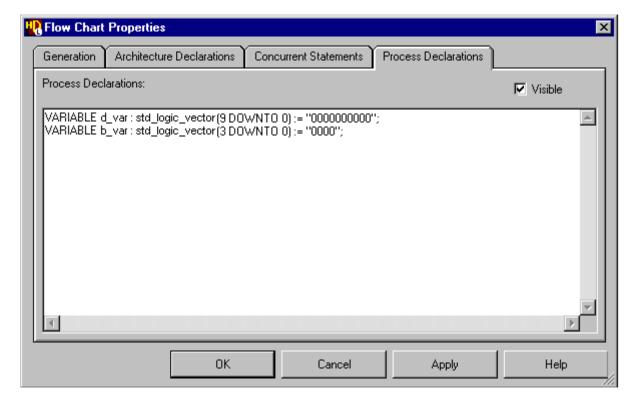

| Set Flow Chart Properties                    |        |

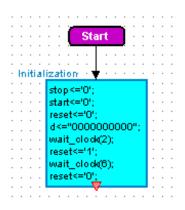

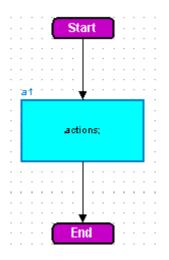

| Add a Start Point and Action Box             |        |

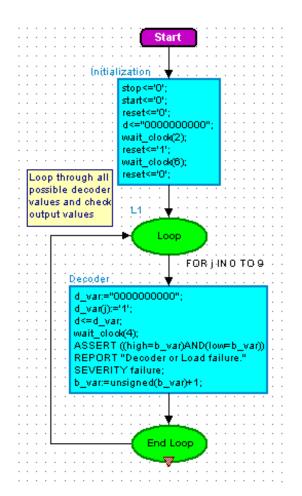

| Add a Loop and an Associated Comment         |        |

| Add an Action Box                            |        |

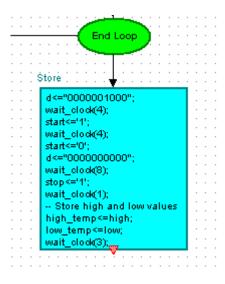

| Add a Hierarchical Action Box                |        |

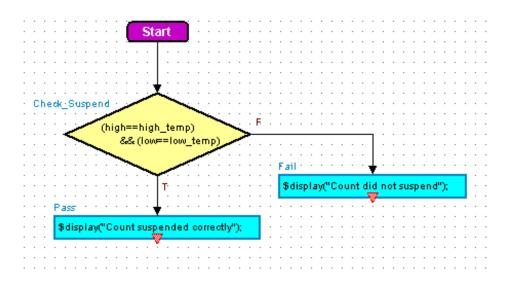

| Add a Decision Box                           |        |

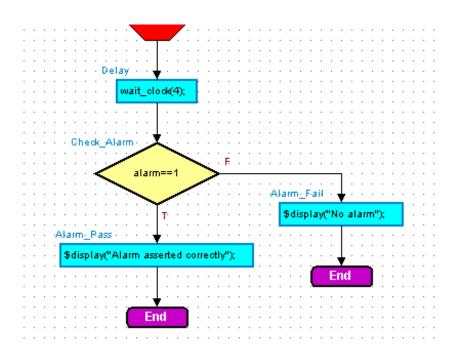

| Add Wait Boxes                               |        |

| Copy the Decision Tree                       |        |

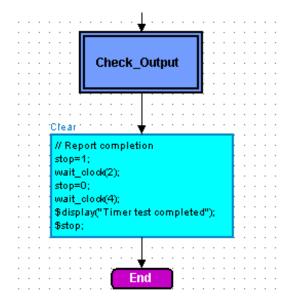

| Completing the Flow Chart                    |        |

| Using HDL2Graphics                           |        |

| Chanter 4                                    |        |

| Chapter 4<br>Creating a Verilog Flow Chart   | 4-1    |

|                                              | ······ |

| Introduction                                 | 4-1    |

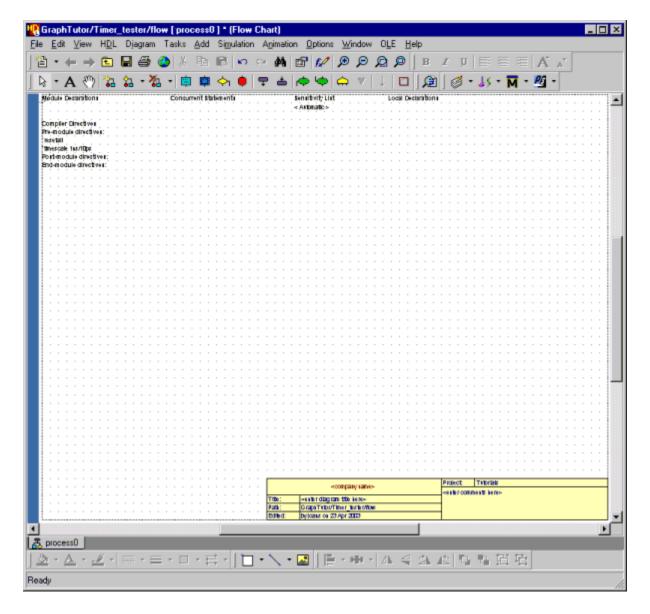

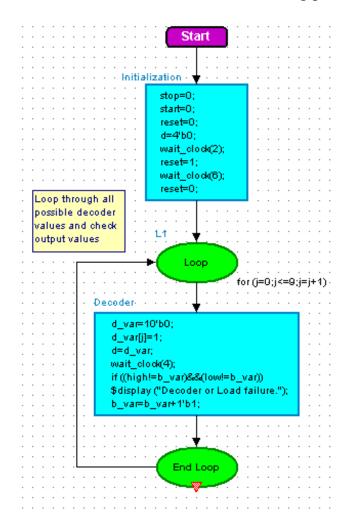

| Create the Tester Flow Chart                 |        |

| Set Flow Chart Properties                    | 4-4    |

| Add a Start Point and Action Box             |        |

| Add a Loop and an Associated Comment         |        |

|                                              |        |

| Add an Action Box             | 4-11 |

|-------------------------------|------|

| Add a Hierarchical Action Box | 4-12 |

| Add a Decision Box            | 4-14 |

| Add a Wait Box                | 4-16 |

| Copy the Decision Tree        | 4-18 |

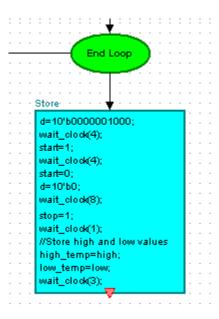

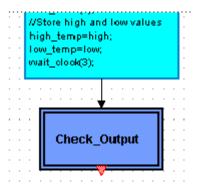

| Completing the Flow Chart     |      |

| Using HDL2Graphics            | 4-21 |

#### **Trademark Information**

**End-User License Agreement**

# **About This Manual**

## Introduction

This manual provides a self-paced tutorial with step-by-step procedures for creating a simple timer design and test bench using VHDL or Verilog graphical views.

You are advised to perform the separate the *Design Management Tutorial* before attempting this tutorial to learn about creating projects and managing your design data.

You can learn about using tabular Interface-Based Design views by performing the separate *Interface-Based Design Tutorial*.

Procedures for completing the tutorial using VHDL are given in Chapter 1 and procedures for using Verilog in Chapter 2. If you want to complete both versions of the tutorial, you should create a separate library for each version of the design.

The tutorial covers the basic procedures required to fully define and verify a design using graphical views. The full tutorial can be completed by users of the HDL Author or HDL Designer tools using block diagram, symbol, state diagram, truth table and flow chart views.

The completed design can be compiled and simulated if ModelSim is available and synthesized if the LeonardoSpectrum tools are available.

The main tutorial includes a test bench which uses a flow chart view. The flow chart can be imported from example HDL code or can optionally be created by following the procedures in Chapter 3 and Chapter 4.

Although the procedures do not describe the use of other tools, the HDL Designer Series includes support for many alternative downstream tool interfaces and it should be possible to use the generated HDL with any of these interfaces. However, you must consider any limitations of your external tool. In particular, some VHDL tools may not support the standard IEEE packages used in the tutorial and you should substitute an appropriate alternative package.

The tutorial assumes that users have some knowledge of the issues for digital hardware design and experience of the VHDL or Verilog language.

It is possible to complete the tutorial without this knowledge by carefully copying the language syntax given in the procedures. However, a separate VHDL or Verilog training course is recommended in order to fully appreciate how the power of HDL design can be exploited using graphical design methods.

The illustrated examples have been laid out for maximum readability in the Acrobat viewer or on the printed page. When you are creating your own design, it is advisable to allow extra space between diagram objects so that you can easily route signals between them.

All user commands in the tutorial procedures are referenced using menu path (shown in bold text) or toolbar button. However, many commands can also be accessed using the shortcut bar or keyboard shortcuts. Refer to Shortcut Keys in the **Quick Reference Index** which can be accessed from the **Help** menu for lists of the available shortcut keys.

The tutorial is divided into sections containing numbered procedures which must be performed for the each section of the tutorial to be completed successfully. If you are working from a printed copy of the tutorial, you are recommended to tick off each numbered procedure as you complete it to ensure no steps are omitted.

Unnumbered paragraphs provide additional information or give advice on other ways to perform an operation. The procedure numbers are continuous through each major section and its subsections but restart for each major section, for example when introducing a new editor.

## **Other Documentation**

The HDL Designer Series documentation (including the release notes and this user manual) can be accessed from the *HDL Designer Series Bookcase* which is available from the **Help** menu in each application window.

Self-paced tutorials can be accessed from the *HDL Designer Series Tutorials* bookcase which can be accessed from the main bookcase or directly from the **Help** menu.

All documents are provided in Adobe Acrobat portable document format (PDF). The Acrobat reader can be installed from the HDL Designer Series CD-ROM if it is not already available.

Refer to the *Release Notes* for information about new features or upgrading from a previous product.

Refer to the *Start Here Guide for the HDL Designer Series* for information about the HDL Designer Series tools, supported platforms and configurations.

Refer to the *HDL Designer Series User Manual* for information about the design manager and procedures common to all HDL Designer Series tools.

Refer to the *HDL Designer Series Graphical Editors User Manual* for information about the graphical editors.

Refer to the *DesignPad Text Editor User Guide* for information about the built in HDL text editor.

Refer to the *Debug Detective User Guide* for information about Debug Detective.

Refer to the *ModuleWare Reference Guide* for information about the ModuleWare library.

A number of quick reference help pages can be accessed by choosing the **Quick Reference Index** from the **Help** menu. Further quick reference pages can be accessed using the Help buttons provided on many of the application dialog boxes.

Information about the state diagram, flow chart and truth table editors is provided as help topics which can be accessed by choosing **Help Topics** from the **Help** menu in these editors.

## **Copying Text From the Acrobat Viewer**

You can copy text from this document by choosing the (Text Select) tool button or  $\bigvee$  shortcut key in the Acrobat viewer and choosing Copy from the Acrobat Edit menu (or using the cm +  $\fbox{}$  shortcut).

The text can be pasted into a text editor (or application dialog box) using the  $\Box + \forall$  shortcut or the **Paste** menu option if one is provided in the destination window. In the graphic editors, you can use the **Paste Special** option to explicitly paste text from the system clipboard.

If you copy HDL text from a tutorial help page, check that punctuation characters are copied correctly. In particular, line feed characters may not be translated on UNIX systems and may need to be re-entered.

## **Example Designs**

Completed examples of the VHDL and Verilog tutorial designs are provided in the HDL Designer Series installation. These can be browsed for reference or can be compiled, simulated and animated directly if you modify their downstream library mapping to use a writable downstream directory.

Refer to the sections "Using the Example VHDL Design" on page 1-89 or "Using the Example Verilog Design" on page 2-90 for more information.

## **Typographic Conventions**

The following conventions have been used in this manual:

| Style  | Usage                                                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold   | Menu options and command line switches.                                                                                                           |

| Italic | Pathnames (and object names derived from file names).<br>Also used for manual titles (for example, <i>ModuleWare</i><br><i>Reference Guide</i> ). |

| Style        | Usage                                               |

|--------------|-----------------------------------------------------|

| Courier font | Monospaced Courier font is used for code examples.  |

| Links        | Cross references within the text are shown in blue. |

When pathnames (or window titles derived from pathnames) are shown in this tutorial, the PC convention ( $\backslash$ ) is used.

# Chapter 1 VHDL Timer Exercise

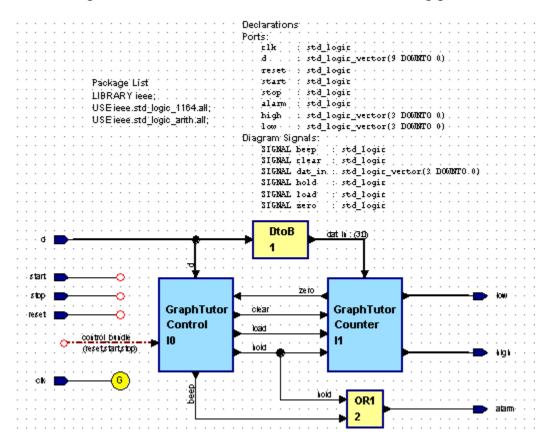

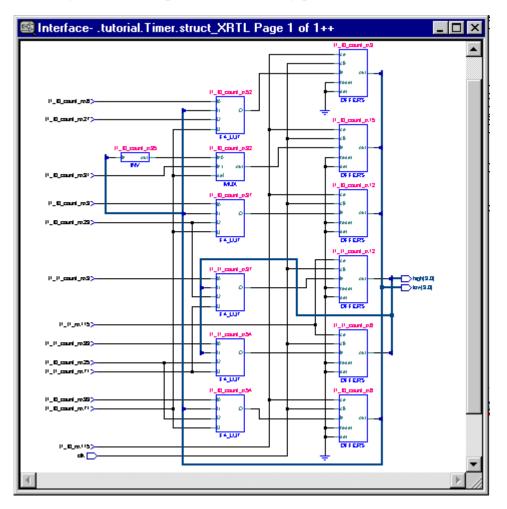

This exercise creates a simple timer using block diagrams and a control block described as a hierarchical state machine. A simple truth table is used to decode four-bit binary codes from the ten-bit input bus. The design is completed using a re-usable component described by a HDL text view.

A test bench is created using a flow chart which can be used as a test harness to simulate the generated VHDL for the timer design. The simulation results can be displayed as animation on the flow chart and state machine to assist in debugging the design. The verified timer design is then synthesized.

The instructions assume that a Model*Sim* simulator and the LeonardoSpectrum synthesis tools are available. However, the VHDL generated from the diagrams can also be used by other compatible downstream tools that are available on your system.

## **Specification**

The timer outputs time data on two four-bit buses representing low and high values. There is also a logic output signal which triggers an audible alarm. The data input is provided on a ten-bit bus and control is provided by start, stop, reset and clock signals. These signals are summarized in the following table:

#### Inputs

start (logic signal) stop (logic signal) reset (logic signal) clk (logic signal) d (10-bit bus)

#### Outputs

high (4-bit bus) low (4-bit bus) alarm (logic signal)

## **Set Library Mapping**

For this tutorial, you can use an existing project such as the project you created for the Design Management tutorial but should create a new library mapping for your design data. The library mapping defines the logical location of the directories containing your design data. The source graphical objects, HDL and downstream data can be stored at any writable locations on your available file system but are typically saved below a common root directory.

1. To set library mapping, click the w New Library icon in the Project group on the shortcut bar or choose Library from the New cascade of the File menu in the design manager window to display the New Library wizard:

| ł | 💦 New Library - Lib | огату Туре                                                                                                           | X |

|---|---------------------|----------------------------------------------------------------------------------------------------------------------|---|

|   | Library Type        |                                                                                                                      | 1 |

|   | Regular             | A Library that can be compiled and generated<br>from. This library can also have mappings for<br>Version Management. |   |

|   | O Protected         | A re-useable HDS library that cannot be compiled<br>or generated.                                                    |   |

|   | 🔿 Downstream Only   | A library that has been compiled.eg vendor libraries.                                                                |   |

|   |                     | Next > Cancel Help                                                                                                   |   |

- 2. Choose the **Regular** library type and click the Next> button to display the library name page.

- 3. Enter a logical library name (for example: *GraphTutor*) and check that the **Auto** option is set in the dialog box.

- 4. Specify or browse for the pathname for the root directory that will contain your library data (for example, *D:\Designs* or *\$HOME/designs*).

Library names and pathnames can be entered using upper, lower or mixed case but note that UNIX systems are case sensitive and the case used for pathnames should match the file structure. (On a PC, library names are case sensitive but pathnames are case insensitive.) Notice that the source HDL directory is named <*root\_directory*>\*GraphTutor*\*hdl* and the source graphics directory is named <*root\_directory*>\*GraphTutor*\*hds*.

| 😯 New Library                                                                                                                                                          | × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| The library mappings can be created automatically based on the root directory<br>and library name, alternatively you may explicitly specify them.(i.e. Uncheck 'Auto') |   |

| Library Name:                                                                                                                                                          |   |

| GraphTutor 🔽 🔽 Auto                                                                                                                                                    |   |

| Root directory:                                                                                                                                                        |   |

| D:\Designs Browse                                                                                                                                                      |   |

| Source Directories                                                                                                                                                     |   |

| HDL: D:\Designs\GraphTutor\hdl                                                                                                                                         |   |

| HDS: D:\Designs\GraphTutor\hds                                                                                                                                         |   |

| < Back Next > Cancel Help                                                                                                                                              |   |

5. Click the Next> button to display the last page of the wizard.

| 🔩 New Library                                                                                                                                                                                       |                                          |        |               | ×    |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|---------------|------|--|--|--|--|--|--|--|

| 🔽 Make this the De                                                                                                                                                                                  | fault library                            |        |               |      |  |  |  |  |  |  |  |

| The default location for opening, saving and other operations.                                                                                                                                      |                                          |        |               |      |  |  |  |  |  |  |  |

| 🔽 Open this library i                                                                                                                                                                               | Open this library in the design explorer |        |               |      |  |  |  |  |  |  |  |

| Exploring the library will automatically create the directories<br>corresponding to the mappings, if they do not exist.<br>A library can also be explored by double clicking in the<br>projects tab |                                          |        |               |      |  |  |  |  |  |  |  |

| 🔲 Create new desig                                                                                                                                                                                  | jn objects                               |        |               |      |  |  |  |  |  |  |  |

| The wizard to cre<br>via the File->New                                                                                                                                                              |                                          |        | o be accessed |      |  |  |  |  |  |  |  |

|                                                                                                                                                                                                     | < Back                                   | Finish | Cancel        | Help |  |  |  |  |  |  |  |

- 6. Set the Make this the Default library and Open this library in the design explorer options.

- 7. Click the Finish button to close the wizard.

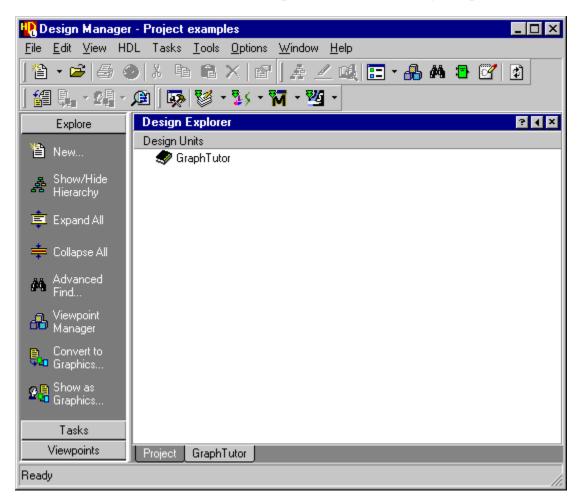

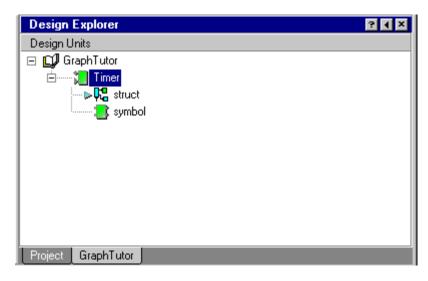

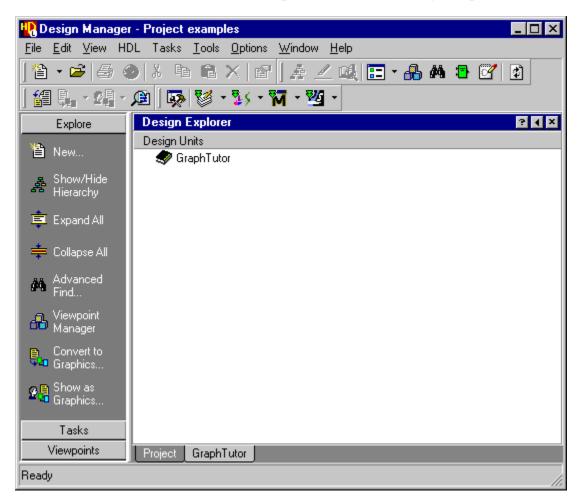

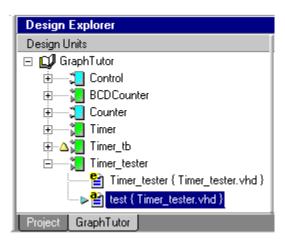

The source design data directories you specified in the wizard are created and the library (shown as a closed "book") is opened in a new design explorer window:

The mapping for the location of compiled data will be defined automatically when the design is compiled.

## Set the Default Language

A set of default preferences are loaded when you invoke a HDL Designer Series tool for the first time. There are separate tabbed dialog boxes for the main settings, VHDL and Verilog options, HDL2Graphics import options, version management, animation settings and master preferences for each type of graphical diagram. The preference dialog boxes can be accessed from the **Options** menu.

1. Choose **Main** from the **Options** menu to display the Main Settings dialog box.

| Main Settings                                               |                    |                         |           | ×      |

|-------------------------------------------------------------|--------------------|-------------------------|-----------|--------|

| General Text Diagrams                                       | Tables Ch          | ecks   Save   User      | Variables |        |

| Automatically downcase Des                                  | ign Unit and Viev  | w names when entered    |           |        |

| Toolbar Buttons                                             | - Filename disp    | play                    |           |        |

| Remain active                                               | Show as            | logical name (e.g. MY_F | ïle)      |        |

| C Activate once only                                        | C Show act         | tual filename (e.g. @m@ | y_@file)  |        |

| Team Preferences Directory L                                | ocation            |                         |           |        |

| <ul> <li>Single User</li> </ul>                             |                    | O Team Membe            | r         |        |

|                                                             |                    |                         |           | Browse |

| Team Administrator mode                                     |                    |                         |           |        |

|                                                             |                    |                         |           |        |

| Temp Directory                                              |                    |                         |           |        |

| C:\TEMP                                                     |                    |                         |           | Browse |

| - Remote Simulation Directory L                             | ocation            |                         |           |        |

| \$HDS_TEAM_VER\remote                                       |                    |                         |           | Browse |

| Desire & Constluction Descretor File                        |                    |                         |           |        |

| Project Synthesis Property File<br>\$HDS_TEAM_VER\generatio |                    | ini                     |           |        |

|                                                             | Intprops (is_props |                         |           | Browse |

| Default Custom Code Generati                                | on Tel Seript      |                         |           |        |

| \$HDS_TEAM_VER\generatio                                    | n\tcl\SynPropsT    | emplate.tcl             |           | Browse |

| Units                                                       |                    | ault Language for New \ | /iews     |        |

| Units for printing: Inches                                  |                    | /HDL O Verilog          |           |        |

|                                                             |                    |                         | 3         |        |

|                                                             | OK                 | Cancel                  | Apply     | Help   |

2. Select the **General** tab and ensure that **VHDL** is set as the default language to be used for new graphic editor views. Use the OK button to confirm your choice.

All other preferences can be left with their default values for this tutorial.

## **Create a Block Diagram**

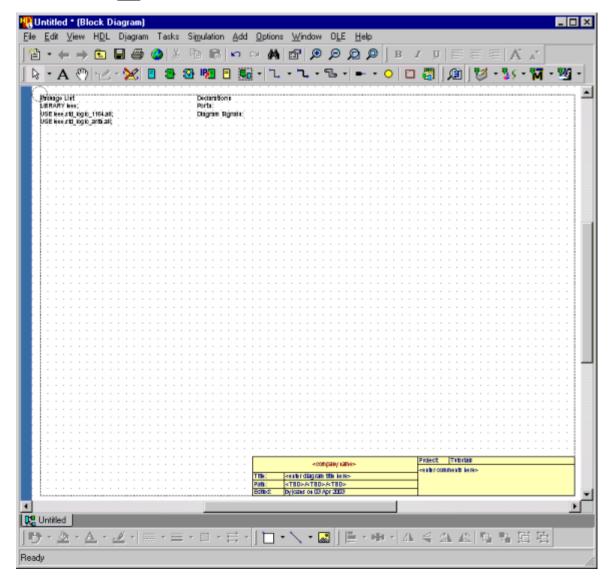

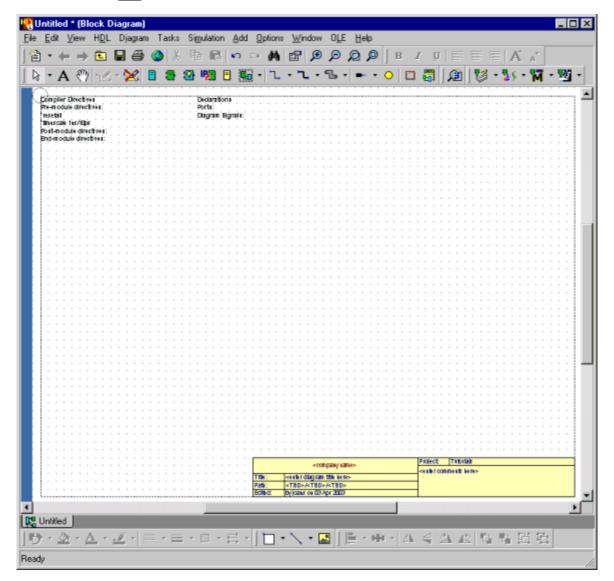

- 1. Use the Diagram from the Graphical View cascade of the dropdown menu to create a new untitled block diagram.

- 2. Use the  $\square$  button to view the entire diagram:.

Notice the five toolbars at the top and three toolbars at the bottom of the diagram. The toolbar buttons provide quick access to many of the most frequently used editing and formatting commands. The block diagram is a blank sheet except for a background grid, a package list (with the standard IEEE libraries *std\_logic\_1164* and *std\_logic\_arith*) and empty text fields with labels for *Declarations*, *Ports* and *Diagram Signals*.

The diagram also shows page boundaries for the default printer and a copy of the default title block.

### **Edit the Title Block Template**

A title block is automatically added to all new diagrams if the Add Title Blocks in new diagrams option is set in your diagram preferences. The default title block is a template with default locations for your company name, diagram title and comments. The template incorporates internal variables which automatically enter the current project name, your login name and the current date. Internal variables are also used to enter the logical pathname for the design. This path is initially shown as <TBD>/<TBD> but the internal variables are converted to show the library, design unit and view name when you save the diagram.

- 3. Click twice on <company name> in the default title block to display a popup edit box and replace the default text by the name of your company.

- 4. Select the title block by clicking with the mouse so that the selection handles are displayed and choose **Save Title Block** from the **File** menu.

5. A dialog box is displayed with a warning that saving the title block cannot be undone. Click the Yes button to proceed.

The title block is saved as a team resource at the location specified in your preferences and will be used as the default template in new diagrams. If shared team preferences have been set up on your system, there may already be a read-only team template stored at this location.

Refer to the *HDL Designer Series User Manual* for information about how you can add and modify title blocks.

### **Add Blocks**

6. Use the 🔳 button (or choose **Block** from the **Add** menu) to add two blocks on the diagram as shown below:

| Pack<br>LIBR/<br>USE<br>USE | age  | List |     |     |     |      |      |     |     |   |   |   |   |   |   |   | D | ecl | ar | ati | oņs | 5.<br>5 |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|-----------------------------|------|------|-----|-----|-----|------|------|-----|-----|---|---|---|---|---|---|---|---|-----|----|-----|-----|---------|------|---|------|-----|----|---|---|---|---|---|---|---|---|---|---|---|

| LIBR                        | ARY  | iee  | e;  |     | -   |      |      |     | -   | - | - |   |   | - | - | - | P | ort | s: |     |     | -       | -    | - | -    |     |    |   |   |   | - | - | - | - | - | - | - | - |

| USE                         | ieee | .std | _10 | gić | _11 | 64   | .al  | 1;  |     |   |   |   |   |   |   |   | D | iag | ŗа | m   | Sig | jņa     | als: | : |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| USE                         | ieee | .std | _lo | gic | ari | ith. | all  | :   | •   | • | • | • | • | • | • | • | • |     |    | •   |     |         | •    | • | •    | •   | •  | • | • | • | • | • | • | • | • | • | • | • |

|                             | • •  |      |     |     |     | •    | •    | •   | •   | • | • | • | • | • | • | • | • | •   | •  | •   | •   | •       | •    | • | •    | •   | •  | • | • | • | • | • | • | • | • | • | • | • |

|                             | • •  |      | • • |     | •   | •    |      | •   | •   | • | • | • | • | • | • |   | • |     | •  | •   |     | •       | •    | • | •    | •   | •  |   | • | • | • |   | • |   |   | • | • | • |

|                             | • •  |      | • • |     | •   | •    | •    | •   | •   | • | • | • |   | • |   |   | • |     | •  | •   | •   |         | •    | • | •    | •   | •  | • | • | • | • |   | • |   |   | • | • | • |

| · ·                         | • •  |      | • • |     | •   | •    | •    | •   | •   | • | • | • | • | • | • | • | • | •   | •  | •   | •   | •       | •    | • | •    | •   | •  | • | • | • | • | • | • | • |   | • | • | • |

| · ·                         | • •  |      | • • | •   | •   | •    | •    | •   | •   | · | • | • | • | • | • | • | • | •   | •  | •   | •   | •       | •    | · | ·    | ·   | ·  | • | · | • | • | • | • | • | • | • | • | • |

| · ·                         | • •  |      | • • |     | •   | •    | •    | •   | •   | • | • | • |   | • |   |   | • |     | -  | •   | •   |         | •    | • | •    | •   | •  | • | • | • | • | • | • |   |   | • | • | • |

| •                           | • •  |      | • • |     | •   | •    | •    | •   | ·   | • | · | · | · | • | · | • | • | •   | •  | •   | •   | •       | •    | · | ·    | ·   | ·  | • | • | • | • | • | · | • | • | • | • | • |

| •                           | • •  |      | • • |     | •   | •    | •    | •   | •   | · | • | • | • | • | • | • | • | •   | •  | •   | •   | •       | •    | · | ·    | ·   | ·  | • | • | • | · | • | • | • | • | • | • | • |

| •                           | • •  |      | • • | •   | •   | •    | •    | •   | ·   | · | · | · | · | • | • |   | • |     | ·  | •   | •   | •       | •    | · | ·    | ·   | ·  | • | · | • | · |   | · |   |   | • | • | • |

| •                           | • •  |      | • • | •   | •   | •    | •    | •   | ·   | · | · | · | · | • | · |   | • |     | ·  | •   |     | ·       | •    | · | ·    | ·   | ·  | • | · | • | · |   | · |   |   | • | • | • |

| · ·                         | • •  |      | • • | •   | •   | ·    | ·    | ·   | ·   | • | · | · | · | • | · |   | - | •   | ·  | ·   | •   | ·       | •    | · | ·    | ·   | ·  | • | · | · | • | • | · | • | • | - | - | • |

| · ·                         | • •  |      | • • | •   | •   | ·    | ·    | ·   | ·   | • | · | · | · | • | · |   | - |     | ·  | ·   | •   | ·       | •    | · | ·    | ·   | ·  | • | · | • | • | • | · | • |   | - | - | - |

| · ·                         | • •  |      |     | •   | •   | ·    | ·    | ·   | ·   | • | · | · | · | - | · |   | - |     | ·  | ·   |     | ·       | •    | · | ·    | ·   | ·  | · | · | · | • |   | · |   |   | - | - | - |

| •                           | • •  |      | • • | •   |     | ·    | ·    | •   | ·   | · | · | · | · |   | · | - | - | -   | ·  | •   |     | ·       |      | · | ·    | ·   | ·  |   | · | • | · |   | · |   | - | - | • | - |

| •                           |      |      |     | •   | •   | ·    | ·    | ·   | ·   | • | · | · | · | - | · |   | - |     | ·  | ·   |     | ·       |      | · | ·    | ·   | ·  | · | · | · | • |   | · |   |   | - | - | - |

| •                           | • •  |      |     | Ē   |     |      |      |     |     |   |   |   | · |   |   | - | - | -   | ·  | ·   |     | П       |      |   |      |     |    |   |   |   | · |   | · |   |   | - |   | - |

| •                           |      |      |     | 1   |     |      |      |     |     |   |   |   |   |   | - |   | - |     | -  |     |     |         |      |   |      |     |    |   |   |   |   |   | - |   |   | - | - | - |

| · ·                         | • •  |      |     | 1   |     |      |      |     |     |   |   |   | • | • |   |   |   |     | -  | ·   | ·   |         |      |   |      |     |    |   |   |   | · | · |   | • | • | • | • | • |

| · ·                         |      |      |     | 1   |     |      |      |     |     |   |   |   |   |   | - |   | - |     | -  | ·   |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| •                           | • •  |      |     | 1   |     |      | ≺liE | ога | гyй | • |   | н | · |   | · |   |   |     | ·  | ·   |     | н       |      | 1 | ≺lit | рга | rγ | • |   |   |   |   | · |   |   |   | • | - |

| •                           |      |      |     | 1   |     |      | ≺Ы   | oc  | k≻  |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   | ≺Ы   | oc  | k≻ |   |   |   |   |   |   |   |   |   |   |   |

| •                           |      |      |     | 1   |     | 1    | 0    |     |     |   |   | н | · |   | · |   |   |     | ·  | ·   |     | н       |      | 1 | 1    |     |    |   |   |   |   |   | · |   |   |   |   |   |

| · ·                         |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| · ·                         |      |      |     | 1   |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| · ·                         |      |      |     | 1   |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| •                           |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     | L       |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

| · ·                         |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

|                             |      |      |     |     |     |      |      |     |     |   |   |   |   |   |   |   |   |     |    |     |     |         |      |   |      |     |    |   |   |   |   |   |   |   |   |   |   |   |

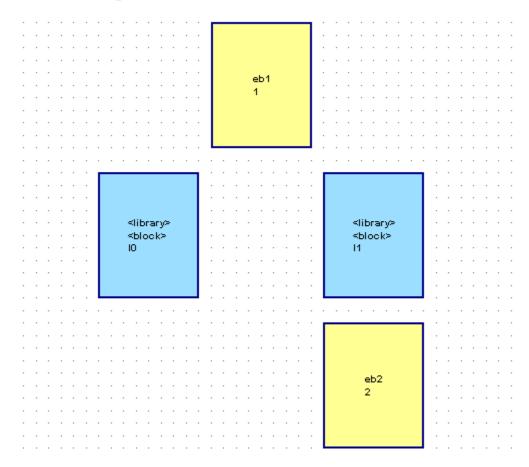

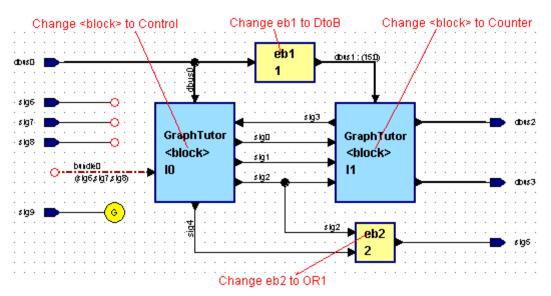

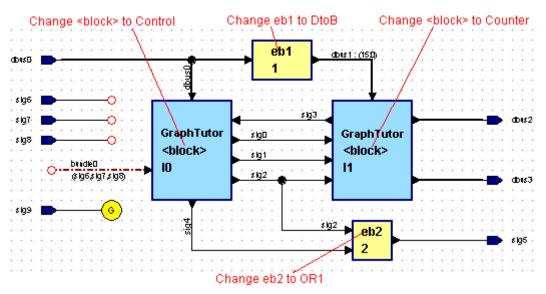

Notice that the blocks are added with the default library *<library>*, the default name *<block>* and unique instance names (*I0* and *I1*).

1

The Add Block command normally auto-repeats until you select another command or terminate the repeating command by using the right mouse button or  $\boxed{Esc}$  key. However, you can change the behavior of the toolbar buttons by setting the Activate once only preference in the General tab of the Main Settings dialog box.

You can also use the  $\boxed{\text{ctrl}}$  key with any toolbar button to toggle the repeat mode. For example, when Remain active is set,  $\boxed{\text{ctrl}} + \boxed{\blacksquare}$  adds a single block on a block diagram.

### Add Embedded Blocks

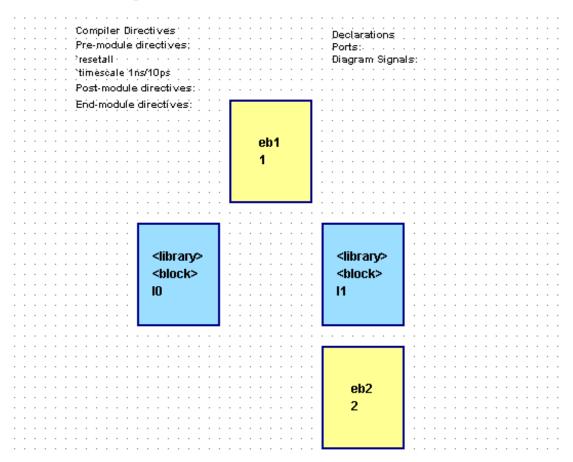

7. Use the 🕒 button to add two embedded blocks on your block diagram as shown in the picture below.

Notice that the embedded blocks are added with unique default names (*eb1* and *eb2*) and numbers (*1* and *2*).

The view describing a block must be saved as a uniquely named design unit in a library directory. However, the view describing an embedded block is saved as part of the parent block diagram and does not impose hierarchy when HDL is generated for your design. The name of an embedded block must be unique on the diagram and is used as a label in the generated HDL.

The blocks (*I0* and *I1*) will be used to define a child state machine and block diagram view. The embedded blocks (*eb1* and *eb2*) will be defined by concurrent assignment statements on the top level block diagram.

### **Add Ports and Signals**

You can use the following buttons to add signal and bus nets on a block diagram:

| "ጊ,  ▼   | Add a signal             |

|----------|--------------------------|

| ▶, ▼     | Add a signal with a port |

| "℃, ▼    | Add a bus                |

| •℃,▼     | Add a bus with a port    |

| <b>~</b> | Add a bus with a ripper  |

Signals or buses can be added between any existing connectable items on the diagram or left unconnected by double-clicking to terminate the net with a dangling net connector. However, you can use the pulldown on the buttons to change the default setting and terminate with a default port or ripper. Notice that the toolbar button changes to show the current setting.

When the to or the button is selected, a port is automatically added at an unconnected source or destination end point. When the to button is selected, a ripper is used if the end point is over an existing bus or bundle.

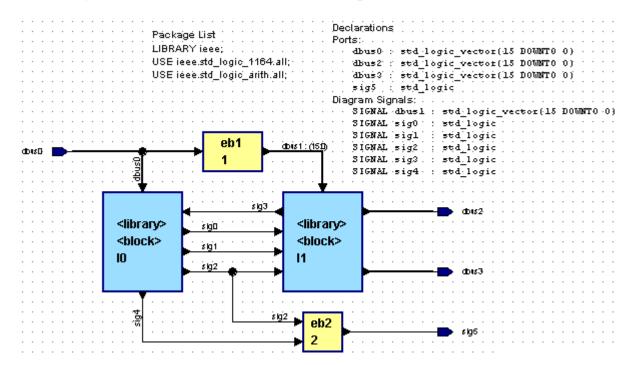

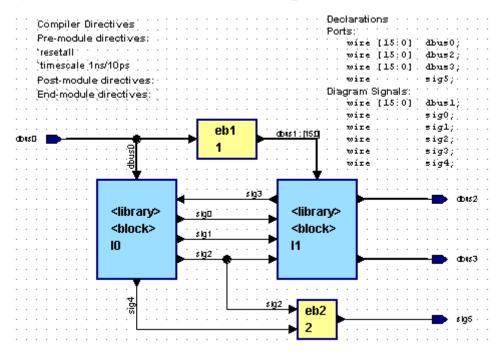

- 8. Choose **Signal with Port** and use the button to connect three signals originating from the block on the left (instance *I0* in the picture) to the block on the right (instance *I1*) and one signal returning from *I1* to *I0*. The signals are added with unique names (*sig0*, *sig1*, *sig2* and *sig3*) and the default type *std\_logic*. Notice how the full declarations for these diagram signals are automatically added to the list of Declarations on the diagram.

- Allow one or more grid lines between each port or signal. You can resize objects by selecting a block or embedded block and dragging one of its resize handles. If necessary, you can drag text elements such as the signal name using the Left mouse button.

- 9. Add a signal from *I0* to the embedded block *eb2* and another signal from a point on *sig2* terminating on the embedded block.

- 10. Add a signal from the embedded block *eb2* terminating in space on the right side of your diagram. Notice that an output port is added when you double-click at the end of the last signal and its declaration is added to the list of ports on the diagram.

- 11. Choose **Bus with Port** and use the **L** button to add a bus from a source on the left side of your diagram with its destination on the upper embedded block *eb1*. A default input port is automatically created at the beginning of the bus.

- 12. Add another bus starting from this bus and terminating on instance *I0*. Notice how both bus segments have the same default name *dbus0*. The full declaration showing the default bus type and bounds *std\_logic\_vector(15 DOWNTO 0)* is added to the list of ports.

- 13. Add a bus (*dbus1*) from *eb1* to *I1*. This internal diagram signal is shown with the default bounds (*15:0*) shown (in abbreviated format) on the net.

- 14. Then add two buses (*dbus2* and *dbus3*) from *I1* terminated with default output ports on the right of the diagram.

Your diagram should now look similar to the picture below:

### Add a Bundle and Global Connector

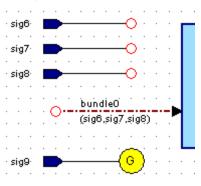

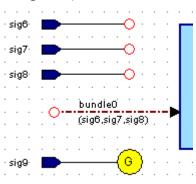

- 15. Use the button to add three signals on the left side of your diagram. Notice that a default input port is created at the source of each signal but a dangling net connector is drawn when you double-click at the end of each signal.

- 16. Select the three signals (by dragging a select rectangle with the Leff mouse button held down) and use the button to connect a bundle containing these signals to block instance *I0* as shown in the picture below.

Notice that the bundle has the default name *bundle0* and the three selected signals are automatically included in the bundle with their names listed under the bundle name.

You can use the pulldown on the button to select a button which allows you to rip one or more signals and buses from an existing bundle.

- 17. Use the O button to add a global connector on your diagram below the bundle.

- 18. Use the to add a signal between the global connector and a default input port. (This will be a clock signal which is implicitly connected to every block on the diagram.)

If you make a mistake when editing a diagram, you can use the 🔊 button to undo your last edit and the 🕶 button to redo an undo operation. You can also use commands from the **Align** cascade of the **Edit** menu to re-align and distribute objects on the diagram.

### Save the Block Diagram

Notice the asterisk (\*) character in the header of the block diagram editor window. This indicates that the diagram has been edited since it was last saved.

- 19. Use the 🖬 button to save the block diagram. The Save As dialog box is displayed which allows you to choose from the currently mapped libraries and specify the design unit and design unit view names.

- 20. Choose the *GraphTutor* library and enter design unit *Timer*. The dialog box should look similar to the example below:

| 🛺 Save As Design Uni                                                                                 | t View       |             | × |

|------------------------------------------------------------------------------------------------------|--------------|-------------|---|

| Library:                                                                                             | Design Unit: | View:       |   |

| GraphTutor<br>exemplar<br>GraphTutor<br>hds_package_library<br>renoir_package_library<br>SCRATCH_LIB | Timer        | struct      |   |

|                                                                                                      | 0            | K Cancel He |   |

The view name and file extension when you save graphical diagrams defaults as follows:

| struct.bd  | block diagram               |

|------------|-----------------------------|

| struct.ibd | interface-based design view |

| fsm.sm     | state diagram               |

| flow.fc    | flow chart                  |

| tbl.tt     | truth table                 |

| symbol.sb  | symbol                      |

If you omit the two-character extension it is automatically added to identify the type of diagram you are saving. The default leaf names can be changed by setting preferences. However, you should not change the extension (*.bd*, *.ibd*, *.sm*, *fc*, *.tt* or *.sb*) or the design data file will not be recognized and cannot be reopened.

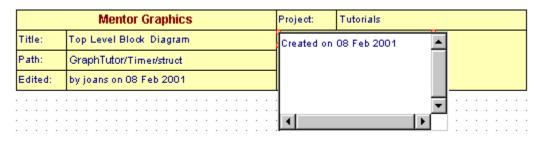

21. When you click the button, your diagram is saved and the window title bar is updated to show the pathname *GraphTutor/Timer/struct*.

This path is also added in the title block replacing the <TBD> used when the diagram was created. Notice that the asterisk (\*) character has been cleared in the block diagram header and the library name used on the blocks in your diagram has been updated to *GraphTutor*.

If the design manager window is obscured, you can pop it to the front by selecting **Design Manager** from the list of open windows in the block diagram **Windows** menu.

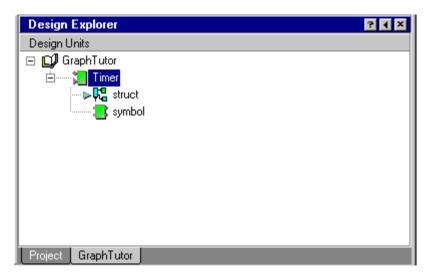

- 22. Click on the  $\boxdot$  icon for the *GraphTutor* library in the design explorer and notice that the view is expanded to display the *Timer* design unit.

- 23. Click on the  $\pm$  icon for the *Timer* design unit to reveal that it contains a symbol and block diagram view.

### **Edit the Block and Signal Names**

You now have a completed top-level block diagram for the *Timer* design. However, the blocks and signals have default names.

24. Click on the text <block> in the lower block on the left (instance *I0* in the picture) and notice the small handles which indicate that the text object is selected. Click again and notice that the text is now highlighted and can be directly overwritten.

If you click again, the cursor changes to an I-beam which allows you to move the cursor in the text and edit individual characters. Enter the new name *Control* and click outside the text to complete the edit.

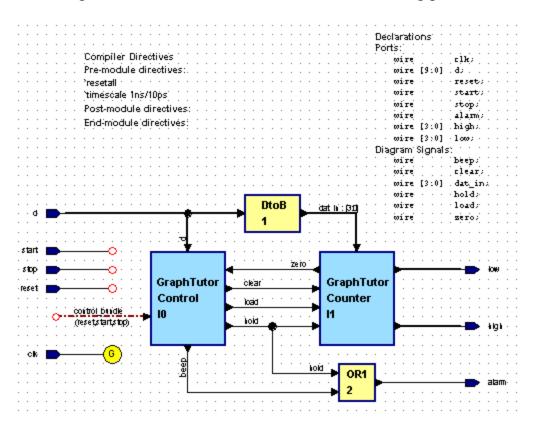

25. Repeat this procedure to change the name of block instance *I1* to *Counter*, embedded block *eb1* to *DtoB* and embedded block *eb2* to *OR1*.

Direct text editing can also be used to edit the signal and bus names. Alternatively, you can use a dialog box which allows you to edit the properties for a selected object. By default, edits to signal and bus nets are applied only to the connected nets but you can choose to apply the changes to the entire diagram or to propagate changes to all occurrences of the net in the hierarchy of the design.

26. Choose Entire Net in diagram from the Scope for Changes cascade of the Signals cascade in the Diagram menu.

| Object Prop                                                                                                                      | perties                                                                                     |                      |                       |             | ×                     |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|-----------------------|-------------|-----------------------|

| Blocks Err                                                                                                                       | bedded Blocks                                                                               | Components           | Gienerics Declaration | Frames Text | Signals Bundles       |

| sig6 : std_logi<br>sig7 : std_logi<br>sig8 : std_logi<br>sig9 : std_logi<br>dbus2 : std_log<br>dbus3 : std_lo<br>sig5 : std_logi | c<br>gic_vector(15 DC<br>gic_vector(15 DC<br>gic_vector(15 DC<br>gic_vector(15 DC<br>c<br>c | )WNTO 0)<br>)WNTO 0) |                       |             |                       |

| Declaration<br>Name:<br>Type:                                                                                                    | dbus0<br>std_logic_v                                                                        | ector                |                       |             | Global Net<br>More >> |

| Constraint:                                                                                                                      | Index                                                                                       | O Range              | O None                |             |                       |

| Bounds:                                                                                                                          | 15                                                                                          | D                    | OWNTO 🔽 🛛             |             |                       |

|                                                                                                                                  |                                                                                             |                      |                       |             |                       |

| User De                                                                                                                          | clarations                                                                                  | 🔽 Align in Col       | umns                  |             |                       |

|                                                                                                                                  |                                                                                             | OK                   | Cancel                | Apply       | Help                  |

Notice that the port declarations are listed at the top of the dialog box and the other internal diagram signals at the bottom. Input ports are listed before the output ports, otherwise the declarations are listed in alphanumeric order.

You can choose one or more existing declarations in the dialog box and enter new values for any of the declaration fields. For example, use  $\Box trl + \Box trl$  mouse button to choose *dbus1*, *dbus2* and *dbus3*, then enter a new *index* constraint with bounds 3 DOWNTO 0 to update all three buses while all other fields remain AS\_IS.

The changes are applied to the diagram when you click the OK or Apply button. Notice that all occurrences on the diagram are updated including the declarations list, signals, buses and bundle contents and that the lists of port and signal declarations are sorted alphanumerically when the changes are applied to the diagram.

28. Use the dialog box to update the port and signal declarations as shown in the following tables.

Ports:

| dbus0dstd_logic_vectorindex9 DOWNsig6startstd_logicnonenone                                                                                                                                            | 5     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| sig6startstd_logicnonenonesig7stopstd_logicnonenonesig8resetstd_logicnonenonesig9clkstd_logicnonenonedbus2lowstd_logic_vectorindex3 DOWNdbus3highstd_logic_vectorindex3 DOWNsig5alarmstd_logicnonenone | nto 0 |

Diagram Signals:

| Old Name                             | New Name | Туре             | Constraint | Bounds     |

|--------------------------------------|----------|------------------|------------|------------|

| dbus1                                | dat_in   | std_logic_vector | index      | 3 downto 0 |

| sig0                                 | clear    | std_logic        | none       | none       |

| sig1                                 | load     | std_logic        | none       | none       |

| sig2                                 | hold     | std_logic        | none       | none       |

| sig3                                 | zero     | std_logic        | none       | none       |

| sig0<br>sig1<br>sig2<br>sig3<br>sig4 | beep     | std_logic        | none       | none       |

All occurrences of each signal name (including the bundle contents) should be automatically updated on the diagram when you confirm the dialog box. If any nets are not updated, check that you have set the scope for changes to **Entire Net in Diagram** as described on page 1-15.

29. Select the bundle name and use direct text editing or the **Bundles** tab of the Object Properties dialog box to change the bundle name to *control bundle*.

If you have difficulty selecting text objects, you can change the selection mode by using the  $\checkmark$  pulldown on the  $\boxed{}$  button to select text or object shapes only.

Your block diagram should now look similar to the following picture:

The More>> button on the dialog box allows you to disclose additional fields which allow you to modify other signal properties including 2D bounds, initial value, kind, attributes and comments. The User Declarations... button allows you to add additional user-entered architecture declarations to the structural VHDL. Refer to the *HDL Designer Series Graphical Editors User Manual* for more information about these features which are not used in this tutorial.

### Add an Embedded HDL Text View

30. Select the *OR1* embedded block and display the popup menu by clicking the Right mouse button. Choose **New View** from the **Open** cascade in the popup menu to display the Create Embedded View dialog box. Choose Text from the pulldown list of views in the dialog box.

| 限 Create Embedded View         |                                     | ×      |

|--------------------------------|-------------------------------------|--------|

| Create a new view for:         | Embedded Block: OR1 No: 2 (No View) | OK     |

| Select type of view to create: | Text                                | Cancel |

|                                | Text<br>Flow Chart                  |        |

|                                | State Diagram<br>Truth Table        |        |

When you confirm the dialog box, an embedded HDL text view containing default text is displayed on the block diagram adjacent to the embedded block.

31. Select the text, re-display the Object Properties dialog box if necessary (using the 🖻 button) and choose the **Text** tab.

| Object F   | Properties          |            |           |               |        |      |         | ×        |

|------------|---------------------|------------|-----------|---------------|--------|------|---------|----------|

| Blocks     | Embedded Blocks     | Components | Gienerics | Declarations  | Frames | Text | Signals | Bundles  |

| Number o   | f selected Comments | : 1        |           |               |        |      |         |          |

| - Bounding | Box                 |            |           |               |        |      |         |          |

| 🔽 Resize   | e to fit text       |            |           |               |        |      |         |          |

| Text Posit | tion Top            |            |           |               |        |      |         | -        |

| Modify     | u                   |            |           |               |        |      |         |          |

|            |                     |            |           |               |        |      |         |          |

| Comment    | Text                |            |           |               |        |      |         |          |

| OR1 2      |                     |            |           |               |        |      |         | <u> </u> |

| alarm <= h | old OR beep;        |            |           |               |        |      |         |          |

|            |                     |            | Enter new | HDL text here |        |      |         |          |

|            |                     |            |           |               |        |      |         |          |

|            |                     |            |           |               |        |      |         | ×        |

|            |                     |            |           |               |        |      |         |          |

|            | Г                   | 0K         |           | Cancel        | Арр    | lu   | 1       | Help     |

|            |                     | OK         |           |               |        | ,    |         | ioip     |

32. Check the bounding box **Resize to fit text** option and enter the following VHDL statement under the default -- OR1 2 comment text in the dialog box:

```

alarm <= hold OR beep;</pre>

```

The modified HDL text is checked for syntax errors and applied to the diagram when you click the OK or Apply button on the dialog box.

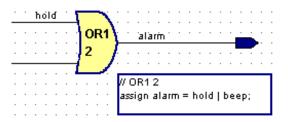

The functional blocks on the diagram are shown by default as simple rectangular shapes. However, it is sometimes useful to use logic notation when a block has a specific logical function. For example, in this block diagram, the *OR1* embedded block represents a logical OR function. You can apply a logical OR shape using the Comment Graphics toolbar which is normally docked at the bottom of the editor window, by choosing **Autoshapes** from the **Shape** cascade of the popup menu or by using the Change Shape... button in the **Embedded Blocks** tab of the Object Properties dialog box.

- 33. Select the embedded block and choose the pulldown ▼ on the <sup>™</sup> button in the Comment Graphics toolbar to display a palette of alternative shapes. Select ⊃ from the palette to apply a logical OR shape to the embedded block.

- 34. Hide the port arrow heads by clearing the **Show Ports when connected** check box in the **Embedded Blocks** tab of the Object Properties dialog box.

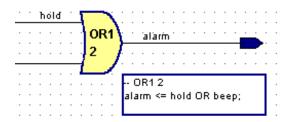

The OR1 embedded block should now look similar to the following picture:

It is also possible to indicate an active low (Not) or edge triggered clock signal. This feature can be used with the alternative shapes to represent extra functions such as an invertor, NAND, NOR or flip-flop. The logical OR function could also be implemented using a ModuleWare part similar to that described in "Add ModuleWare Components" on page 1-53.

### Add a Panel and Edit the Title Block

A panel can be useful to outline areas of a diagram. For example, you can use a panel to outline a view used for simulation or animation.

- 35. Use the 🗖 button to add a panel and hold down the Left mouse button to drag the panel and enclose the graphical objects on your diagram. The panel is added with the default name *Panel0*.

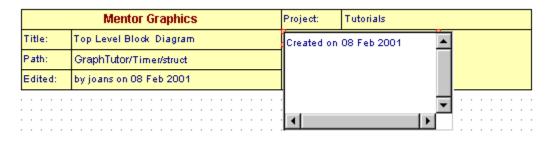

- 36. Complete the block diagram by editing the title and comments in the title block on the diagram. For example, enter the title Top Level Timer Block Diagram and a comment of the form: Created by <your name> on <date>.

The title block comprises a number of grouped comment text objects. Each comment text object can be edited directly by clicking twice on the text to display a text entry box.

You can enter free-format text including line breaks and spaces which will be preserved on the diagram.

- 37. Click the Left mouse button outside the entry box to complete the text entry.

- You can also edit an existing comment text object by double-clicking to display the **Text** tab in the Object Properties dialog box. When comments are edited in the dialog box, it is possible to enter any special characters (for example accents or Kanji characters) which are supported on your system.

- 38. Use the 📕 button to save the block diagram.

You have previously saved the diagram so you are not prompted for library and design unit names. However, you have changed the names of signals connected to input and output ports and the diagram will be inconsistent with the symbol that was automatically created by the previous save. You are prompted whether to update the symbol.

39. Click the Yes button to confirm the save.

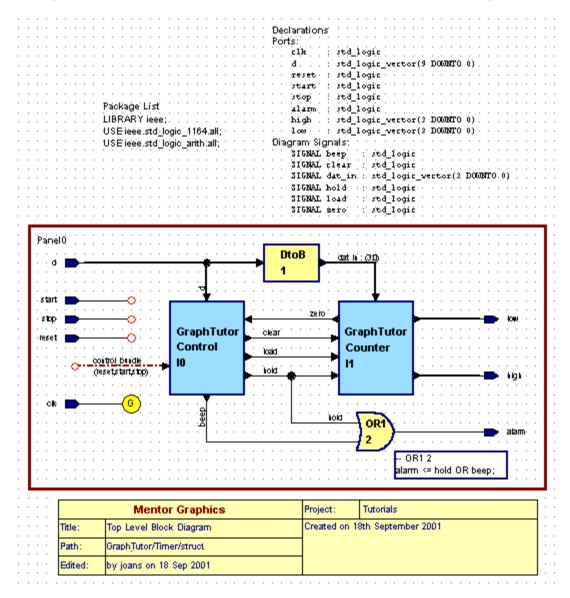

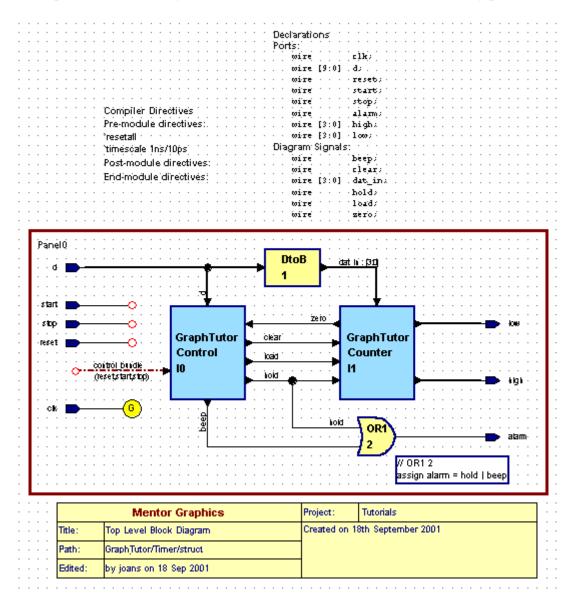

The completed block diagram should look similar to the following picture:

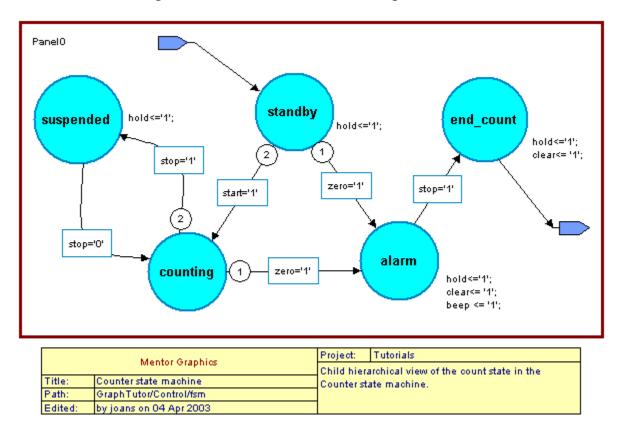

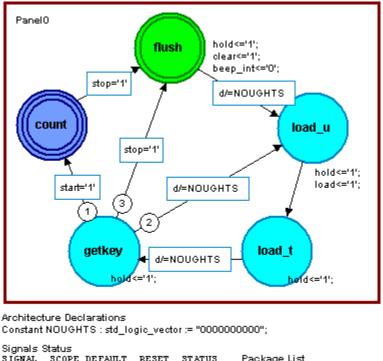

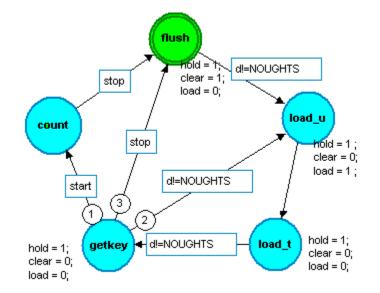

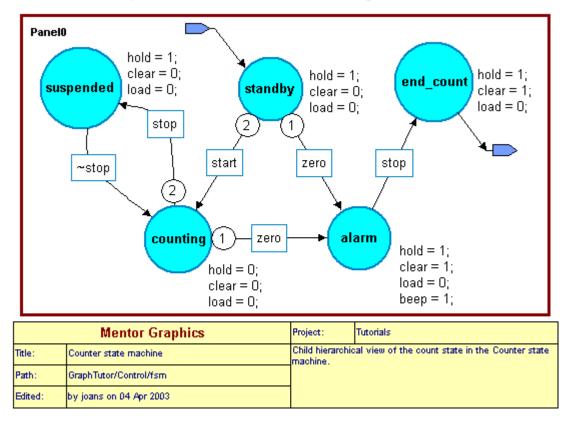

## **Create a Child State Diagram**

The procedures in this section create a graphical state machine to describe the *Control* block.

- 1. Move the cursor over the body of the *Control* block on the *Timer* block diagram, then press and release the Right mouse button to select the block and display the popup menu.

- 2. Choose **New View** from the **Open As** cascade menu. The Open Down Create New View wizard is displayed:

| 🙀 Open Down Create New View - S                                                                                                                                                                                                                                                                                                                                                | pecify Type                                | × |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---|

| Specify what kind of file you wish to create                                                                                                                                                                                                                                                                                                                                   | using which template                       |   |

| File Types:                                                                                                                                                                                                                                                                                                                                                                    | Template Files:                            |   |

| Graphical Views     Block Diagram     BD     State Diagram     BO     State Diagram     Flow Chart     Truth Table     VHDL Views     Architecture     Combined     Combined     Cource File     C++ Source File     EC++ Source File     HEX-Format File     Log File     Memory Initialization File     Mentor Graphics Binary S     Report File     Standard Delay Format F | <no template=""></no>                      |   |

|                                                                                                                                                                                                                                                                                                                                                                                | Create a graphical document (no templates) |   |

|                                                                                                                                                                                                                                                                                                                                                                                | Next > Cancel Help                         |   |

Solid handles are displayed when the body of a block (or other re-sizable object) is selected. You can display the wizard directly by double-clicking on the body of a block which has no views defined.

3. Select *State Diagram* from the list of file types and use the Next button to display the Specify View Name page of the wizard:

| 🕕 Open Dow     | vn Create New View - Specify View Name                | ×    |

|----------------|-------------------------------------------------------|------|

| Creating docur | nent: State Diagram                                   |      |

| File Specifica | stion                                                 |      |

| Library:       | GraphTutor                                            | ~    |

| Design Unit:   | Control                                               | ~    |

| View name:     | fsm.sm                                                |      |

|                |                                                       |      |

|                |                                                       |      |

|                |                                                       |      |

|                |                                                       |      |

|                |                                                       |      |

|                | <back cancel<="" finish="" td=""><td>Help</td></back> | Help |

The library and design unit fields are shown dimmed because they are copied automatically from the library and design unit of the parent diagram. The view name defaults to *fsm.sm* for a state machine.

You do not need to enter the file extension (*.bd*, *.fc*, *ibd*, *.sm* or *.tt*) for graphical views as the correct extension is automatically added. However, if you do enter any other extension you are warned that the file will not be recognized.

4. Use the Finish button to confirm the wizard with the default view name *fsm.sm*.

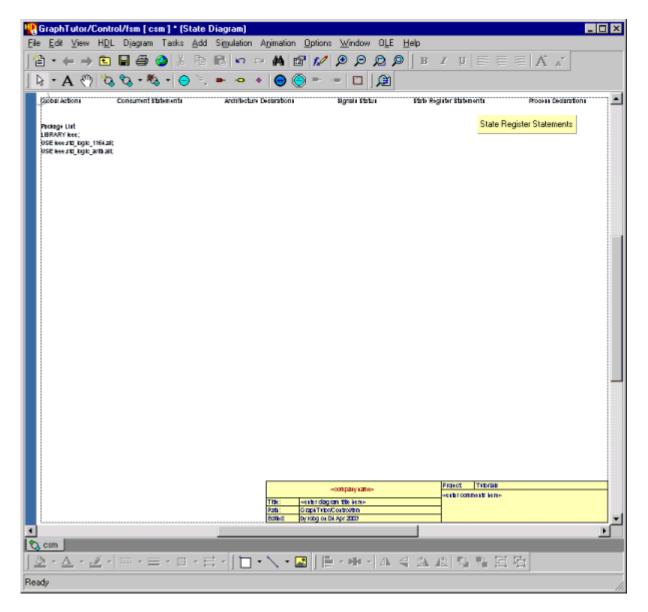

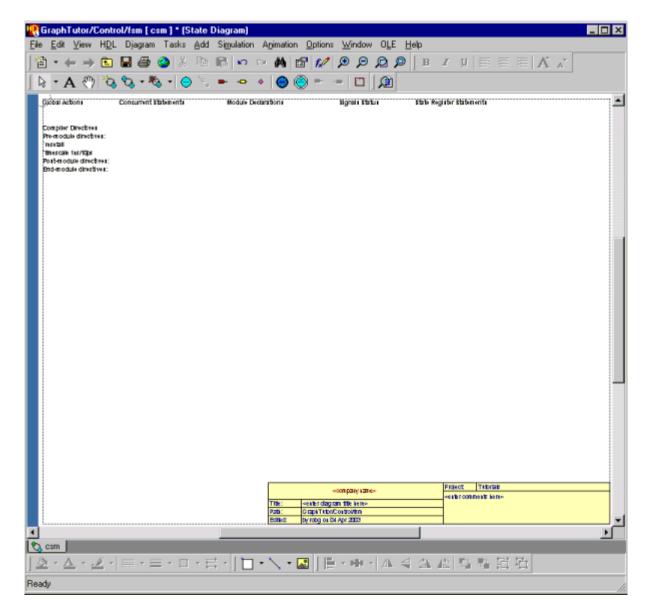

A new state diagram *GraphTutor/Control/fsm [csm]* is created as a child view of the *Control* block.

Note that a default state machine name *csm* is appended to the design unit and view names in the diagram title. This name can be changed by choosing **Rename Concurrent State Machine** from the **Diagram** menu in the state diagram.

The state diagram is a blank sheet with page boundaries set for the default printer. The diagram includes text objects for the default VHDL package list and labels for global actions, concurrent statements, architecture declarations, signals status, process declarations and state register statements:

The diagram also includes the default title block which you saved as a template in an earlier topic.

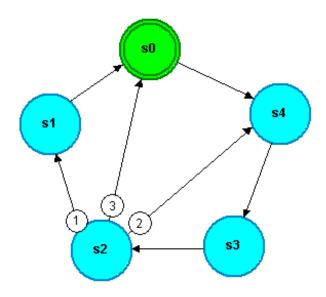

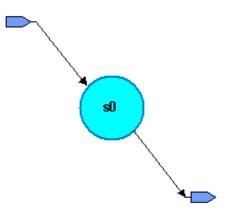

## **Add States and Transitions**

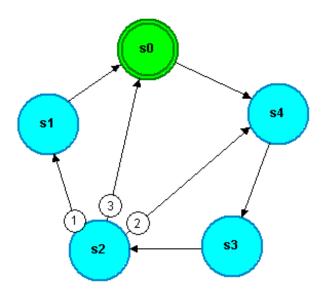

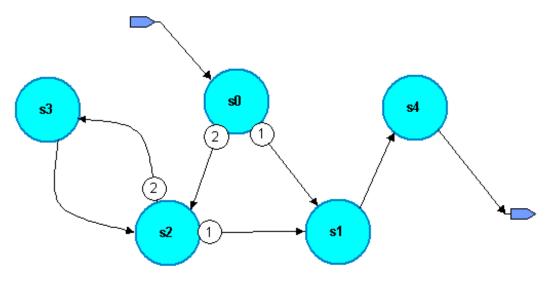

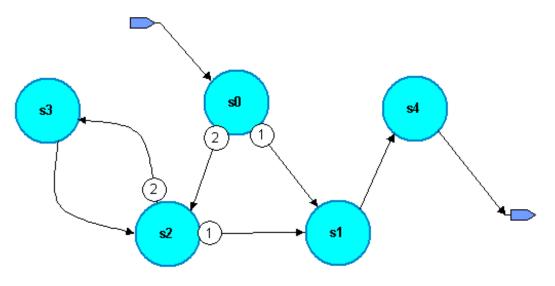

5. Use the  $\bigcirc$  button to add five states on your state diagram. The states are added with default names *s*0, *s*1, *s*2, *s*3 and *s*4.

Notice that the first state you add is assumed to be the start state and is drawn in green with a double outline. The other states are drawn in cyan with a single outline.

6. Use the states as shown in the picture below.

Notice that when you add more than one transition leaving a state, the transition priority is indicated by a number associated with the transition arc. The priorities are initially assigned in the order that you add the transitions but will be re-assigned in a later topic if necessary.

If you add a transition in the wrong direction, you can easily change its direction by choosing **Reverse Direction** from the popup or **Diagram** menu. Note that a popup description (known as an object tip) is displayed when the cursor is stationary over an object. In particular, when the cursor is over a a transition, the source state and the destination state are named even if the states are outside the current window.

### Save the State Diagram

7. Use the 🖬 button to save the state diagram. The state diagram was created as a child view from its parent block diagram and is saved using the library, design unit and view names specified when it was created. The design explorer is updated to display the *Control* design unit.

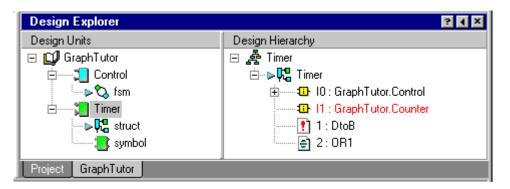

The *Control* design unit is shown as a block in the design explorer because its interface is defined by the connections on its parent block diagram. The *Timer* design unit is shown as a component because it has no parent block diagram and its interface is defined by a symbol.

- 8. Click on the  $\boxdot$  icon for the *Control* design unit in the design explorer to expand the design unit revealing that it contains a state diagram view  $\diamondsuit$ .

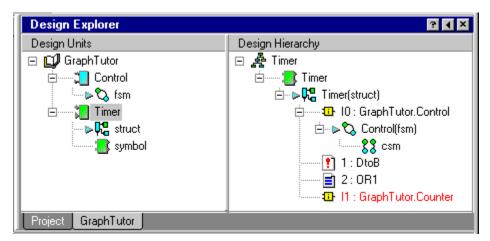

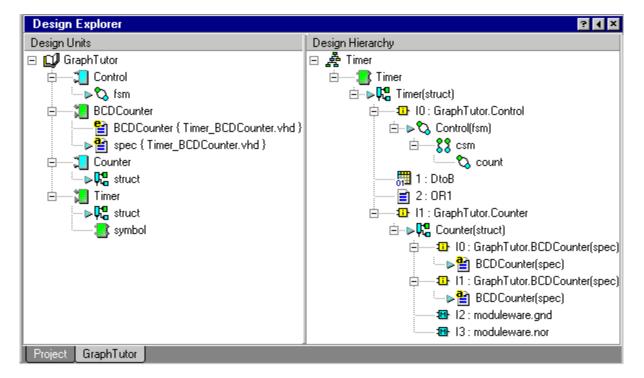

- 9. Select the *Timer* design unit and choose **Show Hierarchy** from the popup menu.

- 10. Select the 👼 Timer hierarchy node in the *Design Hierarchy* pane and choose **Expand All** from the popup menu to reveal the full hierarchy:

Notice that instance *I0* in the hierarchy for the *Timer(struct)* view contains  $\Im$  and  $\Im$  icons showing that the state diagram is described by a concurrent state machine view. The *OR1* embedded block is shown as a text view but the *DtoB* embedded block and the *Counter* instance are not yet defined.

### **Edit the States**

11. Select the start state (*s0* in the picture on page 1-26) and use the 🖾 button to display the **States** tab of the State Machine Object Properties dialog box:

| 限 Object Prope            | rties                  |            |       | ×        |

|---------------------------|------------------------|------------|-------|----------|

| States Trans              | sitions Junctions      | Links Text |       |          |

| Number of selec           |                        |            |       |          |

| Name:                     | ilush                  |            |       |          |

| State Type:               | Start State            |            |       | <b></b>  |

| -                         |                        |            |       |          |

| – Outgoing trans          | itions for this state— |            |       |          |

| Style: 💿                  |                        |            |       | Settings |

| 💌 Implicit loop           | back                   |            |       |          |

| - Actions                 |                        |            |       |          |

| Modify                    |                        |            |       | Visible  |

| holdk='1';<br>cleark='1'; |                        |            |       | <u> </u> |

| beep<='0';                |                        |            |       |          |

|                           |                        |            |       |          |

|                           |                        |            |       |          |

|                           |                        |            |       | <u>_</u> |

|                           |                        |            |       |          |

|                           | OK                     | Cancel     | Apply | Help     |

You can also display the dialog box by choosing **Object Properties** from the **Edit** menu or by double-clicking on a state.

The **States** tab allows you to enter a name and actions text for one or more selected states on a state diagram. You can also change the visibility of state actions and (when a single state is selected) change the state to a start state or a hierarchical state.

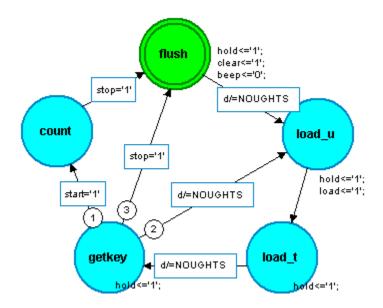

12. Use the dialog box to enter the following state names and actions replacing the default state names s0 to s4 in the picture on page 1-26:

| Old Name | New Name | Style | Actions                                 |

|----------|----------|-------|-----------------------------------------|

| s0       | flush    | IF    | hold<='1';<br>clear<='1';<br>beep<='0'; |

| s1       | count    | IF    | (no actions)                            |

| s2       | getkey   | IF    | hold<='1';                              |

| s3       | load_t   | IF    | hold<='1';                              |

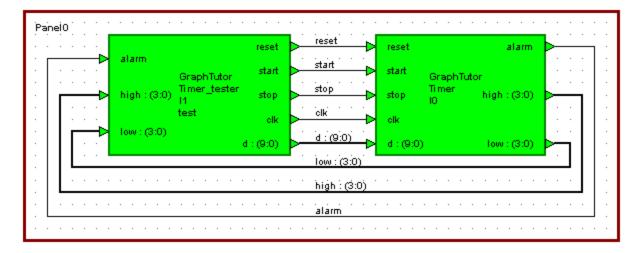

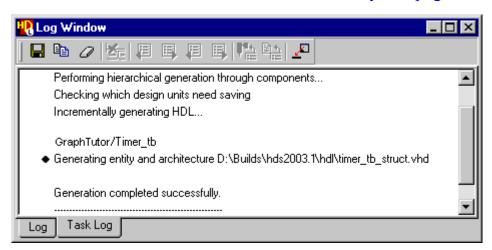

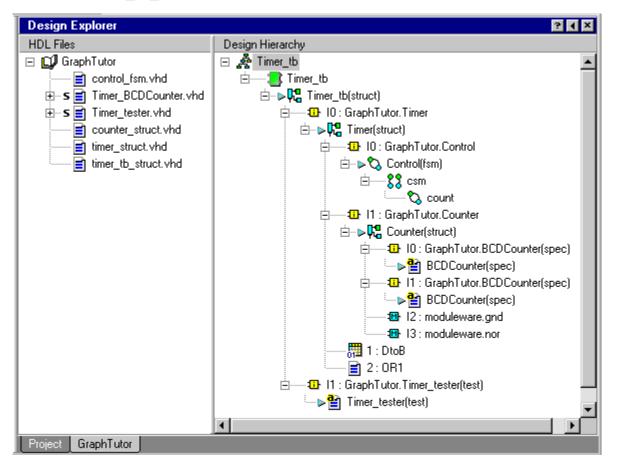

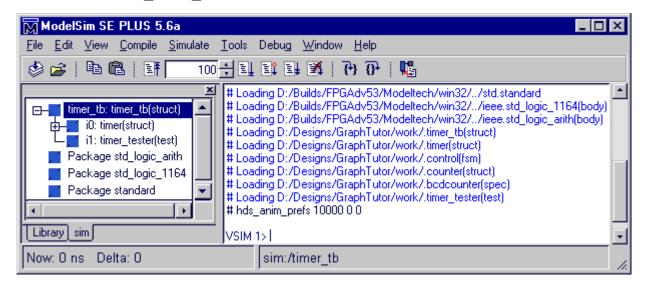

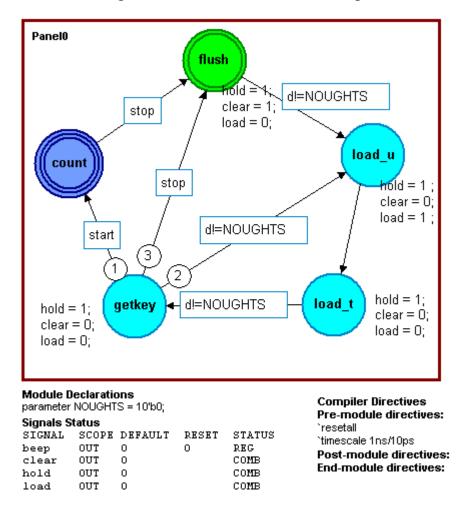

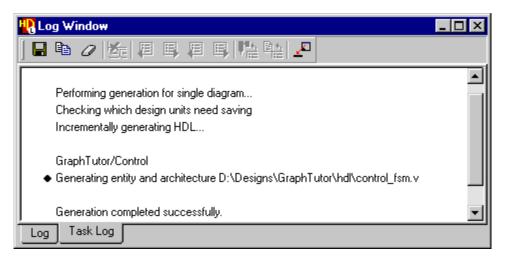

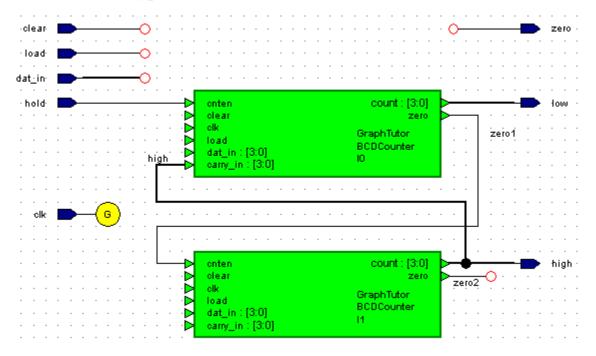

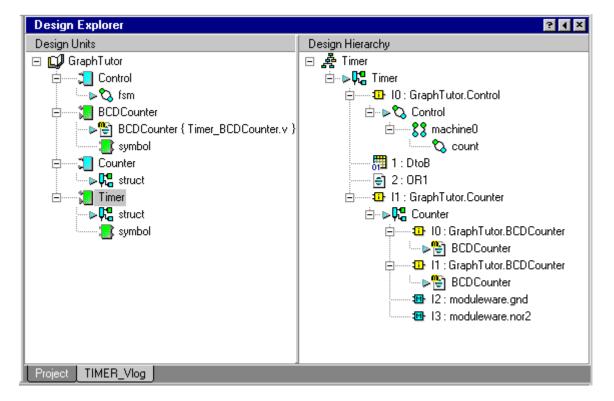

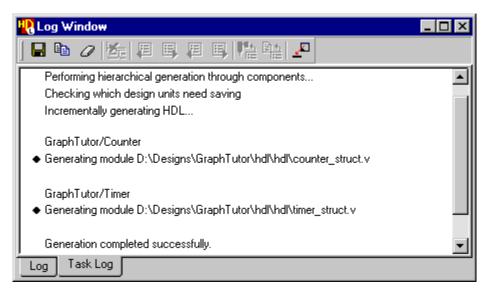

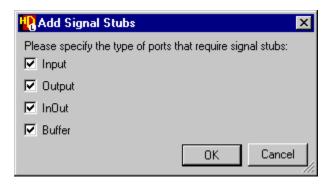

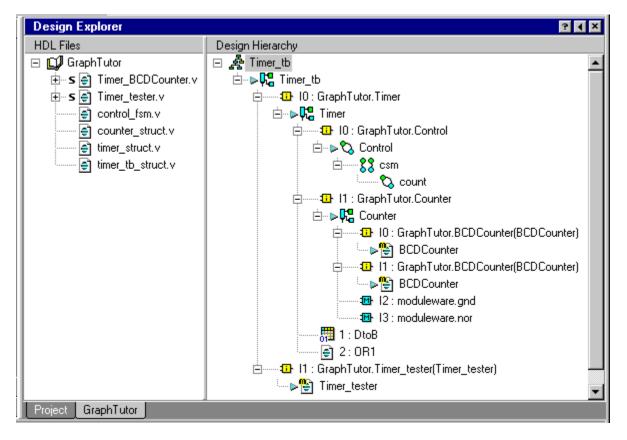

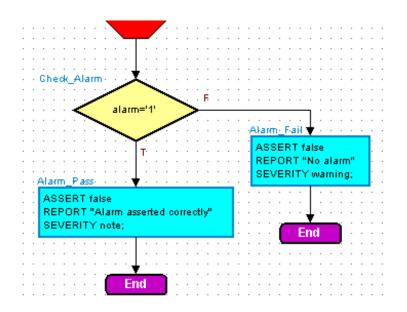

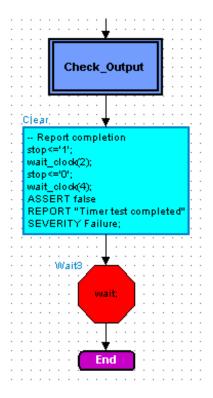

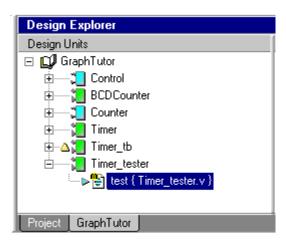

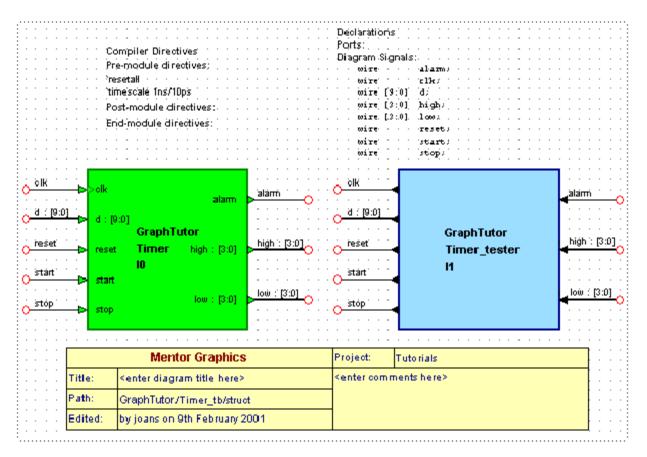

| s4       | load_u   | IF    | hold<='1';<br>load<='1';                |