## Chapter 10

# **SOC Encounter Place and Route**

LACE AND ROUTE is the process of taking a structural file (Verilog in our case) and making a physical chip from that description. It involves placing the cells on the chip, and routing the wiring connections between those cells. The structural Verilog file gives all the information about the circuit that should be assembled. It is simply a list of standard cells and the connections between those cells. The cell layouts are used to place the cells physically on the chip. More accurately, the abstract views of the cells are used. The abstracts have only information about the connection points of the cells (the pins), and routing obstructions in those cells. Obstructions are simply layers of material in the cell that conflict with the layers that the routing tool wants to use for making the connections. Essentially it is a layout view of the cell that is restricted to pins and metal routing layers. This reduces the amount of information that's required by the place and route tool, and it also lets the vendor of the cells to keep other details of their cells (like transistor information) private. It's not need for place and route, so it's not included in the abstract view.

The files required before starting place and route are:

**Cell characterization data:** This should be in a **liberty** (or **<filename>.lib**) formatted file. It is the detailed timing, power, and functionality information that you derived through the characterization process (Chapter 7). It's possible that you might have up to three different **.lib** files with typ, worst, and best timing, but you can complete the process with only a single **.lib** file. It is very important that your **.lib** file include footprints for all cells. In particular you will need to know the footprint of inverter, buffer, and delay cells (delay cells can just be buffers or inverters). If you have special buffers/inverters for building

clock trees, those should use a different footprint than the "regular" buffers and inverters. If you have multiple drive strengths of any cells with the same functionality, those cells should have the same footprint. This enables certain timing optimizations in the place and route tool.

You might have multiple **.lib** files if your structural Verilog uses cells from multiple libraries.

**Cell abstract information:** This is information that you generated through the **abstract** process (Chapter 9), and is contained in a **LEF** (or **<filename>.lef**) file. The LEF file should include technology information and macro information about all the cells in your library.

You might have multiple **.lef** files if your structural Verilog uses cells from multiple different libraries.

**Structural Verilog:** This file defines the circuit that you want to have assembled by the place and route tool. It should be a purely structural description that contains nothing but instantiations of cells from your library or libraries.

If your design is hierarchical you might have multiple Verilog files that describe the complete design. That is, some Verilog modules might include instantiations of other modules in addition to just cells. In any case you should know the name of the top-level module that is the circuit that you want to place and route.

**Delay constraint information:** This is used by the place and router during timing optimization and clock tree generation. It describes the timing and loading of primary inputs and outputs. It also defines the clock signal and the required timing of the clock signal. This file will have been generated by the Synopsys synthesis process, and is <**filename**>.sdc. You can also generate this by hand since it's just a text file, but it's much easier to let Synopsys generate this file based on the timing constraints you specified as part of the synthesis procedure (Chapter 8).

If you have all these files you can proceed to use the place and route tool to assemble that circuit on a chip. In our case we'll be using the **SOC Encounter** tool from Cadence. My recommendation is to make a new directory from which to run the tool. I'll make an IC\_CAD/soc directory, and in fact, under that I'll usually make distinct directories for each project I'm running through the **soc** tool. In this example I'll be using a simple counter that is synthesized from the behavioral Verilog code in Figure 10.1 so I'll make an IC\_CAD/soc/count directory to run this example. Inside this directory I'll make copies or links to the **.lib** and **.lef**

```

module counter (clk, clr, load, in, count);

parameter width=8;

input clk, clr, load;

input [width-1 : 0] in;

output [width-1 : 0] count;

reg [width-1 : 0] tmp;

always @(posedge clk or negedge clr)

begin

if (!clr)

tmp = 0;

else if (load)

tmp = in;

else

tmp = tmp + 1;

end

assign count = tmp;

endmodule

```

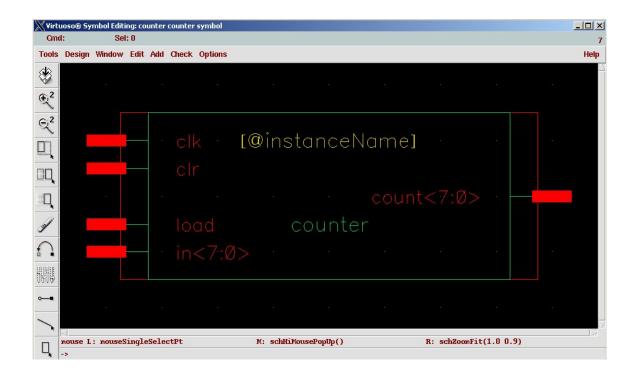

Figure 10.1: Simple counter behavioral Verilog code

files I'll be using. In this case I'll use **example.lib** and **example.lef** from the small library example from Chapters 7 and 9. The structural Verilog file (**count\_struct.v**)generated from Synopsys (Chapter 8) is shown in Figure 10.2, and the timing constraints file, **count\_struct.sdc** is shown in Figure 10.3. This is generated from the synthesis process and encodes the timing constraints used in synthesis. Once I have all these files in place I can begin.

### **10.1 Encounter GUI**

As a first tutorial example of using the **SOC Encounter** tool, I'll describe how to use the tool from the GUI. Most things that you do in the GUI can also be done in a script, but I think it's important to use the tool interactively so that you know what the different steps are. Also, even if you script the optimization phases of the process, it's probably vital that you do the floor planning by hand in the GUI for complex designs before you set the tool loose on the optimization phases.

First make sure that you have all the files you need in the directory you will use to run **SOC Encounter**. I'm using the counter from the previous Figures so I have:

count\_struct.v: The structural file generated by Synopsys

count\_struct.sdc: The timing constraints file generated by Synopsys

module counter ( clk, clr, load, in, count ); input [7:0] in; output [7:0] count; unput clk, clr, load; wire n39, n40, n41, n42, n43, N5, N6, N7, N8, N9, N10, N11, N12, N13, N14, N15, N16, N17, N18, N19, N20, n2, n3, n4, n5, n6, n7, n8, n9, n10, n11, n12, n13, n14, n15, n16, n17, n18, n19, n20, n21, n22, n23, n24, n25, n26, n27, n28, n30, n31, n32, n33, n34, n36, n37; DFF tmp\_reg\_0\_ ( .D(N12), .G(clk), .CLR(clr), .Q(n43) ); DFF tmp\_reg\_1\_ ( .D(N13), .G(clk), .CLR(clr), .Q(n42) ); DFF tmp\_reg\_2\_ ( .D(N14), .G(clk), .CLR(clr), .Q(n41) ); DFF tmp\_reg\_3\_ ( .D(N15), .G(clk), .CLR(clr), .Q(n40) ); DFF tmp\_reg\_4\_ ( .D(N16), .G(clk), .CLR(clr), .Q(n39) ); ); DFF tmp\_reg\_5\_ ( .D(N17), .G(clk), .CLR(clr), .Q(count[5]) ); DFF tmp\_reg\_6\_ ( .D(N18), .G(clk), .CLR(clr), .Q(count[5]) ); DFF tmp\_reg\_7\_ ( .D(N19), .G(clk), .CLR(clr), .Q(count[7]) ); DFF tmp\_reg\_T\_( .D(N18), .G(c1K), .CLR(c1r), .Q(count[6])

DFF tmp\_reg\_T\_( .D(N19), .G(c1K), .CLR(c1r), .Q(count[7])

MUX2\_INV U13 ( .A(N20), .B(in[5]), .S(load), .Y(n4) );

MUX2\_INV U15 ( .A(N8), .B(in[3]), .S(load), .Y(n5) );

MUX2\_INV U15 ( .A(N7), .B(in[2]), .S(load), .Y(n6) );

MUX2\_INV U16 ( .A(N7), .B(in[1]), .S(load), .Y(n7) );

MUX2\_INV U16 ( .A(N5), .B(in[1]), .S(load), .Y(n7) );

MUX2\_INV U18 ( .A(N5), .B(in[0]), .S(load), .Y(n7) );

MUX2\_INV U18 ( .A(N5), .B(in[0]), .S(load), .Y(n8) );

MUX2\_INV U19 ( .A(n4), .Y(N17) );

INVX1 U5 ( .A(n4), .Y(N17) );

INVX1 U5 ( .A(n4), .Y(N17) );

INVX1 U2 ( .A(n23), .B(n20), .Y(n10) );

INVX1 U2 ( .A(n23), .B(n20), .Y(n10) );

INVX1 U2 ( .A(n20), .Y(n12) );

MUX2\_U2 ( .A(n20), .Y(n12) );

MUX2\_U2 ( .A(count[0]), .B(N5), .S(n11), .Y(N6) );

XOR2 U24 ( .A(count[2]), .B(n25), .Y(n14) );

MUX2\_INV U26 ( .A(count[2]), .B(n25), .Y(n14) );

MUX2\_INV U26 ( .A(count[2]), .B(n16), .S(n28), .Y(N20) );

NOR2 U27 ( .A(count[5]), .B(n16), .S(n28), .Y(N20) );

NOR2 U29 ( .A(count[6]), .B(n16), .S(n28), .Y(N20) );

NOR2 U29 ( .A(count[6]), .B(n17), .Y(N10) );

INVX1 U31 ( .A(count[7]), .Y(N18) );

XOR2 U30 ( .A(count[7]), .Y(N18) );

INVX1 U31 ( .A(count[7]), .Y(N1 INVX1 U31 ( .A(count[7]), .Y(n18) ); INVX1 U32 ( .A(count[6]), .Y(n19) ); NOR2 U33 ( .A(n19), .B(n16), .Y(n20) ); NOR2 U34 ( .A(n31), .B(n22), .Y(n23) ); NAND2 U35 ( .A(n12), .B(count[2]), .Y(n22) ); NAND2 U35 ( .A(n12), .B(count[2]), .Y(n22) ); INVXL U36 ( .A(n26), .Y(n24) ); NAND2 U37 ( .A(n40), .B(count[2]), .Y(n26) ); NAND2 U38 ( .A(n12), .B(n24), .Y(n27) ); NOR2 U39 ( .A(N5), .B(n11), .Y(n25) ); NAND2 U40 ( .A(count[4]), .B(n15), .Y(n28) ); MUX2\_INV U41 ( .A(n18), .B(count[7]), .S(n21), .Y(N11) ); INVXL U42 ( .A(N5), .Y(count[0]) ); INVXL U42 ( .A(n42), .Y(n11) ); NAND2 U44 ( .A(n43), .B(n42), .Y(n30) ); NAND2 U44 ( .A(n43), .B(n42), .Y(n30) ); INVX1 U45 ( .A(n40), .Y(n13) ); NAND2 U46 ( .A(count[4]), .B(n40), .Y(n31) ); INVX1 U47 (  $.\texttt{A}(\texttt{n33})\,,\,\,.\texttt{Y}(\texttt{n32})$  ); NOR2 U48 ( .A(n37), .B(n16), .Y(n33) ); INVX1 U49 ( .A(n43), .Y(N5) ); INVXI U50 ( .A(count[5]), .Y(n16) ); INVXI U51 ( .A(n41), .Y(n34) ); INVX4 U52 ( .A(n34), .Y(count[2]) ); INVX1 U53 ( .A(n11), .Y(count[1]) ); INVX1 U54 ( .A(n13), .Y(count[3]) ); INVXI U55 ( .A(n39), .Y(n37)); INVXI U56 ( .A(load), .Y(n36)); INVXI U57 ( .A(n7), .Y(N14)); MUX2\_INV U58 ( .A(in[7]), .B(Nl1), .S(n36), .Y(n2) ); INVX4 U59 ( .A(n37), .Y(count[4]) ); INVX1 U60 ( .A(n5), .Y(N16) ); INVX1 U61 ( .A(n6), .Y(N15) ); MUX2\_INV U62 ( .A(in[6]), .B(N10), .S(n36), .Y(n3) ); INVX1 U63 ( .A(n9), .Y(N12) ); INVX1 U64 ( .A(n3), .Y(N18) ); INVX1 U65 ( .A(n2), .Y(N19) ); endmodule

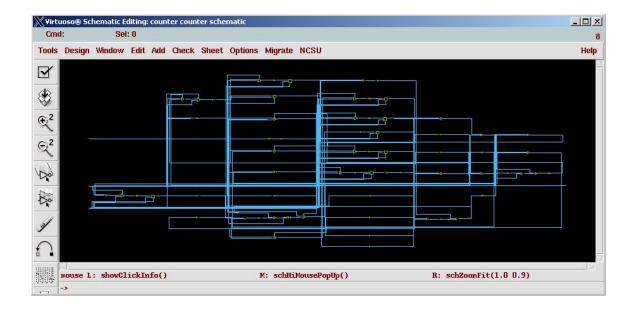

Figure 10.2: Simple counter structural Verilog code using the **example.lib** cell library

\*\*\*\*\*\*

# Created by write\_sdc on Sun Oct 8 17:14:10 2006

```

set_driving_cell -lib_cell INVX4 -library example [get_ports clr]

set driving cell -lib cell INVX4 -library example [get ports load]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[7]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[6]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[5]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[4]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[3]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[2]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[1]}]

set_driving_cell -lib_cell INVX4 -library example [get_ports {in[0]}]

set_load -pin_load 0.0659802 [get_ports {count[7]}]

set_load -pin_load 0.0659802 [get_ports {count[6]}]

set_load -pin_load 0.0659802 [get_ports {count[5]}]

set_load -pin_load 0.0659802 [get_ports {count[4]}]

set_load -pin_load 0.0659802 [get_ports {count[3]}]

set_load -pin_load 0.0659802 [get_ports {count[2]}]

set_load -pin_load 0.0659802 [get_ports {count[1]}]

set_load -pin_load 0.0659802 [get_ports {count[0]}]

create_clock [get_ports clk] -period 3 -waveform {0 1.5}

set_input_delay -clock clk 0.25 [get_ports clr]

set_input_delay -clock clk 0.25 [get_ports load]

set_input_delay -clock clk 0.25 [get_ports {in[7]}]

set_input_delay -clock clk 0.25 [get_ports {in[6]}]

set_input_delay -clock clk 0.25 [get_ports {in[5]}]

set_input_delay -clock clk 0.25 [get_ports {in[4]}]

set_input_delay -clock clk 0.25 [get_ports {in[3]}]

set_input_delay -clock clk 0.25 [get_ports {in[2]}]

set_input_delay -clock clk 0.25 [get_ports {in[1]}]

set_input_delay -clock clk 0.25 [get_ports {in[0]}]

set_output_delay -clock clk 0.25 [get_ports {count[7]}]

set_output_delay -clock clk 0.25 [get_ports {count[6]}]

set_output_delay -clock clk 0.25 [get_ports {count[5]}]

set_output_delay -clock clk 0.25 [get_ports {count[4]}]

set_output_delay -clock clk 0.25 [get_ports {count[3]}]

set_output_delay -clock clk 0.25 [get_ports {count[2]}]

set_output_delay -clock clk 0.25 [get_ports {count[1]}]

set_output_delay -clock clk 0.25 [get_ports {count[0]}]

```

Figure 10.3: Timing information (.sdc file) for the counter example

- **example.lib:** A link to my cell library's characterized data in **.lib** format. Make sure this file has footprint information for all cells.

- **example.lef:** A link to my cell library's abstract data in **.lef** form. Make sure that you have correctly appended the **TechHeader.lef** information in front of the **MACRO** definitions.

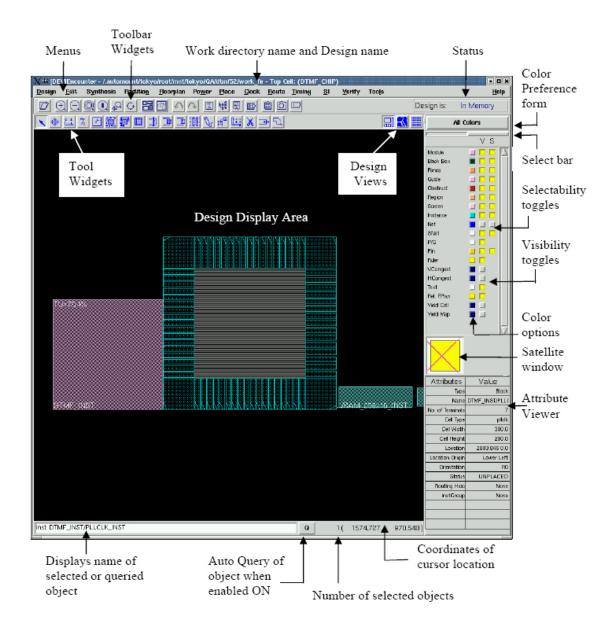

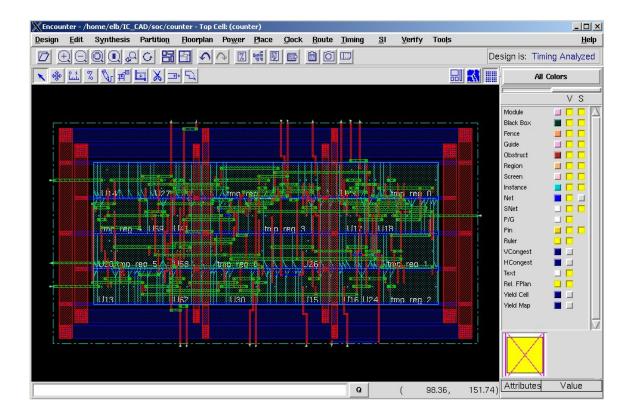

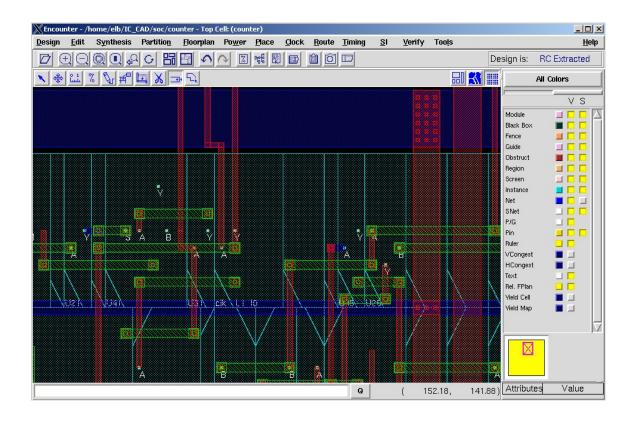

After connecting to your directory (I'm using IC\_CAD/soc/counter) you can start the SOC Encounter tool using the cad-soc script. You'll see the main encounter window as seen in Figure 10.4. This Figure is annotated to describe the different areas of the screen. The pallete on the right lets you choose what is currently visible in the design display area. The Design Views change how you see that design. From left to right the Design Views are:

- **Floorplan View:** This view shows the overall floorplan of your chip. It lets you see the area that is generated for the standard cells, and how the different pieces of your design hierarchy fit into that standard cell area. For this first example there is no hierarchy in the design so the entire counter will be placed inside the cell area. For a more complex design you can manually place the different pieces of the design in the cell area if you wish.

- **Amoeba View:** This view shows information related to the **Amoeba** placement and routing of the cells. It gives feedback on cell placement, density, and congestion.

- **Physical View:** This view shows the actual cells as they are placed, and the actual wires as they are routed by the tool.

All three views are useful, but I generally start out with the **floorplan** view during, as you might guess, floorplanning, then toggle between the that view and the **physical** view once the place and route gets under way.

#### **10.1.1** Reading in the Design

Once the tool is started you need to read all your design files into the tool. Select the **Design**  $\rightarrow$  **Design Import...** menu choice to get the **Design Import** dialog box. This box has multiple fields in multiple tabs that you need to fill in. First fill in the **Basic** fields with the following (see Figure 10.5):

Verilog Netlist: Your structural Verilog file or files. You can either let SOC Encounter pick the top cell, or you can provide the name of the top level module.

Figure 10.4: Main SOC Encounter gui

| Verilog Netlist: —  | Files: counter_struct.v                    |  |

|---------------------|--------------------------------------------|--|

|                     | Top Cell: 🔷 Auto Assign 🔶 By User: counter |  |

| Timing Libraries: - |                                            |  |

| Max Timing Li       | braries:                                   |  |

| Min Timing Li       | braries:                                   |  |

| Common Timing Li    | braries: example.lib                       |  |

|                     |                                            |  |

|                     | Files: example.lef                         |  |

|                     | nt File: counter_struct.sdd                |  |

| IO Assignme         | nt File:                                   |  |

Figure 10.5: Design Import dialog box - basic tab

- Timing Libraries: Your .lib file or files. If you have only one file it should be entered into the **Common Timing Libraries** line. If you have **best**, **typ**, **worst** timing libraries, they should be entered into the other fields with the **worst case** entered into the **max** field, the **best case** into the **min** field, and the **typical case** in the **common** field. This is optional and the process works just fine with only one library in the **common** field.

- LEF Files: Enter your .lef file or files.

- Timing Constraint File: Enter your .sdc file.

Now, move to the Advanced tab and make the following entries:

- IPO/CTS: This tab provides information for the IPO (In Place Optimization) and CTS (Clock Tree Synthesis) procedures by letting SOC Encounter know which buffer and inverter cells it can use when optimizing things. Enter the name of the footprints for buffer, delay, inverter, and CTS cells. Leave any blank that you don't have. I'm entering inv as the footprint for delay, inverter, and CTS, and leaving buffer blank as shown in Figure 10.6. Your library may be different.

- **Power:** Enter the names of your power and ground nets. If you're following the class design requirements this will be **vdd!** and **gnd!** (Figure 10.7).

| Design Import                                                                                                               |                                                                                                                                                                                                                                     | >    |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Basic Advanced                                                                                                              |                                                                                                                                                                                                                                     |      |

| Delay Calculation<br>GDS<br>ILM<br>IPO/CTS<br>OpenAccess<br>Power<br>RC Extraction<br>RTL<br>SI Analysis<br>Timing<br>Yield | IPO:       Buffer Name/Footprint:         Delay Name/Footprint:       inv         Inverter Name/Footprint:       inv         CTS:       Cell Footprint:         Cell List:       Generate Footprint Based on Functional Equivalence |      |

| <u>0</u> K                                                                                                                  | Save Load Cancel                                                                                                                                                                                                                    | Help |

Figure 10.6: Design Import IPO/CTS tab

| esign Import                                                                                                                |                                                                        |              |

|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------|

| Basic Advanced                                                                                                              |                                                                        |              |

| Delay Calculation<br>GDS<br>ILM<br>IPO/CTS<br>OpenAccess<br>Power<br>RC Extraction<br>RTL<br>SI Analysis<br>Timing<br>Yield | Power Nets: vdd!<br>Ground Nets: gnd!<br>Toggle Rate Scale Factor: 1.0 |              |

| οκ                                                                                                                          | Save Load Cancel                                                       | <u>H</u> elp |

Figure 10.7: Design Import Power tab

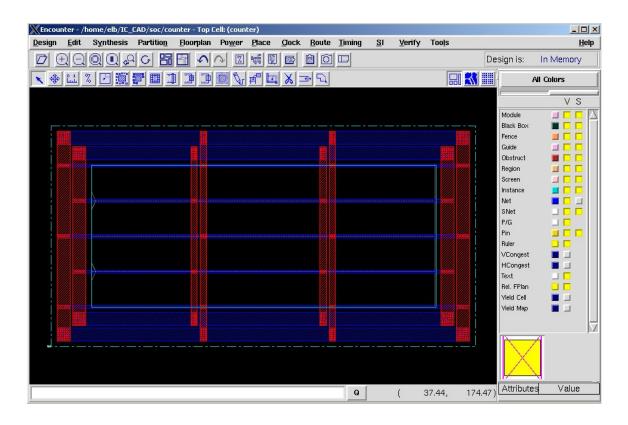

Now you can press OK and read all this information into SOC Encounter. The comments (and potential warnings and errors) will show up in the shell window in which you invoked cad-soc. You should look at them carefully to make sure that things have imported correctly. If they did you will see the SOC Encounter window has been updated to show a set of rows in which standard cells will be placed.

#### 10.1.2 Floorplanning

Floorplanning is the step where you make decisions about how densely packed the standard cells will be, and how the large pieces of your design will be placed relative to each other. Because there is only one top-level module in the counter example, this is automatically assumed to cover the entire standard cell area. If your design had mode structure in terms of hierarchical modules, those modules would be placed to the side of the cell placement area so that you could place them as desired inside the cell area. The default is just to let the entire top-level design fill the standard cell area without further structuring. In practice this spreads out the entire design across the entire area which, for large systems with significant structure, may result in lower performance. For a system with significant structure a careful placement of the major blocks can have a dramatic impact on system performance.

But, for this example, what we really care about is cell density and other area parameters related to the design. Select Floorplan  $\rightarrow$  Specify Floorplan... to get the floorplanning dialog box (Figure 10.8). In this dialog box you can change various parameters related to the floorplan:

- Aspect Ratio: This sets the (rectangular) shape of the cell. An aspect of close to 1 is close to square. An aspect of .5 is a rectangle with the vertical edge half as long as the horizontal, and 1.5 is a rectangle with the vertical edge twice the horizontal. This is handy if you're trying to make a subsystem to fit in a larger project. For now, just for fun, I'll change the **aspect ratio** to **0.5**. Note that the tool will adjust this number a little based on the anticipated cell sizes.

- **Core Utilization:** This lets the tool know how densely packed the core should be with standard cells. The default is around 70% which leaves room for in place optimization and clock tree synthesis, both of which may add extra cells during their operation. For a large complex design you may even have to reduce the utilization percentage below this.

All measurements are **Core Margins:** These should be set by **Core to IO Boundary** and are assumed to be in microns.

to leave room for the power and ground rings that will be generated around your cell. All the **Core to** ... values should be set to **30**. Note that even though you specify **30**, when you **apply** those values they may change slightly according to **SOC Encounter's** measurements.

Others: Other spots in the Specify Floorplan dialog can be left as default. In particular you want the standard cell rows to be **Double-back Rows**, and you can leave the **Row Spacing** as zero to leave no space between the rows. If your design proves hard to route you can start again and leave extra space between the rows for routing.

After adjusting the floorplan, the main **SOC Encounter** window looks like Figure 10.9. The rows in which cells will be placed are in the center with the little corner diagonals showing how the cells in those rows will be flipped. The dotted line is the outer dimension of the final cell. The power and ground rings will go in the space between the cells and the outer boundary.

#### Saving the Design

This is a good spot in which to save the current design. There are lots of steps in the process that are not "undo-able." It's nice to save the design at various points so that if you want to try something different you can reload the design and try other things. Save the design with **Design**  $\rightarrow$  **Save Design...** and name the saved file **<filename>.enc**. In my case I'll name it **floorplan.enc** so that I can restore to the point where I have a floorplan if I want to start over from this point. Saved designs are restored into the tool using the **Design**  $\rightarrow$  **Restore Design...** menu.

I like to save the design at each major step so that I can go back if I need to try something different at that step. Be aware that there's no general "undo" function in Encounter.

#### **10.1.3** Power Planning

Now it's time to put the power and ground ring around your circuit, and connect that ring to the rows so that your cells will be connected to power and ground when they're placed in the row. Start with **Power**  $\rightarrow$  **Power Planning**  $\rightarrow$  **Add Rings**. From this dialog box (Figure 10.10) you can control how the power rings are generated. The fields of interest are:

- **Ring Type:** The defaults are good here. You should have the **Core ring(s) contouring:** set to **Around core boundary**.

- **Ring Configuration:** You can select the metal layers you want to use for the ring, their width, and their spacing. I'm making the top and bottom of the ring horizontal **metal1**, and the right and left vertical

Remember that all the sizes and spacings you specify must be divisible by the basic lambda unit of our underlying technology. That is, everything is measured in units of 0.3 microns, so values should be divisible by 0.3.

| 🕻 Specify Floorplan                                           |           |                |                 |              |

|---------------------------------------------------------------|-----------|----------------|-----------------|--------------|

| - Design Dimensions                                           |           |                |                 |              |

| Specify Dimensions by:                                        |           |                |                 |              |

| 🔷 Size by:                                                    |           |                |                 |              |

| 🔷 Core Size by: 🔶 Aspect R                                    | atio:     | Ra             | tio (H/W):      | 0.5          |

|                                                               |           | 🔶 Core         | Utilization [   | 0.705479     |

|                                                               |           | 🔷 Std. L       | Jtilization:    | 0.699491     |

| 💠 Width and                                                   | l Height: | Co             | ,<br>pre Width: | 176.7        |

|                                                               |           | Co             | re Height:      | 162.0        |

| $\diamondsuit$ Die Size by: Width and Hei                     | ight      | [              | Die Width:      | 176.7        |

|                                                               | D         | ie Height:     | 162.0           |              |

| Core Margins by: 🔶 Core to I                                  | IO Bounda |                | 5 1             |              |

| 💠 Core to I                                                   |           |                |                 |              |

| Core to Left:                                                 | 30        | Co             | re to Top:      | 30           |

| Core to Right:                                                | 30        | Core           | to Bottom:      | 30           |

| Die Size Calculation Use:                                     | 🔶 Max     | 10 Height      | . 🔶 Min 🕻       | O Height     |

| Floorplan Origin at:                                          | 🔶 Lowe    | er Left Cor    | ner 💠 Cer       | nter         |

| ♦ Die/IO/Core Coordinates:                                    |           |                |                 |              |

| Die LL: 0.0                                                   | 0.        | O UR:          | 176.7           | 162.0        |

| IO LL: 0.0                                                    | 0.        | O UR:          | 176.7           | 162.0        |

| Core LL: 0.0                                                  | 0.        | O UR:          | 176.7           | 162.0        |

|                                                               |           |                |                 | unit: microi |

| Standard Cell Rows                                            |           |                |                 |              |

| Double-back rows: 🗕 🗕                                         | Во        | ttom row       | orient: 🔼       |              |

| Row Spacing: 0.0 um F                                         | or Every  | 2 = B          | <br>wc          |              |

| Site: core - Row height: 27.0                                 |           | · · ·          | _               |              |

| Allow overlapping same site i                                 | rows      |                |                 |              |

|                                                               | 0.00      |                |                 |              |

| - IO Specifications<br>Bottom IO Pad Orientation: <b>П</b> во | -         |                |                 |              |

|                                                               |           | 17             | -               | 1            |

| <u>O</u> K <u>A</u> pply                                      |           | <u>C</u> ancel |                 | <u>H</u> elp |

Figure 10.8: The **Specify Floorplan** dialog box

| XEncounter - /home/elb/IC_0           | AD/soc/cou        | inter - Top C | ell: (count    | ter)      |       |               |        |            |                |        |         |                                                                                                         | _         |              |

|---------------------------------------|-------------------|---------------|----------------|-----------|-------|---------------|--------|------------|----------------|--------|---------|---------------------------------------------------------------------------------------------------------|-----------|--------------|

| <u>D</u> esign <u>E</u> dit Synthesis | Partitio <u>n</u> | Floorplan     | Po <u>w</u> er | Place     | Clock | <u>R</u> oute | Timing | <u>S</u> I | <u>V</u> erify | Tools  |         |                                                                                                         |           | <u>H</u> elp |

|                                       | <u>い</u><br>日     |               |                | <b>11</b> |       |               |        |            |                |        | De      | sign is:                                                                                                | In Memor  | /            |

| 🔨 🔶 📖 🕺 💌 🧱 🖡                         |                   |               |                | f 🖿       | 8     | æ 5.          |        |            |                |        | í 🔣 📖   | F                                                                                                       | ll Colors |              |

|                                       |                   |               |                |           |       |               |        |            |                |        |         | Ł                                                                                                       | :         | 5            |

|                                       |                   |               |                |           |       |               |        |            |                |        |         | Module<br>Black Box<br>Fence<br>Guide<br>Obstruct<br>Region<br>Screen<br>Instance<br>Net<br>SNet<br>P/G |           |              |

|                                       |                   |               |                |           |       |               |        |            |                |        |         | Pin<br>Ruler<br>VCongest<br>HCongest<br>Text<br>Rel. FPlan<br>Vield Cell<br>Vield Map                   |           |              |

| j                                     |                   |               |                |           |       |               | Q      |            | 1              | 48.58, | 181.05) | Attribute                                                                                               |           |              |

Figure 10.9: Main design window after floorplanning

**metal2** to match our routing protocol. Change the **width** of each side of the ring to **9.9** and the spacing should be set to **1.8** because of the extra spacing required for wide metal. Finally, the offset can be left alone or changed to **center in channel**. If it's left alone it should probably be changed to **1.8** to match the wide metal spacing.

When you click **OK** you will see the power and ground rings generated around your cell. You can also zoom in and see that the tool has generated arrays of vias where the wide horizontal and vertical wires meet.

Now, for this simple small design, this would be enough, but for a larger design you would want to add *power stripes* in addition to the *power rings*. Stripes are additional vertical power and ground connections that turn the power routing into more of a mesh. Add stripes using the **Power**  $\rightarrow$  **Power Planning**  $\rightarrow$  **Add Stripes...** menu (Figure 10.11). The fields of interest are:

- Set Configuration: Make sure that all your power and ground signals are in the Net(s) field (vdd! and gnd! in our case). Choose the layer you want to the stripes to use. In our case the stripes are vertical so it makes sense to have them in the normal vertical routing layer of metal2. Change the width and spacing as desired (I'm choosing 4.8 for the width and 1.8 for the spacing - remember that they need to be multiples of 0.3).

- Set Pattern: This section determines how much distance there is between the sets of stripes, how many different sets there are, and other things. You can leave the **Set-to-set distance** to the default of **100**.

- **Stripe Boundary:** Unless you're doing something different, leave the default to have the stripes generated for your **Core ring**.

- **First/Last Stripe:** Choose how far from the left (or right) you want your first stripe. I'm using **75** from the left in this example so that the stripes are roughly spaced equally in the cell. Note that this is probably overkill from a power distribution point of view. For a larger cell 250 micron spacing might be a more reasonable choice.

- Advanced Tab Snap Wire to Routing Grid: Change this from None to Grid. The issue here is that our cells are designed so that if two cells are placed right next to each other, no geometry in one cell will cause a design rule violation in the other cell. That's the reason that no cell geometry (other than the well) is allowed within  $0.6\mu$  from the **prBoundary**. That way layers, such as metal layers, are at least  $1.2\mu$  from each other when cells are abutted. However, the power stripes don't have that restriction and if you don't center the power stripes on the grid, a cell could be placed right next to a power grid and cause a

| -                                                      |                                                            |                                             |                          |              |                |

|--------------------------------------------------------|------------------------------------------------------------|---------------------------------------------|--------------------------|--------------|----------------|

| Ring Type-                                             |                                                            |                                             |                          |              |                |

| Core ring                                              | (s) contouring:                                            |                                             |                          |              |                |

| 🔶 Aroun                                                | d core boundary                                            | 💠 Along 🛛                                   | /O boundary              |              |                |

| 🗆 Exclu                                                | de selected obj                                            | ects                                        |                          |              |                |

| 💠 Block rinę                                           | j(s) around                                                |                                             |                          |              |                |

| 🔶 Each I                                               | block                                                      |                                             |                          |              |                |

| 🔶 Each i                                               | reef                                                       |                                             |                          |              |                |

|                                                        | ed power domain                                            |                                             |                          |              |                |

|                                                        |                                                            | id/or group of core                         |                          |              |                |

|                                                        |                                                            | ocks and/or group                           | s of core rows           |              |                |

| L W                                                    | ith shared ring                                            | edges                                       |                          |              |                |

| 🔶 User defi                                            | ned coordinates                                            |                                             |                          |              | Mouse Click    |

| A Coro vi                                              |                                                            |                                             |                          |              |                |

| 🔶 Core ri                                              | ng 🔷 Bloc                                                  | k ring                                      |                          |              |                |

| Ring Config                                            |                                                            | k ring                                      |                          |              |                |

|                                                        | uration ———                                                | -                                           |                          |              |                |

| Ring Config                                            | uration<br>Top:                                            | Bottom:                                     | Left:                    | Right:       |                |

| Ring Config<br>Layer:                                  | uration<br>Top:<br>metal1 H                                | Bottom:<br>metall H -                       | metal2 V -               | metal2 V -   |                |

| Ring Config<br>Layer:<br>Width:                        | Top:<br>metall H ~<br>9.9                                  | Bottom:<br>metal1 H -                       | metal2 V -               | - metal2 V - | 4              |

| Ring Config<br>Layer:<br>Width:<br>Spacing:            | Top:<br>Top:<br>Metal1 H ~<br>9.9<br>1.8                   | Bottom:<br>metal1 H<br>9.9<br>1.8           | metal2 V -               | metal2 V -   | <br>Update     |

| Ring Config<br>Layer:<br>Width:                        | Top:<br>metall H ~<br>9.9                                  | Bottom:<br>metal1 H -<br>9.9<br>1.8<br>nnel | metal2 V -               | 9.9<br>1.8   | <u>U</u> pdate |

| Ring Config<br>Layer:<br>Width:<br>Spacing:            | Top:<br>Top:<br>Metal1 H ~<br>9.9<br>1.8                   | Bottom:<br>metal1 H<br>9.9<br>1.8           | metal2 V -               | - metal2 V - | <u>Update</u>  |

| Ring Config<br>Layer:<br>Width:<br>Spacing:<br>Offset: | Top:<br>Top:<br>metal1 H ~<br>9.9<br>1.8<br>Center in char | Bottom:<br>metal1 H -<br>9.9<br>1.8<br>nnel | metal2 V -<br>9.9<br>1.8 | 9.9<br>1.8   | <u>U</u> pdate |

| Ring Config<br>Layer:<br>Width:<br>Spacing:            | Top:<br>metal1 H ~<br>9.9<br>1.8<br>Center in char<br>1.5  | Bottom:<br>metal1 H -<br>9.9<br>1.8<br>nnel | metal2 V -<br>9.9<br>1.8 | 9.9<br>1.8   |                |

Figure 10.10: Dialog box for adding power and ground rings around your cell

#### CHAPTER 10: SOC Encounter Place and Route Draft September 3, 2007

|                                                       | iration                                              |

|-------------------------------------------------------|------------------------------------------------------|

| Net(s):                                               |                                                      |

| Layer:                                                | metal2 -                                             |

| Direction:                                            | ♦ Vertical ↓ Horizontal                              |

| Width:                                                | 4.8                                                  |

| Spacing:                                              | 1.8 Update                                           |

| - Set Pattern                                         |                                                      |

| ♦ Set-to-set                                          | t distance: 100                                      |

| 💠 Number d                                            | of sets:                                             |

| 🔶 Bumps                                               | 🔶 Over 🛛 🕹 Between                                   |

| 💠 Over P/G                                            | i pins Pin layer: Top pin layer 🚽 🛄 Max pin width: 🛛 |

| 🔶 Maste                                               | er name: 💦 🕹 Selected blocks 🕹 All blocks            |

| 💠 Design bo                                           |                                                      |

|                                                       |                                                      |

| <ul> <li>First / Last</li> <li>Start from:</li> </ul> | Stripe                                               |

| ♦ Relative                                            | from core or selected area                           |

| X from le                                             | eft: 75 X from right: 0                              |

|                                                       | locations                                            |

| Absolute                                              |                                                      |

| Option Set                                            |                                                      |

Figure 10.11: Dialog box for planning power stripes

metal spacing DRC violation when the metal of the stripe is now only  $0.6\mu$  from the metal in the cell. Centering the stripe on a grid keeps this from happening by placing the metal of the stripe in a position so that the next legal cell position isn't directly abutting with the power stripe.

Clicking **Apply** will apply the stripes to your design. If you don't like the looks of them you can select and delete them and try again with different parameters. Or you can select **OK** and be finished.

Once you have the stripes placed you can connect power to the rows where the cells will be placed. Select **Route**  $\rightarrow$  **Special Route** to route the power wires. Make sure that all your power supplies are listed in the **Net(s)**

DRAFT - Please do not distribute 308

Now is another good time to save the cell again. This time I'll save it as **powerplan.enc**.

| d Stripes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| asic Advanced Via Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Stripe Breaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Omit stripes inside block rings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Omit stripes over selected blocks/domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Switch layer over obstructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Target Connection Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Pad / Core ring connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Allow jogging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Block ring connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Allow jogging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Merge with block rings if spacing less than:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Maximum length of same layer jog: 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Top limit: metal3 Bottom limit: metal3 Bottom limit: metal3 Bottom limit: metal1 Bottom li |  |

| Wire Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Use wire group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Interleaving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

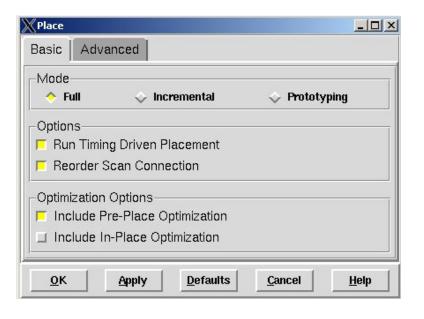

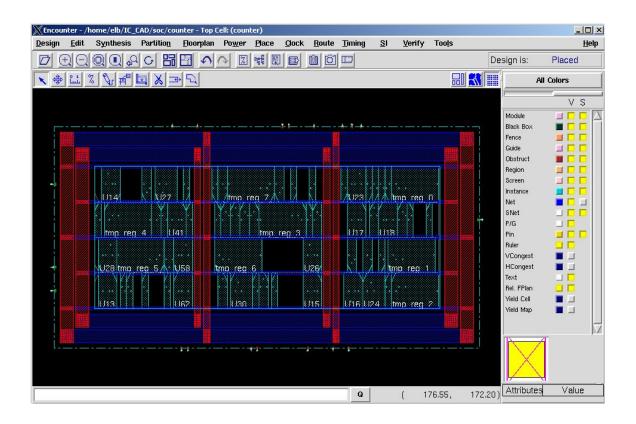

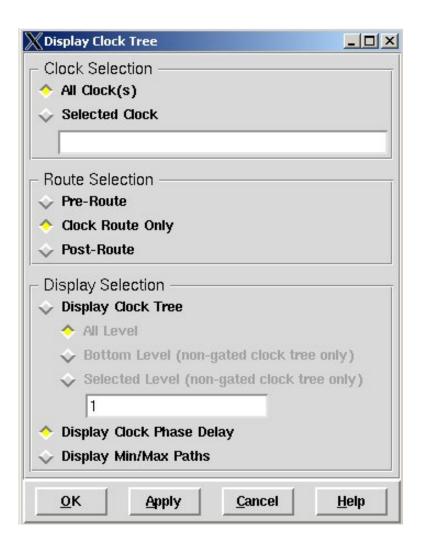

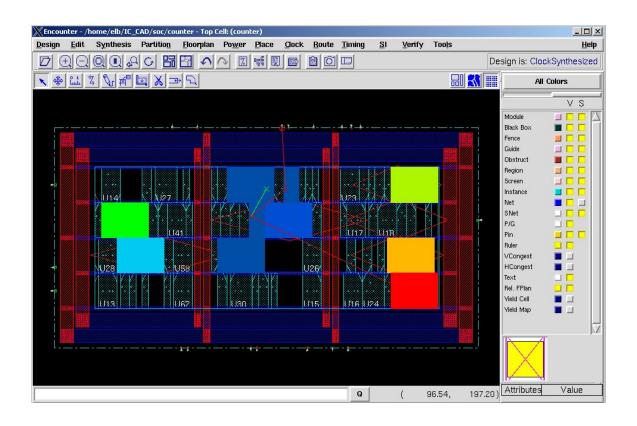

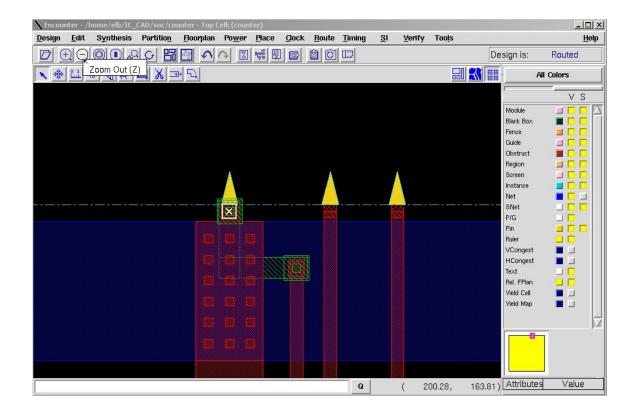

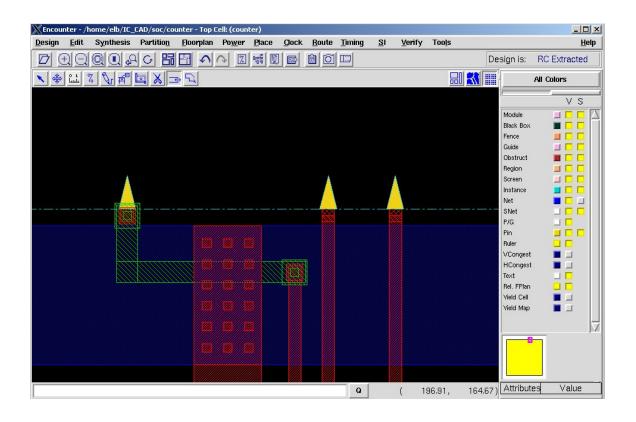

| Number of bits: 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |