## Non-inverting buck-boost converter

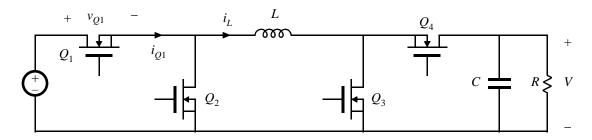

Figure below shows a converter consisting of buck switches  $Q_1$  and  $Q_2$ , and boost switches  $Q_3$  and  $Q_4$ . MOSFETs  $Q_2$  and  $Q_4$  are the synchronous rectifiers for the buck and boost stages, respectively. In all cases considered in this problem you can assume that switches are controlled such that  $Q_1$  and  $Q_2$  are operated in a complementary manner, and are never ON at the same time. Similarly,  $Q_3$  and  $Q_4$  are operated in a complementary manner, and are never ON at the same time. Switching frequency is  $f_s = 1/T_s$ .

The switches can be operated in two different ways:

## (1) Buck-boost mode:

$Q_1$  and  $Q_3$  are simultaneously ON during  $DT_s$ ,  $Q_2$  and  $Q_4$  are simultaneously ON during  $D'T_s$ .

- (2) Buck or boost modes:

- (2.1) **Buck mode**:  $Q_1$  duty cycle is  $D_{buck}$ , while  $Q_3$  is OFF always and  $Q_4$  is ON always.

- (2.2) **Boost mode**:  $Q_3$  duty cycle is  $D_{boost}$ , while  $Q_1$  is ON always,  $Q_2$  is OFF always.

(a) All MOSFETs have the same on-resistance  $R_{on}$ , and inductor winding resistance is  $R_L$ . Derive and sketch equivalent circuit models of the converter valid for (1) the buck-boost mode, and (2) the buck or boost modes. Solve the models to find analytical expressions for the dc conversion ratio  $M = V/V_g$ , and for the average inductor current  $I_L$ . Switching losses can be neglected in this part of the problem.

(b) A switching transition between  $Q_2$  and  $Q_1$  can be described as follows:  $Q_2$  is initially ON, conducting inductor current  $i_L$ , while  $Q_1$  is OFF; once  $Q_2$  is turned OFF, the body diode of  $Q_2$  conducts  $i_L$ . Then,  $Q_1$  is turned ON, initiating reverse recovery of the  $Q_2$  body diode; upon completion of the  $Q_2$  body diode reverse recovery,  $Q_1$  is ON, conducting inductor current  $i_L$ , while  $Q_2$  is OFF. Assuming snappy, abruptrecovery diode, having reverse-recovery time  $t_r$  and reverse recovery charge  $Q_r$ , sketch the waveforms  $i_{Q_1}$ and  $v_{Q_1}$  during the switching transition described above. (c) Following the description in part (b), similarly describe (in words) a transition between  $Q_3$  and  $Q_4$ , which involves reverse recovery of a MOSFET body diode. Sketch the corresponding waveforms.

(d) Derive and sketch equivalent circuit models for the converter operating in each of the buck, boost, and buck-boost modes of operation, including the loss mechanisms from part (a) as well as the reverse recovery behaviors.

(e) The converter is constructed using IRLH5036 MOSFETs having  $R_{on} = 6 \text{ m}\Omega$ , with body diode parameters  $t_r = 42 \text{ ns}$ ,  $Q_r = 201 \text{ nC}$ , which can be considered constant values. The inductor winding resistance is  $R_L = 5 \text{ m}\Omega$ . Inductor current ripple can be neglected. The converter is designed to produce output voltage V = 24 V across the load  $R = 2.3 \Omega$ . The input voltage is between  $V_{gmin} =$ 18 V and  $V_{gmax} = 30 \text{ V}$ . The switching frequency is  $f_s = 100 \text{ kHz}$ .

Solve the models you derived in part (d) to find the converter efficiencies for the two ways of operating the switches, and for the two input voltages. Show your efficiency results in a table, as shown below

|                         | $V_g = V_{gmin} = 18 \text{ V}$ | $V_g = V_{gmax} = 30 \text{ V}$ |

|-------------------------|---------------------------------|---------------------------------|

| (1) Buck-boost mode     |                                 |                                 |

| (2) Buck or boost modes |                                 |                                 |

Briefly comment on the results: compare the two ways of operating the switches; compare switching and conduction losses.

(f) Examine the IRLH5036 MOSFET datasheet and explain how the values for  $R_{on}$ ,  $t_r$  and  $Q_r$  were determined. Brief comments are sufficient. Search for alternative MOSFETs (e.g. on digikey.com), and suggest a replacement MOSFET that would result in improved efficiency results.