## 1. [25 pts] Boost Converter Layout

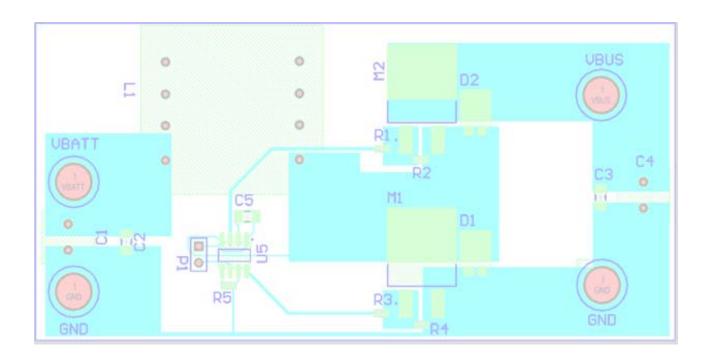

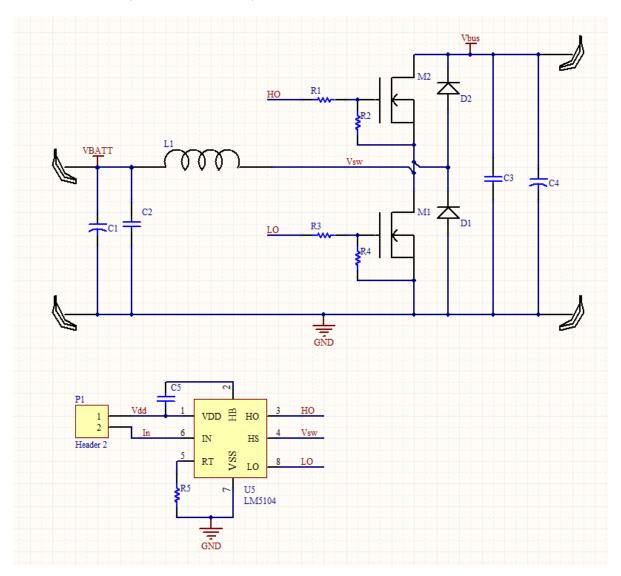

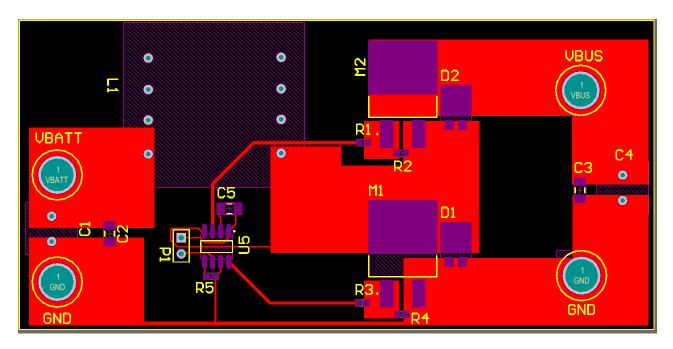

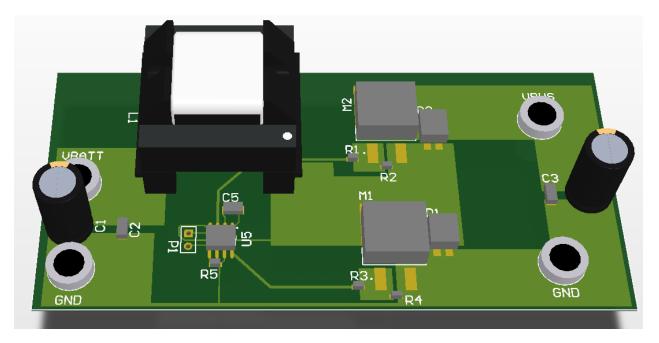

An example boost converter schematic is given in Fig. 1, with its PCB layout implemented in Fig.2 and shown again in Fig. 3. You may assume the following:

- Connections to  $V_{bat}$ ,  $V_{bus}$ , and ground are made externally to the board through banana jacks

- The gate driver input In and supply  $V_{dd}$  are connected externally through the header P1

- $C_1$  and  $C_2$  as well as  $C_3$  and  $C_4$  have sufficient capacitance value to achieve the designed voltage ripples on  $V_{bat}$  and  $V_{bus}$ , respectively

- All other devices and components are sized appropriately for their intended operation

- All electrical connections in the schematic have been made in the PCB layout

- There are no errors in DFM or DRC for the layout

- The PCB layout is *one-layer* only

Figure 1: Boost converter schematic diagram

ECE 482 / 599 \_\_\_\_\_\_\_2/13

Figure 2: Boost converter PCB layout

Figure 3: 3D representation of boost converter layout from Fig. 2

- A. [10 pts] Describe, in one or two sentences at most, the purpose of including the following components in circuit

- $R_1$  and  $R_3$

- $R_2$  and  $R_4$

- *R*<sub>5</sub>

- *C*<sub>5</sub>

- B. [5 pts] Two different types of capacitors are used between  $V_{bus}$  and ground. Explain the purpose of each, and what advantage this has over using two of the same type of capacitor.

ECE 482 / 599 \_\_\_\_\_\_\_4/13

**C.** [10 pts] Describe what you think are the <u>two</u> most important errors which must be addressed in the layout of Fig. 2 in order to ensure that the boost converter is able to work correctly and effectively. Explain what error is in the current layout, how it will harm circuit operation, and what should be altered to eliminate or reduce the harm.

The diagram of Fig. 2 is reproduced below and may be used to supplement your descriptions.