### **Converter Loss Analysis**

ECE 482 Lecture 3 January 20, 2015

### **Announcements**

- Finish Experiment 1: report due Tuesday, 1/27

- This week: Experiment 2

- Intro to FPGA programming

- Next week: Experiment 3

- Boost converter design and construction

- Open-loop, steady-state efficiency analysis

- Component kits available in circuits store later this week

- \$100 per group for components for Labs 3 and after

- Plan to spend additional ~\$5.00 on resistors, etc.

### **Words of Caution**

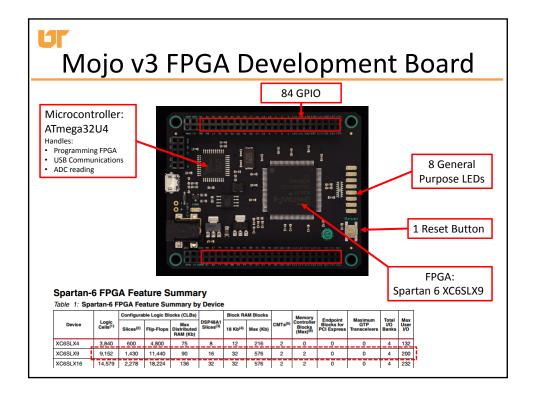

- Very easy to blow pins on FPGA

- 4V maximum!

- Use resistor dividers when necessary

- Double- and Triple-check I/O and connections before operating device

### Basics of FPGA programming

- Microcontroller

- Processor, ram, etc.

- Code is instruction set; executed sequentially

- FPGA

- Application specific circuitry

- Code is hardware design language; all in parallel

| Speed | Technology                                  | Performance/Cost | Time until running | Time to high<br>performance | Time to change code functionality |               |  |

|-------|---------------------------------------------|------------------|--------------------|-----------------------------|-----------------------------------|---------------|--|

|       | ASIC                                        | Very High        | Very Long          | Very Long                   | Impossible                        |               |  |

|       | Custom Processor/<br>DSP<br>FPGA<br>Generic | Medium           | Long               | Long                        | Long                              | Flexibility   |  |

|       |                                             | Low-Medium       | Short              | Short                       | Short                             | Œ             |  |

|       |                                             | neric Low-Medium | Short              | Not Attainable              | Short                             |               |  |

|       |                                             |                  |                    |                             | wp                                | 212 12 001104 |  |

Figure 12: Design Choices<sup>4</sup>

http://www.xilinx.com/support/documentation/white\_papers/wp213.pdf

### U

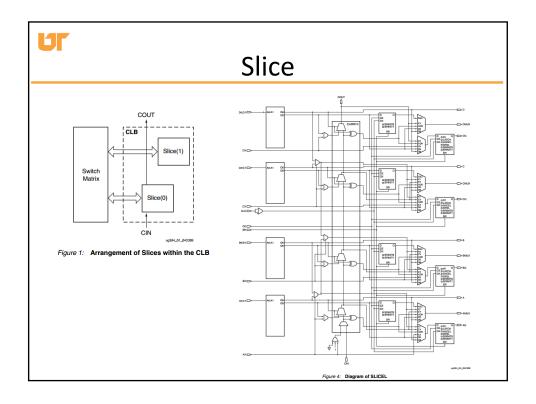

### Configurable Logic Block

Figure 1: Arrangement of Slices within the CLB

### Getting Started with Mojo v3

- Resources from board developer:

- Tutorials

- https://embeddedmicro.com/tutorials/mojo

- Base Project

- https://github.com/embmicro/mojo-baseproject/archive/master.zip

- Will be coding in Xilinx ISE

- Mojo Loader used to write .bit file to on-board RAM/Flash

### **Base Project**

```

module mojo_top(

// 50MHz clock input

input clk,

// Input from reset button (active low)

input rst n,

// cclk input from AVR, high when AVR is ready

input cclk,

// Outputs to the 8 onboard LEDs

output[7:0]led,

// AVR SPI connections

output spi_miso,

input spi_ss,

input spi_ss,

input spi_ss,

input spi_sck,

// AVR ADC channel select

output [3:0] spi_channel,

// Serial connections

input avr_tx, // AVR Tx => FPGA Tx

output avr_rx, // AVR Rx buffer full

);

wire rst = ~rst_n; // make reset active high

// these signals should be high-z when not used

assign spi_miso = 1'bz;

assign svi_miso = 1'bz;

assign spi_channel = 4'bzzzz;

assign led = 8'b0;

endmodule

```

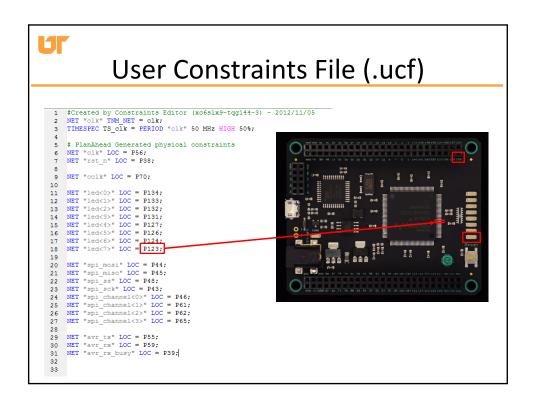

### User Constraints File (.ucf)

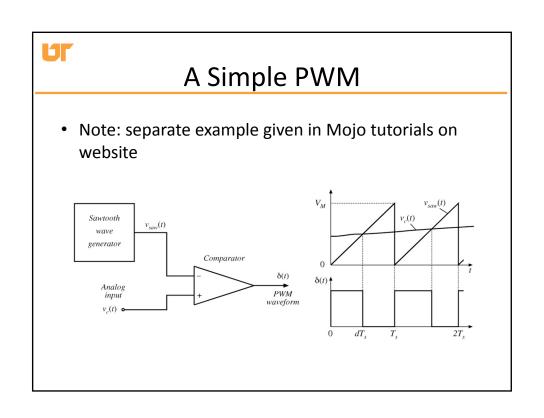

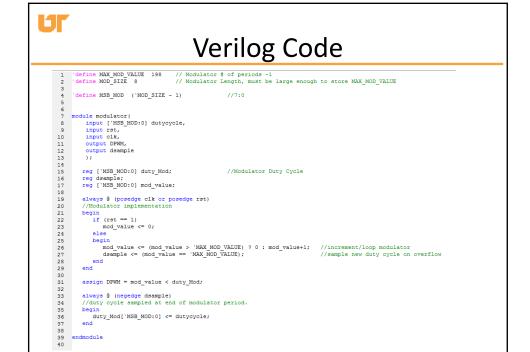

### **Digital Implementation**

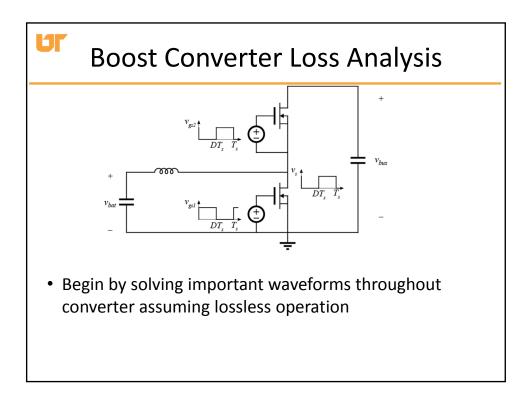

### **Converter Loss Modeling**

### **Analytical Loss Modeling**

- High efficiency approximation is acceptable for hand calculations, as long as it is justified

- Solve ideal waveforms of lossless converter, then calculate losses

- Argue which losses need to be included, and which may be neglected

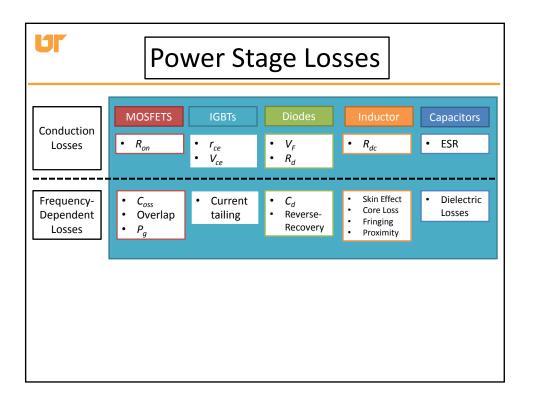

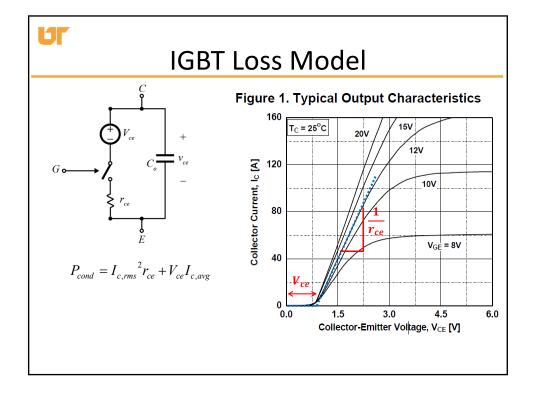

### **Conduction Loss Modeling**

19

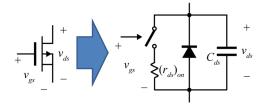

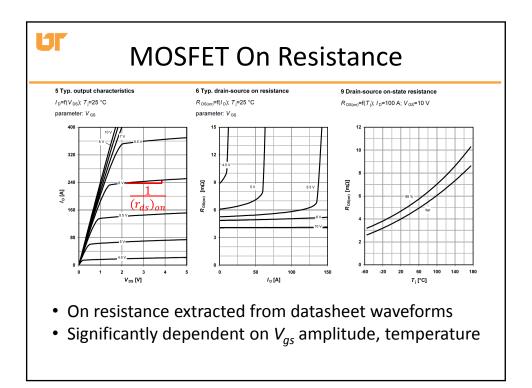

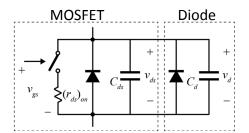

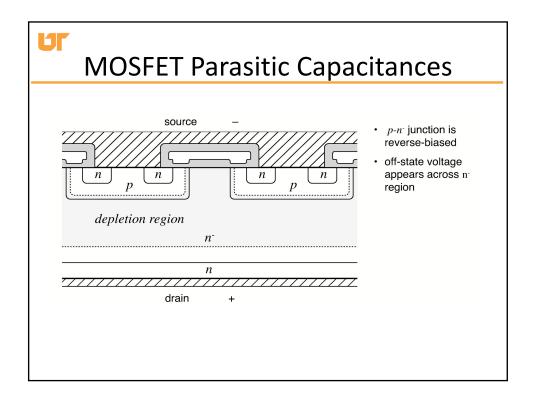

### **MOSFET Equivalent Circuit**

- Considering only power stage losses (gate drive neglected)

- MOSFET operated as power switch

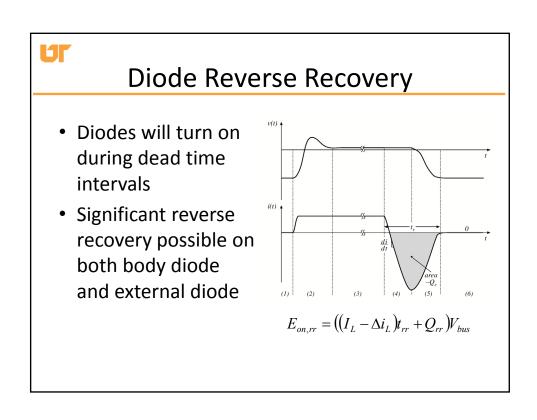

- Intrinsic body diode behaviors considered using normal diode analysis

## Boost Converter RMS Currents

• MOSFET conduction losses due to  $(r_{ds})_{on}$  depend given as

$$P_{cond,FET} = I_{di,rms}^{2} (r_{ds})_{on}$$

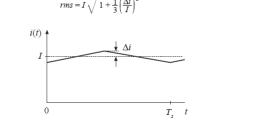

# MOSFET Conduction Losses Pulsating waveform with linear ripple, Fig. A.6: $rms = I \sqrt{D} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta t}{I}\right)^{2}} \qquad (A.6)$ Fig. A.6 • RMS values of commonly observed waveforms appendix from Power Book

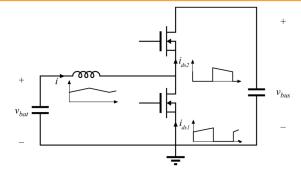

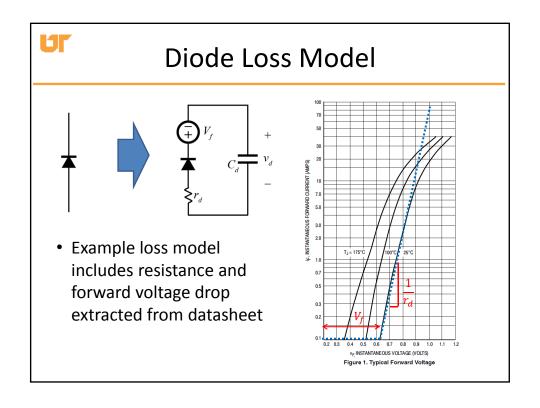

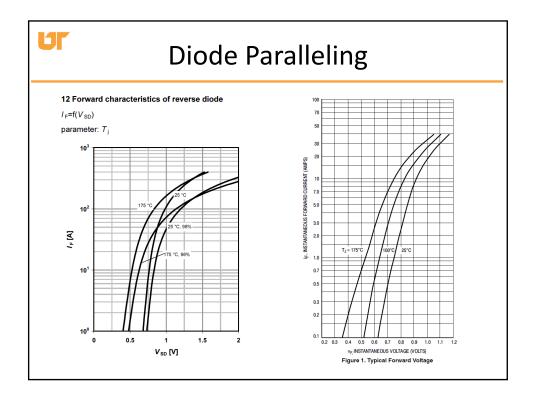

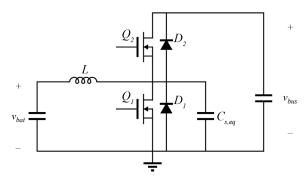

## Semiconductor Switch Conduction Loss

- Equivalent circuit of MOSFET with external antiparallel diode has two, non-ideal diodes

- Diodes, even when matched, will not share current equally, but  $v_d = v_{ds}$  must remain true

- Silicon rectifier diodes are minority carrier devices

- Concentration of minority carriers depends heavily on temperature

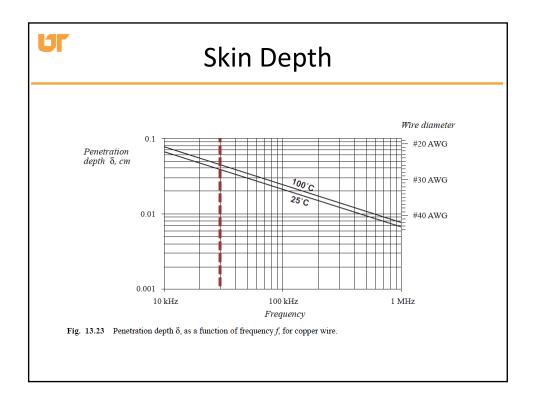

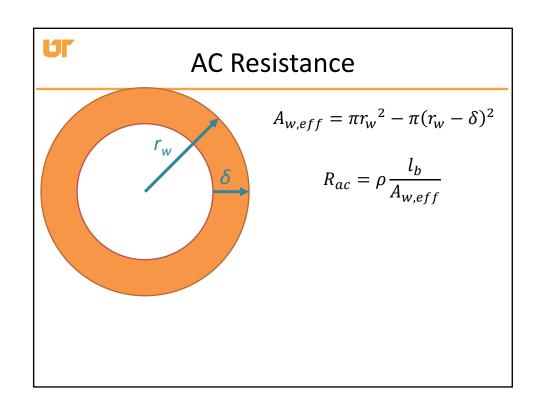

### **DC Inductor Resistance**

• DC Resistance given by

$$R_{DC} = \rho \frac{l_b}{A_w}$$

- At room temp,  $\rho = 1.724 \cdot 10^{-6} \,\Omega$ -cm

- At 100°C,  $\rho = 2.3 \cdot 10^{-6} \,\Omega$ -cm

- Losses due to DC current:

$$P_{cu,DC} = I_{L,rms}^{2} R_{DC}$$

# Inductor Conduction Losses DC plus linear ripple, Fig. A.2:

Fig. A.2

(A.2)

Conduction losses dependent on RMS current through inductor

Primary winding

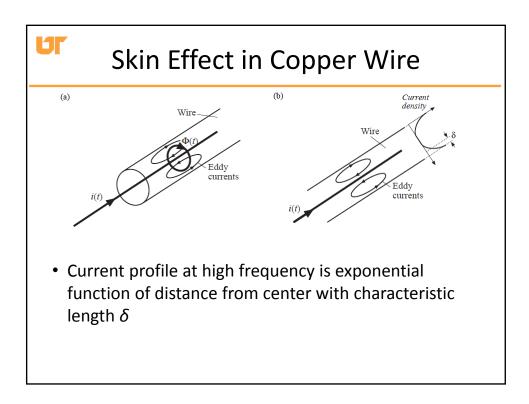

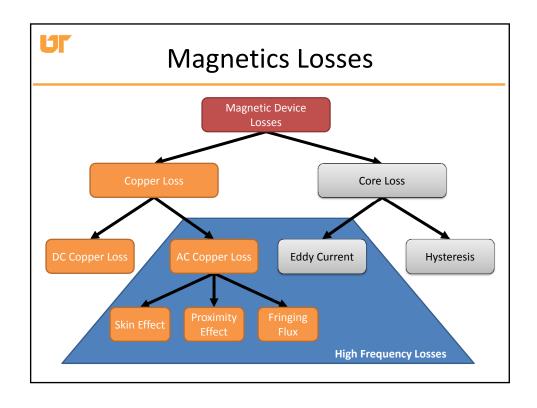

### **Proximity Effect**

• In *foil* conductor closely spaced with  $h \gg \delta$ , flux between layers generates additional current according to Lentz's law.

$$P_1 = I_{L,rms}^2 R_{ac}$$

• Power loss in layer 2:

$$P_2 = I_{L,rms}^2 R_{ac} + (2I_{L,rms})^2 R_{ac}$$

$$P_2 = 5P_1$$

Needs modification for non-foil conductors

density

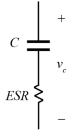

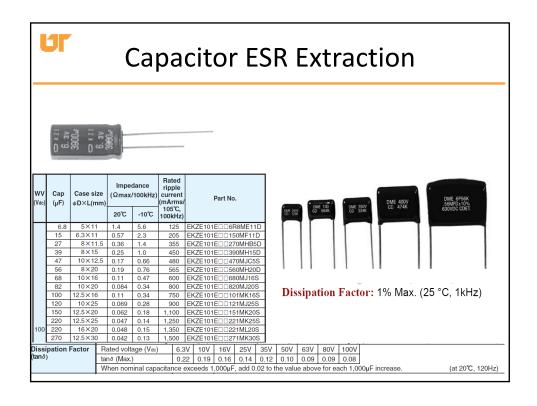

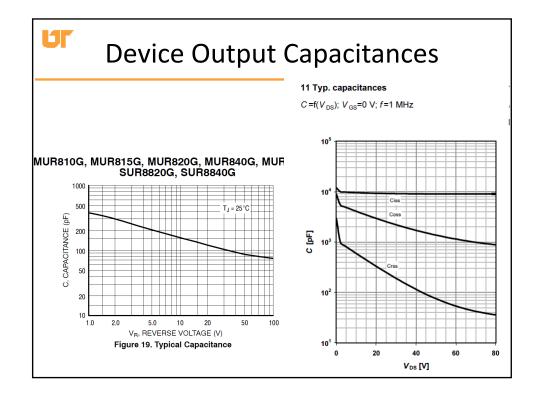

### **Capacitor Loss Model**

- Operation well below resonance

- All loss mechanisms in a capacitor are generally lumped into an empirical loss model

- Equivalent Series Resistance (ESR) is highly frequency dependent

- Datasheets may give effective impedance at a frequency, or loss factor:

$$\delta = \frac{\pi}{2} - \theta$$

$$D = \tan(\delta)$$

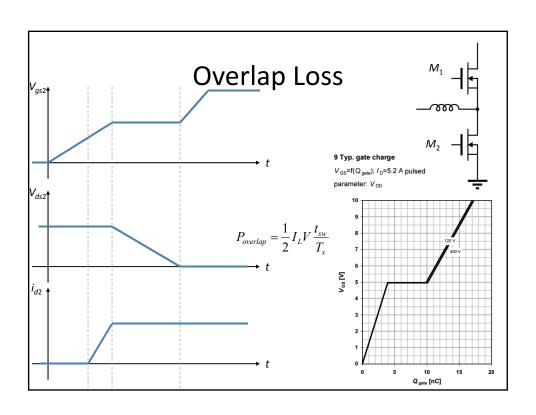

# Lump Switched Node Capacitance

Consider a single equivalent capacitor at switched node which combines energy storage due to all four semiconductor devices

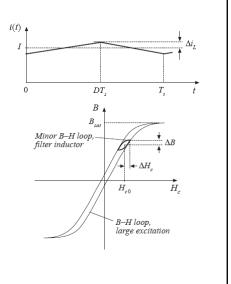

### **Inductor Core Loss**

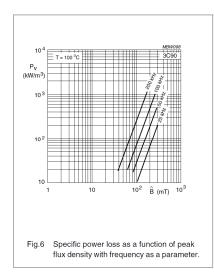

Governed by Steinmetz Equation:

$$P_v = K_{fe} f_s^{\alpha} (\Delta B)^{\beta} \text{ [mW/cm}^3]$$

- Parameters  $K_{fe}$ ,  $\alpha$ , and  $\beta$  extracted from manufacturer data

- $\Delta B \propto \Delta i_L \rightarrow \text{small losses}$ with small ripple

$$P_{fe} = P_v A_c l_m \text{ [mW]}$$

### **Steinmetz Parameter Extraction**

### Ferroxcube Curve Fit Parameters

Power losses in our ferrites have been measured as a function of frequency (f in Hz), peak flux density (B in T) and temperature (T in  $^{\circ}$ C). Core loss density can be approximated  $^{(2)}$  by the following formula :

$$P_{\text{core}} = C_m \cdot f^x \cdot B_{\text{peak}}^y (\text{ct}_0 - \text{ct}_1 T + \text{ct}_2 T^2)$$

[3]

| $= C_m \cdot C_T$ | $f^{x}$ . $B_{peak}^{y}$ | [mW/cm <sup>3</sup> ] |

|-------------------|--------------------------|-----------------------|

|-------------------|--------------------------|-----------------------|

| ferrite                                                     | f (kHz)   | Cm                    | x    | y    | ct <sub>2</sub>       | ct <sub>1</sub>       | ct <sub>0</sub> |

|-------------------------------------------------------------|-----------|-----------------------|------|------|-----------------------|-----------------------|-----------------|

| 3C30                                                        | 20-100    | 7.13.10 <sup>-3</sup> | 1.42 | 3.02 | 3.65.10 <sup>-4</sup> | 6.65.10 <sup>-2</sup> | 4               |

|                                                             | 100-200   | 7.13.10 <sup>-3</sup> | 1.42 | 3.02 | 4.10-4                | 6.8 .10 <sup>-2</sup> | 3.8             |

| 3C90                                                        | 20-200    | 3.2.10 <sup>-3</sup>  | 1.46 | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

| 3C94                                                        | 20-200    | 2.37.10 <sup>-3</sup> | 1.46 | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

|                                                             | 200-400   | 2.10 <sup>-9</sup>    | 2.6  | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

| 3F3                                                         | 100-300   | 0.25.10 <sup>-3</sup> | 1.63 | 2.45 | $0.79.10^{-4}$        | 1.05.10 <sup>-2</sup> | 1.26            |

|                                                             | 300-500   | 2.10 <sup>-5</sup>    | 1.8  | 2.5  | $0.77.10^{-4}$        | 1.05.10 <sup>-2</sup> | 1.28            |

|                                                             | 500-1000  | 3.6.10 <sup>-9</sup>  | 2.4  | 2.25 | $0.67.10^{-4}$        | 0.81.10 <sup>-2</sup> | 1.14            |

| 3F4                                                         | 500-1000  | 12.10 <sup>-4</sup>   | 1.75 | 2.9  | 0.95.10 <sup>-4</sup> | 1.1.10 <sup>-2</sup>  | 1.15            |

|                                                             | 1000-3000 | 1.1.10 <sup>-11</sup> | 2.8  | 2.4  | 0.34.10-4             | 0.01.10 <sup>-2</sup> | 0.67            |

| Table 1: Fit parameters to calculate the power loss density |           |                       |      |      |                       |                       |                 |

U

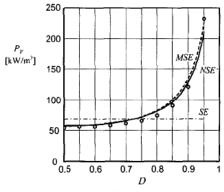

### NSE/iGSE

• More complex empirical loss models exist, and remain valid for non-sinusoidal waveforms

• NSE/iGSE:

$$P_{NSE} = \left(\frac{\Delta B}{2}\right)^{\beta - \alpha} \frac{k_N}{T} \int_0^T \left|\frac{dB}{dt}\right|^{\alpha} dt$$

Van den Bossche, A.; Valchev, V.C.; Georgiev, G.B.;, "Measurement and loss model of ferrites with non-sinusoidal waveforms," Power Electronics Specialists Conference, 2004. PESC 04. 2004 IEEE 35th Annual, vol.6, no., pp. 4814-4818 Vol.6, 20-25 June 2004 doi: 10.1109/PESC.2004.1354851

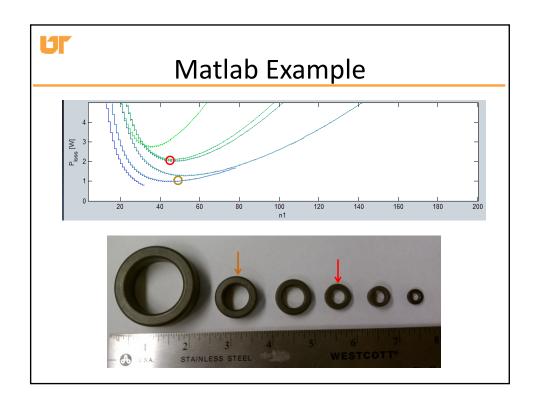

### **Inductor Design**

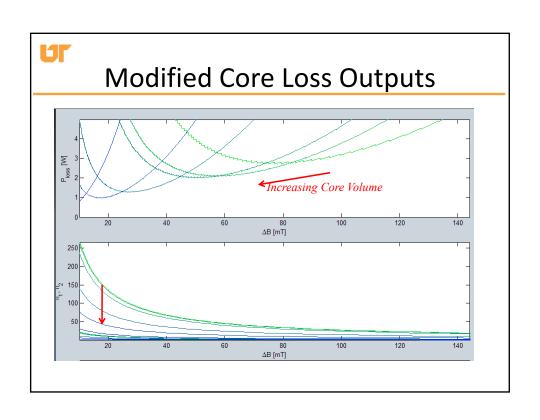

# Minimization of Losses For given core, number of turns can be used to index possible designs, with air gap solved after (and limited) to get correct inductance A minimum sum of the two exists and can be solved for

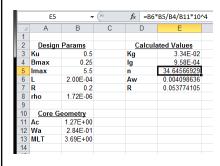

### Spreadsheet Design

- Use of spreadsheet permits simple iteration of design

- Can easily change core, switching frequency, loss constraints, etc.

### $K_g$ and $K_{gfe}$ Methods

- Two closed-form methods to solve for the optimal inductor design *under certain constraints/assumptions*

- Neither method considers losses other than DC copper and (possibly) steinmetz core loss

- Both methods particularly well suited to spreadsheet/iterative design procedures

|                  | $K_g$                 | $K_{gfe}$                                 |

|------------------|-----------------------|-------------------------------------------|

| Losses           | DC Copper (specified) | DC Copper,<br>SE Core Loss<br>(optimized) |

| Saturation       | Specified             | Checked After                             |

| B <sub>max</sub> | Specified             | Optimized                                 |

|                  |                       |                                           |

U

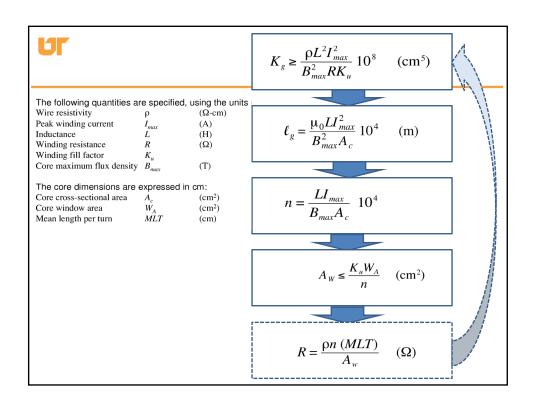

### $K_a$ Method

- Method useful for filter inductors where  $\Delta B$  is small

- Core loss is not included, but may be significant particularly if large ripple is present

- Copper loss is specified through a set target resistance

- The desired  $B_{max}$  is given as a constraint

- Method does not check feasibility of design; must ensure that air gap is not extremely large or wire size excessively small

- Simple first-cut design technique; useful for determining approximate core size required

- Step-by-step design procedure included on website

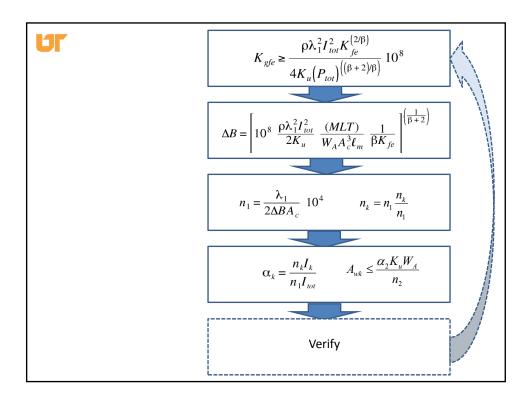

### $K_{gfe}$ Method

- Method useful for cases when core loss and copper loss are expected to be significant

- Saturation is not included in the method, rather it must be checked afterward

- Enforces a design where the sum of core and copper is minimized

### $K_{gfe}$ Procedure

| ed, using the units note                      | ed:                                                                        |

|-----------------------------------------------|----------------------------------------------------------------------------|

| , 0                                           | $(\Omega\text{-cm})$                                                       |

| •                                             | (A)                                                                        |

|                                               |                                                                            |

| $\lambda_1^2$                                 | (V-sec)                                                                    |

| $P_{tot}$                                     | (W)                                                                        |

| K''                                           |                                                                            |

| β                                             |                                                                            |

| $K_{fe}$                                      | $(W/cm^3T^{\beta})$                                                        |

| ns:                                           |                                                                            |

| $A_c$                                         | (cm <sup>2</sup> )                                                         |

| $W_{A}$                                       | (cm <sup>2</sup> )                                                         |

| MLT                                           | (cm)                                                                       |

| $\ell_e$                                      | (cm)                                                                       |

| $A_{w1}, \dots$                               | (cm <sup>2</sup> )                                                         |

| $\Delta \stackrel{\scriptscriptstyle{W1}}{B}$ | (T)                                                                        |

|                                               | $P_{tot}$ $K_u$ $\beta$ $K_{fe}$ ns: $A_c$ $W_A$ $MLT$ $\ell_e$ $A_{w1}$ , |

### U

### $K_{qfe}$ Method: Summary

- Method enforces an operating  $\Delta B$  in which core and copper losses are minimized

- Only takes into account losses from standard Steinmetz equation; not correct unless waveforms are sinusoidal

- Does not consider high frequency losses

- Step-by-step design procedure included on website

| טר |  |  |

|----|--|--|

|    |  |  |

|    |  |  |

|    |  |  |

|    |  |  |

|    |  |  |