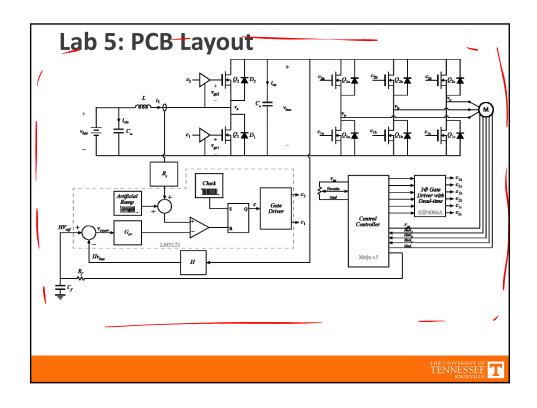

### **PCB Layout**

ECE 482 Lecture 7 March 10, 2015

### **Announcements**

- Prelab 5 due Thursday

- Decide on System Improvements

- Experiment 4 report moved to Thurs. 3/26

- Midterm after spring break

- Open note, book, instructor

- Today: Experiment 5

- No report; deliverables are layout files

## **Basic PCB Layout Concepts**

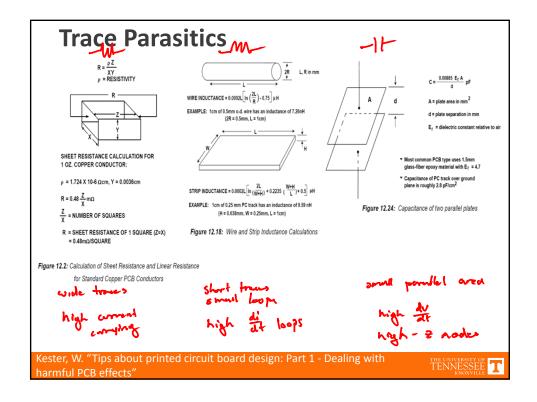

- Trace Parasitics

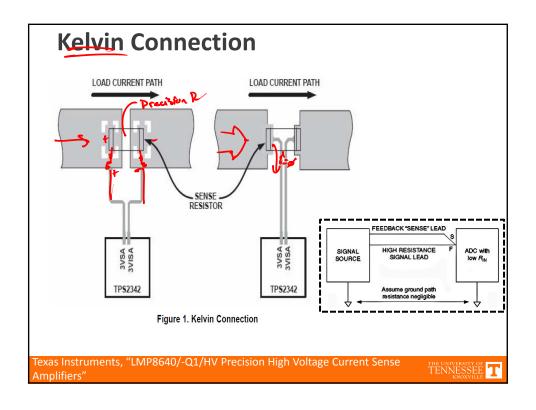

- Kelvin Connection

- Parasitic Capacitances and Decoupling

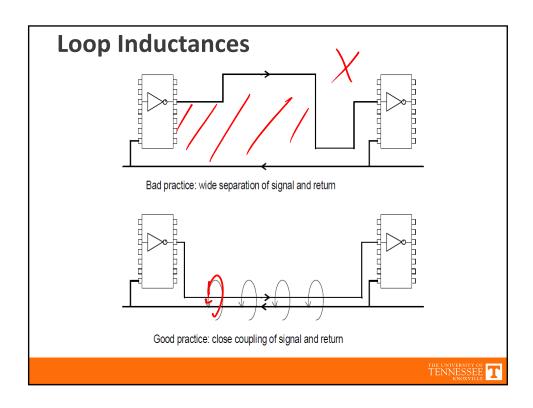

- Loop Inductances

- Ground Plane / Return Currents

- Partitioning

TENNESSEE

# **Trace Sizing Rough Guidelines**

#### 2.2 PCB Etch

Table 1 is helpful to determine the current carrying capacity of PCB etches. The table assumes:

- 1oz/sq foot copper (0.035mm thickness).

- 10°C rise on outer layers, 20°C inner layers

- . Groups of high current tracks are de-rated

- . Tracks are not near or over heat sink areas

Table 1. Current Capacity PCB Etch

| WIDTH  | CURRENT CAPACITY |

|--------|------------------|

| 0.010" | 0.8 A            |

| 0.015" | 1.2 A            |

| 0.020" | 1.5 A            |

| 0.050" | 3.2 A            |

| 0.100" | 6.0 A            |

#### 2.3 Vias or Feedthrus

Vias limit the current and add inductance between the power supply and load. Layouts are usually done with 10-mil inner ring feedthrus. At this size, current capability is about 1 A per feedthru.

Kester, W. "Tips about printed circuit board design: Part 1 - Dealing with harmful PCB effects"

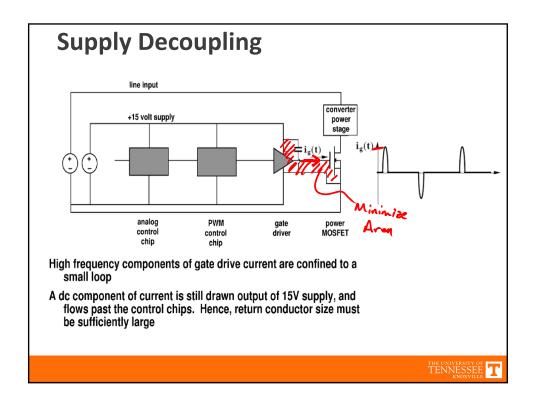

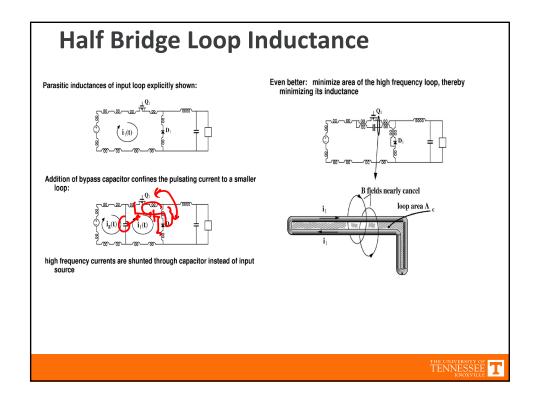

## **Decoupling**

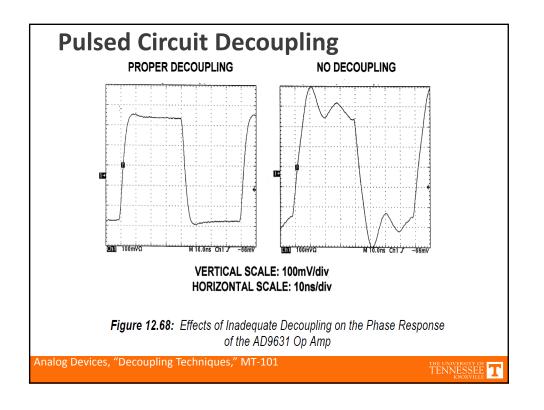

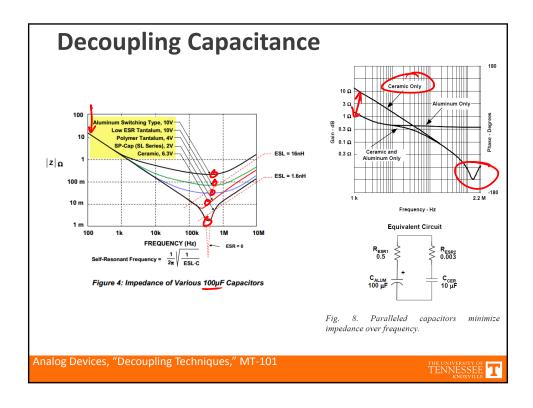

- Always add bypass capacitor at power supply for any IC/reference

- Use small-valued (~100nf), low ESR and ESL capacitors (ceramic)

- Limit loop for any di/dt

THE UNIVERSITY OF TENNESSEE T

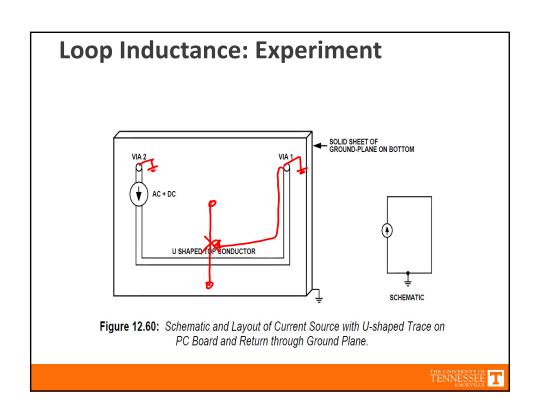

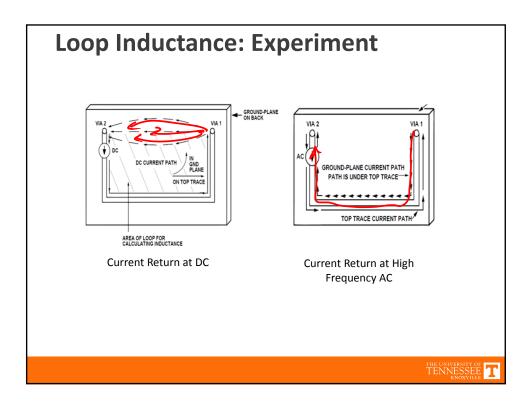

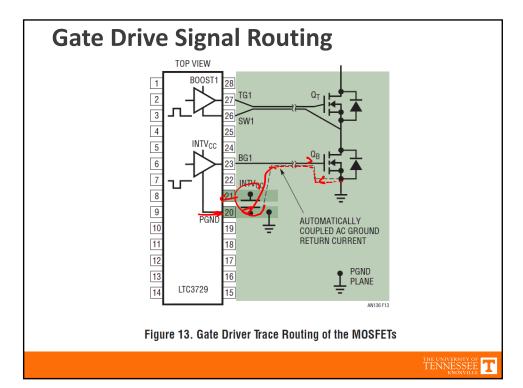

## **Complete Routing of Signal**

- Always consider return path

- Ground plane can help, but still need to consider the path and optimize

TENNESSEE T

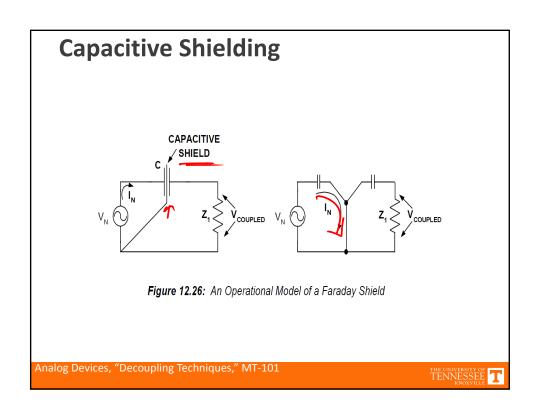

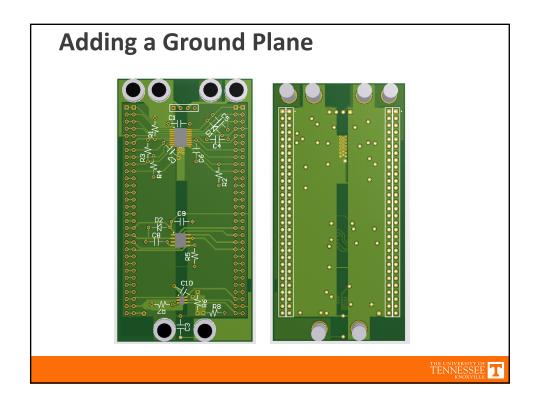

### **Ground Plane**

- Benefits:

- Common reference voltage

- Shielding

- Heat dissipation

- Reduced inductance (increased capacitance)

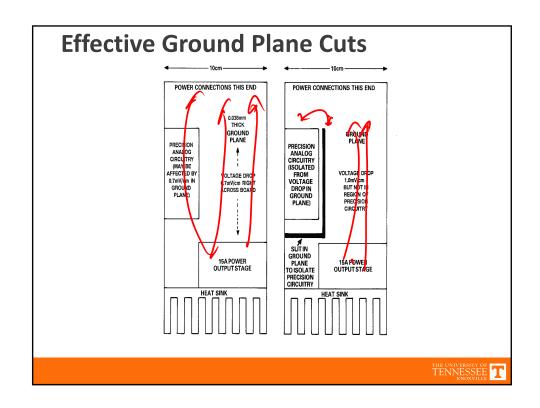

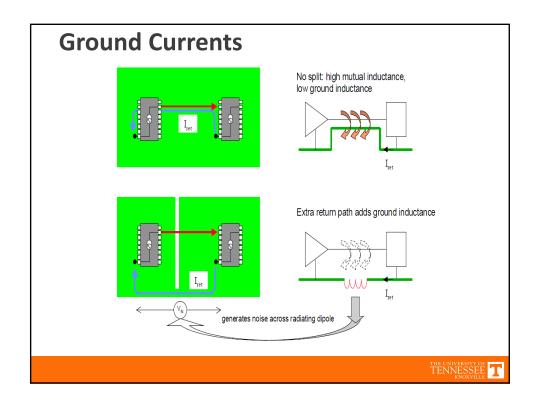

- Resist urge to cut ground plane as much as possible; consider paths of return currents when cuts are unavoidable

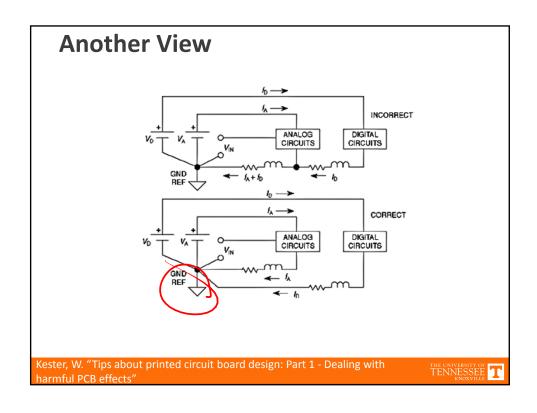

#### **A Poor Ground Plane Layout** ground plane Return current of noisy circuit runs power underneath sensitive supply circuits, and can still sensitive Noisy sensitive circuit corrupt their ground power circuit circuit references supply return A solution is to remove the ground plane noisy circuit from the ground plane. One power could then run a supply separate ground wire for sensitive sensitive Noisy the noisy circuit. The circuit circuit power circuit only drawback is that supply return noise can be coupled into the input signal v.

#### **Cuts in Ground Plane**

- Goals:

- minimize inductance/loops

- Minimize ground interference

- Routing cuts should be kept short and out of the path of any significant (high frequency) return paths

- Cuts can be used effectively for ground isolation, and to reduce noise coupled between digital/analog/power circuitry

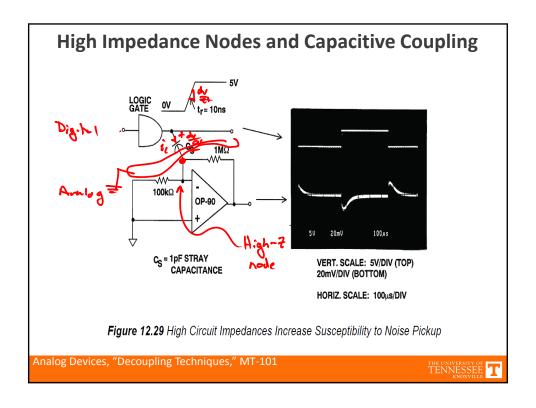

- Reducing parasitic capacitance in sensitive signal locations (i.e. op-amp circuitry)