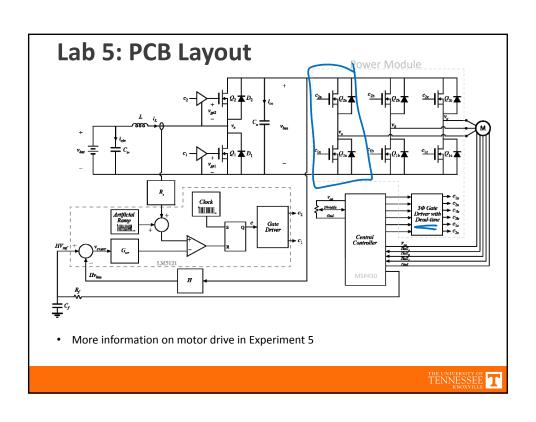

## **PCB Layout**

ECE 482 Lecture 5 March 7, 2016

## **Announcements**

- Prelab 5 due Tuesday

- Decide on System Improvements

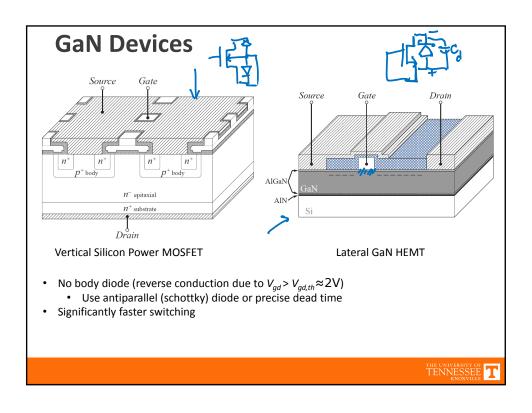

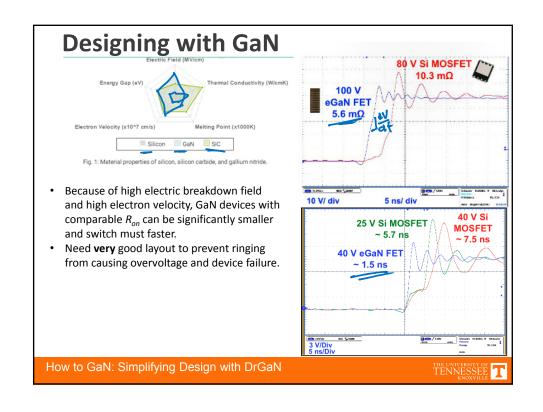

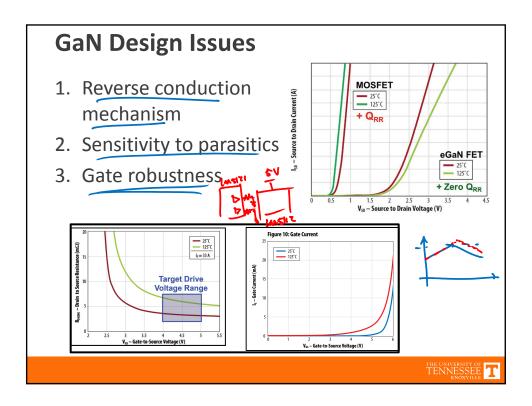

- Redesign using GaN Devices

- Experiment 4 report moved to Thurs. 3/24

- Midterm after spring break

- Open note, book, instructor

- Today: Experiment 5

- No report; deliverables are layout files

# **Design Modification**

- You may order additional parts, at reasonable cost/benefit

- Will need to provide a listing of parts from digikey with final Exp 5 files

- Reuse components from lab kit where possible

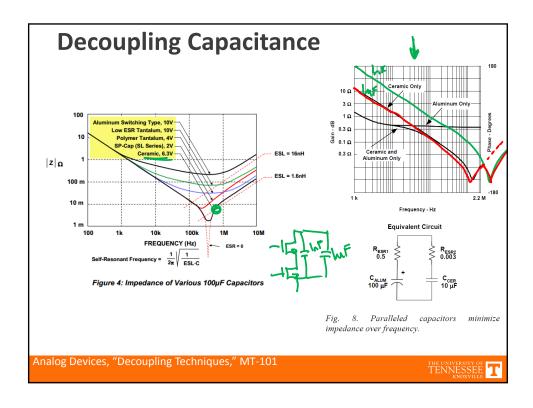

- Use SMD ceramic, low ESR caps for power stage and gate drive decoupling

## **Prelab for Experiment 5: Redesign with GaN**

#### **GaN Systems GS61008T**

- 7.4 mOhm

- 100V/80A

- $Q_q = 12 \text{ nC}$

- $C_{oss} = 250 \text{ pF (80V)}$

- Top-cooled

#### **EPC EPC2001C**

- 7 mOhm

- 100V/36A

- Q<sub>g</sub> = 9 nC

C<sub>oss</sub> = 375 pF (80V)

- · Bottom-cooled

#### **WBG Device Characterization**

- Seminar Monday, March 7<sup>th</sup>, 12:00-4:00pm

- Registration (w/ lunch)

- https://docs.google.com/forms/d/15xaqCM\_jwjD 1CW0e9Iny0jaBLruwjLZXFPu7Za8FWcM/viewform

- Also available remotely via WebEx

THE UNIVERSITY OF TENNESSEE T

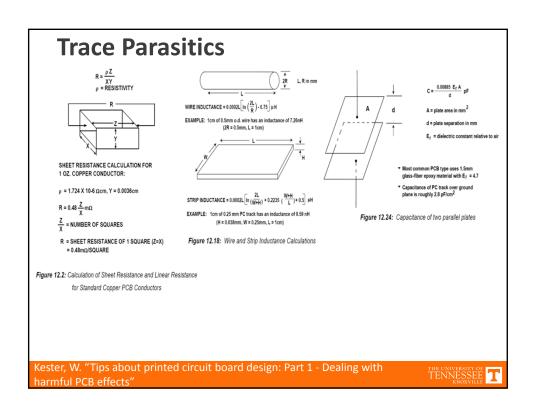

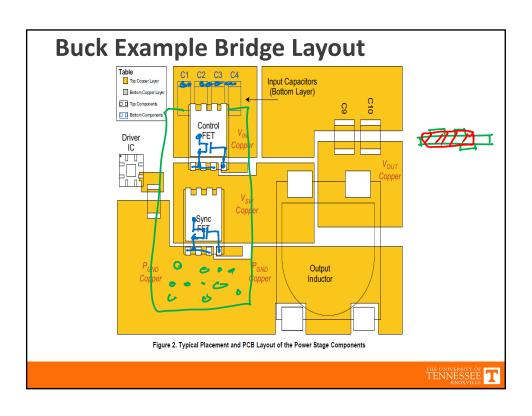

# **Basic PCB Layout Concepts**

- Trace Parasitics

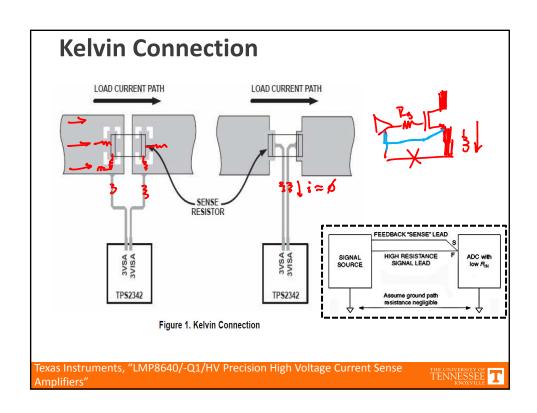

- Kelvin Connection

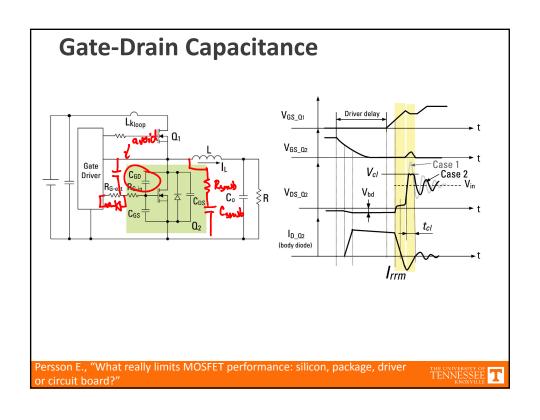

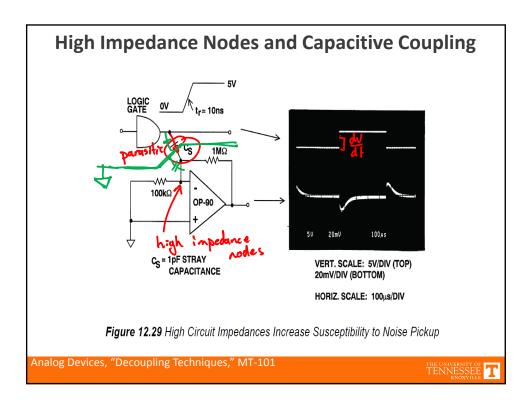

- Parasitic Capacitances and Decoupling

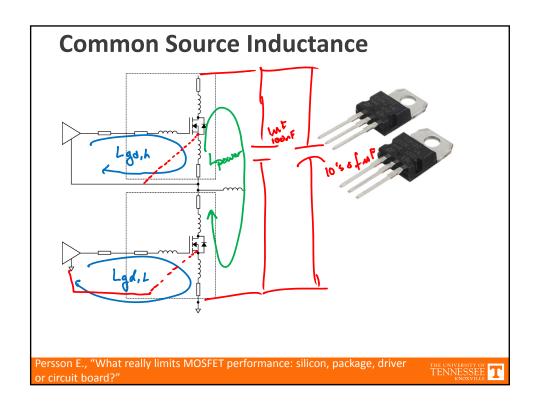

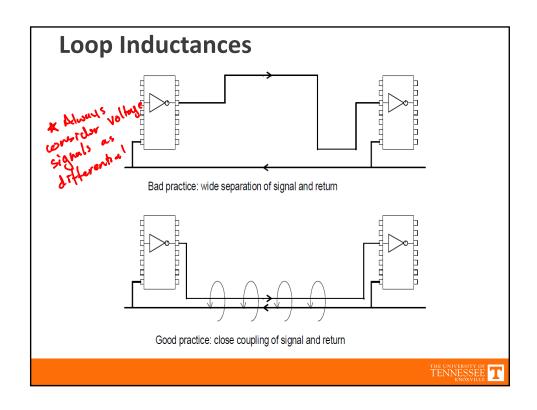

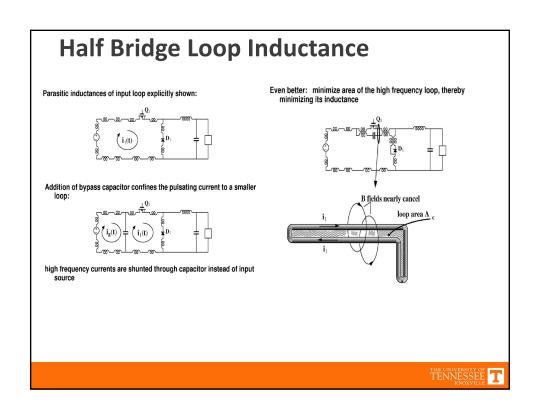

- Loop Inductances

- Ground Plane / Return Currents

- Partitioning

# **Trace Sizing Rough Guidelines**

#### 2.2 PCB Etch

Table 1 is helpful to determine the current carrying capacity of PCB etches. The table assumes:

- 1oz/sq foot copper (0.035mm thickness).

- 10°C rise on outer layers, 20°C inner layers

- . Groups of high current tracks are de-rated

- . Tracks are not near or over heat sink areas

Table 1. Current Capacity PCB Etch

| WIDTH  | CURRENT CAPACITY |

|--------|------------------|

| 0.010" | 0.8 A            |

| 0.015" | 1.2 A            |

| 0.020" | 1.5 A            |

| 0.050" | 3.2 A            |

| 0.100" | 6.0 A            |

#### 2.3 Vias or Feedthrus

Vias limit the current and add inductance between the power supply and load. Layouts are usually done with 10-mil inner ring feedthrus. At this size, current capability is about 1 A per feedthru.

Kester, W. "Tips about printed circuit board design: Part 1 - Dealing with harmful PCB effects"

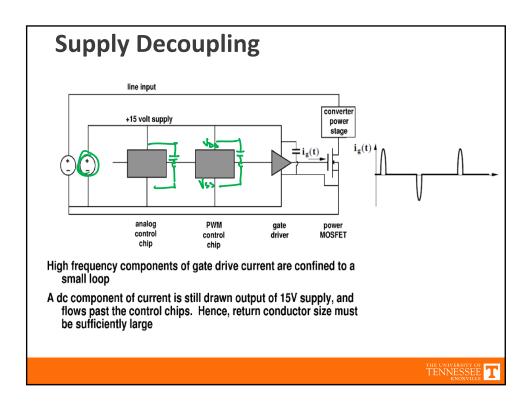

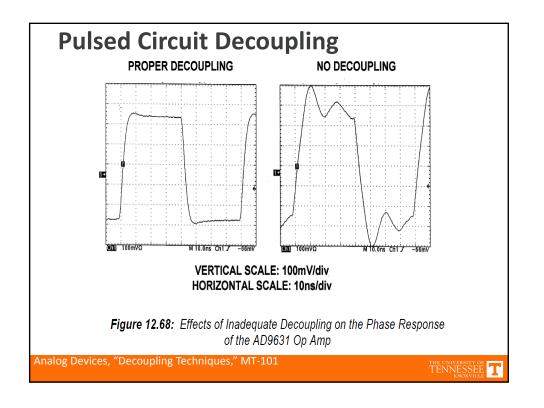

# **Decoupling**

- Always add bypass capacitor at power supply for any IC/reference

- Use small-valued (~100nf), low ESR and ESL capacitors (ceramic)

- Limit loop for any di/dt

THE UNIVERSITY OF TENNESSEE T

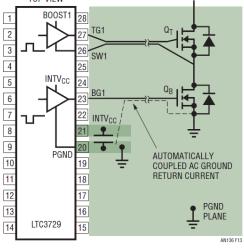

# Gate Drive Signal Routing TOP VIEW 1 BOOST1 28

Figure 13. Gate Driver Trace Routing of the MOSFETs

TENNESSEE T

# **Complete Routing of Signal**

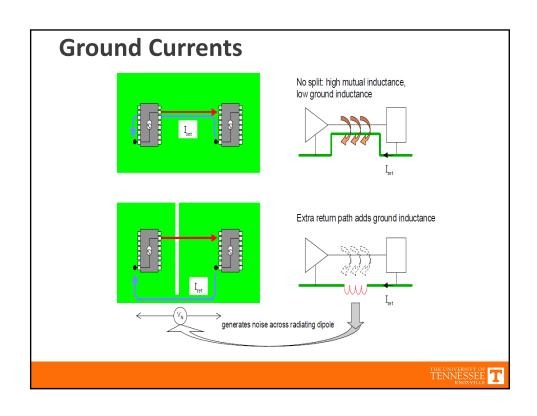

- Always consider return path

- Ground plane can help, but still need to consider the path and optimize

TENNESSEE T

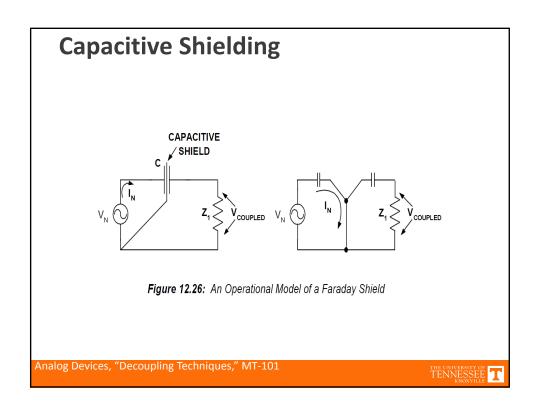

## **Ground Plane**

- Benefits:

- Common reference voltage

- Shielding

- Heat dissipation

- Reduced inductance (increased capacitance)

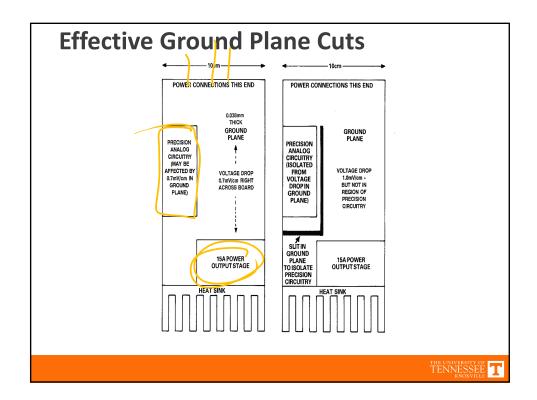

- Resist urge to cut ground plane as much as possible; consider paths of return currents when cuts are unavoidable

### **Cuts in Ground Plane**

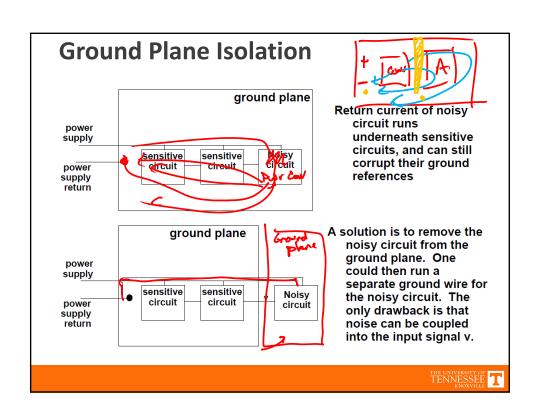

- · Goals:

- minimize inductance/loops

- Minimize ground interference

- Routing cuts should be kept short and out of the path of any significant (high frequency) return paths

- Cuts can be used effectively for ground isolation, and to reduce noise coupled between digital/analog/power circuitry

- Reducing parasitic capacitance in sensitive signal locations (i.e. op-amp circuitry)

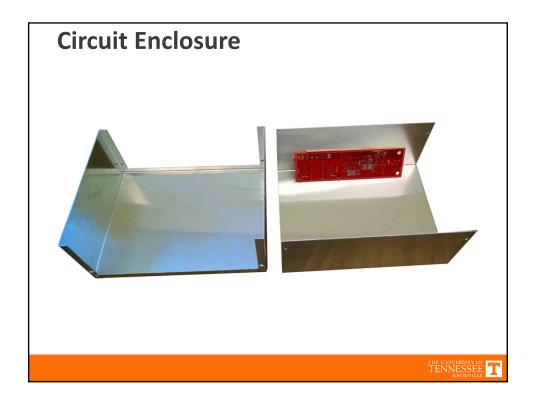

| <b>Experiment 5: Starting Files</b> |                   |

|-------------------------------------|-------------------|

|                                     |                   |

|                                     |                   |

|                                     |                   |

|                                     |                   |

|                                     |                   |

|                                     |                   |

|                                     |                   |

|                                     | THE INDUSTRIES OF |

|                                     | TENNESSEE T       |