#### **Power Electronics Circuits**

Prof. Daniel Costinett

ECE 482 Lecture 3 January 26, 2016

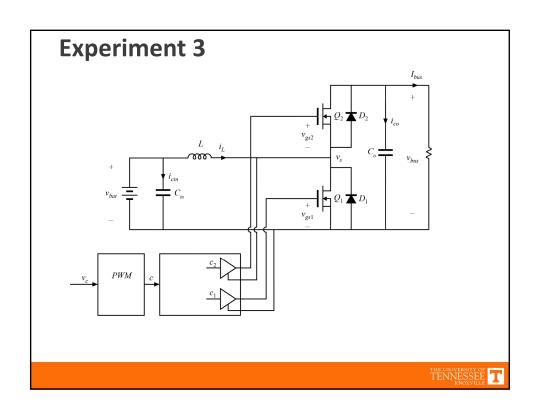

#### **Prelab Assignment Experiment 3 ÉCE 482**

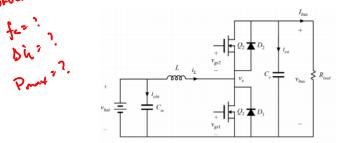

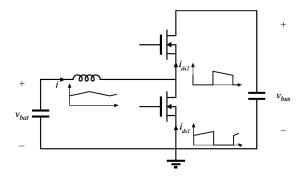

Fig. 1 shows the power stage of the drivetrain boost converter to be assembled in experiment 3. For all parts of this prelab, consider operation of the converter at an operating point around which:

- 5 kHz  $\leq f_s \leq$  1 MHz

- $\Delta v_{out} \le 1 \text{ V}$

Figure 1: Open loop boost converter (implementation shown with MOSFET devices)

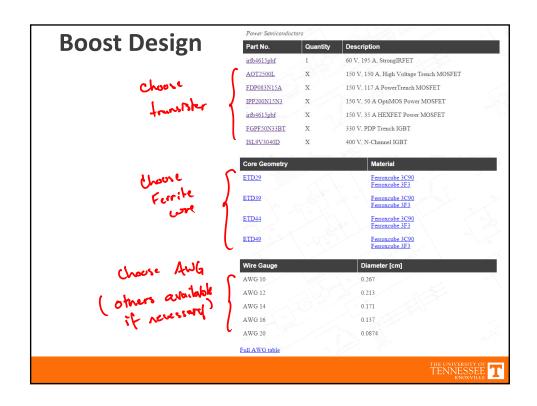

#### **Design Assessment**

In experiment 3, a portion of your grade will be the performance of the design that you choose to build. A 20% segment of the lab grade will be determined by the following formula, which rewards designs with small size, high efficiency, and high power capability:

Grade [%] =

$$25 - \kappa_{core} - 100 \cdot (0.98 - \eta_{Pout=100}) - \frac{P_{max} - 250}{50}$$

where

$$\kappa_{core} = \begin{cases} 0, & ETD29/EFD25 \\ 3, & ETD39 \\ 6, & ETD44 \\ 9, & ETD49 \end{cases}$$

According to the inductor core you have chosen for your design.  $P_{max}$  is the maximum power tested, which must be at least 100W, and may be as high as 250W.

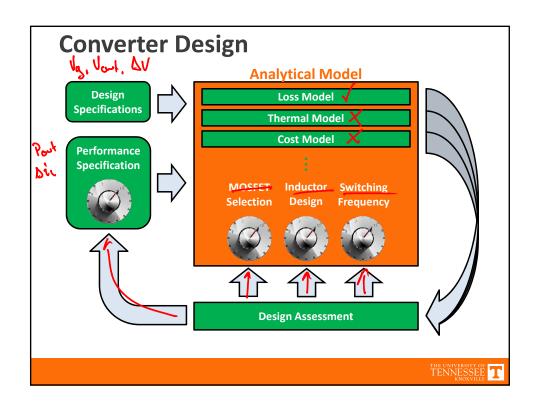

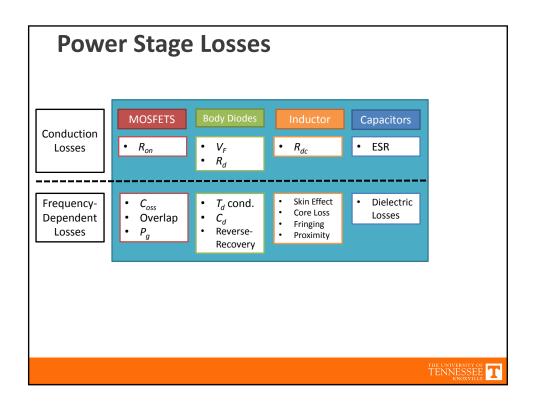

#### **Analytical Loss Modeling**

- High efficiency approximation is acceptable for hand calculations, as long as it is justified

- Solve ideal waveforms of lossless converter, then calculate losses

- Argue which losses need to be included, and which may be neglected

- "Rough" approximation to gain insight into significance

TENNESSEE T

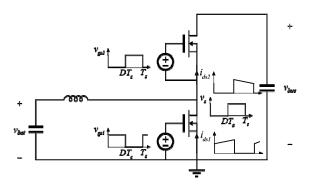

#### **Boost Converter Loss Analysis**

Begin by solving important waveforms throughout converter assuming lossless operation

- Considering only power stage losses (gate drive neglected)

- MOSFET operated as power switch

- Intrinsic body diode behaviors considered using normal diode analysis

TENNESSEE TENNESSEE

#### **Boost Converter RMS Currents**

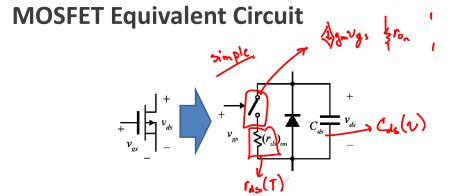

• MOSFET conduction losses due to  $(r_{ds})_{on}$  depend given as

$$P_{cond,FET} = I_{di,rms}^{2} (r_{ds})_{on}$$

TENNESSEE T

(A.6)

#### **MOSFET Conduction Losses**

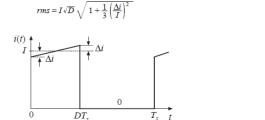

Pulsating waveform with linear ripple, Fig. A.6:

Fig. A.6

• RMS values of commonly observed waveforms appendix from Power Book

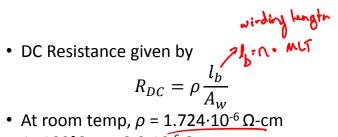

#### **DC Inductor Resistance**

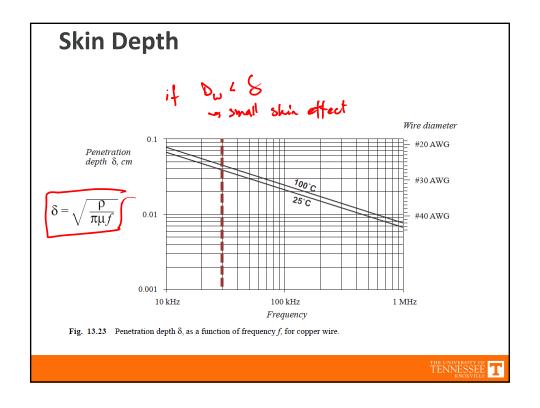

- At room temp,  $\rho = 1.724 \cdot 10^{-6} \,\Omega$ -cm At 100°C,  $\rho = 2.3 \cdot 10^{-6} \,\Omega$ -cm

- Losses due to DC current:

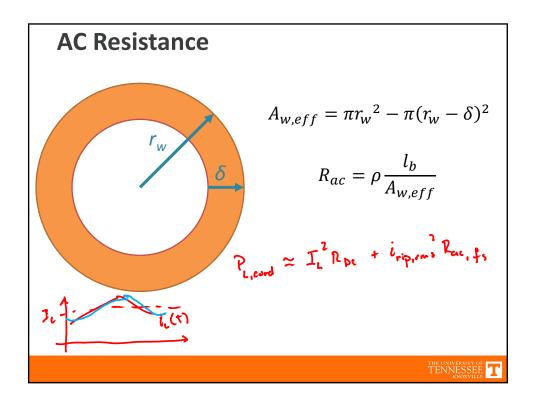

$$P_{cu,DC} = I_{L,rms}^{2} R_{DC}$$

#### **Inductor Conduction Losses**

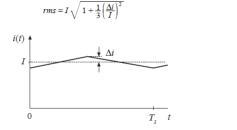

DC plus linear ripple, Fig. A.2:

Fig. A.2

Conduction losses dependent on RMS current through inductor

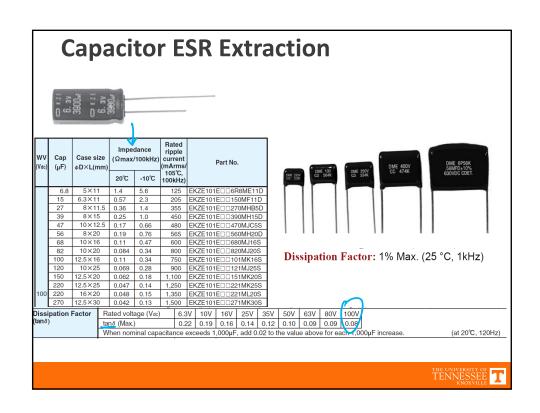

#### **Capacitor Loss Model**

-Re(Z)

-Im(Z)

- · Operation well below resonance

- All loss mechanisms in a capacitor are generally lumped into an empirical loss model

- Equivalent Series Resistance (ESR) is highly frequency dependent

- Datasheets may give effective impedance at a frequency, or loss factor:

$$\delta = \frac{\pi}{2} - \theta$$

$$D = \tan(\delta)$$

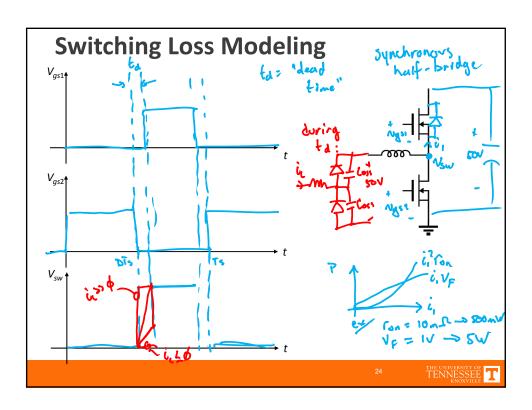

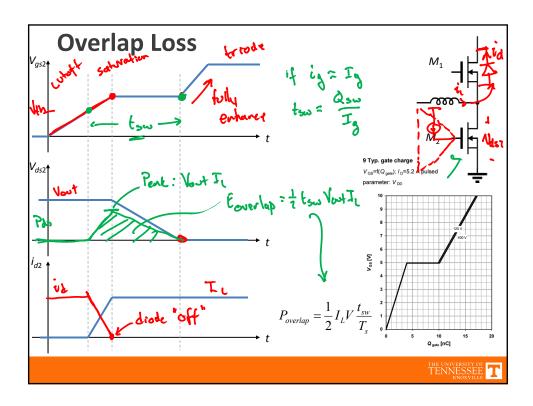

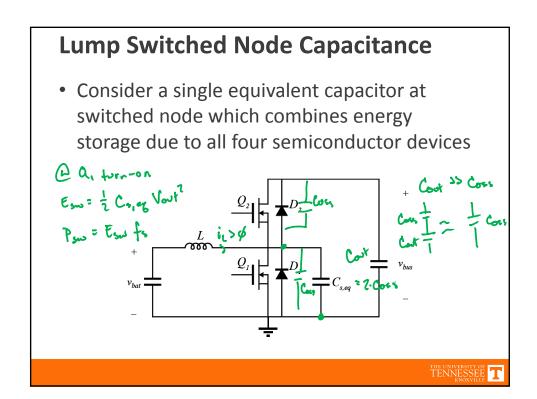

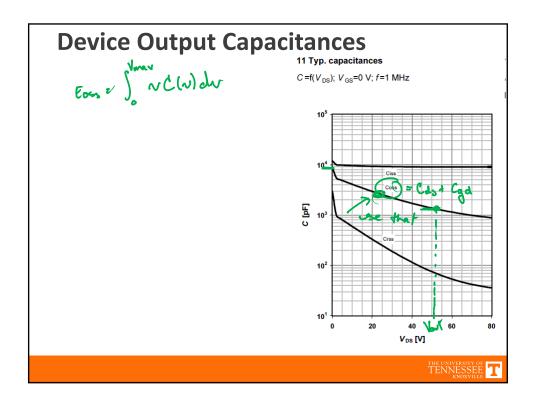

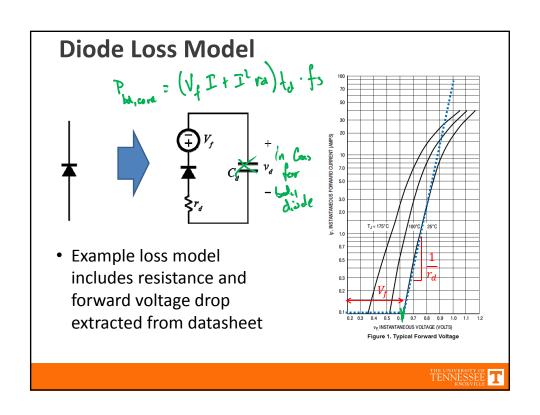

## **Types of Switching Loss**

- 1. Gate Charge Loss

- 2. Overlap Loss

- 3. Capacitive Loss

- 4. Body Diode Conduction

- 5. Reverse Recovery

- 6. Inductive Losses

THE UNIVERSITY OF TENNESSEE

Gate Charge Loss

9 Typ. gate charge  $V_{GS} = f(Q_{gain}) \cdot I_{D} = 5.2 \text{ A pulsed}$ parameter:  $V_{DD}$   $E = Q_{S}(V_{AT}) \cdot V_{AT}$   $P_{g} = Q_{g}V_{AT}S$ The entrespit of Tennessity of Tenn

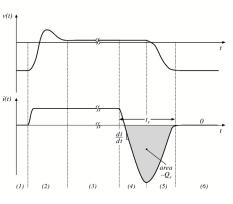

## **Diode Reverse Recovery**

- Diodes will turn on during dead time intervals

- Significant reverse recovery possible on both body diode and external diode

in low-side  $E_{on,rr} = \left( \left( I_L - \Delta i_L \right) t_{rr} + Q_{rr} \right) V_{bus}$  was fell

TENNESSEE T

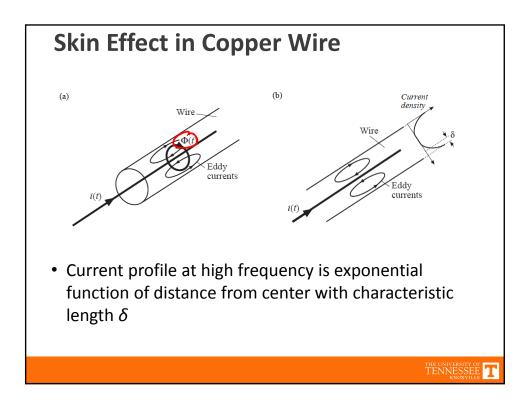

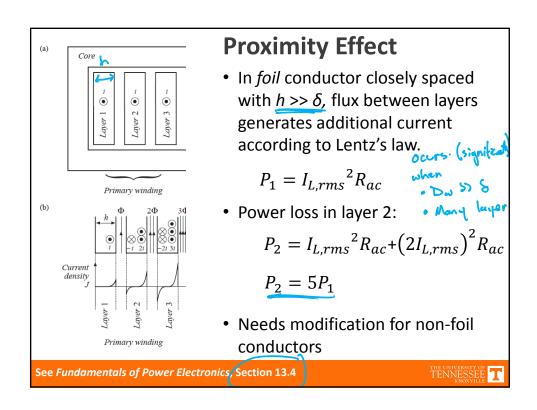

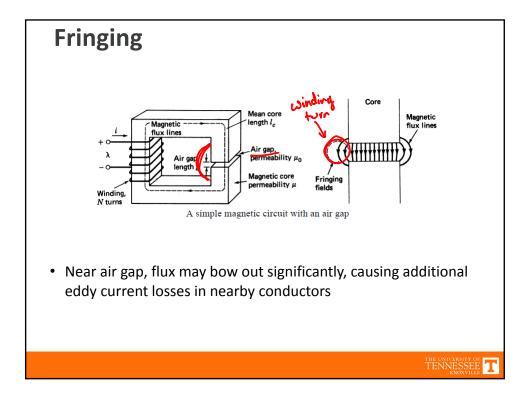

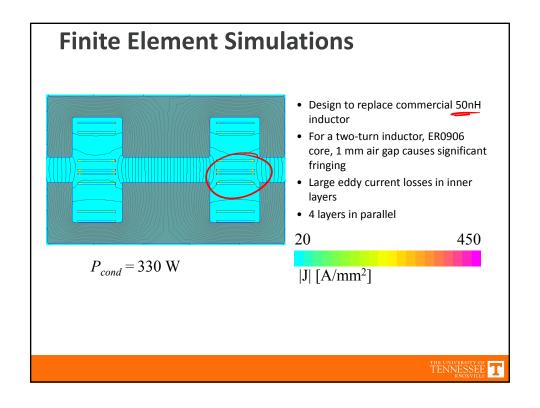

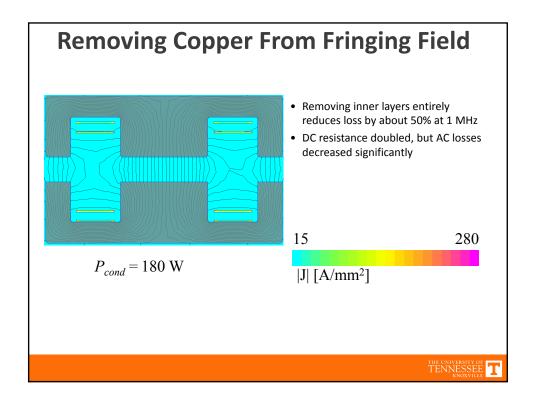

#### **Inductor AC Losses**

THE UNIVERSITY OF TENNESSEE

#### **Inductor Core Loss**

- Governed by Steinmetz Equation:

- $P_v = K_{fe} f_s^{\alpha} (\Delta B)^{\beta} \quad [\text{mW/cm}^3]$

- Parameters  $K_{fe}$ ,  $\alpha$ , and  $\beta$  extracted from manufacturer data

$$P_{fe} = P_v A_{cm} \text{ [mW]}$$

•  $\Delta B \propto \Delta i_L \rightarrow {\rm small\ losses}$  with small ripple

#### **Steinmetz Parameter Extraction**

Specific power loss as a function of peak flux density with frequency as a parameter.

#### **Ferroxcube Curve Fit Parameters**

Power losses in our ferrites have been measured as a function of frequency (f in Hz), peak flux density (B in T) and temperature (T in  $^{\circ}$ C). Core loss density can be approximated  $^{(2)}$  by the following formula :

$$P_{core} = C_m \cdot f^x \cdot B_{peak}^y(ct_0-ct_1T+ct_2T^2)$$

[3]

| $= C_m$ | CT | f ×. | $\mathbf{B}_{peak}^{\mathbf{y}}$ | [mW/cm <sup>3</sup> ] |

|---------|----|------|----------------------------------|-----------------------|

|---------|----|------|----------------------------------|-----------------------|

| ferrite  | f (kHz)   | Cm                    | x    | у    | ct <sub>2</sub>       | ct <sub>1</sub>       | ct <sub>0</sub> |

|----------|-----------|-----------------------|------|------|-----------------------|-----------------------|-----------------|

| 3C30     | 20-100    | 7.13.10 <sup>-3</sup> | 1.42 | 3.02 | 3.65.10 <sup>-4</sup> | 6.65.10 <sup>-2</sup> | 4               |

|          | 100-200   | 7.13.10 <sup>-3</sup> | 1.42 | 3.02 | $4.10^{-4}$           | 6.8 .10 <sup>-2</sup> | 3.8             |

| 3C90 →   | 20-200    | 3.2.10 <sup>-3</sup>  | 1.46 | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

| 3C94     | 20-200    | 2.37.10 <sup>-3</sup> | 1.46 | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

| 0        | 200-400   | 2.10 <sup>-9</sup>    | 2.6  | 2.75 | 1.65.10 <sup>-4</sup> | 3.1.10 <sup>-2</sup>  | 2.45            |

| 3F3      | 100-300   | 0.25.10 <sup>-3</sup> | 1.63 | 2.45 | $0.79.10^{-4}$        | 1.05.10 <sup>-2</sup> | 1.26            |

| <b>~</b> | 300-500   | 2.10 <sup>-5</sup>    | 1.8  | 2.5  | $0.77.10^{-4}$        | 1.05.10 <sup>-2</sup> | 1.28            |

|          | 500-1000  | 3.6.10-9              | 2.4  | 2.25 | 0.67.10-4             | 0.81.10-2             | 1.14            |

| 3F4      | 500-1000  | 12.10 <sup>-4</sup>   | 1.75 | 2.9  | 0.95.10 <sup>-4</sup> | 1.1.10-2              | 1.15            |

|          | 1000-3000 | 1.1.10 <sup>-11</sup> | 2.8  | 2.4  | 0.34.10-4             | 0.01.10 <sup>-2</sup> | 0.67            |

Table 1: Fit parameters to calculate the power loss density

TENNESSEE 7

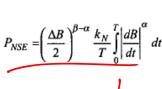

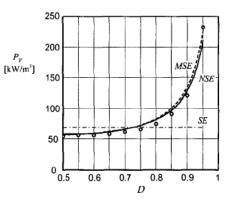

# NSE/iGSE

- More complex empirical loss models exist, and remain valid for non-sinusoidal waveforms

- NSE/iGSE:

iden Bossche, A.; Valchev, V.C.; Georgiev, G.B.; , "Measurement and loss model of ferrites with non-sinusoidal waveforms," Power Electronics Specialists Conference, 2004. PESC 04. 2004 IEEE 35th Annual , vol.6, no., pp. 4814-4818 Vol.6, 20-25 June 2004 doi: 10.1109/PEG-2004.1354851 THE UNIVERSITY OF TENNESSEE T

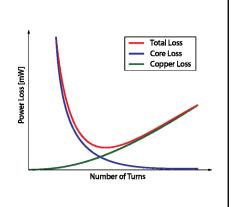

## **Minimization of Losses**

- For given core, number of turns can be used to index possible designs, with air gap solved after (and limited) to get correct inductance

- A minimum sum of the two exists and can be solved for

TENNESSEE TENNESSEE

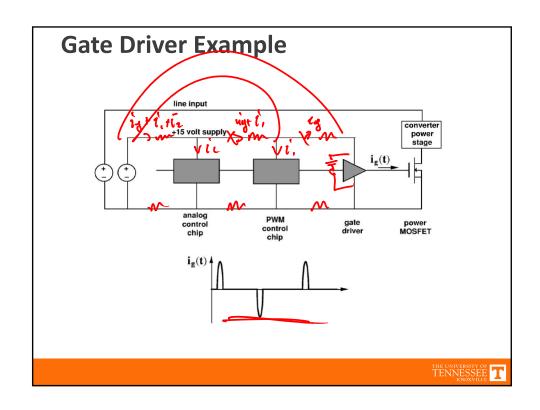

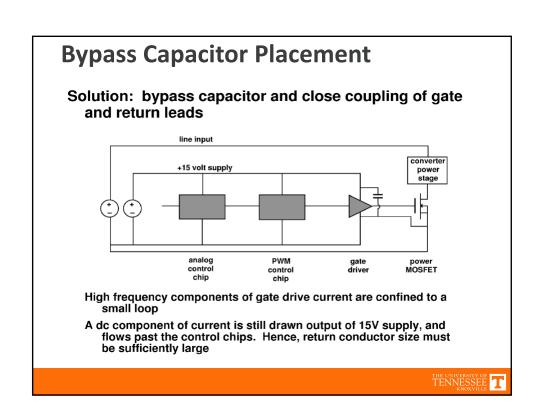

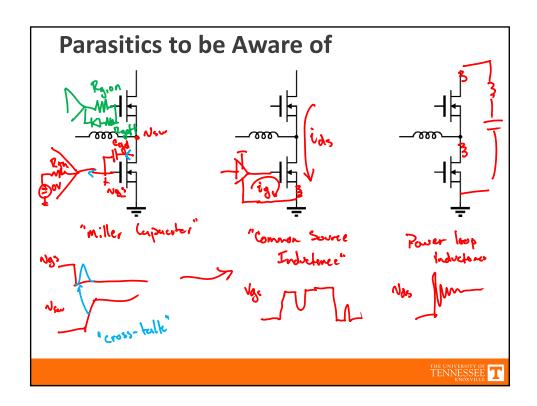

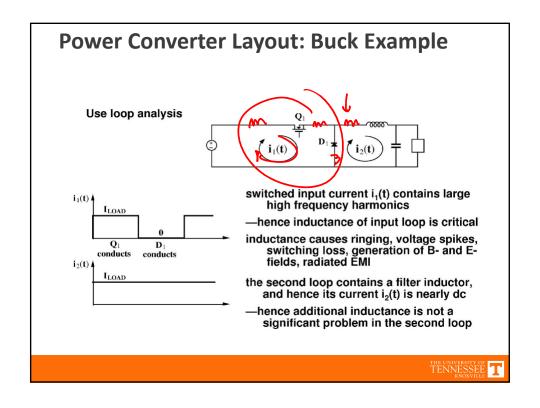

#### **Parasitic Wire Inductances**

Parasitic inductances of input loop explicitly shown:

Addition of bypass capacitor confines the pulsating current to a smaller

high frequency currents are shunted through capacitor instead of input

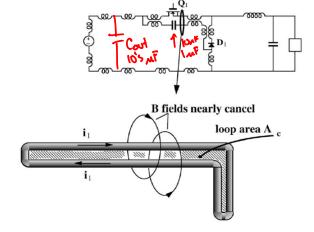

### **Loop Minimization**

Even better: minimize area of the high frequency loop, thereby minimizing its inductance

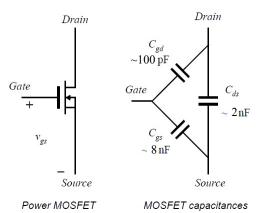

#### **Driving a Power MOSFET Switch**

- MOSFET is off when  $v_{gs} < V_{th} \approx$  3 V

- MOSFET fully on when  $v_{gs}$  is sufficiently large (10-15 V)

- Warning: MOSFET gate oxide breaks down and the device fails when  $v_{gs} > 20 \text{ V}$ .

- Fast turn on or turn off (10's of ns) requires a large spike (1-2 A) of gate current to charge or discharge the gate capacitance

- MOSFET gate driver is a logic buffer that has high output current capability

ENNESSEE T

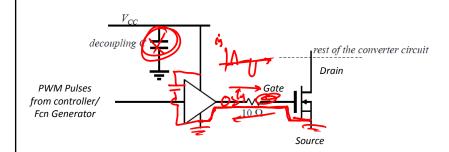

#### **Driving a Power MOSFET Switch**

- MOSFET gate driver is used as a logic buffer with high output current (~1.8 A) capability

- The amplitude of the gate voltage equals the supply voltage VCC

- Decoupling capacitors are necessary at all supply pins of LM5104 (and all ICs)

- Gate resistance used to slow dv/dt at switch node