### **GaN Devices**

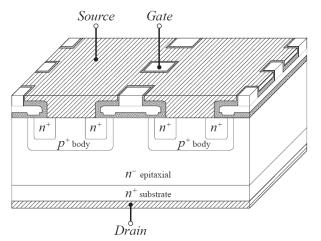

Vertical Silicon Power MOSFET

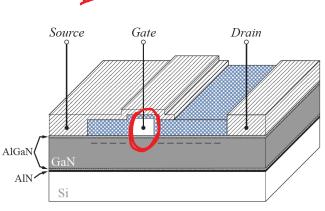

Lateral GaN HEMT

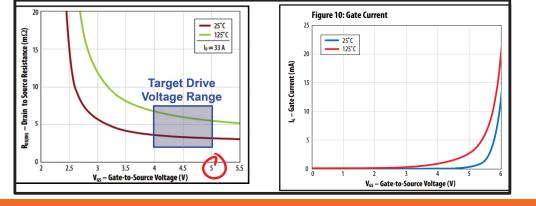

Use antiparallel (schottky) diode or precise dead time

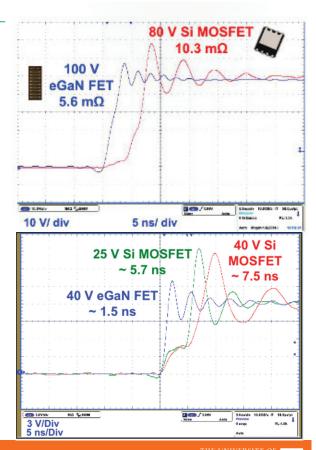

Significantly faster quitching

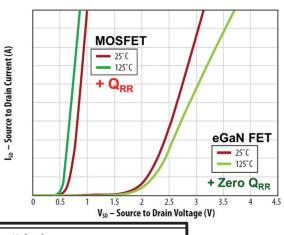

No body diode (reverse conduction due to  $V_{ad} > V_{ad,th} \approx 2V$ )

Significantly faster switching

### Designing with GaN Electric Field (MV/cm) Energy Gap (eV) Thermal Conductivity (W/cmK) Electron Velocity (x10^7 cm/s) Melting Point (x1000K) Silicon GaN SiC

Fig. 1: Material properties of silicon, silicon carbide, and gallium nitride.

- Because of high electric breakdown field and high electron velocity, GaN devices with comparable *R*<sub>on</sub> can be significantly smaller and switch must faster.

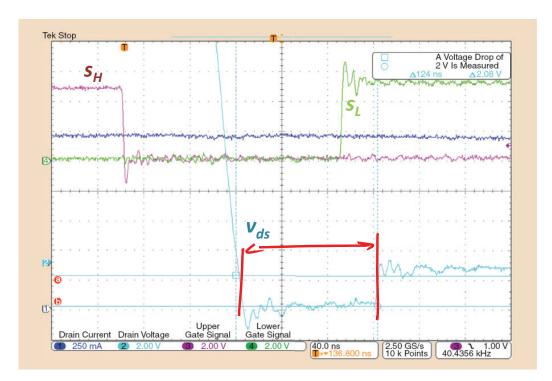

- Need **very** good layout to prevent ringing from causing overvoltage and device failure.

- More information:

- http://potenntial.eecs.utk.edu/About. php?topic=PowerSemiconductors

TENNE

How to GaN: Simplifying Design with DrGaN

## **GaN Design Issues**

- 1.- Reverse conduction mechanism

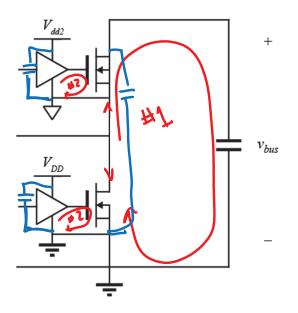

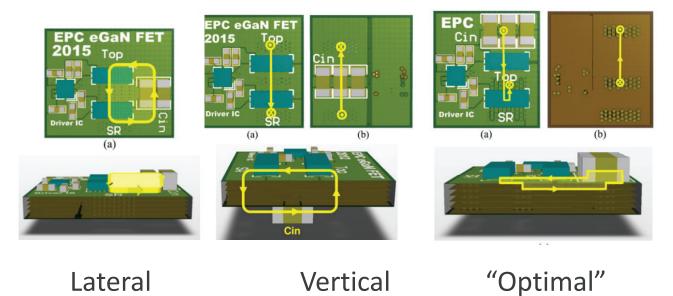

- 2.-- Sensitivity to parasitics

- 3.-- Gate robustness

- 4.- Small size -> Thermal, soldering difficult

EPC

TENNESSEE KNOXVILLE

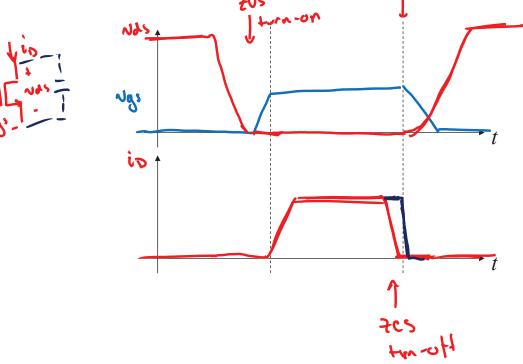

### **Reverse Conduction**

P Shamsi, M Mcdonough, and B Fahimi, "Wide-Bandgap Semiconductor Technology: Its impact on the electrification of the transportation industry" 2013

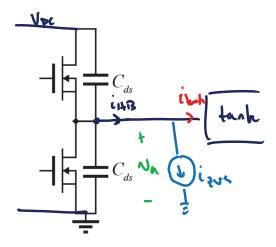

### **Bridge Layout**

TENNESSEE KNOXVILLE

### Half Bridge Layout: Example

### **Kelvin Measurement**

### TENNESSEE T

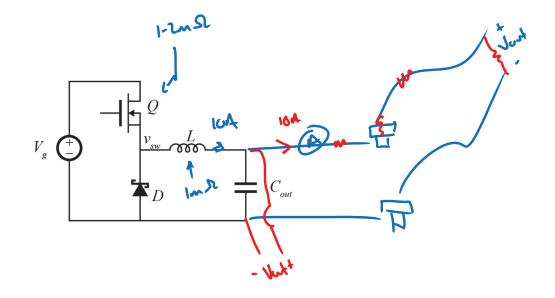

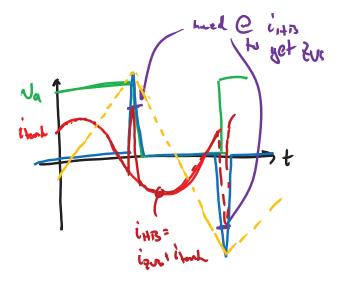

### **ZVS Assist Circuits**

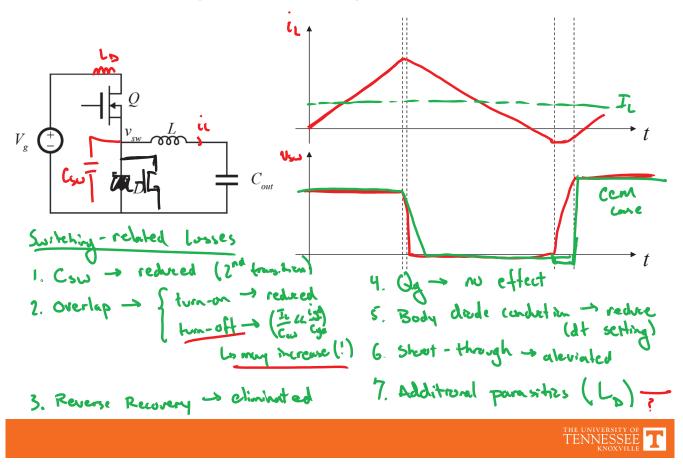

### **Remaining Switching Losses**

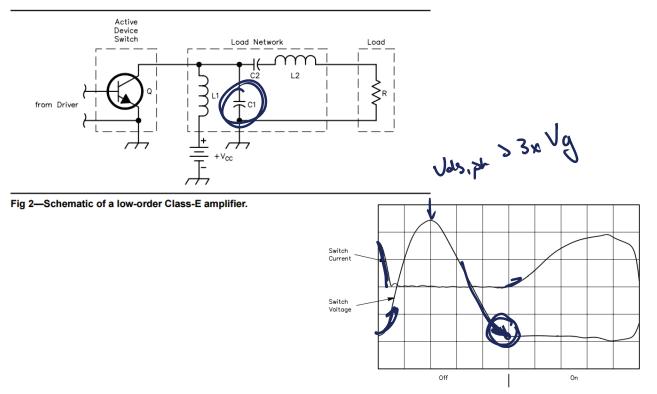

### **Class-E Amplifier**

Fig 3—Actual transistor voltage and current waveforms in a low-order Class-E amplifier.

N. O. Sokal, "Class-E RF Power Amplifiers," 2001

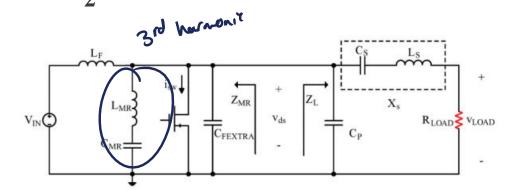

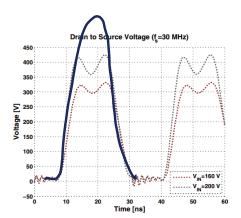

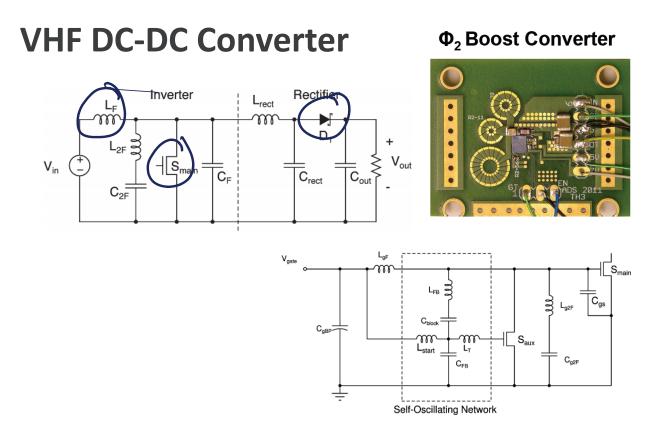

# Class $\Phi_2$ Inverter

<u>TENNE</u>SSEI

J. M. Rivas, O. Leitermann, Y. Han, A. D. Sagneri, and D. J. Perreault, " A High-Frequency Resonant Inverter Topology With Low-Voltage Stress", 2008

#### TENNESSEE KNOXVILLE

Fig. 5. Trapezoidal resonant gate drive circuit with self-oscillating network. The converter is enabled by applying the voltage  $V_{\rm gate}$ , and disabled by setting  $V_{\rm gate}$  to zero. This gate driver is employed in the 110-MHz converter (Fig. 9).

R. C. N. Pilawa-Podgurski, A. D. Sagneri, J. M. Rivas, D. I. Anderson and D. J. Perreault, "Very-High-Frequency Resonant Boost Converters," 2009