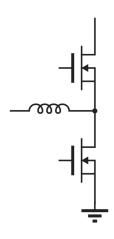

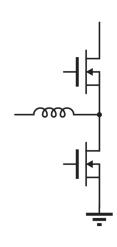

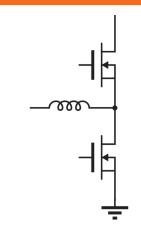

# **Synchronous Switching**

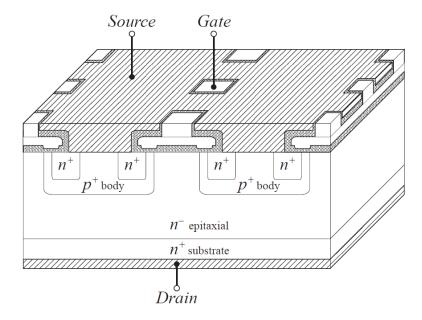

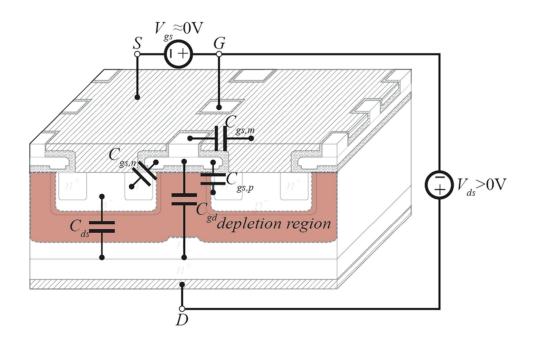

### **MOSFET Cross Section**

# **MOSFET Depletion Capacitance**

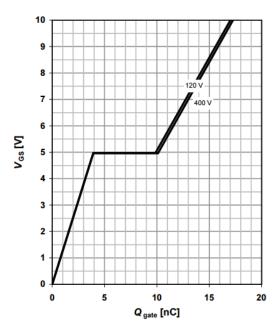

## **Gate Charge**

### 9 Typ. gate charge

$V_{\rm GS}$ =f(Q  $_{\rm gate}$ );  $I_{\rm D}$ =5.2 A pulsed

parameter: V<sub>DD</sub>

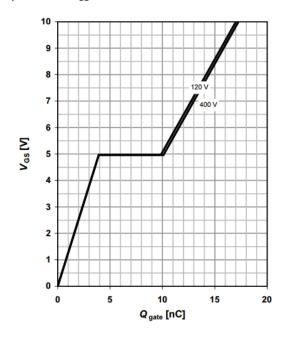

# **Overlap Time**

### 9 Typ. gate charge

| $V_{\rm GS}$ =f(Q <sub>gate</sub> ); $I_{\rm D}$ =5.2 A pulsed |

|----------------------------------------------------------------|

| parameter: V <sub>DD</sub>                                     |

| Gate threshold voltage | V <sub>GS(th)</sub> | V <sub>DS</sub> =V <sub>GS</sub> , I <sub>D</sub> =0.34 mA | 2.5 | 3   | 3.5 |   |

|------------------------|---------------------|------------------------------------------------------------|-----|-----|-----|---|

| Gate resistance        | R <sub>G</sub>      | f=1 MHz, open drain                                        | -   | 1.8 |     | Ω |

### THE UNIVERSITY OF TENNESSEE

# **FET Turn-On**

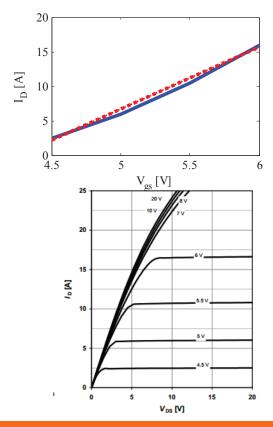

### **Device Transconductance**

TENNESSEE NOOVULLE

### T

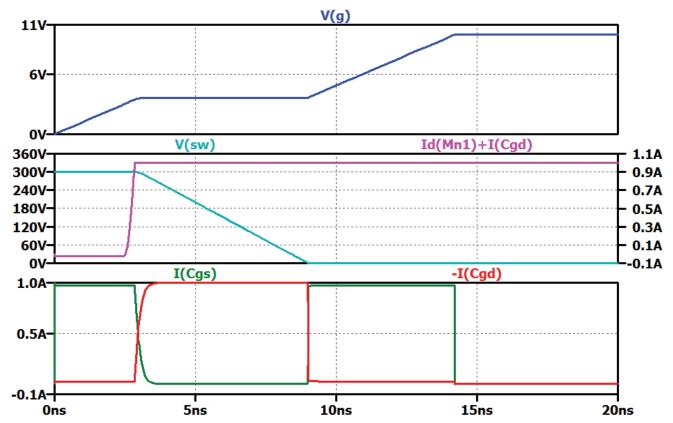

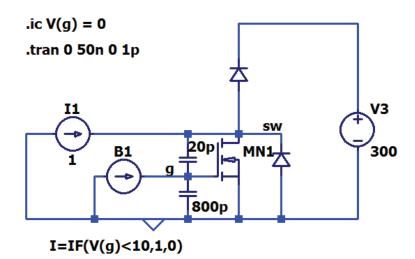

## **Example Simulation**

.model myD D(n=.01)

.model testFET VDMOS(Rg=.1 Rd=0 Rs=0 Vto=3 Kp=9 Cgdmax=0p

+ Cgdmin=0p Cgs=0p Cjo=1.5f Is=26p Rb=0m Vds=600 Ron=385m Qg=0n)

### **Simulation Waveforms – Turn On**