#### Near-Optimal Placement of MPI Processes on Hierarchical NUMA Architecture

Emmanuel Jeannot, Guillaume Mercier

LaBRI/INRIA Bordeaux Sud-Ouest/ENSEIRB

**Runtime Team**

Emmanuel.Jeannot@inria.fr

## **CCGSC** in France?

http://europar2011.inria.bordeaux.fr

## Introduction

## • MPI is the main standard for programming parallel applications

- . It provides portable code across platforms

- . What about performance portability?

## Performance of MPI programs

Depend on many factors:

- Implementation of the standard (e.g. collective com.)

- . Parallel algorithm(s)

- . Implementation of the algorithm

- . Underlying libraries (e.g. BLAS)

- . Hardware (processors, cache, network)

- etc.

- . and ...

#### **Process placement**

The MPI model makes little (no?) assumption on the way MPI processes are mapped to resources

It is often assume that the network topology is flat and hence the process mapping has little impact on the performance

## The network topology is not flat

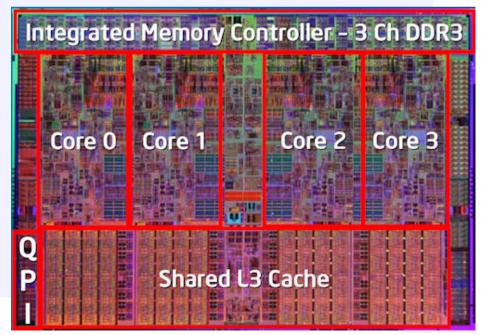

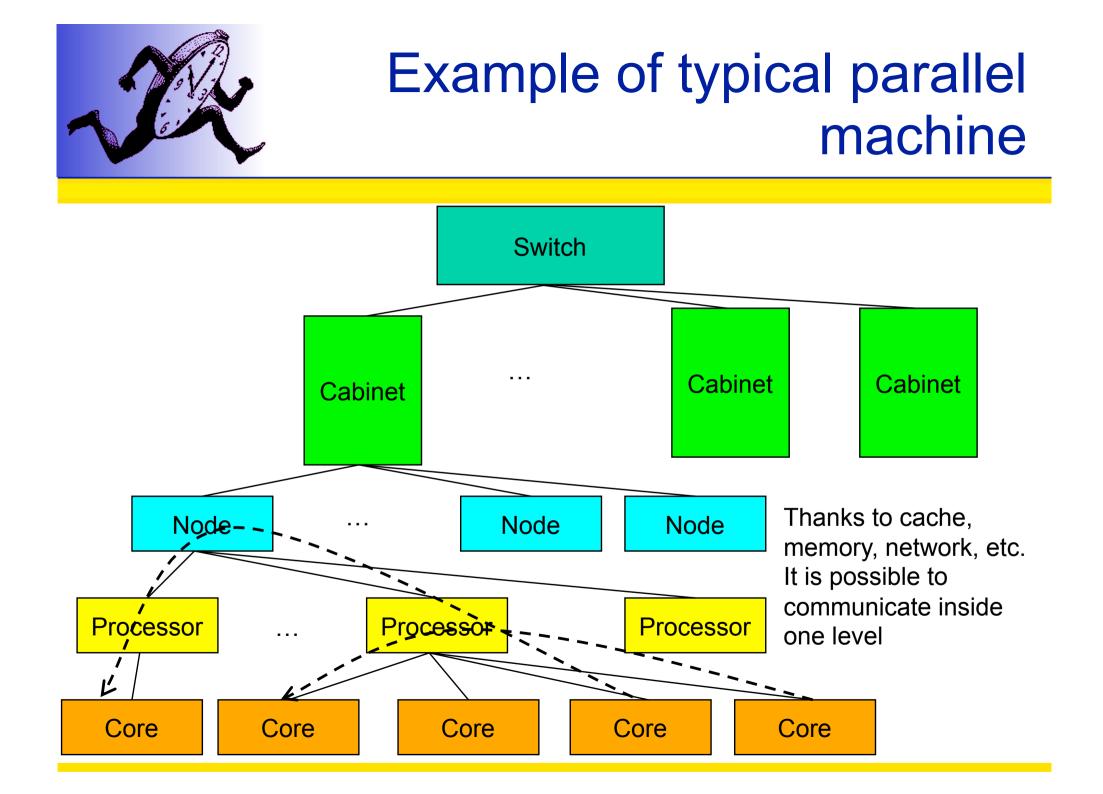

Due to multicore processors current and future parallel machines are hierarchical

#### Communication speed depend on:

- receptor and emitter

- . Cache hierarchy

- . Memory bus

- Interconnection networketc.

#### Rationale

Not all the processes exchange the same amount of data

The speed of the communications, and hence performance of the application depend on the way processes are mapped to resources.

## Process placement problem

Given:

- The parallel machine topology

- The processes communication pattern

Map processes to resources (cores) to reduce the communication cost.

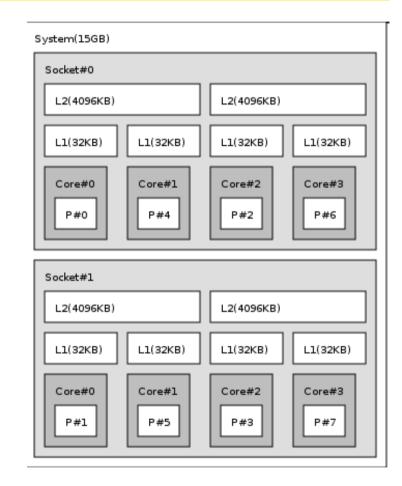

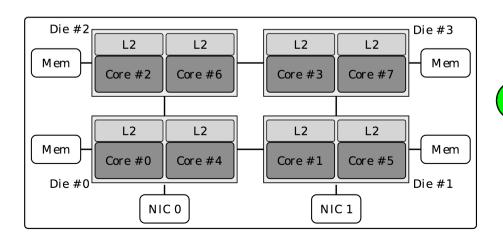

## Obtaining the toplogy

#### HWLOC (portable hardware locality)

- Runtime and OpenMPI team

- portable abstraction (across OS, versions, architectures, ...)

- Hierarchical topology

- Modern architecture (NUMA, cores, caches, etc.)

- ID of the cores

- C library to play with

- etc.

# Obtaining the communication pattern

No automatic way so far

For now done through application monitoring

Left to future work (static code analysis?)

## State of the art

Process placement fairly well studied problem:

- Graph Partitioning (Scotch/Metis): do not take hierarchy into account.

- . [Träff 2002]: placement through graph embedding and graph partitioning

- . MPIPP [Chen et al. 2006]: placement through local exchange of processes until no gain is achievable

- [Clet-Ortega & Mercier 09] : placement through graph renumbering

### Example

#### T: topology matrix

| 0    | 100   | 100  | 10   | 1000 | 100  | 100  | 10   |

|------|-------|------|------|------|------|------|------|

| 100  | 0     | 10   | 100  | 100  | 1000 | 10   | 100  |

| 100  | 10    | 0    | 100  | 100  | 10   | 1000 | 100  |

| 10   | 100   | 100  | 0    | 10   | 100  | 100  | 1000 |

| 1000 | 100   | 100  | 10   | 0    | 100  | 100  | 10   |

| 100  | 1000  | / 10 | 100  | 100  | 0    | 10   | 100  |

| 100  | 10    | 1000 | 100  | 100  | 10   | 0    | 100  |

| 10   | 100 / | 100  | 1000 | 10   | 100  | 100  | 0    |

|      |       |      |      |      |      |      |      |

Communication speed between processor 2 and processor 3

Formal problem

Input: T and C two n by n matrices Output: A permutation of size n Constraint: minimize

$$\sum_{i\neq j} C(i,j)/T(\boldsymbol{\sigma}_i,\boldsymbol{\sigma}_j)$$

#### C: communication matrix

Amount of data exchanged between process 1 and process 3

#### **Example of solutions:**

| Round-robin:     | 01234567 | 241.3  |

|------------------|----------|--------|

| Graph embedding: | 37406251 | 210.52 |

| Optimal (B&B):   | 04152637 | 29.08  |

## Complexity of the problem

Finding the optimal permutation is NP-Hard

However, posed this way the problem does not take into account the hierarchy of the topology

**Question**: does taking the hierarchy into consideration help?

# Taking into account the hierarchy

#### Topology matrix

| 0    | 100  | 100  | 10   | 1000 | 100  | 100  | 10   |

|------|------|------|------|------|------|------|------|

| 100  | 0    | 10   | 100  | 100  | 1000 | 10   | 100  |

| 100  | 10   | 0    | 100  | 100  | 10   | 1000 | 100  |

| 10   | 100  | 100  | 0    | 10   | 100  | 100  | 1000 |

| 1000 | 100  | 100  | 10   | 0    | 100  | 100  | 10   |

| 100  | 1000 | 10   | 100  | 100  | 0    | 10   | 100  |

| 100  | 10   | 1000 | 100  | 100  | 10   | 0    | 100  |

| 10   | 100  | 100  | 1000 | 10   | 100  | 100  | 0    |

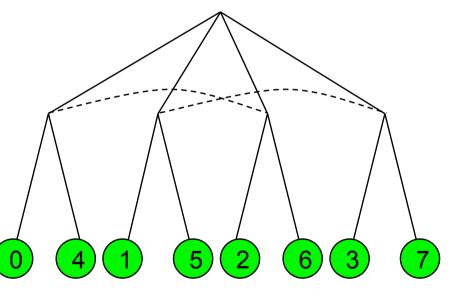

HWLOC output

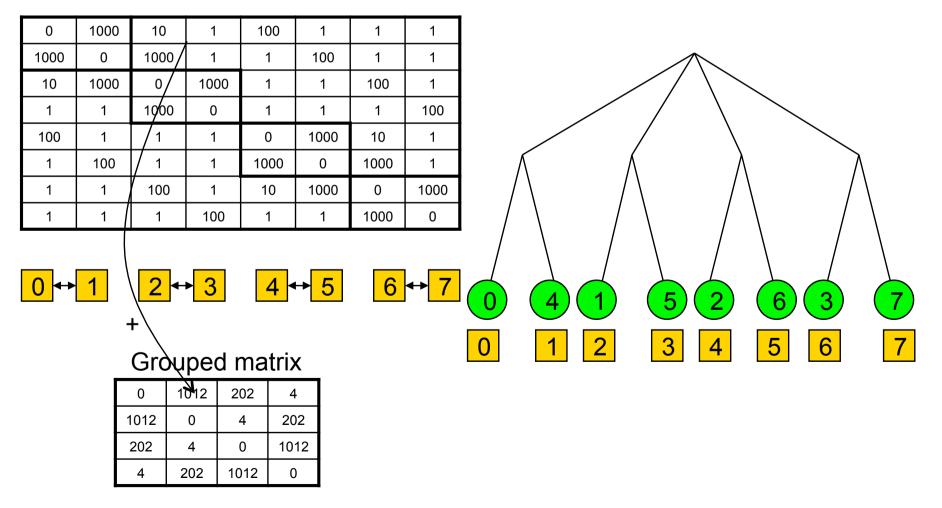

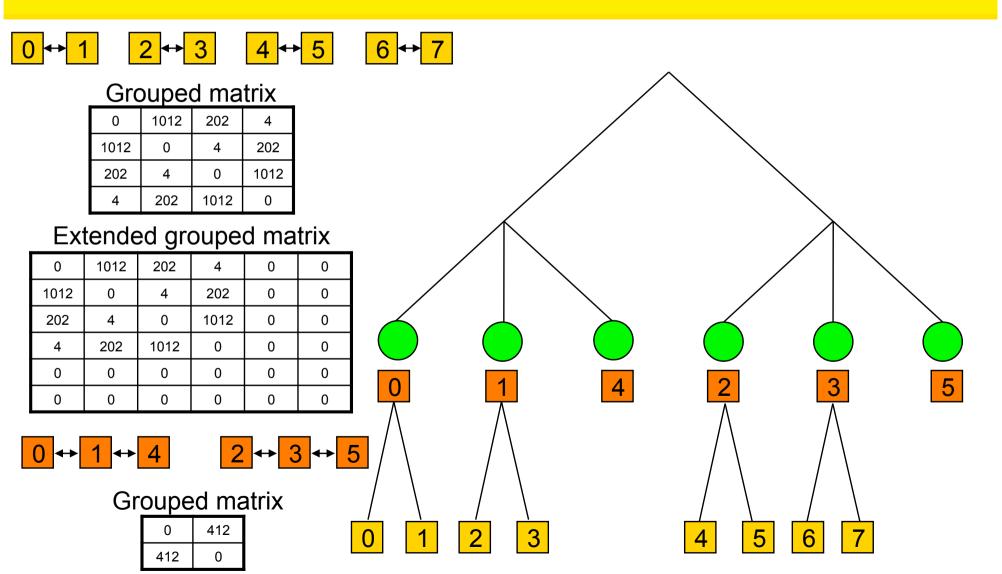

Mapping the communication matrix to the topology tree: the TreeMatch algorithm

Idea: for each level of the tree, group nodes to minimize remaining communication.

Group size should be equal to the arity of the considered level

#### Example

#### C: communication matrix

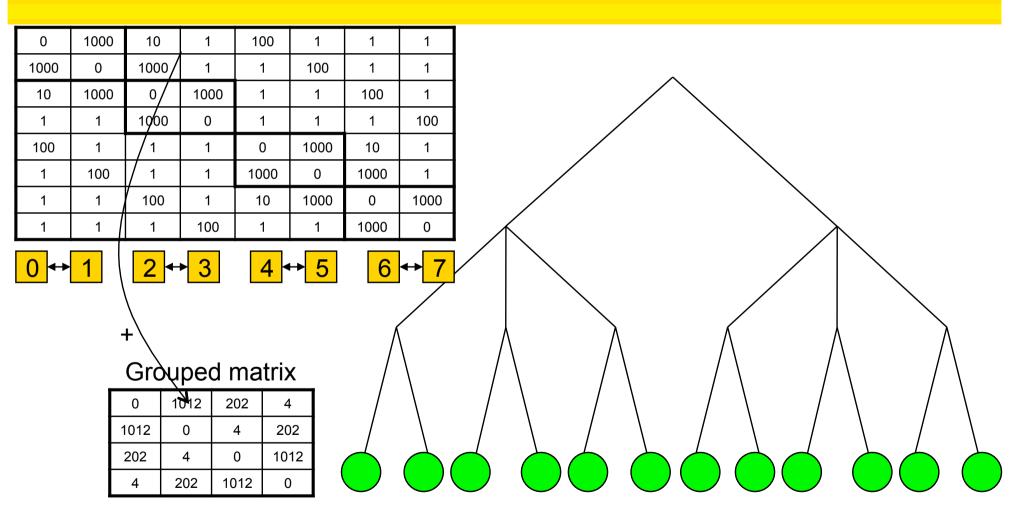

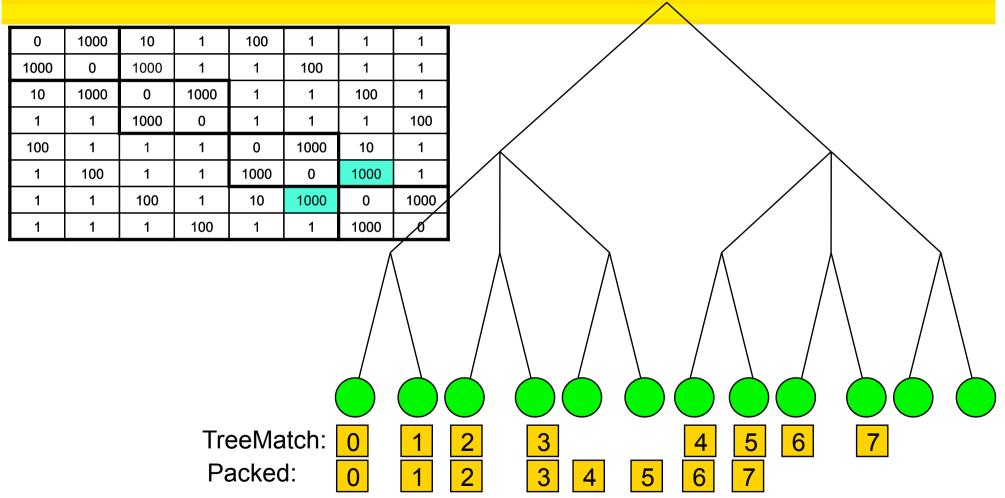

#### A more complex example

## A more complex example

#### A more complex example

Packed solution worst than the TreeMatch one because there is a large communication between processes 5 and 6

## **TreeMatch properties**

Work if there is more cores than processes (by adding virtual processes that do not communicate)

- . Work whatever the arity of a given level (do not need to be binary)

- Optimal if the communication pattern is hierarchic and symmetric and the topology tree is balanced

n: size of the matix, k: arity of the level n/k: size of the grouped matrix  $\binom{n}{k} \leq O(n^k)$  number of such groups

Ok if the arity of the tree is not too large.

We can manage a reasonable complexity in decomposing k in primes number: a vertex of arity 32 will be consider as a binary tree of 5 levels

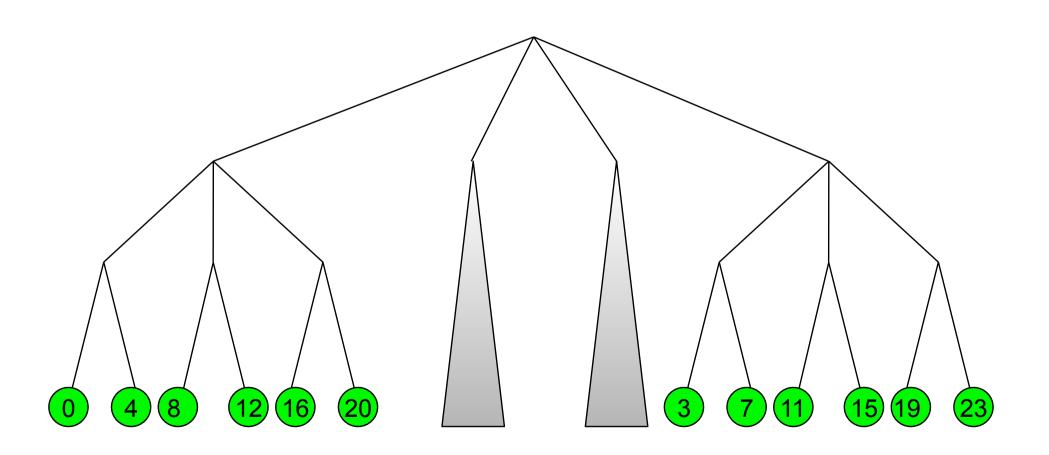

## Experiments

We use the NAS benchmarks:

- . All the kernels

- . Class: A,B,C,D

- . Size: 16, 32/36, 64

- On highly NUMA machine (4 nodes of 4 Xeon quad-core Dunnington)

- Comparison with : MPIPP [Chen et al. 2006] (two versions), Packed (by sub-tree), Round-Robin (process i to core i).

| Node#0(47GB)                                                           |                                                                               |                                                                         |                                                                         |  |  |  |  |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Socket#1                                                               | Socket#0                                                                      | Socket#2                                                                | Socket#3                                                                |  |  |  |  |

| L2(3072KB) L2(3072KB)   L1(32KB) L1(32KB)   L1(32KB) L1(32KB)          | L2(3072KB) L2(3072KB) L2(3072KB)   L1(32KB) L1(32KB) L1(32KB) L1(32KB)        | L2(3072KB) L2(3072KB)   L1(32KB) L1(32KB)   L1(32KB) L1(32KB)           | L2(3072KB) L2(3072KB)   L1(32KB) L1(32KB)   L1(32KB) L1(32KB)           |  |  |  |  |

| Core#0 Core#1 Core#2 Core#3 Core#4 Core#5   P#0 P#4 P#8 P#12 P#16 P#20 | Core#0 Core#1 Core#2 Core#3 Core#4 Core#5   P#1 P#5 P#9 P#13 Core#4 P#17 P#21 | Core#0 Core#1 Core#2 Core#3 Core#4 Core#5   P#2 P#6 P#10 P#14 P#18 P#22 | Core#0 Core#1 Core#2 Core#3 Core#4 Core#5   P#3 P#7 P#11 P#15 P#19 P#23 |  |  |  |  |

## 1of the 4 nodes of the target machine

## **Simulation Results**

#### 40.51 % (>) 63.29 % (>) 93.67 % (>) 94.94 % (>) 29.11 % (=) 16.46 % (=) 5.06 % (=) Median=1.113 Median=1.000 Median=1.016 TreeMatch Median=1.415 Avg=1.159 Avg=1.011 Avg=1.036 Avg=1.446 [0.960.1.800] [0.895,1.156] [0.960,1.432] [1.000,2.352] 75.95 % (>) 96.20 % (>) 96.20 % (>) 8.86 % (=) Median=1.102 Median=1.418 3.80 % (=) MPIPP.5 Median=1.015 Ava=1.146 Avg=1.025 Avg=1.423 [0.944, 1.800] [0.877,1.256] [1.000,2.069] 83.54 % (>) 93.67 % (>) 12.66 % (=) 5.06 % (=) Packed Median=1.062 Median=1.387 Avg=1.119 Avg=1.391 [1.000,2.064] [0.988.1.800] 73.42 % (>) Median=1.215 RR Avg=1.251 [0.788.1.830] լո ս MPIPP.1 0.5 1.0 1.5 0.5 1.0 1.5 0.5 1.0 1.5 0.5 1.0 1.5

Sim NAS ALL

#### We simulate the execution time using our model

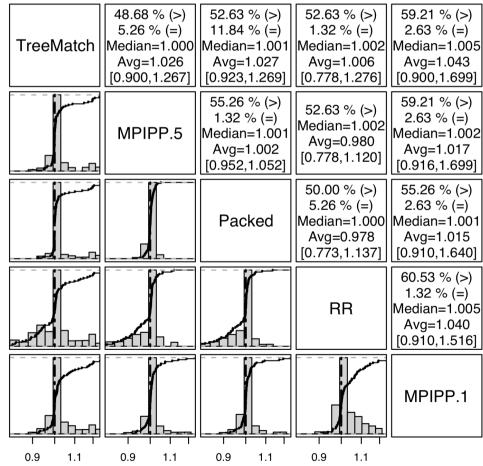

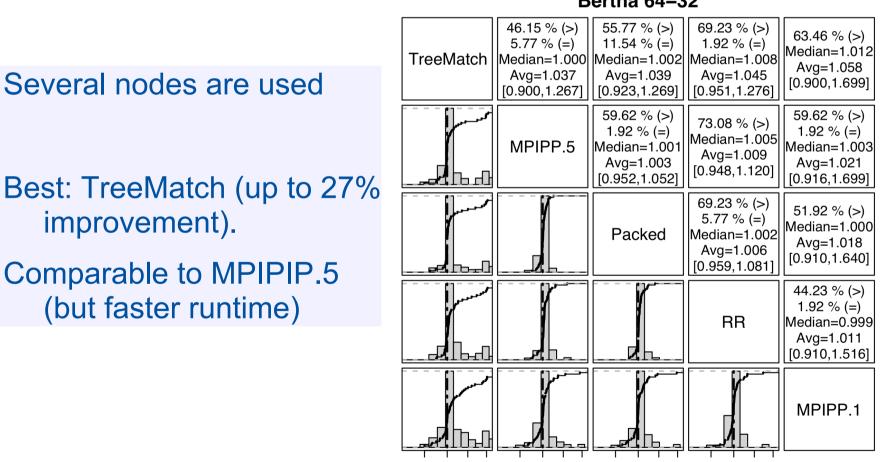

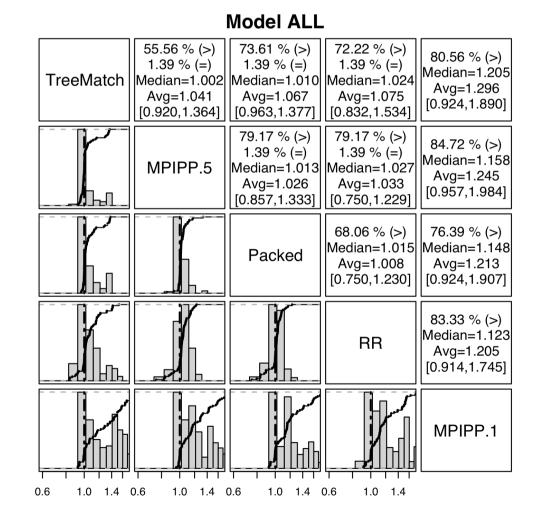

### NAS on the real machine

#### Best strategy: TreeMatch

#### Some very bad results against round-robin

#### **Bertha ALL**

#### 32-64 processes

0.9

1.1

0.9

1.1

0.9

1.1

0.9

1.1

Bertha 64-32

## Communication Only Application

#### We extract the communication pattern of the NAS

Up to 37% improvement

## Conclusion

Mapping processes can help to reduce the communication cost

#### TreeMatch: an algorithm to perform such mapping

- Bottom-up

- Fast

- Does not require that the number process equals the number of cores /processors

- Optimal in some cases

#### Early results:

- TreeMatch: best method on average

- Works well when more than one node is used

- Difference between model and reality

### Future work

On going work

#### Future work:

- Test real applications

- Top Down?

- Improve model (NUMA effect)

- Hybrid case

- Dymamic adaptation

- Automation

- Process topology interface of MPI 2.2 (With J. L. Träff).