# High Dynamic Performance Programmed PWM Control of a Multilevel Inverter with Capacitor DC Sources

John N. Chiasson, Zhong Du, Burak Özpineci, and Leon M. Tolbert

Abstract—A cascade multilevel inverter consisting of a standard 3-leg inverter supplied by a DC source and three full H-bridges each supplied by a capacitor is considered for use as a motor drive. The capacitor H-bridges can only supply reactive voltage to the motor while the standard three leg inverter can supply both reactive and active voltage. A switching control algorithm is presented that shows this inverter topology can be used as an AC drive achieving considerable performance advantages (e.g., higher motor speed) compared to using a standard 3-leg inverter while at the same time regulating the capacitor voltages. The converter controller is a fundamental frequency switching controller based on programmed PWM to achieve higher efficiency (less power losses in the switches) compared to high-frequency PWM approaches. As is well known, the programmed PWM switching times are computed assuming the drive is in sinusoidal steady-state, that is, the derived switching angles achieve the fundamental while rejecting specified harmonics if the voltage waveforms are in sinusoidal steady-state. Here it shown that the switching commands to the converter can be implemented in a smooth fashion for voltage waveform commands whose frequency and amplitudes are continuously varying.

Index Terms—Cascade Multilevel Inverter, Capacitor Sources, Reactive Voltage, Dynamic Programmed PWM

## I. INTRODUCTION

A cascade multilevel inverter (CMLI) is a power electronic device built to synthesize a desired AC voltage from several levels of DC voltages. Such inverters have been the subject of research in the last several years [1][2][3][4], where the DC levels were considered to be identical in that all of them were either batteries, solar cells, etc. In [5], a multilevel converter was presented in which the two separate DC sources were the secondaries of two transformers coupled to the utility AC power. Corzine et al [6] have proposed using a single DC power source and capacitors for the other DC sources. A method was given to transfer power from the DC power source to the capacitor in order to regulate the capacitor voltage. A similar approach was later (but independently)

J. Chiasson is with the ECE Department, Boise State University, Boise ID 83725, johnchiasson@boisestated.edu.

Z. Du is with the Parker Hannifin Corporation, 8225 Hacks Cross Rd, Olive Branch, MS 38654, zhong.du@parker.com

Burak Ozpineci is with The Oak Ridge National Laboratory, Knoxville, TN USA, burak@ieee.org.

Leon M. Tolbert is with the ECE Department, The University of Tennessee, Knoxville, TN USA 37996, tolbert@utk.edu

Prepared by the Oak Ridge National Laboratory, Oak Ridge, Tennessee 37831, managed by UT-Battelle for the U.S. Department of Energy under contract DE-AC05-00OR22725. The submitted manuscript has been authored by a contractor of the U.S. Government under Contract No. DE-AC05-00OR22725. Accordingly, the U.S. Government retains a nonexclusive, royalty-free license to publish from the contribution, or allow others to do so, for U.S. Government purposes.

proposed by Du et al [7]. Explicit conditions when the capacitor voltage can be regulated are given in terms of the modulation index and power factor angle in [8]. Other similar methods have also been proposed by Veenstar and Rufer [9][10][11].

Here a cascade multilevel inverter consisting of a standard 3-leg inverter supplied by a DC source and three full H-bridges each supplied by a capacitor is considered for use as an AC motor drive. The basic idea is that the capacitor H-bridges supply the reactive voltage required of the motor and the standard three leg inverter supplies the active voltage. A control algorithm is presented that shows this inverter topology can provide this capability while simultaneously keeping the capacitor voltage regulated.

In addition, a fundamental frequency switching controller based on programmed PWM is used to achieve higher efficiency (lower losses in the switches) compared to high-frequency (sine-triangle) PWM approaches. However, as is well known, the programmed PWM switching times/angles are computed assuming the drive is in sinusoidal steady-state, that is, the derived switching angles achieve the fundamental while rejecting specified harmonics assuming the voltage waveforms are in sinusoidal steady-state. We propose a method to *dynamically* implement the programmed PWM switching times/angles for smooth transitions under a varying (amplitude and frequency) voltage command.

#### II. CMLI ARCHITECTURE

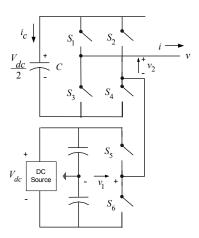

Figure 1 shows a DC source connected to a single leg of a standard 3-leg inverter and second DC source consisting of a capacitor.

Fig. 1. One leg of a 3-leg inverter connected to a full H-bridge with a capacitor DC source.

The output voltage  $v_1$  of this leg (with respect to the ground) is either  $+V_{dc}/2$  ( $S_5$  closed) or  $-V_{dc}/2$  ( $S_6$  closed). This leg is connected in series with a full H-bridge which is supplied by a capacitor. If the capacitor is kept charged to  $V_{dc}/2$ , then the output voltage of the H-bridge can take on the values  $+V_{dc}/2$  ( $S_1\&S_4$  closed), 0 ( $S_1\&S_2$  closed or  $S_3\&S_4$  closed), or  $-V_{dc}/2$  ( $S_2\&S_3$  closed). Due to this series connection in the topology of Fig. 1, we will use the current as the reference for active/reactive quantities rather than the voltage. The voltage out of the multilevel inverter that is in phase with the current will be referred to as the active voltage while the voltage 90° out of phase with the current will be referred to as the reactive voltage. The approach here is to have the H-bridge provide the reactive part of the voltage (the component 90° out of phase with the load current) so that the capacitor is not discharged. The standard three leg inverter then provides the active part of the voltage (the component in phase with the load current). As a consequence, this inverter provides a voltage boost to account for the reactive voltage required by the load.

## A. Reactive Voltage Control

We now present a method for providing the reactive voltage while regulating the capacitor voltage as proposed by one of the authors (B. Özpineci). Let  $i_{S1}, i_{S2}$ , and  $i_{S3}$  be the stator currents and define the space vector form [12] of the stator currents as

$$\underline{i}_S = i_{Sa} + ji_{Sb} \triangleq \sqrt{\frac{2}{3}} \left( i_{S1} + e^{j2\pi/3} i_{S2} + e^{j4\pi/3} i_{S3} \right). \tag{1}$$

Similarly, let  $v_{S1}, v_{S2}$ , and  $v_{S3}$  be the stator phase voltages and define the space vector form of the stator voltages as

$$\underline{v}_S = v_{Sa} + jv_{Sb} \triangleq \sqrt{\frac{2}{3}} \left( v_{S1} + e^{j2\pi/3} v_{S2} + e^{j4\pi/3} v_{S3} \right).$$

(2

We then decompose the voltage into its *active* and *reactive* components with respect to the stator current as

$$v_{S\_active} \triangleq \underline{v}_{S} \cdot \frac{\underline{i}_{S}}{|i_{S}|}$$

(3)

$$v_{S\_reactive} \triangleq \underline{v}_S \cdot \frac{j\underline{i}_S}{|\underline{i}_S|}$$

(4)

where "." denotes the vector dot product, i.e.,

$$\underline{v}_S \cdot \underline{i}_S \triangleq (v_{Sa} + jv_{Sb}) \cdot (i_{Sa} + ji_{Sb}) \triangleq v_{Sa} i_{Sa} + v_{Sb} i_{Sb}. \tag{5}$$

Note that we are making the identification  $v_{Sa} + jv_{Sb} \leftrightarrow [v_{Sa}, v_{Sb}]^T$  and  $i_{Sa} + ji_{Sb} \leftrightarrow [i_{Sa}, i_{Sb}]^T$  so that "·" is a vector operation and not complex multiplication. Further, we define  $j\underline{i}_S \triangleq j (i_{Sa} + ji_{Sb}) = -i_{Sb} + ji_{Sa} \leftrightarrow [-i_{Sb}, i_{Sa}]^T$ . With these definitions, we have

$$(\underline{i}_S) \cdot (j\underline{i}_S) \triangleq (i_{Sa} + ji_{Sb}) \cdot j (i_{Sa} + ji_{Sb})$$

$$= (i_{Sa} + ji_{Sb}) \cdot (-i_{Sb} + ji_{Sa})$$

$$= 0$$

$$|\underline{i}_S| = \sqrt{\underline{i}_S \cdot \underline{i}_S} = \sqrt{i_{Sa}^2 + i_{Sb}^2}.$$

The idea here is that  $\underline{i}_S/|\underline{i}_S|$  and  $\underline{j}\underline{i}_S/|\underline{i}_S|$  are two *orthogonal* vectors and are used as a new set of basis vectors (the original basis being  $[1,0]^T$  and  $[0,1]^T$ ). In (3) and (4) we projected the voltage vector  $\underline{v}_S$  onto these two vectors to obtain the components of the voltage vector with respect to this new basis, that is, a component in phase with the current and a component 90 degrees out of phase with the current. We can then rewrite the voltage vector  $\underline{v}_S$  with respect to this new basis as

$$\underline{v}_{S\_active} \triangleq v_{S\_active} \frac{\underline{i}_S}{|\underline{i}_S|}$$

(6)

$$\underline{v}_{S\_reactive} \triangleq v_{S\_reactive} \frac{j\underline{i}_S}{|\underline{i}_S|}.$$

(7)

Then

$$\underline{v}_S = \underline{v}_{S~active} + \underline{v}_{S~reactive}$$

where  $\underline{v}_{S\_active}$  is a vector parallel to  $\underline{i}_S$  and  $\underline{v}_{S\_reactive}$  is a vector perpendicular to  $\underline{i}_S$ . As a consequence, over a cycle of period T we have

$$\int_{T} \underline{v}_{S} \cdot \underline{i}_{S} dt = \int_{T} \underline{v}_{S\_active} \cdot \underline{i}_{S} dt + \int_{T} \underline{v}_{S\_reactive} \cdot \underline{i}_{S} dt

= \int_{T} \underline{v}_{S\_active} \cdot \underline{i}_{S} dt$$

(8)

as  $\underline{v}_{S\_reactive} \cdot \underline{i}_S = 0$ . Using the two-phase to three-phase transformation, the command voltages to the three leg inverter (with the DC source) are then

$$v_{S1active} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_active} \right)$$

$$v_{S2active} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_active} e^{-j2\pi/3} \right)$$

$$v_{S3active} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_active} e^{-j4\pi/3} \right).$$

while the command voltages to the H-bridge (with the capacitor sources) are

$$\begin{array}{lcl} v_{S1reactive} & = & \sqrt{\frac{2}{3}}\operatorname{Re}\left(\underline{v}_{S\_reactive}\right) \\ \\ v_{S2reactive} & = & \sqrt{\frac{2}{3}}\operatorname{Re}\left(\underline{v}_{S\_reactive}e^{-j2\pi/3}\right) \\ \\ v_{S3reactive} & = & \sqrt{\frac{2}{3}}\operatorname{Re}\left(\underline{v}_{S\_reactive}e^{-j4\pi/3}\right). \end{array}$$

If there were no losses, the capacitors would keep their voltage level as they are only supplying reactive voltage. However, there are invariably going to be losses and so a control loop is required to regulate the capacitor voltages. To do so, we modify the command voltages to the H-bridges. Let  $V_c$  be the desired value of the capacitor voltage and  $v_c$  be its measured value. The command voltage to the first H-bridge is modified to be

$$v_{S1reactive} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_reactive} \right) - K_{cap} \left( V_c - v_{c1} \right) v_{S1active}. \tag{9}$$

Here  $K_{cap} > 0$  is the controller gain for regulating the capacitor voltage level. Note that over one period T of a cycle the energy *out* of the capacitor is given by

$$\int_{T} v_{S1reactive} i_{S1} dt = \sqrt{\frac{2}{3}} \int_{T} \operatorname{Re}(\underline{v}_{S\_reactive}) i_{S1} dt

-K_{cap}(V_{c} - v_{c1}) \int_{T} v_{S1active} i_{S1} dt

= -K_{cap}(V_{c} - v_{c1}) \int_{T} v_{S1active} i_{S1} dt$$

(10)

where it was assumed that  $V_c - v_{c1}$  does not vary significantly over a single period. If  $v_{c1} < V_c$ , then the capacitor needs charging and energy must be supplied to the capacitor, i.e., the energy out of the capacitor must be negative. Equation (10) shows that the controller does indeed do this because  $v_{S1active}$  and  $i_{S1}$  have the same sign (they are in phase) so that  $\int_T v_{S1active}i_{S1}dt > 0$  and therefore

$$\int_{T} v_{S1reactive} i_{S1} dt = -K_{cap} \left( V_{c} - v_{c1} \right) \int_{T} v_{S1active} i_{S1} dt$$

$$< 0. \tag{11}$$

That is, energy is being supplied to the capacitor of phase 1 to recharge it. Similarly, if  $v_{c1} > V_c$ , the controller will discharge the capacitor.

In summary, the voltage commands to the H-bridges are

$$v_{S1reactive} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_reactive} \right)$$

$$-K_{cap} \left( V_c - v_{c1} \right) v_{S1active}$$

$$v_{S2reactive} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_reactive} e^{-j2\pi/3} \right)$$

$$-K_{cap} \left( V_c - v_{c2} \right) v_{S2active}$$

$$v_{S3reactive} = \sqrt{\frac{2}{3}} \operatorname{Re} \left( \underline{v}_{S\_reactive} e^{-j4\pi/3} \right)$$

$$-K_{cap} \left( V_c - v_{c3} \right) v_{S3active}.$$

## B. Simulations

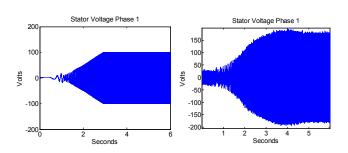

The controller is set up so that the H-bridge with capacitor sources supply reactive voltage and each leg of the three leg inverter supplies only active voltage. A PM synchronous machine was chosen as they often require significant reactive voltage. The DC link voltage  $V_{dc}$  was set to 250 V yet the overall voltage used is less than 200 V as shown in Fig. 3. Consequently, the supply for the three leg standard inverter is 100 V and the capacitors for the H-bridge are charged and regulated to  $V_{dc}/2 = 125 V$ . With respect to the reactive voltage, the CMLI is thus providing a boost of 2.5 times that of a standard three leg inverter. The motor's parameter values are an inertia of J=0.1 kg-m<sup>2</sup>,  $n_p=4$  pole-pairs, stator resistance is  $R_S = 0.065$  Ohms, stator inductance is  $L_S = 3$  mH, torque/back-emf constant  $K_T = K_b = 0.37$ Nm/A (V/rad/s) and a load torque of  $\tau_L=19$  Nm. The H-bridge capacitor value is C = 0.01 F.

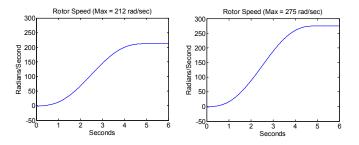

For comparison purposes, simulations were performed using both the multilevel inverter of Fig. 1 and a standard

3-leg inverter (i.e., only the bottom half of Fig. 1). Though the multilevel inverter can supply up to  $\pm (V_{dc} + V_{dc}/2)) = \pm 250\,$  V, it can do this and maintain regulation of the capacitor voltages only if 150 V of the 250 V is reactive voltage.

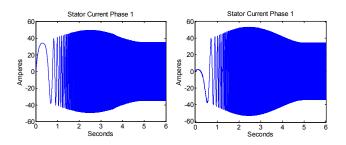

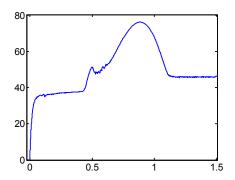

The PM motor was run to achieve the highest possible speed under the given load and available voltage. This is shown in Fig. 2. The standard 3-leg inverter could only achieve a maximum speed of 212 rad/s while the proposed multilevel inverter could get the motor up to 275 rad/s using the same DC source voltage.

Fig. 2. Rotor speeds achievable using a standard 3-leg inverter (left) and the proposed multilevel inverter (right).

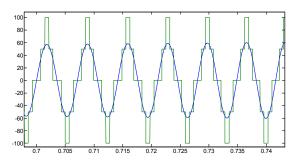

The corresponding voltages for the speed trajectories of Fig. 2 are shown in Fig. 3. The peak voltage of the standard 3-leg inverter is nearly a six step wave form with  $V_{dc}/2=100~V$  corresponding to a fundamental voltage of  $(4/\pi)V_{dc}/2=127~V$  peak while the multilevel inverter is supplying up to 165~V peak.

Fig. 3. Left: Voltage using a standard 3-leg inverter. Right: Voltage obtained using the proposed multilevel inverter.

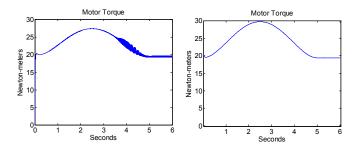

The corresponding torques for the above trajectories are shown in Fig. 4. The chattering shown in the torque response of the standard 3-leg inverter is due to the fact its link voltage is limited to 100 V and the controller is asking for more than 100 V on the output (see the left-side of Fig. 3). The torque produced is greater in the case of the multilevel inverter as the motor is being accelerated to a higher speed in the same amount of time.

Fig. 4. Left: Motor torque using standard 3-leg inverter. Right: Motor torque using proposed multilevel inverter.

The stator currents are shown in Fig. 5.

Fig. 5. Left:  $i_{S1}$  for a standard 3-leg inverter. Right:  $i_{S1}$  for the proposed multilevel inverter.

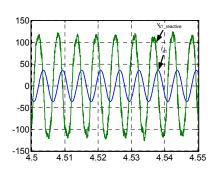

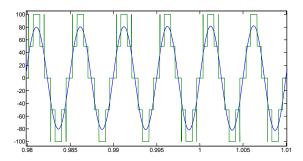

The stator current and the reactive component of the stator voltage (the output of the H-bridge) are plotted in Fig. 6 showing that they are  $90^{\circ}$  out of phase. (Both signals were put through a low pass filter with a cutoff of 5 kHz.).

Fig. 6. Stator current  $i_{S1}$  (A) and the reactive component  $v_{S1\_reactive}$  (V) vs. time (s).

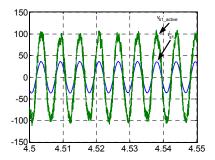

Fig. 7 is a plot of the stator current and the active component of the voltage (output of the three leg inverter) showing that they are in phase. (Both signals were put through a low pass filter with a cutoff of 5 kHz.)

Fig. 7. Stator current  $i_{S1}$  (A) and the active component  $v_{S1\_active}$  (V) vs. time (s).

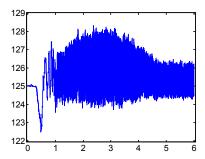

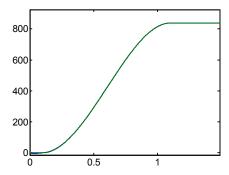

The capacitor voltage as a function of time is plotted in Fig. 8 showing that it is kept within about 2 volts of the desired value.

Fig. 8. Capacitor voltage (V) versus time (s).

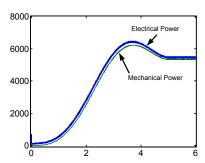

The electrical power  $v_{S1}i_{S1}+v_{S2}i_{S2}+v_{S3}i_{S3}$  and the mechanical power  $\tau\omega$  are shown in Fig. 9.

Fig. 9. Electrical and mechanical power (W) vs. time (s).

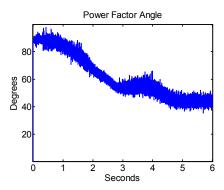

The power factor angle  $\phi$  is defined by

$$\phi \triangleq \cos^{-1} \left( \frac{v_{S1}i_{S1} + v_{S2}i_{S2} + v_{S3}i_{S3}}{3V_S I_S} \right)$$

$$V_S = |\underline{v}_S|$$

$$I_S = |\underline{i}_S|$$

with  $\underline{i}_S, \underline{v}_S$  given by equations (1) and (2), respectively.  $\phi$  is plotted in Fig. 10. Note that the machine operates with

a rather large power factor angle so that the drive requires significant reactive voltage making the choice of a capacitor fed H-bridge CMLI attractive.

Fig. 10. Power factor angle  $\phi$  vs time.

#### III. DYNAMIC PROGRAMMED PWM

Programmed PWM techniques have been proposed for over 30 years for choosing the switching angles in an inverter to provide a specified fundamental voltage and eliminate various higher-order harmonics. If the switching losses in an inverter are not a concern (i.e., switching on the order of a few kHz is acceptable), then the sine-triangle PWM method and its variants are very effective for controlling the inverter [13]. On the other hand, for systems where high switching efficiency (low power loss) is of importance, it is desirable to keep the switching frequency much lower. In this case, another approach is to choose a finite number of switching times  $t_i$  per period T (with a corresponding finite number of switching angles  $\theta_i = (t_i/T) 2\pi$ ) such that a desired fundamental output is generated and specifically chosen harmonics of the fundamental are suppressed [13][14][15][16][17]. This is referred to as harmonic elimination or programmed PWM as the switching angles  $\theta_i$  are chosen (programmed) to eliminate specific harmonics. However, these methods assume the drive is in sinusoidal steady-state, that is, the derived switching angles achieve the fundamental while rejecting specified harmonics if the voltage waveforms are in sinusoidal steady-state. In an application such as a motor drive, it is typically the case that the frequency and amplitude of the voltage waveform is changing in response to the changing speed of the motor, that is, *dynamic* performance is required. As pointed out by Holtz and Beyer [18][19], applications of programmed PWM techniques are few because of their low dynamic performance.

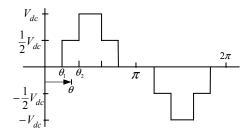

A new approach which achieves high dynamic performance programmed PWM has been proposed by one of the authors (Z. Du) and is now discussed. To fix ideas, consider again the five-level inverter shown in Fig. 1. A fundamental switching scheme for the output waveform is shown in Fig. 11 where  $\theta_1$  and  $\theta_2$  are the switching angles relative the fundamental period.

Fig. 11. Output waveform of a five-level cascade multilevel inverter.

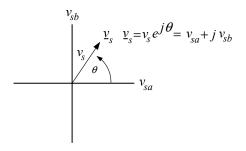

As in the previous section,  $\underline{v}_S = v_{Sa} + jv_{Sb} \triangleq \sqrt{2/3} \left(v_{S1} + e^{j2\pi/3}v_{S2} + e^{j4\pi/3}v_{S3}\right)$ . We rewrite this space vector in polar coordinate form as  $\underline{v}_S = v_S e^{j\theta}$  where  $v_S \triangleq \sqrt{v_{Sa}^2 + v_{Sb}^2}$  and  $\theta \triangleq \tan^{-1}\left(v_{Sb}/v_{Sa}\right)$  (see Fig. 12).

Fig. 12. Space vector form of the commanded stator voltages.

The switching angles  $\theta_1$  and  $\theta_2$  of Fig. 11 are determined solely by the modulation index  $m \triangleq \frac{4}{\pi} \frac{v_S}{s(V_{dc}/2)}$  where  $V_{dc}$  is the link voltage and s=2 is the number of DC sources [20]. That is, the output waveform is completely determined by the modulation index and, in particular, does not depend on the specific value of the period T of the fundamental waveform.

The (instantaneous) angle  $\theta$  of the commanded stator voltage is computed modulo  $2\pi$  determining its position in the interval  $[0, 2\pi]$  and thus according to Fig. 11 the corresponding switch positions are determined. We remark that for a significant range of the modulation index, the angles  $\theta_1$  and  $\theta_2$  of the waveform of Fig. 11 can be chosen to achieve a given fundamental voltage and no fifth harmonic [21][20] (see the Appendix).

# **Dynamic Programmed PWM Algorithm**

- 1) Compute the voltage command  $\underline{v}_S$  to the inverter (e.g., a field-oriented controller based on measured stator currents, speed and/or position).

- 2) Compute the magnitude  $v_S \triangleq \sqrt{v_{Sa}^2 + v_{Sb}^2}$  and phase  $\theta \triangleq \tan^{-1}(v_{Sb}/v_{Sa})$  of the command voltage. These will typically be noisy because, for example, a field-oriented controller uses noisy measurements of the currents.

- 3) Put the voltage magnitude through a low pass filter to eliminate some of the noise.

- 4) Put the filtered magnitude through a lookup table containing the preprogrammed PWM switching patterns to

- obtain the switching angles. (It typically will not help to filter the phase because it changes too rapidly and any filter that removes the noise will invariably cause too much of a delay in the phase).

- 5) Check the value of the computed phase angle  $\theta$  against the switching angles to determine the value of the inverter output voltage (and therefore switch positions).

## A. Simulations with Dynamic Programmed PWM

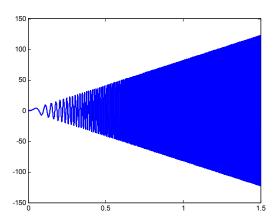

As an illustration of the approach, command voltages to the inverter were ramped up in magnitude and frequency. Specifically, the phase 1 voltage is given by  $v_{S1}(t) = V_S \sin(\omega_S t)$  with  $\omega_S(t) = 2\pi(100)t$  and  $V_S(t) = 100t$  and is plotted in Fig. 13.

Fig. 13.  $v_{S1}(t) = V_S \sin(\omega_S t)$ ,  $\omega_S(t) = 2\pi (100)t$  and  $V_S(t) = 100t$ .

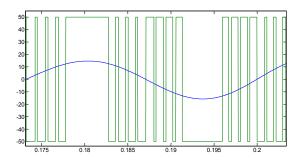

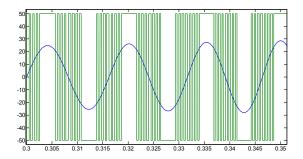

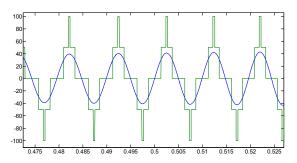

The inverter simulated is a five level multilevel inverter with a DC link of  $V_{dc}=100$  V. For  $V_S\leq 38$  (modulation index of 0.484) the capacitor DC sources are not needed so a bipolar scheme was used with the 3-leg inverter while for higher voltage amplitudes the fundamental switching scheme of Fig. 11 was used. Figures 14, 15, 16, 17, and 18 are enlarged views of Fig. 13 along with the inverter output voltage computed from the commanded voltage at t=0.2,0.35,0.5,0.75 and 1.0, respectively. These sequence of figures demonstrate the smooth transition of CMLI output waveform as the frequency is increased.

Fig. 14. Bipolar scheme where  $V_S=20~\mathrm{V}$  and  $\omega_S=25~\mathrm{rad/s}$ .

Fig. 15. Bipolar switching with  $V_S=35~{\rm V}$  and  $\omega_S=77~{\rm rad/s}$ .

Fig. 16. Fundamental switching with  $V_S = 55$  V and  $\omega_S = 155$  rad/s.

Fig. 17. Fundamental switching with  $V_S = 75$  V and  $\omega_S = 350$  rad/s.

Fig. 18. Fundamental switching with  $V_S = 100$  V and  $\omega_S = 635$  rad/s.

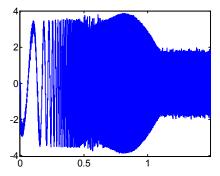

#### B. Field-Oriented Control with Dynamic Programmed PWM

We now use a dynamic programmed PWM algorithm to drive an induction motor. The induction motor parameters are M=0.011 H,  $R_R=3.9$  Ohms,  $R_S=1.7$  Ohms,  $L_R=0.014$  H,  $L_S=0.014$  H, J=0.00011 kgm²,  $n_p=3$  pole-pairs and  $V_{dc}=100$  V. The motor was brought up from zero speed to 838 rad/s (400 Hz) as shown in Fig. 19. The corresponding current in stator phase 1 is shown in Fig. 20.

A field-oriented controller was used to have the motor provide the tracking shown in Fig. 19. The output of the field oriented controller is the stator voltage and its magnitude  $|v_S|$  for the above trajectory is shown in Fig. 21 (the corresponding modulation index is easily calculated).

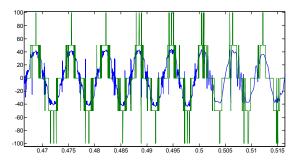

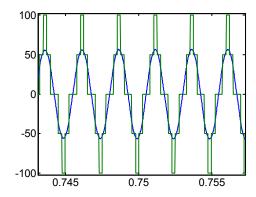

Figure 22 is a plot of the command voltage from the controller and the inverter output voltage with a voltage magnitude  $v_S=52$  V and a frequency  $\omega_S=945$  rad/s (150 Hz), and is implemented using a five-level multilevel switching scheme. Figure 23 shows a plot of the command voltage from the controller and the inverter output voltage with voltage magnitude  $v_S=67$  V and frequency  $\omega_S=2513$  rad/s (400 Hz), and is implemented using a five-level multilevel switching scheme.

Fig. 19.  $\omega$  and  $\omega_{ref}$  (rad/s) versus time (s).

Fig. 20. Stator current  $i_{S1}$  (A) versus time (s).

Fig. 21.  $|v_S|$  (V) versus time (sec).

Fig. 22. Commanded and inverter output voltage (V) with  $V_S=52$  V and  $\omega_S=945$  rad/s (150 Hz).

Fig. 23. Commanded and inverter output voltage (V) with  $V_S=67~{\rm V}$  and  $\omega_S=2513~{\rm rad/s}$  (400 Hz).

## IV. CONCLUSIONS

A five-level cascade multilevel inverter topology has been proposed that requires only a single standard 3-leg inverter and capacitors as the power sources. An algorithm was presented that could simultaneously regulate the (capacitor sourced) voltage of the H-bridges and produce the requisite reactive voltage required by the AC machine. Simulations showed that the multilevel PM drive can attain significantly higher speeds compared to the standard three leg inverter

simply because the capacitor sourced H-bridges provide the reactive voltage required by the load.

Additionally, a method to dynamically implement programmed PWM switching patterns was presented and was shown to smoothly set the switching angles while the voltage command varied in frequency.

## V. APPENDIX

The Fourier series expansion of the (stepped) output voltage waveform of the multilevel inverter as shown in Figure 11 is

$$V(\omega t) = \sum_{n=1,3,5,\dots}^{\infty} \frac{4V_{dc}}{n\pi} \left( \cos(n\theta_1) + \cos(n\theta_2) \right) \sin(n\omega t)$$

(12)

Given a desired fundamental voltage  $V_1$ , the goal here is to determine the switching angles  $\theta_1, \theta_2$  so as to make the first harmonic equal to the desired fundamental voltage  $V_1$  and the  $5^{th}$  order harmonic zero. (As the application of interest here is a three-phase motor drive, the triplen harmonics in each phase need not be canceled as they automatically cancel in the line-to-line voltages.) The mathematical statement of these conditions is

$$\frac{4V_{dc}}{\pi} \left( \cos(\theta_1) + \cos(\theta_2) \right) = V_1$$

$$\cos(5\theta_1) + \cos(5\theta_2) = 0.$$

(13)

This is a system of two transcendental equations in the two unknowns  $\theta_1, \theta_2$ . To solve these equations, let  $x_1 = \cos(\theta_1)$  and  $x_2 = \cos(\theta_2)$  and use the trigonometric identity  $\cos(5\theta) = 5\cos(\theta) - 20\cos^3(\theta) + 16\cos^5(\theta)$  so that the conditions (13) become

$$p_1(x_1, x_2) \triangleq x_1 + x_2 - m = 0$$

$$p_2(x_1, x_2) \triangleq 5x_1 - 20x_1^3 + 16x_1^5 + 5x_2 - 20x_2^3 + 16x_2^5$$

= 0

where  $x=(x_1,x_2)$  and  $m\triangleq V_1/(4V_{dc}/\pi)$ . This is a set of two equations in the two unknowns  $x_1,x_2$ . Further, the solutions must satisfy  $0\leq x_2< x_1\leq 1$ . To solve this set one simply solves

$$p_2(x_1, m - x_1) = 0$$

for all roots  $x_{1i}$  satisfying  $0 < x_{1i} \le 1$ . For each such root  $x_{1i}$ , the corresponding root  $x_{2i} = m - x_{1i}$  keeping only those solution pairs  $(x_{1i}, x_{2i})$  that also satisfy  $0 \le x_{2i} < x_{1i} \le 1$ . The corresponding angles are  $\theta_1 = \cos^{-1}(x_1), \theta_2 = \cos^{-1}(x_2)$  where the  $\cos^{-1}$  is restricted to the angle in the first quadrant. (This approach to solving the harmonic elimination equations is generalized in [20][21].)

## REFERENCES

M. Klabunde, Y. Zhao, and T. A. Lipo, "Current control of a 3 level rectifier/inverter drive system," in *Conference Record 1994 IEEE IAS Annual Meeting*, pp. 2348–2356, 1994.

- [2] W. Menzies, P. Steimer, and J. K. Steinke, "Five-level GTO inverters for large induction motor drives," *IEEE Transactions on Industry Applications*, vol. 30, pp. 938–944, July 1994.

- [3] J. K. Steinke, "Control strategy for a three phase AC traction drive with three level GTO PWM inverter," in *IEEE Power Electronic Specialist Conference (PESC)*, pp. 431–438, 1988.

- [4] J. Zhang, "High performance control of a three level IGBT inverter fed AC drive," in *Conf. Rec. IEEE IAS Annual Meeting*, pp. 22–28, 1995

- [5] M. Manjrekar, P. K. Steimer, and T. Lipo, "Hybrid multilevel power conversion system: A competitive solution for high-power applications," *IEEE Transactions on Industry Applications*, vol. 36, pp. 834– 841, May/June 2000.

- [6] K. A. Corzine, F. A. Hardrick, and Y. L. Familiant, "A cascaded multi-level H-bridge inverter utilizing capacitor voltages sources," in *Proceedings of the IASTED International Conference*, pp. 290–295, Palm Springs CA, 2003.

- [7] Z. Du, L. M. Tolbert, J. N. Chiasson, and B. Özpineci, "Cascade multilevel inverter using a single dc source," in *Proceedings of the Applied Power Electronics Conference (APEC)*, pp. 426–430, 2006. Dallas TX.

- [8] J. Chiasson, B. Ozpineci, Z. Du, and L. Tolbert, "Condition for capacitor voltage regulation in a five level cascade multilevel inverter: Application to voltage boost in a pm drive," in *Proceedings of the International Conference on Electric Machines*, May 2007. Antayla Turkey.

- [9] M. Veenstra and A. Rufer, "Non-equilibrium state capacitor voltage stabilization in a hybrid asymmetric nine-level inverter: Non-linear model-predictive control," in *Proceedings of the European Control* Conference, 2003. Toulouse FR.

- [10] M. Veenstra and A. Rufer, "Control of a hybrid asymmetric multilevel inverter for a competitive medium-voltage industrial drives," *IEEE Transactions on Industry Applications*, vol. IAS-41, pp. 655–664, March/April 2005.

- [11] J. Liao, K. Corzine, and M. Ferdowsi, "A new control method for single-dcsource cascaded h-bridge multilevel converters using phaseshift modulation," in *Proceedings of the IEEE Applied Power Elec*tronics Conference and Exposition, vol. 52, pp. 886–890, Feb 2008.

- [12] J. Chiasson, Modeling and High-Performance Control of Electric Machines. John Wiley & Sons, 2005.

- [13] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Converters, Applications, and Design, Third Edition*. John Wiley and Sons, 2003.

- [14] P. N. Enjeti, P. D. Ziogas, and J. F. Lindsay, "Programmed PWM techniques to eliminate harmonics: A critical evaluation," *IEEE Trans*actions Industry Applications, vol. 26, pp. 302–316, March/April 1990.

- [15] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thryristor inverters: Part I - harmonic elimination," *IEEE Transactions on Industry Applications*, vol. 9, pp. 310–317, May/June 1973.

- [16] H. S. Patel and R. G. Hoft, "Generalized harmonic elimination and voltage control in thryristor inverters: Part II - voltage control technique," *IEEE Transactions on Industry Applications*, vol. 10, pp. 666– 673, September/October 1974.

- [17] J. Sun and I. Grotstollen, "Pulsewidth modulation based on real-time solution of algebraic harmonic elimination equations," in *Proceedings* of the 20th International Conference on Industrial Electronics, Control and Instrumentation IECON, vol. 1, pp. 79–84, 1994.

- [18] J. Holtz and B. Beyer, "Optimal synchronous pulse width modulation with a trajectory tracking scheme for high dynamic performance," in *Proceedings of the Applied Power Electronics Conference APEC*, pp. 147–154, 1992. Boston MA.

- [19] J. Holtz and B. Beyer, "The optimal trajectory tracking approach a new method for minimum distortation pwm in dynamic high-power drives," in *Conference Record of the Industry Applicatons Society Annual Meeting*, 1992. Houston TX.

- [20] J. Chiasson, L. Tolbert, K. McKenzie, and Z. Du, "Elimination of harmonics in a multilevel converter using the theory of symmetric polynomials," *IEEE Transactions on Control Systems Technology*, vol. 13, pp. 216–223, March 2005.

- [21] J. Chiasson, L. M. Tolbert, K. McKenzie, and Z. Du, "Control of a multilevel converter using resultant theory," *IEEE Transactions on Control System Technology*, vol. 11, pp. 345–354, May 2003.