# SiC-BASED POWER CONVERTERS

Leon M. Tolbert<sup>1,2</sup>, Hui Zhang<sup>1</sup>, Burak Ozpineci<sup>2</sup>, Madhu S. Chinthavali<sup>2</sup>

### **ABSTRACT**

The advantages that silicon carbide (SiC) based power electronic devices offer are being realized by using prototype or experimental devices in many different power applications ranging from medium voltage to high voltage or for high temperature or high switching frequency applications. The main advantages of using SiC-based devices are reduced thermal management requirements and smaller passive components which result in higher power density. An overview of the SiC research effort at Oak Ridge National Laboratory (ORNL) and The University of Tennessee (UT) is presented in this paper.

### INTRODUCTION

Silicon carbide power electronic devices are expected to have better characteristics than their silicon counterparts once processing and packaging issues have been solved. SiC devices have higher blocking voltages, lower on-state resistance and switching losses, and higher thermal conductivity and operating temperatures. Use of these devices will impact several application areas including hybrid electric vehicles, electric grid interface with distributed energy sources, and high temperature environments.

In pursuit of mass production of hybrid electric vehicles, the automotive research industry has set goals such as reducing the size and weight of the power electronics and cooling systems and increasing their efficiency. The U.S. Department of Energy's research goals for the year 2020 include hybrid electric vehicle inverters that have power densities of more than 14.1 kW/kg and 13.4 kW/L, and efficiencies greater than 98 % at a cost less than \$3.3/kW.

SiC devices are capable of operating at higher voltages, higher frequencies, and higher junction temperatures than comparable Si devices, which result in significant reduction in weight and size of the power converter and an increase in system efficiency. The objectives of research efforts on SiC based device applications at ORNL and UT are

- Assessing the impact of replacing silicon (Si) power devices in transportation applications such as hybrid electric vehicles (HEVs) or plug-in hybrid electric vehicles (PHEVs) with wide-bandgap (WBG) semiconductors, especially silicon carbide (SiC). Researchers have also examined what impact high voltage SiC devices would have in power electronics for electric utility applications.

- Developing temperature-dependent device and power converter models for various system simulation studies and analyzing the impact of SiC devices on the system performance.

- Building SiC-based prototype converters to validate the performance of SiC devices.

- Building high temperature packages and gate drives for SiC power devices to operate at 200°C ambient.

<sup>&</sup>lt;sup>1</sup>Electrical Engineering and Computer Science, The University of Tennessee, Knoxville, TN 37996-2100

<sup>&</sup>lt;sup>2</sup>Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory, Knoxville, TN 37932

### DEVICE CHARACTERIZATION AND MODELING

The static and dynamic characteristics of SiC Schottky diodes and JFETs are obtained experimentally. The experimental data are analyzed to extract device parameters to develop behavioral models. The behavioral models are integrated into system level models to study their impact on the overall system performance. The models of SiC Schottky diodes are briefly summarized below. For more information, see [1-4].

# **SiC Schottky Diode Models**

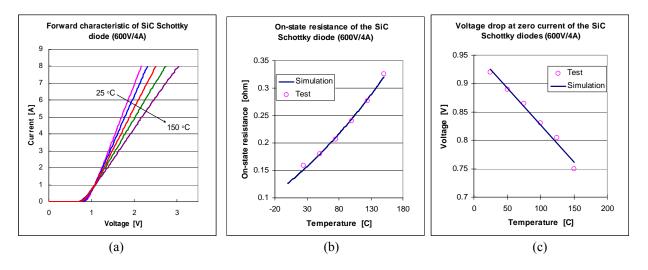

Static characteristics: The forward characteristics of a 600 V, 4 A SiC Schottky diode obtained at different temperatures from 25 °C to 150 °C temperature are shown in Fig. 1(a). It can be approximated with the following equation [4]:

$$V_d = V_D + R_D \cdot I_d \tag{1}$$

where  $V_d$  and  $I_d$  are the diode forward voltage and current,  $V_D$  is the voltage drop at zero current, and  $R_D$  is the on-state resistance, which is modeled using equations (2)-(7).

$$R_D = \frac{4V_B^2}{\varepsilon E_c^3 \mu_n} \tag{2}$$

$$\mu(E) = \frac{\mu_0}{\left\{1 + \left|\frac{\mu_0 E}{v_s}\right|^{\beta}\right\}^{1/\beta}}$$

(3)

$$\mu_0 = \mu_{\min} + \frac{\mu_{\max} - \mu_{\min}}{1 + \left(N_{tot}/N_{ref}\right)^{\alpha}}$$

(4)

$$\mu_{\text{max}} = A_{\mu_{\text{max}}} \times \left(\frac{T}{300}\right)^{-B_{\mu_{\text{max}}}} \tag{5}$$

$$\mu_{\min} = A_{\mu_{\min}} \times \left(\frac{T}{300}\right)^{-B_{\mu_{\min}}} \tag{6}$$

$$N_{ref} = A_{N_{ref}} \times \left(\frac{T}{300}\right)^{-B_{N_{ref}}} \tag{7}$$

Table 1. Parameters used in the device models [5-6]

| Table 1. Parameters used in the device models [5-6] |                       |

|-----------------------------------------------------|-----------------------|

| Property                                            | 4H-SiC                |

| Breakdown electric field, $E_c$ (kV/cm)             | 2200                  |

| Relative dielectric constant, $\varepsilon_r$       | 10.1                  |

| Doping coefficient of $\mu$ , $\alpha$              | 0.76                  |

| Electric field exponent of $\mu$ , $\beta$          | 1                     |

| Coefficient of $\mu_{max}$ , $A_{\mu max}$          | 950                   |

| Exponent of $\mu_{max}$ , $B_{\mu max}$             | 2.4                   |

| Coefficient of $\mu_{min}$ , $A_{\mu min}$          | 40                    |

| Exponent of $\mu_{min}$ , $B_{\mu min}$             | 0.5                   |

| Coefficient of $N_{ref}$ , $A_{Nref}$               | 2×10 <sup>17</sup>    |

| Exponent of $N_{ref}$ , $B_{Nref}$                  | 1                     |

| Maximum saturated velocity, $v_{smax}$ (cm/s)       | 4.77×10 <sup>17</sup> |

Temperature impact is also considered in the model. For the diode shown in Figure 1,  $V_D$  is modeled as a linear function of temperature, T:

$$V_D = -0.0013T + 0.9573. (8)$$

The characteristics of the SiC Schottky diode obtained from simulations are compared to those from tests in Figure 1(b) and (c).

**Figure 1.** (a) Forward characteristics of a 600 V, 4 A SiC Schottky diode at different temperatures, (b) comparison of on-state resistance of the diode from simulations and tests, (c) comparison of voltage drop at zero current of the diode from simulations and tests.

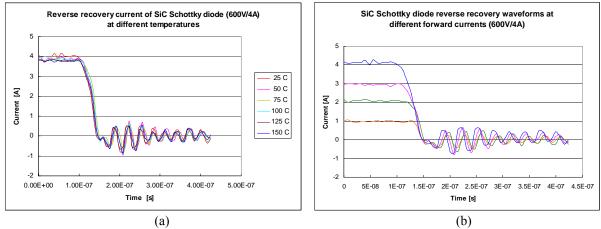

Dynamic characteristics: The same SiC Schottky diode was also tested in a chopper circuit to observe its dynamic characteristics. The reverse recovery current waveforms are obtained at different temperatures (same reverse voltage and forward current) and at different forward currents (same temperature and forward current), which are shown in Figure 2. As seen in the figure, the turn-off behavior of the diode does not change with temperature and forward current. However, it changes with the different forward voltages. Since the depletion layer capacitance dominates the reverse recovery behavior and considering equations (9) and (10), the relationship between the energy loss during the diode reverse recovery and voltage can be estimated by equation (11).

$$C_d = \frac{\varepsilon}{w_d} = \sqrt{\frac{qN_d\varepsilon}{2(V_R + \phi_B)}} \tag{9}$$

**Figure 2.** (a) Reverse recovery waveforms of a 600V/4A SiC Schottky diode at different temperatures, (b) reverse recovery waveforms of the SiC Schottky diode at different forward voltages.

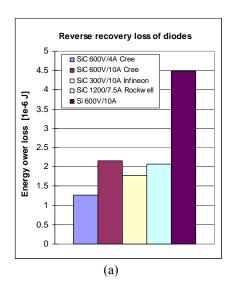

**Figure 3.** (a) Reverse recovery energy loss of diodes at reverse voltage of 200V and room temperature, (b) reverse recovery energy loss of the 600V, 4A SiC Schottky diode at different reverse voltages obtained from simulation.

$$E_{D,sw} = \frac{1}{2} C_d V_R^2 \tag{10}$$

$$E_{D,sw} = \left(\frac{V_R}{V_{R0}}\right)^{1.5} E_{D,sw0} \tag{11}$$

where  $C_d$  is depletion layer capacitance,  $V_R$  is reverse voltage,  $Ed_{D,sw\theta}$  is the energy loss at voltage  $V_{R\theta}$ . The reverse recovery energy loss of the 600 V, 4 A diode is shown in Fig. 3(a) at a reverse voltage of 200 V, and it is expanded for other voltages using equation (11) in Fig. 3(b).

### **SiC JFET Models**

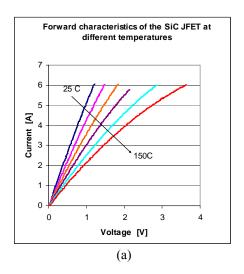

Static characteristics: The forward characteristics of a 600 V, 5 A SiC JFET obtained at different temperatures from 25 °C to 150 °C temperature are shown in Figure 4 (a). It can be approximated with the following equation:

$$V_d = R_D \cdot I_d \tag{12}$$

where  $R_D$  is on-state resistance. Since like Schottky diodes, JFETs are also majority devices, the same model can be used for  $R_D$  (equations (2-7)). The on-state resistances (at 3A) of the SiC JFET obtained from simulations are compared to those from tests in Figure 4 (b).

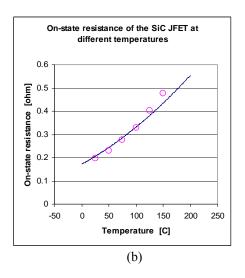

The transfer characteristics of the JFET are also obtained at different temperatures from 25 °C to 150 °C and shown in Figure 5(a). The threshold voltage and transconductance are modeled as linear functions of temperature, which are shown in Figure 5(b) and (c).

$$V_{th} = -0.0091T + 3.0167 (13)$$

$$g_m = -0.0072T + 1.9308 \tag{14}$$

**Figure 4.** (a) Forward characteristics of a 600V, 5A SiC JFET at different temperatures, (b) comparison of the on-state resistances of the SiC JFET from simulations and tests.

**Figure 5.** (a) Transfer characteristics of a 600 V, 5 A SiC JFET at different temperatures, (b) comparison of the threshold voltages of the JFET from simulations and tests, (c) comparison of transconductances of the JFET from simulations and tests.

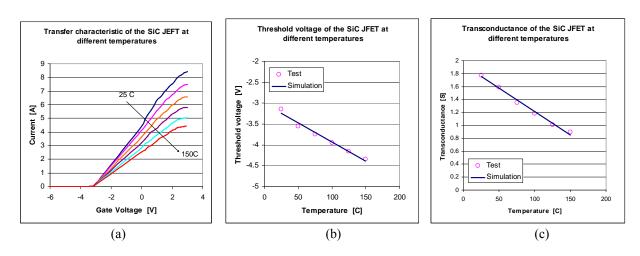

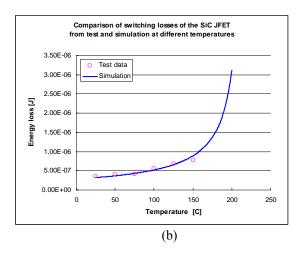

Dynamic characteristics: The same SiC JFET was also tested in a chopper circuit to observe its dynamic characteristics. The switching waveform obtained at room temperature is shown in Figure 6(a). Assuming the gate drive resistance,  $R_G$ , is 0, and the applied gate voltage,  $V_G$ , is a step signal changing from  $V_{GL}$  to  $V_{GH}$  and vice versa. Then the Miller effect is minimized in the JFET, and the current rises and falls very quickly. The switching loss of the JFET can be modeled as the charging and discharging of the drain-to-source and drain-to-gate capacitance under the control of the gate drive current [5]. The equations of turn-on energy loss and turn-off energy loss are shown as follows:

$$E_{on} = \frac{1}{3(K_1 - 1)} \varepsilon E_c V_R \left(\frac{V_R}{V_R}\right)^{1/2} \tag{15}$$

**Figure 6.** (a) Switching waveform of the SiC JFET at room temperature, (b) comparison of the switching energy losses of the SiC JFET at different temperatures obtained from simulations and tests.

$$E_{off} = \frac{1}{3(K_2 + 1)} \varepsilon E_c V_R \left(\frac{V_R}{V_B}\right)^{1/2} \tag{16}$$

where  $K_1 = g_m (V_{GH} - V_{th})/I$ ,  $K_2 = g_m (V_{th} - V_{GL})/I$ ,  $\varepsilon$  is dielectric constant,  $E_C$  is breakdown electrical field,  $V_B$  is breakdown voltage, I is forward current, and  $V_{GH}$  and  $V_{GL}$  are high-level and low-level gate voltage, respectively. The energy losses of SiC JFET at different temperatures are calculated and compared to the test results in Figure 6(b).

# LOSS MODELING FOR HYBRID ELECTRIC VEHICLES (HEVs)

The application of SiC devices (as battery interface, motor controller, etc.) in a HEV has merit because of their high-temperature capability, high-power density, and high efficiency. Moreover, the light weight and small volume will affect the whole power train system in a HEV, and thus performance and cost.

An HEV system model based on 2004 Toyota Prius HEV was developed in PSAT (Powertrain System Analysis Tool - vehicle simulation software). An inverter model based on the previous discussion is inserted in the built-in motor drive model in order to calculate the power loss and efficiency of different inverters. A 3-phase dc/ac SiC inverter composed of SiC JFETs and SiC diodes is applied to the primary motor to take the place of the conventional Si inverter. Simulations are run for a UDDS cycle (US EPA-Urban Dynamometer Driving Schedule, which represents city driving conditions of light duty vehicles) for both a HEV with a SiC inverter and one with a Si inverter. The device performance and vehicle performance are observed and compared.

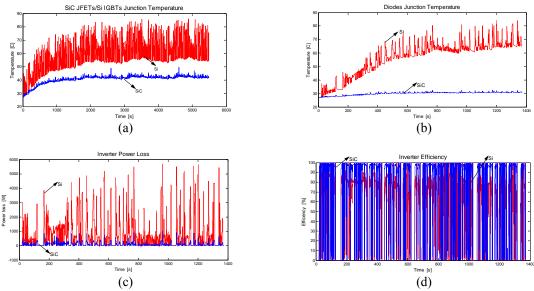

Assume the two inverters have the same size heatsink and cooling conditions, and the switching frequency is 20 kHz. The initial SOC is equal to final SOC. As for the inverter itself, the benefits of the SiC devices are demonstrated in Figure 7. Due to the lower power losses of the SiC devices, the junction temperatures of the SiC devices are much lower than those of Si ones (see Figure 7(a) and (b)). As a result, the power loss of the SiC inverter is reduced, and its efficiency is

**Figure 7.** Comparison of the SiC and Si inverters in the 2004 Toyota Prius HEV: (a) SiC JFETs/Si IGBTs junction temperature, (b) diode junction temperature, (c) inverter power loss, (d) inverter efficiency.

much improved (see Figure 7(c) and (d)). Furthermore, the benefits of the SiC-based inverter are also seen at system level. For example, the system efficiency is improved from 31.3 % to 37.2 % (increased by 22.6 %, corresponding to 0.82 kWh) due to the energy saving in other powertrain components (such as engine, generator, mechanical accessories, and etc.) and the improvement in recuperating braking energy. As a result, the fuel economy is improved from 24.1 to 29.5 km/liter (increased by 18.8%).

A plug-in hybrid vehicle (PHEV) with the same powertrain architecture and components as the 2004 Toyota Prius HEV and 50 km all electric range (AER) is also studied. Compared to the conventional HEV, more benefits are observed at both inverter-level and system-level. The system efficiency is improved from 62.6 % to 79.6 % (increased by 27.2 %, corresponding to 1.9 kWh), and the electricity consumption is reduced from 124.4 to 83.8 Wh/km (decreased by 32.6%). In addition, the studies indicate that the optimized size of the battery bank for the plug-in vehicle with the SiC inverter and that with the Si inverter are 5.1 kAh and 7.8 kAh, respectively, compared to 1.1 kAh battery for 2004 Toyota Prius HEVs (assume initial SOC 90% and final SOC 30%). Thus, for this design, using a SiC-based inverter can reduce the size of the battery bank for a PHEV by 34.6%.

Since the junction temperatures of the SiC devices in the PHEV remained low (around 40 °C) when using the same heatsink as for a Si-based inverter, an additional study was done by reducing the size of the heatsink of the SiC inverter. The junction temperature is allowed to rise to the same level as the Si inverter (around 60 °C). It is found that the efficiency of the SiC inverter is lowered by only 0.5 % and at system level, the system efficiency is lowered by 0.3 % with the smaller heatsink. Thus, using SiC devices in such a system can simplify the thermal management system and improve system compactness. For more information, see [7].

### MODELING FOR UTILITY APPLICATIONS

Because SiC is a wide-bandgap semiconductor, it inherently has higher blocking voltage. Companies are working on SiC switching devices (MOSFETs, IGBTs, thyristors) capable of

blocking  $10-20~\mathrm{kV}$  or more. While some laboratory prototypes of these high-voltage devices have been fabricated and tested, these devices will not be commercially available until several years into the future. Simulations have also shown that high voltage SiC devices in the  $10~\mathrm{kV}-20~\mathrm{kV}$  range would allow electric utility applications such as a high voltage dc (HVDC) interface to operate with fewer power electronic devices and at a higher efficiency that would save hundreds of thousands of dollars per year in operating costs because of reduced losses [9].

# **Converter for Battery Energy Storage**

A system model was developed to ascertain the effectiveness of replacing a Si-based inverter/rectifier for a battery charger with a SiC-based inverter/rectifier battery charger that would be used in combination with a renewable energy source such as solar cells or wind power. For the simulation, it was assumed the utility had a line voltage of 480 Vrms, a frequency of 60 Hz, and the converter was controlled to produce current at unity power factor. The battery bank is composed of 84 13Ah Hawker Genesis batteries in series. The battery bank is discharged at a constant current of 120 A from full charge to 40% state of charge (SOC), and the power is delivered to the utility through the three-phase, full-bridge converter. For its charging mode, it is charged at a constant voltage of 1109 V from 40% SOC to full charge, and the power is provided by the utility through the converter. In both discharge and charge processes, the converter works as an interface. They are expected to consume as little power as possible. The power losses and efficiencies of the SiC and Si converters were computed.

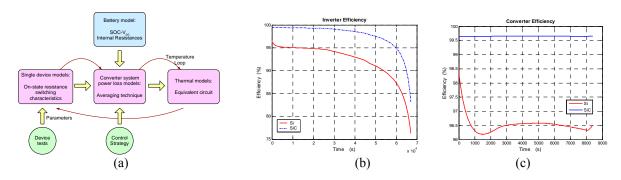

Based on the specific system information discussed previously, the battery system model shown in Figure 8(a) worked out the unknown system parameters required for power losses calculation. The lower on-state resistance of the SiC JFETs and lower switching losses of the diodes enabled the converter to operate at a lower temperature and have a higher efficiency than a comparable converter with Si devices as shown in Figure 8(b) for charging mode and Figure 8(c) for discharging mode.

Using MATLAB Simulink, two sets of simulations have been done for both the SiC-based and Si-based systems for a charge cycle and a discharge cycle, respectively. In the first set of simulations, the ambient temperatures and the heatsink sizes were the same for the Si and SiC systems. The junction temperatures are reduced by about 5-8 °C, and the average efficiency improvement is about 3.3-5.5% for the SiC-based converter. In the second set of simulations, the heatsinks were selected to limit the maximum junction temperature to 125°C for both the SiC and Si devices. The simulations indicate that the size of the heatsink required by the SiC converter is

**Figure 8.** (a) Modeling methodology for battery-converter system, (b) converter efficiency during battery charging, (c) converter efficiency during battery discharging.

reduced to about 1/25 of that of the Si converter under the same cooling method (forced cooling with fan) or 4/5 when the SiC inverter is naturally cooled, and at the same time the efficiency is improved by 3.1% for discharge, 5.4% for charge. For more information, see [8].

### 55 kW HYBRID INVERTER TESTING

SiC Schottky diodes replaced Si diodes in a 55kW inverter. The superior switching performance of the diodes improves the efficiency of the inverter and also impacts the main power switches by reducing the stress on them and thus improving system performance.

SiC Schottky diodes are already commercially available at current ratings up to 50 A. These diodes are being used in niche applications such as power factor correction circuits or as antiparallel (free-wheeling) diodes in inverters. It is expected that the first impact of SiC devices on inverters will be as a result of SiC Schottky diodes replacing the conventional Si pn diodes.

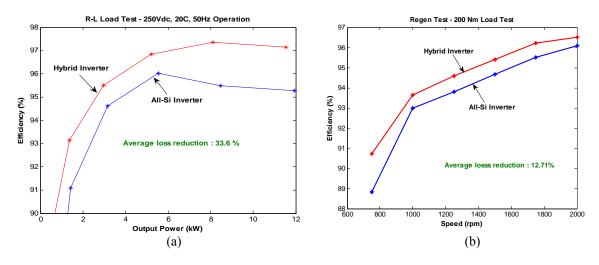

ORNL collaborated with Cree and Semikron to build a hybrid 55 kW (Si IGBT–SiC Schottky diode) inverter by replacing the Si pn diodes in Semikron's automotive inverter with Cree's SiC Schottky diodes [10]. A performance comparison of the all-Si and the hybrid inverter is shown in Figure 9. The hybrid inverter efficiencies are higher than the all-Si inverter for all operating conditions. The results show up to 33.6% reduction in the losses.

**Figure 9.** (a) R-L load test efficiency curves for one of the load conditions, (b) Dynamometer test – regeneration mode efficiency plots at 70°C.

## HIGH TEMPERATURE APPLICATIONS

SiC power electronics are able to operate at ambient temperatures well over 200°C. However, for SiC devices to operate at these elevated temperatures, packaging that can survive these temperatures and the stresses from thermal cycling are needed.

# **High Temperature Packaging**

One of the most important characteristics of SiC power devices is that they can operate at much higher junction temperatures (>300°C) than Si power devices. Presently, SiC devices use

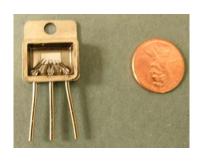

(a)

Fig. 10. (a) TO-220 through-hole high temperature package of 75 A SiC Schottky diode, (b) test results.

Si device packages that limit their operation temperature (~150°C). ORNL collaborated with the University of Arkansas and University of Idaho to build several high temperature packages that can operate at 200°C ambient [11].

A single die 600 V/75 A SiC Schottky diode was packaged in a TO-220 thru-hole style package shown in Figure 10. The packaged device was tested at different dc current levels with 200°C ambient temperature and without a heat sink. The case temperature of the diode was measured using a thermocouple. The diode operated with a case temperature of 361°C with 20 A continuous current for over an hour without a failure. However at 25 A the diode operated for a short time and it failed short. This is a significant milestone in terms of operating temperature of the device which clearly demonstrates the high temperature operation capability of SiC devices.

# **High Temperature Gate Driver**

To benefit from the high temperature operation capability of SiC power devices, other related components also need to be high temperature rated. One such component is the gate driver which has to be as close to the switch as possible to reduce the gate parasitics. The best option for high temperature gate drivers would be SiC-based ones; however, the technology is not mature enough yet. ORNL collaborated with The University of Tennessee to build high temperature gate drivers using silicon-on-insulator (SOI) technology that can handle temperatures of up to 200°C.

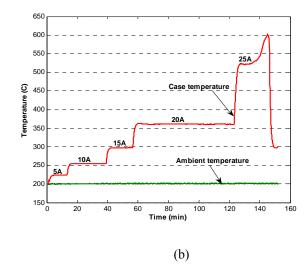

A high temperature gate driver integrated circuit (IC) was designed and fabricated using 0.8 micron, 3-metal and 2-poly bipolar CMOS and DMOS (BCD) on silicon on insulator (SOI) process [12]. Figure 11(a) shows the fabricated chip's microphotograph. This circuit occupies an area of 3.6 mm² (2,240  $\mu$ m × 1,600  $\mu$ m) including pads. The two high-voltage NMOS devices of the half-bridge output stage occupy a major portion of the die area. They are sized (W/L = 24,000  $\mu$ m/1.6  $\mu$ m) to provide large peak current as needed to minimize the switching loss of the power FET. Each of these NMOS transistors is comprised of six hundred 45 V NMOS devices (W = 40  $\mu$ m) connected in parallel. The high-voltage devices are well isolated from the low-voltage devices through a thick dielectric layer. Multiple pad connections are used for the power supply and output nodes to minimize the bond wire's parasitic inductances. All critical metal

**Figure 11.** (a)Micrograph of the gate driver IC with bond wires. (b) Gate driver IC in CDIL44 package in comparison with a dime.

interconnects are made thick to avoid electromigration which is a potential failure mechanism at higher temperatures. Figure 11(b) shows a gate driver chip in QFN44 package placed next to a dime for visual comparison of the size of the chip.

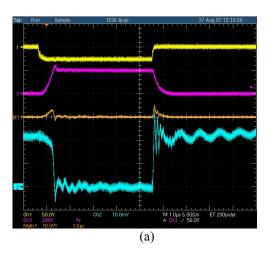

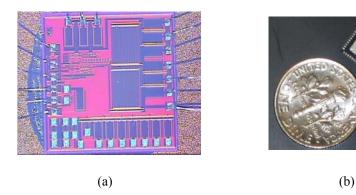

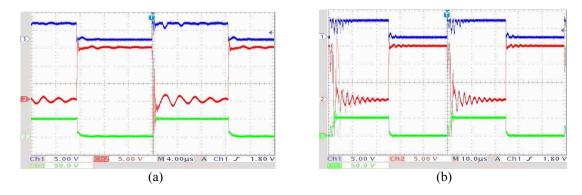

A SiC power MOSFET developed by Cree was used to test the gate driver chip. A 10 ohm resistive load was connected between the 50 V power supply and the drain terminal of the MOSFET. Approximately 5 A switching current was flowing through the load and the MOSFET when it was turned ON by the gate driver chip. The test board was placed inside a temperature chamber and the SiC MOSFET was kept outside the chamber as it was not packaged for the high temperature operation. Starting from room temperature, the chip was tested up to 200°C.

One chip was successfully tested up to 175°C and at 40 kHz switching frequency (Figure 12(a)). Another IC successfully switched ON/OFF the MOSFET up to 200°C (Figure 12(b)). The gate driver was placed inside the temperature chamber without any cooling facility and the temperature was raised from room temperature to 200°C in five steps (85°C, 125°C, 150°C, 175°C and 200°C) and at each temperature step, it was kept for 15 minutes before taking any readings. At 200°C it was tested for more than 30 minutes. This way, the chip successfully operated over 150°C for more than 90 minutes without any cooling mechanism.

After the successful testing of the first version of the chip, a second version has been designed and fabricated to improve the gate drive reducing its temperature sensitivity and adding an on-chip voltage regulator.

**Figure 12.** (a) Gate driver test results for 175°C and 40 kHz switching frequency, (b) Gate driver test results for 200°C and 20 kHz switching frequency.

### CONCLUSIONS

The device characterization, system modeling, and application tests using SiC-based power electronics have revealed some important results, which were discussed with the device manufacturers to further improve the design and fabrication. The impact of SiC devices on performance parameters compared to Si devices will have a large impact on system efficiency and thermal management issues for several applications. The inherent properties of SiC-based power electronics will enable these to become the device of choice for certain high power applications - those with high temperature ambient environment, high voltage requirements, or high switching frequency [13]. Efficiency and thermal management savings can help to justify the higher cost of SiC devices.

## **ACKNOWLEDGMENTS**

The authors wish to thank Dr. Mike Mazzola of SemiSouth and Dr. Anant Agarwal and Jim Richmond of Cree for providing SiC devices samples for testing and characterization. The authors wish to thank Dr. Fred Barlow of the University of Idaho for his high temperature packaging of SiC diodes. We also thank M. Aminul Huque, Dr. Ben Blalock, and Dr. S. Kamrul Islam at The University of Tennessee for their development of a high temperature gate driver.

### REFERENCES

- 1. H. Zhang, L. M. Tolbert, B. Ozpineci, *IEEE Workshop on Computers in Power Electronics* (2006) pp. 199-204.

- 2. H. Zhang, L. M. Tolbert, B. Ozpineci, M. Chinthavali, *IEEE Industry Applications Society Annual Meeting* (2005), pp. 2630-2634.

- 3. B. Ozpineci, L. M. Tolbert, *IEEE Power Electronics Letters*, vol. 1 (2003), pp. 54-57.

- 4. B. Ozpineci, M. Chinthavali, L. M. Tolbert, *International Journal of High Speed Electronics and Systems*, vol. 16, (2006), pp. 545-556.

- 5. B. J. Baliga, Modern Power Devices, 1987.

- 6. M. Roschke, F. Schwierz, "Electron mobility models for 4H, 6H, and 3C SiC," *IEEE Transactions on Electron Devices*, vol. 48, (2001), pp. 1442-1447.

- 7. H. Zhang, Ph.D. Dissertation of the University of Tennessee, Knoxville, December 2007.

- 8. H. Zhang, L. M. Tolbert, B. Ozpineci, M. Chinthavali, *IEEE Industry Applications Society Annual Meeting* (2006), pp. 346-350.

- 9. M. Chinthavali, L. M. Tolbert, B. Ozpineci, *IEEE Power Engineering General Meeting* (2004), pp. 680-685.

- 10. B. Ozpineci, M. Chinthavali, A. Kashyap, L. M. Tolbert, A. Mantooth, *IEEE Applied Power Electronics Conference* (2006), pp. 448-454.

- 11. F. D. Barlow, A. Elshabini, K. Vanam, B. Ozpineci, L. D. Marlino, M. S. Chinthavali, L. M. Tolbert, *IMAPS 40th International Symposium on Microelectronics* (2007).

- 12. M. Huque, R. Vijayaraghavan, M. Zhang, B. Blalock, L. Tolbert, S. Islam, *IEEE Power Electronics Specialist Conference* (2007), pp. 1491-1495.

- 13. L. M. Tolbert, H. Zhang, M. S. Chinthavali, B. Ozpineci, *Materials Science Forum*, vols. 556-557 (2007), pp. 965-970.