## ECE581

## GaN Boost Converter Design

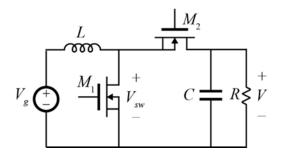

A 10-to-50 V boost converter is shown in Fig. 1. The output power is 50 W. The boost converter design constraints at this operating point are as follows:

- Power stage efficiency  $\eta \ge 95\%$

- Inductor current ripple  $\Delta i_l \leq 10\%$

- Output voltage ripple  $\Delta v_c \leq 2\%$

Figure. 1: Boost converter

Both  $M_1$  and  $M_2$  are implemented as the following device, made from Gallium Nitride on silicon:

http://epc-co.com/epc/documents/datasheets/EPC2007 datasheet.pdf

Other than the devices' resistance, output capacitance  $C_{oss}$ , and gate charge  $Q_g$ , the circuit is lossless. When calculating losses due to the device output capacitance, the full nonlinear  $C_{osss}$ -vs- $V_{ds}$  characteristic should be considered. Use a gate drive voltage of  $V_{gs} = 5$  V.

You may assume that, regardless of  $f_s$ , the switching transitions occupy a negligibly small portion of the switching period. Small ripple approximations do apply.

Assume that the size of the converter is proportional to the sum of the capacitance C and inductance L. Find the switching frequency  $f_s$  of the converter, such that the sum L + C is minimized, while still meeting the constraints on efficiency and voltage/current ripple.

Report the inductance L and capacitance C, and the switching frequency of the converter  $f_s$ .