## **Final Project**

- Select a <u>dc-d</u>c converter and application, design a closed-loop digital controller

- Detail

- Converter Design (brief, may leverage midterm)

- Target performance (both large and small-signal)

- should be aggressive

- Design and final implementation

- Design must include

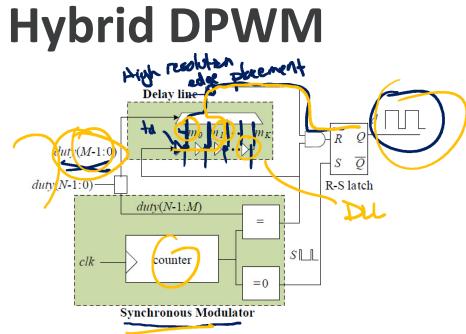

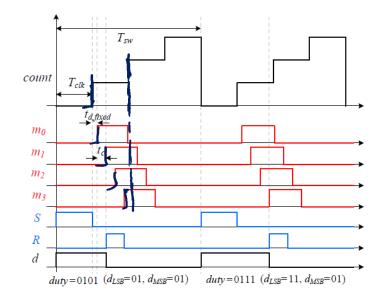

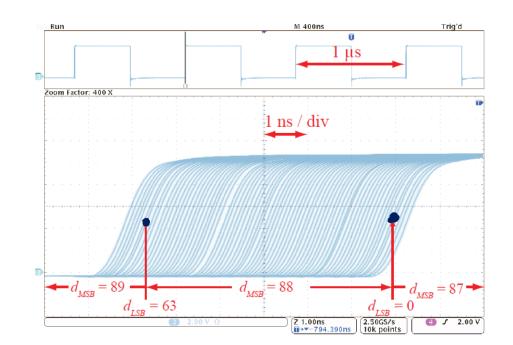

- Realistic ADC/DPWM models (sampling, delay, quantization)

- At least one additional nonlinearity (Nonlinear controller, GSS, etc.)

- At least one technique from an IEEE publication not directly discussed in class

- Validation must include

- Direct comparison between small-signal prediction and large-signal performance

- Testing over conditions motivating valid operation in a realistic use case

- Apply techniques from class

- Should result in prototype-ready paper design

- Validate through simulation (PLECs/Simulink)

- Presentations Nov 25<sup>th</sup>

- Report Due December 2<sup>nd</sup>

- Narrative of analysis and results

- Clear but minimally "wordy"

- IEEE format (though incomplete content w.r.t. review and explanation)

D. Costinett, M Rodriguez, D Maksimovic, "Simple Digital Pulse Width Modulator with 60 picoseconds resolution using a low-cost FPGA," 2012