# HDL Designer 2007.1 SystemVerilog Tutorial

For use with AVM3.0 & Questa 6.3

Mentor Graphics Company Copyright © Mentor Graphics Corporation 2007 All Rights Reserved

This document contains unpublished information that is confidential and proprietary to Mentor Graphics Corporation, 8005 SW Boeckman Road, Wilsonville, Oregon 97070.

# **Table of Contents**

| 1    | INTRODUCTION                                                 | 4  |

|------|--------------------------------------------------------------|----|

| 1.1  | Overview of the tinycache design                             | 4  |

| 2    | SETUP                                                        | 5  |

| 3    | PROJECTS                                                     | 6  |

| 3.1  | Creating a new project                                       | 6  |

| 3.2  | Add the tinycache files to the project                       | 7  |

| 3.3  | Side Data – add functional spec & test plan                  | 8  |

| 3.4  | Check the Verilog `include search path for the library       | 9  |

| 3.5  | Add the pre-compiled mtiAvm library reference to the project | 10 |

| 4    | DESIGN BROWSERS                                              | 11 |

| 4.1  | Columns                                                      | 11 |

| 4.2  | Design Unit Browser Objects                                  | 12 |

| 4.3  | File Browser                                                 | 13 |

| 4.4  | Hierarchy Browser                                            | 13 |

| 4.5  | Testbench Environment                                        | 15 |

| 4.6  | Top-level                                                    | 15 |

| 4.7  | Testbench                                                    | 15 |

| 4.8  | Assertions and Covergroups                                   | 17 |

| 4.9  | Where Used                                                   | 18 |

| 4.10 | 0 Where Bound                                                | 18 |

| 5    | THE DESIGNPAD TEXT EDITOR  5.1.1 Design Traversal            | 19 |

| _    | 5.1.2 Outline mode                                           |    |

| 6    | QUESTA VERIFICATION FLOW                                     | 20 |

| 7    | CONCLUSION                                                   | 21 |

| 8    | APPENDIX A – USING THE AVM SOURCE LIBRARY                    | 21 |

| 8.1  | Add the AVM files to the project                             | 21 |

| 8.2 | AVM_LIB – check the Verilog `include search path for the library      | 22 |

|-----|-----------------------------------------------------------------------|----|

| 8.3 | Change the Library search path for the project to use the new AVM_LIB | 23 |

| 9   | APPENDIX B - CHANGING QUESTA COMPILATION SETTINGS IN ADVANCE          | 23 |

## 1 Introduction

This document provides a self-paced tutorial with step-by-step procedures to import a simple mixed language design and use the new SystemVerilog language features in the Design Manager and DesignPad text editor in order to rapidly understand and explore a class-based testbench. The testbench uses the Questa Advanced Verification Methodology (AVM) and supports incremental compilation and launching of the Questa simulator. Further details on the AVM can be found in the Advanced Verification Methodology Cookbook Version 3.0 which can be downloaded along with examples from <a href="http://www.mentor.com/go/cookbook">http://www.mentor.com/go/cookbook</a>

A number of other tutorials can be accessed from links in the HDL Designer Series InfoHub which is opened by choosing Help and Manuals from the **Help** menu in all application windows.

All user commands in the tutorial procedures are referenced using their menu path (shown in bold text). However, many commands can also be accessed using the toolbar, shortcut bar or keyboard shortcuts. Refer to Shortcut Keys in the **Quick Reference Index** which can be accessed from the HDL Designer Series InfoHub opened through the **Help** menu.

The tutorial is divided into sections containing numbered procedures. Unnumbered paragraphs provide additional information or give advice on other ways to perform an operation. The procedure numbers are continuous through a section and restart for each new section.

The use of the term **RMB** in this document represents pressing the Right Mouse Button.

## 1.1 Overview of the tinycache design

\*\* This example is designed to be used with AVM version 3.0 \*\*

\*\* together with Questa version 6.3 \*\*

The "TinyCache" project is a 16 word, 8-bit, write-through cache that sits between a CPU and its memory. All writes to the memory and all reads from the memory go through the cache. If the contents of a requested memory address are not currently stored in the cache (a cache miss), the CPU must wait until the cache has loaded the word from the memory before it can receive the data.

The cache uses the 4 least significant bits (LSB) of the address to access the first 16 words of a 255 word RAM.

The cache contains 3 RAMs

Date Modified: 29-Jul-07

- Cache RAM

An 255x8 bit RAM which stores the cached data.

- Key RAM

An 255x16 bit RAM which stores the addresses related to the cached data.

- Invalid

A 255-bit register which contains the status for each entry. All entries are made invalid on reset.

The design uses two protocols. The Tinycache...

- is a master for the memory bus...

- ...and a Slave for the CPU bus

Each transaction is clearly defined and there are a number of different interactions between these transactions.

Although this is a very simple design, the approach would be similar for a complex ASIC or FPGA.

More information on the design can be found in the Functional Spec which you will be associating with the design later on in the tutorial.

# 2 Setup

#### 1. Questa 6.3

If you have not already installed Questa 6.3, please install it now.

## 2. Invoke HDL Designer

#### 3. Preference migration

- If you have used a previous 2007.1 beta build, your preferences will not be migrated. It is therefore

recommended that you rename the HDL Designer Preferences directory to ensure you are using

the most up-to-date preference settings.

- On Windows the preferences directory is:

C:\Documents and Settings\<user\_name>\Application Data\HDL Designer Series

- On UNIX/Linux the preferences directory is:

<nome\_directory>/hdl\_designer\_series

- If you have used earlier released versions of HDL Designer, a message will appear in the log window to inform you that your preferences are being migrated to a new 2007.1 set. This will not affect your existing preferences, instead a copy of your current preferences directory will be made and modified to incorporate the new 2007.1 options.

#### 4. General Settings

- If this is the first time HDL Designer has been invoked on your machine, the tool will automatically bring up the Setup Assistant.

- Otherwise please invoke it directly using Help> Setup Assistant

- Step through the wizard. On the *simulator page* set **Questa 6.3** as your simulator. On the *Project page* choose **Examples**. You will be creating a new project later on.

#### 5. Text Editor Settings

- In order to review the SystemVerilog features available within the HDL Designer DesignPad text editor, please ensure DesignPad is set as the default text editor.

- To do this, choose Options> Main and go to the "Text" tab.

- Use the drop-down to select DesignPad as the Editor (and optionally also as the HDL Viewer).

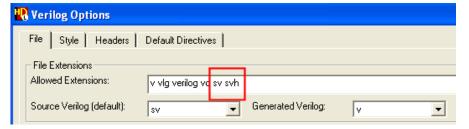

#### 6. File Extension Settings

- This design uses the ".sv" extension for SystemVerilog source files and the ".svh" file extension for included class files.

- To check that these extensions have been added to the allowed list, choose Options> Verilog

and review the list of allowed File Extensions on the "File" tab. If the list does not include ".sv" or

".svh", please type them in it at the end of the list.

#### 7. Switching back to pre-2007.1 language parsing

- If you wish to switch back to the language parsing used in previous releases, you can do this by setting the environment variable HDS\_2006\_VLOG\_PARSER to any value (eg 1 or TRUE).

- Note, however, that this will restrict SystemVerilog parsing to the 3.0 Accellera standard subset which will not support the IEEE Std 1800™-2005 verification constructs used in this tutorial.

# 3 Projects

HDL Designer interacts either directly with your existing design files or on a copy of specified design files. You can direct HDS to analyze a design simply by specifying a directory underneath which the HDL files are located.

A library can be treated like an environment variable which maps to the directory containing the HDL files for a given design. The files can reside in any number of subdirectories and have any names.

You can associate descriptions and other data with the design by specifying an HDS mapping for the logical library name. A typical logical library name would have an "HDL" mapping to the HDL directory and an "HDS" mapping to the associated data directory. Additional mappings can be specified for directories in which downstream tool data such as a compiled simulation database or the output of synthesis should be stored. The tool will create appropriate default mappings where necessary.

When using repository-based Version Management tools, libraries will also have corresponding mappings for the HDL and HDS repository locations.

For VHDL designs, library directories correspond to VHDL library names. For Verilog designs, they represent a convenient way to refer to the design directories.

Many designs may just use a single library, although typically there would be a small number of IP directories with corresponding mappings to allow shared components to be reused without the need for copying. Complex designs may be spread across many libraries.

The mapping of logical library names to their actual location on the file system is stored in the HDS project file (\*.hdp). The same libraries can be used in different projects, eg for directories of shared IP or reusable components.

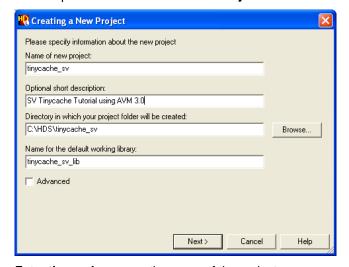

# 3.1 Creating a new project

First you will need to create a new project in which to put the tinycache design and reference the precompiled AVM library.

1. Use the pulldown menu File> New> Project...

- Enter tinycache\_sv as the name of the project.

- 3. Specify a convenient location for the project folder to be created.

- 4. Click on **Next** to view the summary page.

- 5. Click on Next again and choose the option Add existing design files

- 6. Click Finish to compete the process.

- 7. You will now add the tinycache files to the project...

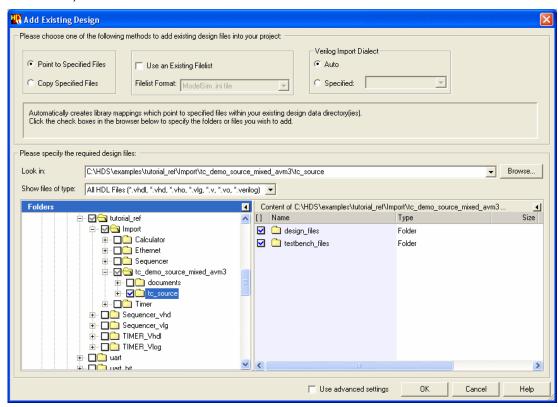

# 3.2 Add the tinycache files to the project

We will next point to the Tinycache design and testbench.

- 1. In the resulting dialog box, you can either reference (point to) or copy the existing design. Choose: *Point to Specified Files*.

- 2. Set the Show files of type filter to All HDL Files

- 3. Using the File browser, navigate to the folder containing the tinycache source files, for example:

C:\HDS\examples\tutorial ref\Import\tc demo source mixed avm3\tc source

**Check** the tc\_source folder in the Folders pane.

The dialog should look like this (again note the check marks and the content of the right-hand pane in the browser):

4. Click OK.

Date Modified: 29-Jul-07

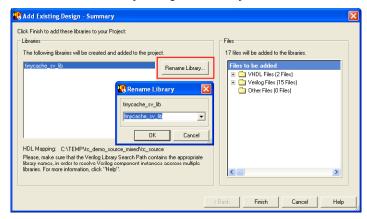

- We are going to add the tinycache files to the default library, so in the Summary dialog, click on Rename Library...

- 6. In the *Rename Library* dialog choose tinycache\_sv\_lib from the drop-down and **OK** the dialog.

- 7. Then click **Finish** to add the files to the tinycache\_sv\_lib library within the project.

- 8. The following dialog maybe displayed. If so simply click **OK**.

- 9. The design is added to the project and the top of the design is automatically detected.

- 10. Note the following:

- The tool can parse any specified HDL files irrespective of how they are named or the directory structure underneath the specified library folder.

- Any critical syntax errors which prevent the tool from extracting the overall design structure and dependencies would be flagged, as would be any missing or unbound instances.

- The tool also automatically detects the language and dialect of the files, allowing mixed-language designs to be added to the project in one pass.

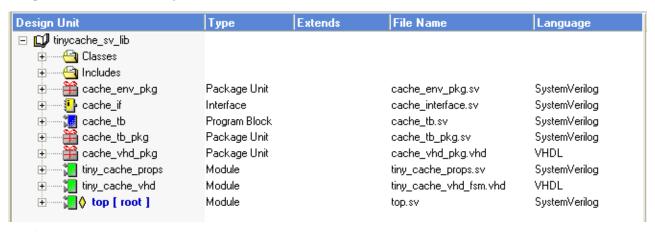

- In the "Design Unit Browser" you can see the cache\_env\_pkg SystemVerilog package file.

The .svh files included by the package are all detected and shown as include files within the "Includes" virtual folder.

- All Classes have also been identified and are shown grouped under the "Classes" virtual folder.

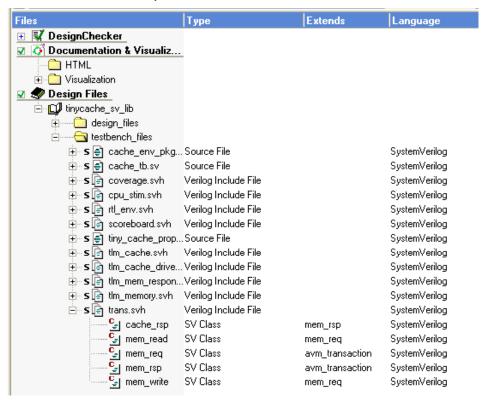

- The "Files Browser" shows the actual files and folders as they appear in the file system. In this

case, since we used the option "Point to Specified Files" these are the original files still in their

original location.

## 3.3 Side Data – add functional spec & test plan

When developing, understanding or verifying a design, it is important to be able to quickly refer to the design documentation and test plan.

Just as you were able to reference or import the design and testbench, you can also create, import or reference any other files and associate them with objects in the design. The following steps show how to associate the Functional Spec and Test Plan with the top-level of the tinycache. Alternatively the documents can be placed in a sub-directory within the files browser.

- 1. Click on the **Sub Browser** tab which is located down the right hand edge of the tool. This shows you the *Side Data* and *Downstream* browser panes if they are not already visible.

- 2. In the *tinycache\_sv\_lib* library, select the *tiny\_cache\_vhd* design unit by clicking on it.

- 3. In the Side Data browser, RMB on *User Data* & choose Add> Existing Files...

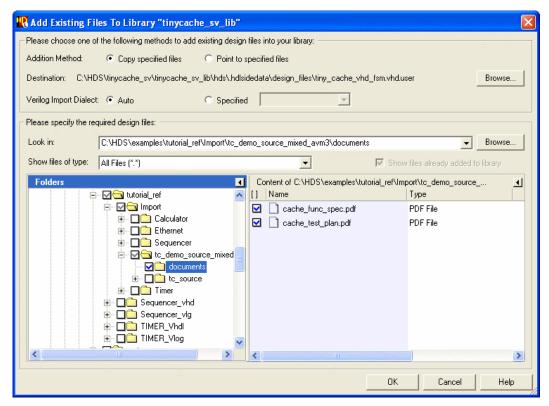

- 4. In the resulting dialog box, choose Copy Specified Files.

- 5. Set the Show files of type filter to All Files

- 6. Using the File browser, navigate to the *documents* folder, for example:

C:\HDS\examples\tutorial ref\Import\tc demo source mixed avm3\documents

Check the documents Folder inside tc demo source mixed avm3

The dialog should look like this (again note the check marks and the content of the right-hand pane in the browser):

- 7. OK the dialog.

- 8. You can now open the documents at any time by selecting the "tiny\_cache\_vhd" design unit, expanding the "User Data" folder and double-clicking on the document within the Side Data browser.

# 3.4 Check the Verilog 'include search path for the library

As we have seen, the library contains a number of include files in subfolders. In order for these include files to be found, the appropriate search path must be defined.

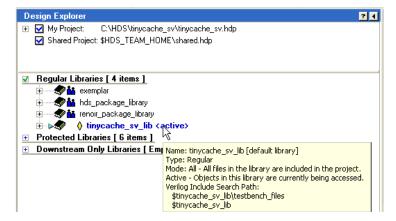

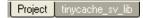

To check the Verilog Include search path for the tinycache\_sv\_lib, click on the Project tab at the bottom left of the tool.

- 2. Ensure the **Regular Libraries** group is expanded.

- 3. Hover the cursor over the tinycache\_sv\_lib and check the entries for "Verilog Include Search Path"

- 4. Ensure the list contains **\$tinycache\_sv\_lib \testbench\_files** and **\$tinycache\_sv\_lib**Note that the "\$" in front of a library name acts as a environment variable which refers to the HDL source mapping directory for the library.

- If not, you can edit the search path using RMB over the tinycache\_sv\_lib library and choosing Edit Verilog Include Search Path

# 3.5 Add the pre-compiled mtiAvm library reference to the project

The AVM library is available pre-compiled in the Questa installation. Since the AVM library will potentially be used by a number of libraries in the project, we need to add it to the project library search path so all other libraries in the project can find the compilation units within it (eg the package).

In a real development environment, the AVM library reference would typically be added to a shared project so that it can be accessed by many different projects across many design teams.

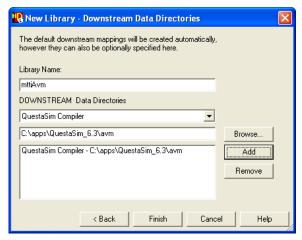

- 1. Staying in the Project Tab, use File> New> Library...

- 2. Click library type **Downstream Only** then click **Next>.**

- 3. Enter library name mtiAvm

- 4. From the drop-down list choose **QuestaSim Compiler** and browse to the pre-compiled AVM library in your Questa installation eg C:\apps\QuestaSim 6.3\avm

- 5. Click the Add button then click Finish in the wizard.

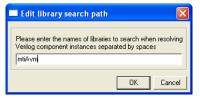

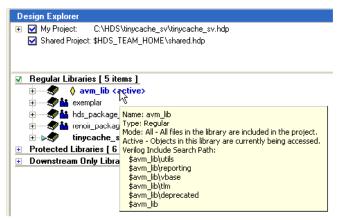

- Now add the library to the search path.

RMB over *My Project* and choose Edit Verilog Library Search Path

- Enter mtiAvm and OK the dialog. (Note there is no "\$" – the Library Search Path contains logical library names rather than directory names)

Note that, if you wish to analyze the AVM source, you could add it to the project in the same way you added the tinycache design. See Appendix A – Using the AVM source library on page 21.

# 4 Design Browsers

The Design Manager provides 3 main views of the HDL design data:

- Design Unit Browser

This is a "virtual" representation of the main declarative objects within the design.

- Design Files Browser

This shows the actual file structure of the files and folders which are part of the project, HDL source files can also be expanded to see the top-level objects within them.

- Design Hierarchy Browser

This shows the static instance hierarchy from a given level. Modules, classes and Program Blocks can be dragged into this browser (or the menu item Edit> Show Hierarchy used) in order to explore the design hierarchy underneath that level.

- Object List

The Design Unit browser can be toggled to an object list where you can group, sort and filter all objects (including instances)

You can control which objects are visible, which columns of additional data are shown (including user-defined property information) and save these settings in alternative "viewpoints".

#### 4.1 Columns

For this tutorial, we will modify the column information shown within each browser:

1. Click on the tinycache\_sv\_lib tab at the bottom left of the tool.

- 2. Click on the button in the top-right corner of the Sub Browser pane to collapse it. This gives more space for the other browser panes.

- 3. In the Design Unit browser, **RMB** over the *header row*.

- 4. In the drop-down list, ensure the following fields have check marks

- o Type, Extends, File Name, Language

Note: Instead of changing each one individually, you can choose the option **more...** at the end of the list and change the settings in the Viewpoint Manager.

- 5. Similarly, in the File browser ensure the following fields have check marks

- o Type, Extends, Language

- 6. Finally, in the Hierarchy browser ensure the following fields have check marks:

- Design Unit Name, Extends, File Name, Library

- You can click-drag a column header to move the column or drag the dividers to change the size of the column.

# 4.2 Design Unit Browser Objects

The following objects can be seen in the tinycache\_sv\_lib library:

- VHDL and Verilog Modules

- o SV Program Block

- SV Interface

- SV and VHDL Packages

- Classes virtual folder

- Includes virtual folder

- 1. Expand each object in turn.

- Double-click on the package cache\_env\_pkg

The package is opened in the DesignPad text editor. You will look at the editor in more detail later on.

This package `includes all the tinycache testbench classes.

Drag select the first included file trans.svh (take care not to select the quotes) and use the menu item File> Open Selected.

This opens the transaction class file in DesignPad. This file contains the classes for the main tinycache transactions.

- 4. Close trans.svh using File> Close.

- 5. The file **cache\_env\_pkg** should still be open. **Double-click** the second package name **cache\_tb\_pkg** and use the menu item **File> Open package**.

This opens the cache\_tb\_pkg file in DesignPad which contains the parameters and user-defined types.

6. Close DesignPad using File> Exit.

## 4.3 File Browser

You can also expand the files themselves to see the top-level objects contained within them.

For example, expand folder testbench\_files and then expand file trans.svh to see the transaction classes defined within it which you saw earlier.

#### 4.4 Hierarchy Browser

- If not already shown, RMB over the Design Unit top and choose Show Hierarchy.

This shows you the static instance hierarchy of the design.

- 2. **Expand** top to see the following:

- The tiny\_cache\_vhd VHDL RTL device under test (DUT)

- The cache\_tb Program block (tb) which contains the testbench

- The cache if interface which connects the DUT to the testbench program block (c\_if)

- 3. Now **expand** the Program Block **tb** to see the top-level verification environment class (env).

- 4. **Expand** the Class *env* which will show the top-level instances within the testbench.

You can also expand into the other hierarchical blocks - the *coverage* block and the *scoreboard*Since we are using the pre-compiled AVM library, objects within the AVM library are not displayed (eg cpu\_f, mem\_f)

5. If necessary, use the **F5** key to refresh the browser contents.

Note that objects from the AVM library are shown in red since the source is not available.

| esign Hierarchy                | Design Unit Name    | Extends         | File Name              |

|--------------------------------|---------------------|-----------------|------------------------|

| ∃ 🏚 top                        | top                 |                 | top.sv                 |

|                                | top                 |                 | top.sv                 |

|                                | cache_if            |                 | cache_interface.sv     |

| <u>₽</u> DUT                   | tiny_cache_vhd      |                 | tiny_cache_vhd_fsm.vhd |

|                                | cache_tb            |                 | cache_tb.sv            |

| —— <mark>(≜)</mark> c_if       | cache_if            |                 | cache_interface.sv     |

| ⊟ <mark>⊆</mark> env           | tb_env              | avm_env         | rtl_env.svh            |

| — <mark>∰</mark> c_if          | cache_if            |                 | cache_interface.sv     |

| ⊕ © cov                        | coverage            | avm_threaded_co | coverage.svh           |

|                                | cpu_stim            | avm_threaded_co | cpu_stim.svh           |

| — <b>□</b> cpu_f               | tlm_req_rsp_channel |                 | rtl_env.svh            |

| ⊕ 🤤 driver                     | tlm_cache_driver    | avm_threaded_co | tlm_cache_driver.svh   |

| ⊞                              | tlm_memory          | avm_threaded_co | tlm_memory.svh         |

| <b>⊡</b> mem_f                 | tlm_req_rsp_channel |                 | rtl_env.svh            |

| 🗓 🤤 responder                  | tlm_mem_responder   | avm_threaded_co | tlm_mem_responder.svh  |

| 🖃 🖫 scoreboard                 | cache_scoreboard    | avm_threaded_co | scoreboard.svh         |

| actual_cache_rsp               | cache_rsp           | mem_rsp         | trans.svh              |

| actual_cache_rsp_export        | avm_analysis_export |                 | scoreboard.svh         |

| actual_cache_rsp_fifo          | analysis_fifo       |                 | scoreboard.svh         |

| actual_mem_req                 | mem_req             | avm_transaction | trans.svh              |

| actual_mem_req_export          | avm_analysis_export | _               | scoreboard.svh         |

| actual_mem_req_fifo            | analysis_fifo       |                 | scoreboard.svh         |

| ± S  cache                     | tlm_cache           | avm_threaded_co | tlm_cache.svh          |

| - 10 cache_req_export          | avm_analysis_export |                 | scoreboard.svh         |

| - 10 cache_req_fifo            | analysis_fifo       |                 | scoreboard.svh         |

|                                | tlm_req_rsp_channel |                 | scoreboard.svh         |

| <u>S</u>   cpu_req<br>S  dummy | mem_req             | avm_transaction | trans.svh              |

|                                | cache_rsp           | mem_rsp         | trans.svh              |

|                                | tlm_memory          | avm_threaded_co | tlm_memory.svh         |

| ——— mem_f                      | tlm_req_rsp_channel | - <b>-</b>      | scoreboard.svh         |

|                                | cache_rsp           | mem_rsp         | trans.svh              |

| predicted_cache_rsp_fifo       | analysis_fifo       |                 | scoreboard.svh         |

| predicted_mem_req              | mem_req             | avm_transaction | trans.svh              |

| predicted mem reg fifo         | analysis_fifo       | <u>-</u>        | scoreboard.svh         |

#### 4.5 Testbench Environment

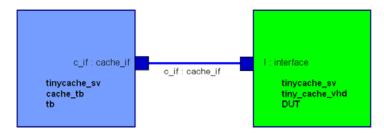

# 4.6 Top-level

The diagram below shows the top-level with the Tinycache Device Under Test connected to the testbench Program Block via a single SystemVerilog interface

A Module containing the SVA properties is also "Bound" to the DUT at this level.

Packages: import avm\_pkg::\*; import cache\_tb\_pkg::\*;

#### 4.7 Testbench

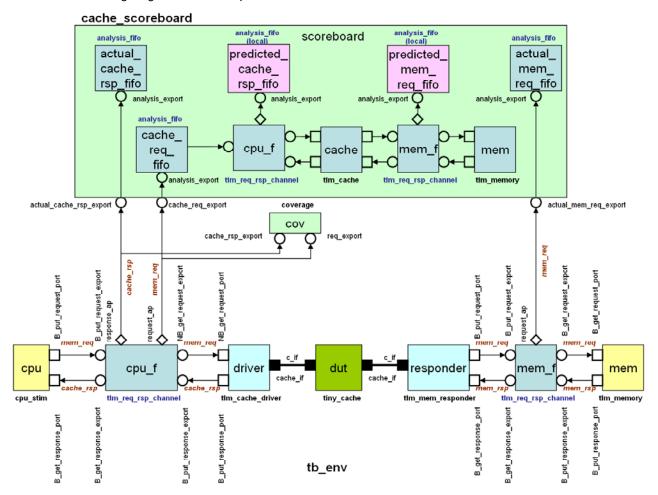

The following diagram shows a representation of the overall testbench

As mentioned earlier, the Tinycache DUT sits between the CPU and the main memory.

Across the bottom is the master/slave testbench structure, from left to right this comprises:

- *cpu* In the testbench the CPU block emulates the behaviour of the CPU by generating stimulus ie read, write and reset operations via mem\_req (memory request) transactions.

- **cpu\_f** This contains 2 fifos, one in each direction (depth of 1). Since the transaction layer is untimed, each fifo holds the next transaction until it can be processed.

- driver This converts between transactions and "pin wiggles" in the interface connected to the DLIT

- dut this is the RTL-level cache

- responder This does the same as the driver but on the memory side

- **mem\_f** This does the same as **cpu\_f** but on the memory side

- *mem* This is a high-level model of the memory.

The other two main blocks are the coverage block and the scoreboard.

To maximise reuse, these would typically be attached to the interface via a monitor (similar to a one-way driver/responder). In this case, since it is a custom interface, they are attached to the driver/responder themselves via analysis ports.

- **cov** This is a hierarchical block and contains the covergroups to gather functional coverage information on the operations performed, addresses accessed etc.

- scoreboard This contains a replica of the main testbench, but this time with a high-level model of the tinycache.

The same information goes to the scoreboard (via analysis ports) and the predicted and actual requests and responses are "stored" in fifos and compared. Messages then write out the information to the log.

In addition, the assertions/coverpoints module *tiny\_cache\_props* is "bound" to the VHDL DUT so that assertions and temporal coverage can monitor activity of the RTL cache.

- Double-click on the top-level testbench environment instance env.

This opens the tb env class in the text editor.

- Note the code browser to the left of the editing area which groups the main objects within the file

- You can control the amount of information shown here using Options> Preferences and choosing Code Browser.

- The Code Browser provides two-way cross referencing.

- 2. **Expand** the *tb\_env* class in the *Code Browser* and then the *declarations* group.

- 3. Click on items in the *Code Browser* and see them highlighted in the *editor* pane. Clicking in constructs in the *editing* pane will highlight them in the *Code Browser*.

- 4. Close DesignPad using File> Exit.

Date Modified: 29-Jul-07

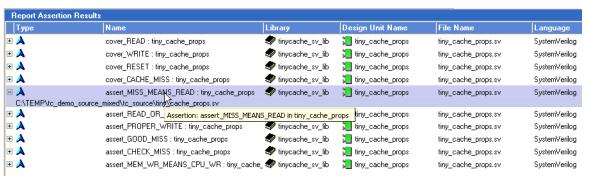

## 4.8 Assertions and Covergroups

Assertions and coverage are vital aspects of an Advanced Verification methodology. In addition to the advanced Find capabilities, HDL Designer provides specific reports to summarise and locate assertions, property-based temporal coverage and SVA functional covergroups within the design. You can report assertions/coverage within a single object, its hierarchy or within the entire library

In the Design Manager, RMB on the Design Unit top and choose Reports> Assertions(SV)> For Library

A report tab is opened. You can sort, filter and group these entries (RMB on the header) or even add/remove additional columns of information.

- Double-click on any entry (eg assert\_MISS\_MEANS\_READ).

DesignPad opens and highlights the assertion.

- 3. Go back to the Assertions report and **close** it (RMB over the tab at the bottom or click on the small at the top-right of the report tab.

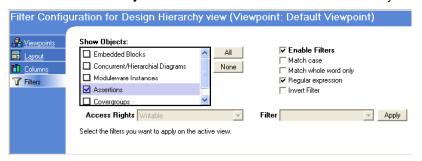

- You can optionally view assertions in the hierarchy browser using the Viewpoint filter mechanism.

There are Additional Viewpoint filters for

- o Assertions, covergroups for the Hierarchy browser

- Interfaces and Program Blocks for the Design Unit browser

- 5. Choose Tools> Viewpoint manager

- Click on the filters tab (ensure the hierarchy window is active, if not click in the hierarchy window to activate it)

- 7. Scroll in the Show Objects window and ensure the Assertions entry is checked.

- 8. Now **close** the **Viewpoint Manager** using the in the top right of its window.

- RMB on the Design Unit tiny\_cache\_props and choose Show Hierarchy

- 10. If necessary, **expand** this and you will see the assertions within *tiny\_cache\_props*.

- Similarly for Covergroups, RMB on the Design Unit top and choose Reports> Covergroups (SV)> For Library

- Double-click on any entry (eg address\_cover).

DesignPad opens and highlights the construction for the new address\_cover object.

- 13. To locate the declaration, RMB on address cover and choose Go To Declaration.

- 14. Close DesignPad and then close the CoverGroup report (**RMB** over the tab at the bottom or click on the small at the top-right of the report tab.

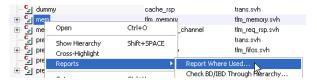

#### 4.9 Where Used

When making changes to a design object, it is important to be able to find out where and how that object is used. The **Where Used** report lists the instances of a selected Interface, Program Block, Package or Class.

- 1. **Expand** the **Scoreboard** instance in the hierarchy browser.

- 2. RMB on mem and choose Reports> Report Where Used...

3. A dialog appears to allow you to change the scope of the report. Leave the scope as *Libraries in this Design Explorer tab only* and **OK** the dialog.

Another report tab appears (similar to those for assertions and covergroups earlier).

You can see that the **mem** class (which is the memory model) is used in 2 places – in the top level of the testbench where it acts as a model of the main memory and also in the scoreboard. This is because the scoreboard replicates the testbench using a high-level model of the DUT in order to predict the response to a given stimulus and to compare the predicted value with the actual values.

- To check double click on each entry in turn which will open the containing class in DesignPad.

- Close the report.

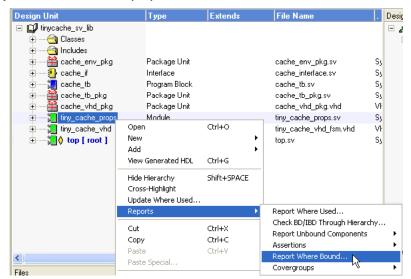

#### 4.10 Where Bound

The SystemVerilog "Bind" construct allows you to associate verification components with a DUT without editing the source. This is especially useful when the DUT is of another language as is the case in the tutorial example where the SVA Properties, Assertions and Cover directives have been placed in a Module and associated with the VHDL DUT in the top-level.

In the Design Unit Browser, RMB over tiny\_cache\_props and choose Reports> Where Bound (SV)

Another report tab appears (similar to those for assertions and covergroups earlier).

You can see that the *tiny\_cache\_props* module (which contains the Properties, Assertions and Cover directives) is bound as an instance *tc\_bind* in file *top.sv*.

- 2. Double-click on the entry

- DesignPad opens and highlights the bind instance which binds the properties module to the VHDL tiny\_cache\_vhd component.

- 3. Close DesignPad and then close the Where Bound report (**RMB** over the tab at the bottom or click on the small at the top-right of the report tab.

# 5 The DesignPad Text Editor

DesignPad is a fully-featured, design-aware text editor. It provides syntax parsing and language templates for VHDL, Verilog and SystemVerilog, plus customisable syntax highlighting for these and a range of other languages including PSL, XML, C/++, Tcl, XML etc.

The editor is tightly integrated with HDL Designer to provide Drag 'n drop Component instantiation, Design navigation (open up/down), Cross-referencing and Task and Version Management integration.

In addition to common text editor features, DesignPad also provides Outlining/code folding, Column editing, bracket matching, HTML Export, link traversal, file compare and powerful Search functions including "find in files".

A Code Browser provides an interactive abstraction of the key constructs within the file.

With customizable, menus and shortcuts, the editor also supports Emacs and Vi keystroke emulation.

For more information on DesignPad please see **Help> User Guide** from within DesignPad; or from the Design Manager see **Help> Help and Manuals** to open the HDS InfoHub and choose DesignPad User Manual from the **Help and Manuals** tab.

#### 5.1.1 Design Traversal

- In the *Design Unit browser*, double-click on top. This will open the module "top" in DesignPad.

- Click the cursor on the tiny\_cache\_props instance and RMB to choose Open Down > <file path>

This opens the properties module.

```

// Bind the properties module to the VHDL DUT

bind tiny cache vhd tiny_cache_props to bind

(

Cut

.clk

(clk),

⊆ору

.rst

(rst),

Append

(cpu_rd),

.cpu_rd

Paste

.cpu wr

(cpu wr),

Open Down

Src:testbench_files/tiny_cache_props.sv(tiny_cache_props)

.cpuwait

(cpuwait),

.mem rd

(mem rd),

14

Look Word Next

.mem_wr

(mem_wr)

Look Word Previous

Go To Declaration

```

#### 5.1.2 Outline mode

In addition to the code browser view, you can also perform "code folding" by using "Outline mode".

Click on the right-hand icon underneath the line number column or choose Document> Outline Mode.

The code constructs are collapsed allowing you to choose which parts of the file you wish to view or work on.

- 2. Experiment with **expanding** and **collapsing** some of the constructs.

- To turn Outline mode off either click on the left-hand icon underneath the line number column or choose **Document> Outline Mode.**

#### 5.1.3 Syntax checks

DesignPad performs syntax checking when the file is saved. You can also check the syntax at any time simply by clicking on the syntax check toolbar button or **Document> Check Syntax**.

1. Remove the trailing parenthesis ")" from the module declaration line and check the syntax using **Document> Check Syntax.**

A report pane appears and flags any warnings or errors. You can click on the entries to take you to the problem area of the code. This report can also be saved or printed for future reference.

Close the file without saving either by clicking on the in the top-right corner of the editing pane or by using File> Close.

Ensure you say No when asked to save the changes.

#### 6 Questa Verification Flow

After initial analysis of the project files, HDL Designer incrementally parses files when they change and identifies the impact on any dependencies. This allows the tool to automatically determine which files need to be recompiled at any given point.

- 1. Select Design Unit top in the Design Unit Browser

- To run the Questa compile and simulation flow either RMB on the Simulate icon in the main Shortcut

Bar and choose Run through components or use the pulldown menu Tasks> QuestaSimFlow> Run

through components.

Compilation works across multiple libraries.

During compilation, you may see a number of warning messages. These can be suppressed in future compilations by adding the Questa suppress command to the compilation task (see Appendix B - Changing Questa compilation settings in advance on page 23).

The Simulation dialog will appear.

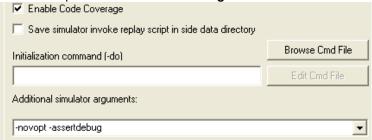

3. Check the option Enable Code Coverage...

In the Additional simulator arguments field type -novopt -assertdebug

then **OK** the dialog

QuestSim invokes

- Enable the Analysis windows using View> Coverage> Assertions, View> Coverage> Cover Directives, View> Coverage> CoverGroups

- Setup the wave window by running the wave.do script e.g. do C:/HDS/examples/tutorial\_ref/Import/tc\_demo\_source\_mixed\_avm3/wave.do

- 7. **Run** simulation for a short time e.g. run 1000

- 8. Examine the simulation waveforms and the assertions in the waveform.

- 9. Also refer to the messages in the log window The *configure* function within the *tb\_env* class currently has the message verbosity level set to the maximum of 3. This can be changed to a lower level of 1 or 2 or turned off altogether by setting the value to 0.

- Ensure top is selected in the Sim tab of the Workspace window and View the assertions and cover directives results in the Analysis window.

- Now click on the cache\_env\_pkg in the Sim tab of the Workspace window and View the covergroup results in the Analysis window.

- 12. Close Questa using File> Quit.

## 7 Conclusion

This concludes the overview tutorial.

You should now feel confident to follow similar steps on your own existing design or to create a new design using the file template, language templates and drag and drop instantiation capabilities.

For information on the many other HDL Designer features which were not covered in this tutorial (such as Design Management, Version Management, etc.) please see **Help> Help and Manuals** to open the HDS InfoHub and choose the HDS User Manual from the **Help and Manuals** tab.

# 8 Appendix A – Using the AVM source library

If you would like to explore the AVM source within HDL Designer rather than using the pre-compiled version, you simply follow similar steps to those for "importing" the tinycache design.

# 8.1 Add the AVM files to the project

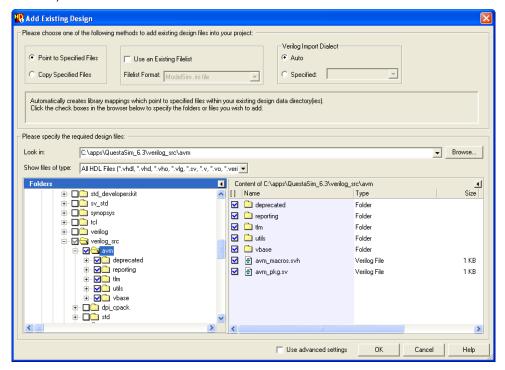

- 1. Choose **File> Add> Existing Design**. This will bring up the dialog you used earlier which allows you to create new design objects or add existing design files.

- 2. In the resulting dialog box, you can either reference (point to) or copy the existing design. Choose: *Point to Specified Files*.

- 3. Set the Show files of type filter to All HDL Files

- 4. Using the File browser, navigate to the folder containing the AVM source files in the Questa installation, for example:

C:\apps\QuestaSim\_6.3\verilog\_src

**Check** the avm folder in the Folders pane.

The dialog should look like this (note the check marks and the content of the right-hand pane in the browser):

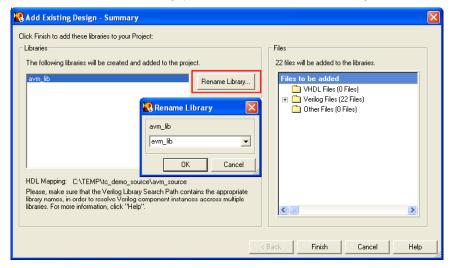

- 5. Click OK

- We are going to have a separate library for the AVM, so in the Summary dialog, click on Rename Library...

- In the Rename Library dialog type in avm\_lib and OK the dialog.

# 8.2 AVM\_LIB - check the Verilog `include search path for the library

As we have seen, the library contains a number of include files in subfolders. In order for these include files to be found, the appropriate search path must be defined.

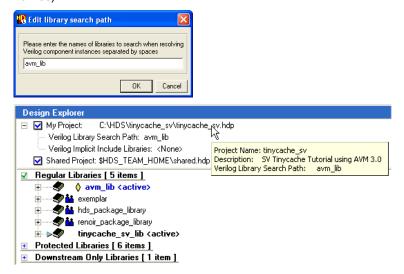

To check the Verilog Include search path for the avm\_lib, click on the Project tab at the bottom left of the tool.

- 7. Ensure the Regular Libraries group is expanded.

- 8. Hover the cursor over the avm\_lib and check the entries for "Verilog Include Search Path"

- 9. Ensure the list contains at least \$avm\_lib

- If not, you can edit the search path using RMB over the avm\_lib library and choosing Edit Verilog Include Search Path

# 8.3 Change the Library search path for the project to use the new AVM\_LIB

- 1. Staying in the Project Tab, RMB over My Project and choose Edit Verilog Library Search Path

- Delete the pre-compiled library eg mtiAvm (if it is there) and enter avm\_lib and OK the dialog. (Note there is no "\$" – the Library Search Path contains logical library names rather than directory names)

# 9 Appendix B - Changing Questa compilation settings in advance

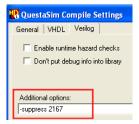

The following steps explain how to modify the Questa Compile task setting. In addition to the options supplied in the dialog, you can also enter any vcom or vlog options. In this example, you will add the "-suppress" option to suppress a specific warning message.

- 1. Click on the Tasks/Templates tab which is located down the right hand edge of the tool.

- 2. Ensure the *Tasks tab* is active.

- 3. RMB on the Questa Compile task and choose Settings...

- 4. In the resulting dialog, click on the Verilog tab

- 5. Enter -suppress 2167 (including the minus sign) in the Additional Options field and OK the dialog.