# **Platform Express User's Guide**

Software Version 1.1f

Release 1.1f

November 2002

Copyright © Mentor Graphics Corporation 2002. All rights reserved.

This document contains information that is proprietary to Mentor Graphics Corporation. The original recipient of this document may duplicate this document in whole or in part for internal business purposes only, provided that this entire notice appears in all copies. In duplicating any part of this document, the recipient agrees to make every reasonable effort to prevent the unauthorized use and distribution of the proprietary information.

End-User License Agreement Trademark Information This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

The terms and conditions governing the sale and licensing of Mentor Graphics products are set forth in written agreements between Mentor Graphics and its customers. No representation or other affirmation of fact contained in this publication shall be deemed to be a warranty or give rise to any liability of Mentor Graphics whatsoever.

MENTOR GRAPHICS MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OR MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

MENTOR GRAPHICS SHALL NOT BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS PUBLICATION OR THE INFORMATION CONTAINED IN IT, EVEN IF MENTOR GRAPHICS CORPORATION HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

#### **RESTRICTED RIGHTS LEGEND 03/97**

U.S. Government Restricted Rights. The SOFTWARE and documentation have been developed entirely at private expense and are commercial computer software provided with restricted rights. Use, duplication or disclosure by the U.S. Government or a U.S. Government subcontractor is subject to the restrictions set forth in the license agreement provided with the software pursuant to DFARS 227.7202-3(a) or as set forth in subparagraph (c)(1) and (2) of the Commercial Computer Software - Restricted Rights clause at FAR 52.227-19, as applicable.

Contractor/manufacturer is: Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

This is an unpublished work of Mentor Graphics Corporation.

## **Table of Contents**

#### **About this Manual**

| Using the Documentation                 | xiii  |

|-----------------------------------------|-------|

| Using Acrobat                           |       |

| Using JavaHelp                          |       |

| Typographical Conventions               |       |

| Manual Organization                     | xvii  |

| Related Publications                    | xvii  |

| About the Platform Express User's Guide | xviii |

#### **Chapter 1 Introduction to Platform Express**

| Overview1-1                                        |

|----------------------------------------------------|

| About Platform Express1-1                          |

| Understanding the Design and Verification Cycle1-1 |

| Automating the Design Cycle1-2                     |

| Designing with Various Platform Cores1-2           |

| Setting up and Invoking Platform Express1-3        |

| Licensing1-3                                       |

| Defining Environment Variables1-4                  |

| Invoking Platform Express1-5                       |

| Platform Express Quick Tour1-6                     |

| Graphical Design Editor1-7                         |

| Component Browser1-8                               |

| Memory Map Pane1-8                                 |

| Output Pane1-8                                     |

| Clearing the Contents of the Output Pane1-8        |

| Copying the Contents of the Output Pane1-9         |

| Additional User Interface Elements1-9              |

| Menu Bar1-9                                        |

| File Menu1-9                                       |

| Edit Menu1-10                                      |

| Tools Menu1-10                                     |

| Settings Menu1-11                                  |

| Help Menu1-12                                      |

| Button Bar1-12                                     |

| Status Bar                                         | 1-12 |

|----------------------------------------------------|------|

| Size-Configurable Panes                            | 1-13 |

| Understanding the Design Process                   |      |

| Step One: Create the Design                        |      |

| Step Two: Build the Design                         |      |

| Step Three: Invoke the Co-Verification Environment |      |

#### **Chapter 2 Creating Designs**

| Overview                            | 2-1  |

|-------------------------------------|------|

| Before You Begin                    | 2-1  |

| Defining User Preferences           | 2-2  |

| Defining Project Settings           | 2-2  |

| Changing Current Project Settings   | 2-3  |

| Changing Default Project Settings   | 2-3  |

| Creating a New Design               | 2-4  |

| Opening an Existing Design          | 2-9  |

| Using the Design Editor             | 2-9  |

| Working with Componets              | 2-10 |

| Color Coding for Components         | 2-11 |

| Creating Component Instances        | 2-11 |

| Configuring Components              | 2-12 |

| Configuring the Pin Settings        | 2-12 |

| Deleting Components                 | 2-13 |

| Accessing Component Information     | 2-13 |

| Accessing the Details Window        | 2-14 |

| Working with Connectors             | 2-15 |

| Creating Connections                | 2-15 |

| Connecting an Unconnected Component | 2-16 |

| Deleting Connections                | 2-16 |

| Working With Buses                  | 2-16 |

| Bus Views                           | 2-17 |

| Automatic Bus Connections           | 2-18 |

| Changing Bus Connections            | 2-18 |

| Bus Bridges                         | 2-18 |

| Multiple Bus Connections            | 2-19 |

| Master and Slave Components | 2-19 |

|-----------------------------|------|

| Configuring Buses           | 2-19 |

#### **Chapter 3 Building Designs**

| Overview                                    | 3-1  |

|---------------------------------------------|------|

| Before you begin                            | 3-1  |

| Configuring the Build                       | 3-2  |

| Defining all configurable components        | 3-2  |

| Defining configurable components separately | 3-2  |

| Setting Driver Signals                      |      |

| Configuring the Required Drivers            |      |

| Configuring the Decoder Selection           |      |

| Defining the Pin Configuration              |      |

| Pin Configuration Example                   |      |

| Using the Scatter Loader                    |      |

| Adding Execution Regions                    | 3-11 |

| Scatter Loader Data Types                   |      |

| Remapping Address Ranges                    |      |

| Configuring Software Memory                 |      |

| Saving Your Design                          |      |

| Hardware Design Files                       |      |

| Software Design Files                       |      |

| Building your Design                        |      |

#### **Chapter 4 Verifying Designs**

| Overview                           | 4-1 |

|------------------------------------|-----|

| Before you begin                   | 4-1 |

| Invoking a Co-Verification Session |     |

| Using the Co-Verification Session  |     |

| Starting HW/SW Simulators Examples | 4-7 |

#### **Chapter 5 Use Case Example**

| Overview                | 5- | -1 |  |

|-------------------------|----|----|--|

| Set up your environment |    |    |  |

| Invoke Platform Express       |     |

|-------------------------------|-----|

| Begin Your Design             |     |

| Select the Core               |     |

| Add a Memory Component        | 5-3 |

| Save the Design               | 5-7 |

| Design Explanation            |     |

| Build Your Design             | 5-7 |

| Simulate Your Design          | 5-8 |

| Verify Your Design            |     |

| Cycle through the Design Flow | 5-9 |

|                               |     |

#### **Appendix A Directory Structures**

| Overview                                | A-1 |

|-----------------------------------------|-----|

| Platform Express Directory Structure    | A-1 |

| Directory Structure of Generated Design |     |

#### **Appendix B Frequently Asked Questions (FAQs)**

| Overview          | B-1 |

|-------------------|-----|

| Product Questions | B-1 |

| General Usage     |     |

| Error Messages    |     |

|                   |     |

#### **Appendix C Build Log File**

#### **Appendix D Using the Documentation Generator**

| Overview                              | D-1 |

|---------------------------------------|-----|

| About PxDoc                           |     |

| Installing PxDoc                      |     |

| Using PxDoc                           |     |

| To generate documentation with PxDoc: |     |

| Accessing the Generated Documentation |     |

| Location of Generated Files           |     |

|                                       |     |

| Sample of Generated Documentation       | D-5 |

|-----------------------------------------|-----|

| Customizing the Documentation Generator | D-8 |

#### **Appendix E Contacting the SupportCenter**

| North America Support        | E-1 |

|------------------------------|-----|

| International Support        |     |

| Product Licensing Assistance |     |

|                              |     |

#### Glossary

| Address block                   |     |

|---------------------------------|-----|

| Address space                   | 1-3 |

| Bus                             |     |

| Bus Bridge                      |     |

| Component Library               |     |

| Interrupt Controller            | 1-4 |

| Interrupt Service Routine (ISR) | 1-4 |

| Literal Pool                    |     |

| Memory Map                      | 1-4 |

| Scatter Loader                  |     |

| Test Bench                      |     |

|                                 |     |

#### **Trademark Information**

**End-User License Agreement**

# List of Figures (cont.)

| Figure 1. Ja | avaHelp viewer interface                       | XV   |

|--------------|------------------------------------------------|------|

| Figure 1-1.  | Design and Verification Flow                   | 1-3  |

| Figure 1-2.  | Platform Express Interface                     | 1-7  |

| Figure 1-3.  | Platform Express, with Maximized Design Editor | 1-14 |

| Figure 1-4.  | Seamless Co-Verification Environment           | 1-17 |

| Figure 2-1.  | Component Browser                              | 2-6  |

| Figure 2-2.  | Example Core Configuration Dialog Box          | 2-7  |

| Figure 2-3.  | Simple Design with core and peripherals        | 2-9  |

| Figure 2-4.  | Details window                                 | 2-15 |

| Figure 3-1.  | Required Driver Configuration dialog box       | 3-5  |

| Figure 3-2.  | Configure Decoder Selection Dialog Box         | 3-7  |

| Figure 3-3.  | Pin Configuration dialog box                   | 3-9  |

| Figure 3-4.  | Scatter Loader dialog box                      |      |

| Figure 3-5.  | Add Execution Region dialog box                | 3-13 |

| Figure 3-6.  | Sofware Memory Configuration Panel             |      |

| Figure 4-1.  | Seamless CVE Interface                         | 4-3  |

| Figure 4-2.  | XRAY Debugger interface                        | 4-4  |

| Figure 4-3.  | ModelSim interface                             | 4-5  |

| Figure 4-4.  | Wave viewer interface                          | 4-6  |

| Figure D-1.  | PxDoc Dialog Box                               | D-4  |

| Figure D-2.  | Sample Memory Map documentation, Netscape      | D-6  |

| Figure D-3.  | Sample Memory Map Documentation, Java          | D-7  |

# List of Figures (cont.)

# List of Figures (cont.)

# List of Tables (cont.)

| Table 1-1. Invocation Switches                            | 1-5  |

|-----------------------------------------------------------|------|

| Table 1-2. File Menu                                      | 1-9  |

| Table 1-3. Edit Menu                                      | 1-10 |

| Table 1-4. Tools Menu                                     | 1-10 |

| Table 1-5. Settings Menu                                  | 1-11 |

| Table 1-6. Help Menu                                      |      |

| Table 2-1. Project Settings                               | 2-4  |

| Table 3-1. Configuration Dialog Boxes                     | 3-2  |

| Table 3-2. Scatter Loader Data Types                      |      |

| Table A-1. Platform Express Installation                  | A-1  |

| Table A-2. Directory Structure of Platform Express Design | A-4  |

| Table D-1. Generated HTML Filenames                       |      |

|                                                           |      |

# List of Tables (cont.)

# **About this Manual**

The Platform Express User's Guide describes how to use Platform Express to quickly create platform-based designs based on open source or other third-party components. This manual is targeted to hardware and software engineers working in the Electronic Design Automation (EDA) industry. As such, this manual assumes a basic knowledge of System-On-Chip (SoC) embedded-processor electronic designs.

# **Using the Documentation**

To accommodate differences in accessibility, viewing, and printing, the Platform Express User's Guide is delivered in two formats:

- Adobe PDF

- Sun JavaHelp

The technical content in each format is essentially the same. The two formats are provided as alternate delivery mechanisms of the same content.

# **Using Acrobat**

The Adobe PDF format requires the Adobe Acrobat Reader application. The Adobe Acrobat Reader, which is available at no cost, is available at:

http://www.adobe.com/products/acrobat/readermain.html

The PDF version of the User's Guide is available in the /doc directory of your Platform Express installation. The User's Guide in PDF format is ideal for printing because it maintains the page paradigm.

## **Using JavaHelp**

The User's Guide in JavaHelp is easily accessible from the Help menu of the Platform Express user interface. No third-party application is required. The Platform Express online help is ideal for accessing documentation directly from the Platform Express interface, and is customized for online viewing. For better printing results, use the PDF format instead of JavaHelp.

Select **Help > User's Guide** to invoke the JavaHelp viewer and display the first help topic. The viewer window contains two panes: the Content pane and the Navigation pane.

#### Figure 1. JavaHelp viewer interface

Content Pane

Contains topic text. Within the topic text, there may be blue, underlined links that you can click to display related topics.

• Navigation Pane

Provides two tabs: Contents and Search; and four buttons: Back, Next, and two Print buttons.

o Contents Tab

Displays the Table of Contents. In the table of contents, click on a topic title to display that topic's contents in the Content pane. Double-click a folder to display the topic tree.

• Search Tab

Displays the Search tab and invokes the global search tool. Search through the entire User's Guide for an item by entering text in the Find box and pressing Return. The viewer displays titles of all topics containing the item in the Navigation pane. Click on a topic title to display the topic.

o Previous and Next buttons

Cycle forwards and backwards through previously displayed topics in the order in which they were displayed.

• Print buttons: Print and Print Setup

The left **Print** button displays a print dialog box for configuring and initiating printing; the right **Print Setup** button sets the page format.

#### **Typographical Conventions**

| Convention                              | Meaning                                                                            | Example                                      |

|-----------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------|

| <i>italic</i> text                      | Indicates a variable or user-<br>supplied argument.                                | -f filename                                  |

| square brackets []                      | Encloses optional commands, parameters, or arguments.                              | filename [ <i>list</i> ]                     |

| menu > menu choice<br>> sub-menu choice | Shows the top-level menu on the main menu, to a menu choice, to a sub-menu choice. | File > Save                                  |

| Bold                                    | Indicates selectable items within<br>the interface, such as menus.                 | In the <b>File</b> menu, select <b>New</b> . |

Screen captures in the *Platform Express User's Guide* reflect the Solaris platform with the Common Desktop Environment (CDE) windowing system. The actual appearance of GUI elements on other platforms may vary.

# **Manual Organization**

The Platform Express User's Guide contains the following topics:

- Introduction to Platform Express

- Creating Designs

- Building Designs

- Verifying Designs

- Use Case Example

- Directory Structures

- Frequently Asked Questions (FAQs)

- Build Log File

- Using the Documentation Generator

- Contacting the SupportCenter

# **Related Publications**

The following Mentor Graphics publications contain information relevant to the usage of Platform Express:

• The *Platform Express Installation Manual* explains how to install Platform Express and how to set up your environment.

- The *Platform Express Release Notes* contain changes and enhancements, as well as caveats specific to Platform Express or its operating environment.

- The *Platform Express Integrator's Guide* is targeted specifically to IP providers for the express purpose of integrating custom core components into the Platform Express interface. End-users creating designs with the provided third-party and open source components do not need the *Integrator's Guide*.

- The *Seamless CVE User's and Reference Manual* contains an overview of the product, explains how to prepare designs for cosimulation, and provides procedures for workstation and design configuration and workstation configuration.

#### About the Platform Express User's Guide

Product Version: 1.1f

Release Date: November 2002

# Chapter 1 Introduction to Platform Express

# **Overview**

This chapter contains conceptual and high-level procedural information on Platform Express. It contains the following sections:

- About Platform Express

- Setting up and Invoking Platform Express

- Platform Express Quick Tour

- Understanding the Design Process

# **About Platform Express**

Platform Express is a software tool for rapidly designing and building complex System-on-Chip (SoC) subsystems based on standard platform cores. As a design tool, Platform Express enables you to select an optimized processor subsystem as the design foundation, and then extend the core functionality by integrating complex IP. Platform Express provides the ability to integrate complex IP by utilizing SoC-standard buses. By providing optimized, prefabricated and configurable design modules, Platform Express enables engineers to concentrate on distinctive design characteristics.

## **Understanding the Design and Verification Cycle**

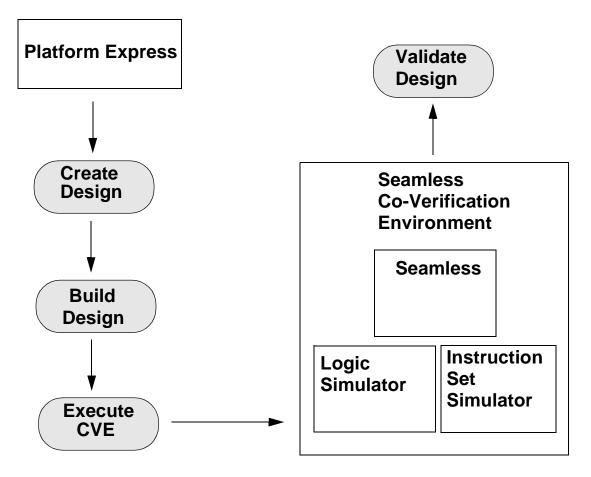

Platform Express is a tool in a design and verification toolset. In addition to Platform Express, Mentor Graphics provides the Seamless Co-Verification Environment (Seamless CVE). Seamless CVE is an environment for hardware and software co-verification, enabling you to validate the hardware/software interfaces. See Figure 1-1 for a graphical representation of the design flow.

The Seamless CVE interface provides access to software debugging tools (for example, XRAY Debugger and Green Hills MULTI), as well as to hardware logic simulation tools (for example, ModelSim and NCSim). Platform Express provides the essential functionality for designing and building complex SoC subsystems, and Seamless CVE provides the interface for design verification.

## Automating the Design Cycle

Platform Express assists the system designer with tools that automate the design cycle. All relevant design elements are presented in detail within the Platform Express interface, accelerating design creation. The Design Editor is context-aware and allows on-the-fly configuration. After the design is created, Platform Express provides tools for automating the build of the design database and tool configuration files. The build files generated by Platform Express are used directly in concert with the Seamless Co-Verification environment. Platform Express provides the following automatic functionality:

- Bus decoding

- Bus bridging

- Interrupt bridging

#### **Designing with Various Platform Cores**

The Platform Express interface provides the flexibility of offering a selection of platform cores (for example, ARM966 and ARM926) to use as the basis of your design. The default Platform Express application ships with a number of libraries (which contain platform core components), and alternate third-party libraries are also available. Many platform cores are provided as "open source," while others are proprietary. (Proprietary components are shipped as simulation models and do not provide sources). For information on creating and implementing libraries, consult the *Platform Express Integrator's Guide*.

Figure 1-1. Design and Verification Flow

# Setting up and Invoking Platform Express

## Licensing

Platform Express utilizes the FlexLM License Manager software. Refer to the *Platform Express Installation Manual* for licensing information.

#### **Defining Environment Variables**

Platform Express is a Java SDK application. In addition to JAVAHOME, Platform Express utilizes environment variables to function properly. The required PXHOME environment variable points to the root directory of the Platform Express installation. Immediately after installing Platform Express, you must manually set the PXHOME environment variable.

Other optional environment variables which are relevant to Platform Express include:

• JAVAHOME

Points to your JRE or Java SDK installation.

PXPATH

Points to your component libraries.

• CVE\_HOME

Points to your Seamless CVE installation.

MODELTECH

Points to your ModelSim installation.

• ARMTOOLS

Points to your ARM build tools, such as the ARM compiler.

For further information on defining your environment to run Platform Express, refer to the *Platform Express Installation Manual*.

Platform Express is validated against specific versions of Seamless CVE. Consult the *Platform Express Release Notes* to ensure you have installed a version of Seamless CVE that has been certified to work with Platform Express.

#### **Invoking Platform Express**

To invoke Platform Express, enter the following:

\$PXHOME/bin/px

For enhanced control of the Platform Express invocation, additional commandline switches are available:

```

$PXHOME/bin/px [-d] [-v] [-l logfilename] [-i] [-G

generatorchain] [[-b|-r] designname]

```

See Table 1-1 for a listing and description of the invocation switches.

| Switch      | Description                                                                                                                                                                                                                           |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -d          | Enables debug message output. Use the -l<br>option to specify output to a log file.<br>Otherwise, the messages appear in the output<br>pane.                                                                                          |

| -v          | Enables additional (verbose) debug<br>messages, including the names of generators<br>as they execute during the build. Use the -1<br>option to specify output to a log file.<br>Otherwise, the messages appear in the output<br>pane. |

| -1          | Creates a log file. A default log file is created<br>(or overwritten) unless a logfilename is<br>specified. The default log file is located in<br>your home directory in .pxrc/pxlogfile.                                             |

| logfilename | Specifies the filename and optional path for debug messages.                                                                                                                                                                          |

| -i          | Ignores generator errors and continues build.<br>If not used, the build stops if an error occurs.                                                                                                                                     |

**Table 1-1. Invocation Switches**

| Switch         | Description                                                                                                            |

|----------------|------------------------------------------------------------------------------------------------------------------------|

| -G             | Invokes Platform Express in batch mode. All required drivers must be specified in the design before using this option. |

| generatorchain | One of Build or Execute.                                                                                               |

| -b             | Automatically builds designname.                                                                                       |

| -r             | Automatically executes a co-verification session on designname.                                                        |

| designname     | The root directory of an existing Platform Express design.                                                             |

Table 1-1. Invocation Switches

# **Platform Express Quick Tour**

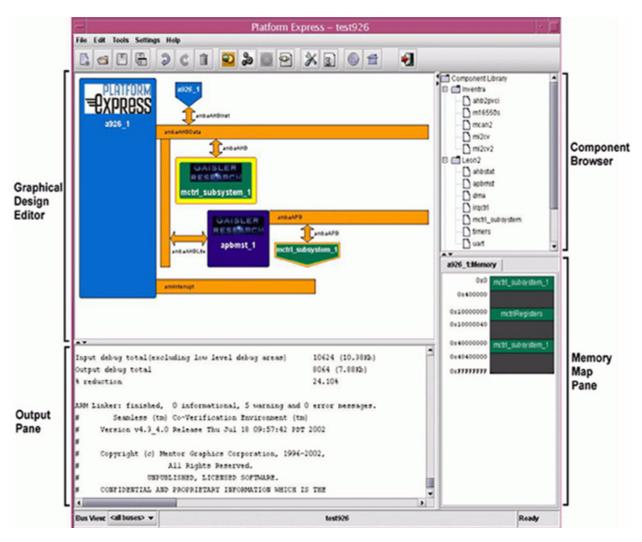

The following is an overview of the Platform Express Graphical User Interface (GUI). In addition to the standard menu bar, tool bar, and status bar of modern application interfaces, the Platform Express interface is composed of four basic elements:

- Graphical Design Editor

- Component Browser

- Memory Map Pane

- Output Pane

#### Figure 1-2. Platform Express Interface

## **Graphical Design Editor**

The Graphical Design Editor enables you to create a block diagram of your design. The components in the design editor are configurable. To configure the components in the design editor, right-click on a component and select the desired configuration.

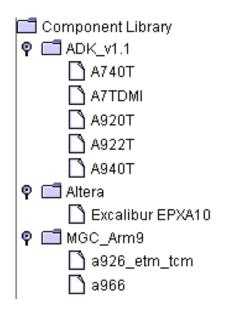

#### **Component Browser**

The component browser lists all the available platform cores. (The available platform cores vary depending on your installed libraries.) Initially, only core platforms are visible. Additional components (such as memory, bus bridges, interrupt controllers, and peripherals) become visible *after* you have selected a core platform and placed it in the Design Editor.

## **Memory Map Pane**

Memory and other peripheral components automatically connect to the appropriate bus on the platform. The memory map pane is a Read-Only pane that displays where a given component fits into the platform address space in relation to other components. The memory map pane displays address locations in hexadecimal format.

#### **Output Pane**

The output pane functions as a standard output display. Build statuses are automatically displayed in the output pane.

The contents of the output pane do not clear automatically when you close the current design.

#### **Clearing the Contents of the Output Pane**

- 1. Right-click within the output pane.

- 2. Select **Clear** from the context menu.

You cannot clear a selection of the output pane. The Clear function deletes the entire contents.

## **Copying the Contents of the Output Pane**

- 1. Select the desired contents in the output pane.

- 2. Right-click within the output pane.

- 3. Select **Copy** from the context menu.

- 4. Paste the contents into a text editor or shell.

#### **Additional User Interface Elements**

In addition to the graphical design editor, component browser, output pane, and memory map pane, there are several common elements in the Platform Express interface:

- Menu Bar

- Button Bar

- Status Bar

#### Menu Bar

The main menu bar is used for creating and saving designs, configuring tool settings, and building and executing finished designs.

#### **File Menu**

| Menu Item | Description                                                                         |

|-----------|-------------------------------------------------------------------------------------|

| New       | Closes current design and creates a new design using your default project settings. |

| Open      | Opens an existing design (*.plx).                                                   |

| Save      | Saves the current design.                                                           |

#### Table 1-2. File Menu

| Save As | Allows you to save the current design with a new name. |

|---------|--------------------------------------------------------|

| Exit    | Exits Platform Express.                                |

#### **Edit Menu**

#### Table 1-3. Edit Menu

| Menu Item | Description                     |

|-----------|---------------------------------|

| Undo      | Undoes the last change.         |

| Redo      | Undoes the last Undo.           |

| Delete    | Deletes the selected component. |

## **Tools Menu**

#### Table 1-4. Tools Menu

| Menu Item | Description                                                        |

|-----------|--------------------------------------------------------------------|

| Build     | Builds the current design, using the specified verification tools. |

| Execute   | Simulates the current design; executes<br>Seamless CVE.            |

| Stop      | Stops the current build.                                           |

Depending on your installed components, you may see additional items on the Tools menu. For example, the Platform Express Documentation Generator (which is an add-on component) is accessible from the Tools menu. See Appendix D, Using the Documentation Generator, for more information.

## **Settings Menu**

| N                   | Description                                                                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Menu Item           | Description                                                                                                                                                                                                                       |

| User<br>Preferences | Configures Platform Express environment settings; does not affect the settings of the current design.                                                                                                                             |

| Project<br>Settings | Configures design-related settings for the current design.                                                                                                                                                                        |

| Save As<br>Default  | Saves the current design settings as the default for all your new designs.                                                                                                                                                        |

| Log Messages        | Configures the level of log message output.<br>The three choices are:                                                                                                                                                             |

|                     | • None: outputs no messages                                                                                                                                                                                                       |

|                     | • Info: sets logmask to "8"                                                                                                                                                                                                       |

|                     | • Debug: sets logmask to "4"                                                                                                                                                                                                      |

|                     | The logmask is a filter setting that defines<br>which types of messages are displayed. The<br>"8" logmask displays informational messages<br>only. The "4" logmask displays the most in-<br>depth messages, useful for debugging. |

| Configure All       | Configures all design-related settings for the current design. This dialog box enables you to configure <i>all</i> settings of your design from a single location. The three top-level settings are:                              |

|                     | • design                                                                                                                                                                                                                          |

|                     | • component                                                                                                                                                                                                                       |

|                     | • bus                                                                                                                                                                                                                             |

## Help Menu

| Menu Item    | Description                                                      |  |

|--------------|------------------------------------------------------------------|--|

| User's Guide | Invokes JavaHelp and loads the User's Guide.                     |  |

| About        | Displays Platform Express version numbers and legal information. |  |

| Px Web       | Invokes a browser and loads the Platform<br>Express website.     |  |

#### Table 1-6. Help Menu

## **Button Bar**

Contains buttons for managing designs and configuring Platform Express.

## **Status Bar**

The status bar has three active areas, from left to right:

- Bus View menu, which allows the Design Editor to show all buses or only one bus type.

- Displays the current design name.

- Displays one of the following states:

- Ready

- Building

- Executing

The states displayed in the Status Bar are dependent on the generation tool. As the generation tool may vary, the values displayed in the Status bar that reflect the state may vary.

## **Size-Configurable Panes**

The Platform Express interface is configurable. Resize the Design Editor, Component Library, Memory Map, and Output panes by dragging the dotted bars between the panes:

.....

Minimize or restore panes by clicking the arrows in the bar next to the pane(s):

....

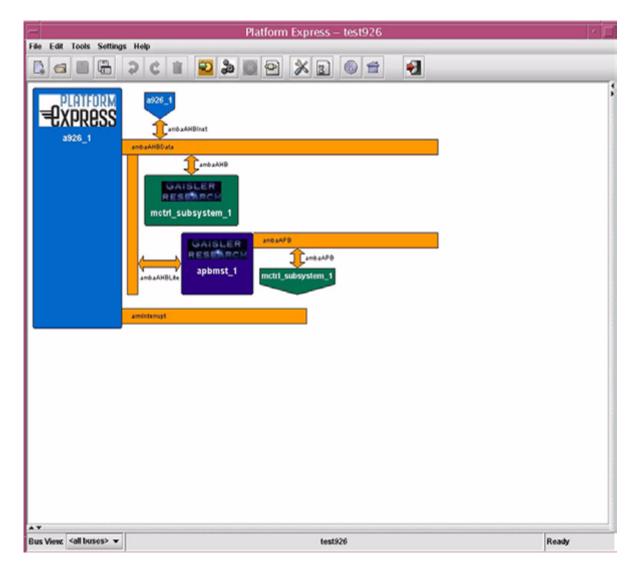

Figure 1-3 depicts the Platform Express interface with the Design Editor expanded (and the Component Library, Memory Map, and Output panes minimized).

Figure 1-3. Platform Express, with Maximized Design Editor

# **Understanding the Design Process**

The platform design cycle consists of three main processes:

- 1. Creating the Design

- 2. Building the Design

- 3. Executing the Co-Verification Environment

#### **Step One: Create the Design**

Platform Express provides a set of platform cores and complex IP as building blocks to create your design. The Component Browser lists your licensed platform cores. After you have selected the desired core platform and moved it to the graphical design editor, the Component Browser automatically lists all the associated memories and peripherals.

- 1. Select the platform core on which to base your design.

- 2. Double-click or drag-and-drop the desired platform core into the design editor.

- 3. Specify addresses and other information in the core's configuration dialog box.

Once the platform is in the design editor, you may begin adding memory and peripheral components to the desired buses. Most components have dialog boxes that allow you to specify addresses and other configuration information.

#### Step Two: Build the Design

Platform Express generates an HDL system design based on the contents of the Design Editor and the component configurations. To initiate the build process, select **Tools > Build** or click the **Build** button on the toolbar. The generated design files include most of the basic requirements of an embedded system design, such as component instantiation and connection within a top-level design, decode logic, and interrupt setup.

#### **Step Three: Invoke the Co-Verification Environment**

Platform Express provides an interface for executing a co-verification environment that invokes Seamless CVE. All the required scripts and configuration files, which are necessary for running the co-verification session, are automatically generated by Platform Express. Use the co-verification environment to verify the design you created and built with Platform Express. To execute the co-verification session, select **Tools > Execute** or click the **Execute** button on the toolbar. When you invoke a co-verification session, the following applications are automatically loaded:

- Seamless CVE

- Logic simulator interface (for example, ModelSim)

- Wave viewer

In addition, log windows also appear. Depending on your environment, you may have to issue additional commands to invoke the Instruction Set Simulator (ISS). For example, to invoke the XRAY Debugger ISS, enter the following command at the ModelSim command prompt:

run -all

Platform Express relies on environmental settings to invoke Seamless CVE. Ensure that you have set all the required environment variables to properly execute a co-verification session. For more detailed information, consult the *Platform Express Installation Manual*.

| wave – default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ele Edit Cursor Zoom Compare France France ModelSim SE PLUS 5.5f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Eile Edit Design View Project Bun Compare Macro Options Window Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 📕 top_anbaapb_1_pr U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre>incorrect address decoding<br/>. Time: 0 ns Iteration: 1 Instance: /pxdestbench/top_1/<br/>pxdecoder_ambaahb_1<br/>. "Warning: NUMERIC_STD."&gt;=": metavalue detected, r<br/>eturning FALSE<br/>. Time: 0 ns Iteration: 1 Instance: /pxdestbench/top_1/<br/>pxdecoder_ambaahb_1<br/>. "Warning: NUMERIC_STD."&gt;=": metavalue detected, r<br/>eturning FALSE<br/>. Time: 0 ns Iteration: 1 Instance: /pxdestbench/top_1/<br/>pxdecoder_ambaahb_1<br/>. "Werning: NUMERIC_STD."&gt;=": metavalue detected, r<br/>eturning FALSE<br/>. Time: 0 ns Iteration: 1 Instance: /pxdestbench/top_1/<br/>pxdecoder_ambaahb_1<br/>. CVE NOTE: Instance '/pxdestbench/top_1/a926_1/uarm<br/>926ejs" waiting for connection from software process<br/>. CVE NOTE: Instance '/pxdestbench/top_1/a926_1/uarm<br/>926ejs" connected to software process<br/>. Time: 0 ns Delta: 3<br/></pre>                                                    |

| Go Step Next StepI NextI GoRtn Stop Up Down Cancel Conn+ HW-Step<br>HW-Next HW-StepI HW-NextI HW-Go HW-Break                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Import interrupt_handler           15         IMPORT IImage\$\$R0\$\$Basel ; Start of ROM           16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17 <u>B Reset_Handler</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Elle Setur Octimice Man Profession -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Eile     Setup     Optimize     View     Preference     Help       General Setup     CPU Setup     Optimization     Run       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup     Image: Setup     Image: Setup     Image: Setup       Image: Setup     Image: Setup |

| Name Proc Type Address : e/componentLibrary/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| pxtestbench.top_1.a926_1.uARM926EJS arm926ejs_rev0 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| cve>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Figure 1-4. Seamless Co-Verification Environment

# **Chapter 2 Creating Designs**

### **Overview**

This chapter contains procedural and conceptual information on creating a design with Platform Express. It contains the following sections:

- Before You Begin

- Creating a New Design

- Using the Design Editor

# **Before You Begin**

This chapter assumes you have properly installed Platform Express (including libraries), and have configured your environment to run Seamless CVE. Check that you have defined the following environement variables: PXHOME, PXPATH, CVE\_HOME, MODELTECH (for ModelSim logic simulation), and ARMTOOLS (if you are using ARM tools). Consult the *Platform Express Installation Manual* for complete instructions.

#### **Defining User Preferences**

Before creating your first design, check your user preferences. User preference settings affect the operation of Platform Express. (All of your designs use the same user preferences.)

To configure user preferences, select **Settings** > **User Preferences**:

Browser Command

The Browser Command is the system command for invoking an Internet browser (such as Netscape), directly from within the Platform Express interface. (To invoke the browser, right-click a component in the Design Editor, select Browse, and then select a menu choice.) The direct browser access enables you to view information and documentation provided by third-party core vendors.

To define a browser, enter the full path to the browser and all command parameters, including an embedded URL tag (\$url). The URLs from the component configuration files will be inserted when the browser is invoked.

#### **Defining Project Settings**

Before creating your first design, check your project settings. When you invoke Platform Express, it creates a directory named .pxrc in your home directory (if .pxrc does not already exist). Your default project settings are stored in the .pxrc directory. Platform Express applies your default project settings to all new projects. (The words *project* and *design* are used interchangeably.)

A warning appears if the .pxrc directory does not exist:

```

[WARN] - Error opening settings file

"/user/michael/.pxrc/preferences.xml"

/user/michael/.pxrc/preferences.xml (No such

file or directory)

[WARN] - Error opening settings file

"/user/michael/.pxrc/projectSettings.xml"

/user/michael/.pxrc/projectSettings.xml (No such

file or directory)

```

### **Changing Current Project Settings**

- 1. Select **Settings** > **Project Settings**.

- 2. In the Edit Properties dialog box, enter the desired settings.

- 3. Click OK.

The new project settings are stored in the project directory when you save your design.

#### **Changing Default Project Settings**

- 1. Select **Settings** > **Project Settings**.

- 2. In the Edit Properties dialog box, enter the desired settings.

- 3. Click OK.

- 4. Select **Settings > Save As Default**.

The design settings are listed in Table 2-1.

| Setting Name                           | Description                                                                 | Default  |

|----------------------------------------|-----------------------------------------------------------------------------|----------|

| HDL Top Module<br>Name                 | Name of HDL top module.                                                     | top      |

| HDL Language                           | One of: VHDL, Verilog.                                                      | VHDL     |

| Clock Period                           | Period, in nanoseconds, for one-shot or clock signals that require drivers. | 40 ns    |

| Clock Pulse Offset                     | Pulse offset, in nanoseconds, for clock signals that require drivers.       | 10 ns    |

| Clock Pulse Value                      | Pulse value for clock signals that require drivers.                         | 0        |

| Clock Pulse<br>Duration                | Pulse duration, in nanoseconds, for clock signals that require drivers.     | 20 ns    |

| Reset Offset                           | In nanoseconds.                                                             | 40 ns    |

| Reset Assertion<br>Value               | Reset assertion value.                                                      | 0        |

| Current<br>Verification<br>Environment | Used by <b>Tools</b> > <b>Build</b> . ModelSim or NCSim.                    | ModelSim |

Table 2-1. Project Settings

## **Creating a New Design**

To create a design with Platform Express, you use three areas of the interface:

• Graphical Design Editor

Create, view, and save your design, starting from a new or existing design.

• Component Browser

Select the components for your design.

• Memory Map Pane

Displays how the components map into your design's memory space. The memory map refreshes when components are added or component configurations are modified. The memory map is "Read-Only"; you cannot edit it directly.

If a design is already open, select **File** > **New** or click the **New** button. This step clears the Design Editor and allows you to create a new design. Platform Express applies the default design settings to all new designs.

- 1. Browse the available core platforms from the list of components in the component browser.

- 2. Double-click the desired core or click-and-drag the component to the design editor.

#### Figure 2-1. Component Browser

3. Enter your selections in the provided core configuration dialog box.

See Figure 2-2 for a sample configuration dialog box based on the ARM926 core.

4. Click OK.

The fields in the core configuration dialog boxes vary depending on the selected core.

| a926_1 Basic Con           | figuration – Basic          |  |

|----------------------------|-----------------------------|--|

| Boot Output Name           | a926.x                      |  |

| compiler                   | armcc                       |  |

| compilerFlags              | -c-g-I\${PXVAR_COMP         |  |

| assembler                  | armasm                      |  |

| assemblerFlags             | -g-I\${PXVAR_COMPON         |  |

| linker                     | armlink                     |  |

| linkerFlags                | -Xref -elf -map -info total |  |

| Linker Command File Name   | linkerCommandFile           |  |

| Linker Command Line Switch | -scatter                    |  |

| Enable Linker Command File | <b>V</b>                    |  |

| Current Model              | Modelsim VHDL 🛛 👻           |  |

| Modelsim Pli Libraries     | \${CVE_HOME}/lib/arm9:      |  |

| Ncsim Pli Build Command    | make -f \${CVE_HOME}/r      |  |

| Boot source file           | software/boot/init.s        |  |

| Boot source file           | software/boot/reset_vect    |  |

| Boot source file           | software/boot/interrupt_r   |  |

| ок                         | Cancel                      |  |

#### Figure 2-2. Example Core Configuration Dialog Box

When the dialog box closes, the core appears in the design editor.

5. Add memory and peripheral components to the buses.

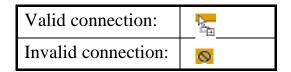

Drag components from the component browser into the Design Editor. As you drag the component over the buses, the cursor changes to indicate a valid or invalid connection.

If you drop the component while a bus is highlighted, the component attaches to that bus. If you drop a component while no bus is highlighted, Platform Express makes the required connections by default.

1. If prompted with a dialog box, specify the component's Base Address or other configuration settings and click OK.

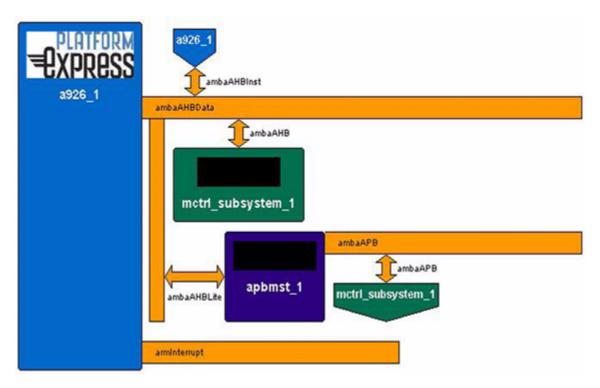

When you close the dialog box, the component automatically connects to the selected bus on the platform. Figure 2-3 shows a simple design in the Design Editor.

### **Opening an Existing Design**

- 1. Select **File** > **Open**.

- 2. Navigate to the desired design (a file with the \*.plx extension).

You can also open a design from a shell by invoking Platform Express with a specified design (\*.plx). For more information on invocation switches, refer to Table 1-1.

# **Using the Design Editor**

The Design Editor pane is the working space for creating and manipulating your design. You can add and configure components and buses in the Design Editor. Figure 2-3 shows a basic design in the Design Editor. After you have placed components into the Design Editor, you can right-click on the components and buses for further configuration.

The Design Editor enables you to build a design with the following building blocks:

- Components

- Connectors

- Buses

The Design Editor does not allow:

- Repositioning of components, except when moving them to a new bus

- Re-routing of connections

#### **Working with Componets**

The Platform Express Component Browser displays a list of components containing platform cores, memories, and peripherals. (Refer to the Component Browser to browse the available cores for your design.) The components in the Component Browser are essentially the building blocks of your design. These components have bus interfaces. The bus interfaces connect to buses. The connections to buses are represented by connectors.

When you begin a design, only platform cores are visible in the Component Browser. Once a platform has been placed in the Design Editor, additional components appear in the Component Browser, and you can begin adding memory and peripheral components and buses. Only those components that can be connected to the currently available buses appear in the Component Browser. Components can be connected directly or through bus bridges.

Besides adding components, you may need to configure components, including master and slave components, or add bus bridges to adapt the components to the buses in the design.

#### **Color Coding for Components**

Color-coding of the cores, memories and peripherals is provided as a means for distinguishing them. Platform cores are blue. Any component that provides a bus bridge is displayed in one of eight shades of purple. All other components are assigned one of eight shades of green. Buses and connectors in the Design Editor are displayed in yellow.

#### **Creating Component Instances**

The available platform cores listed in the Component Browser vary depending on your installed libraries. If you do not see components which you believe are installed, check your PXPATH environment variable.

Insert a component into the Design Editor in one of the following ways:

- Double-click the component name in the Component Browser.

- Right-click on the component name in the Component Browser and select **Add** from the context menu.

- Select the component and drag it to the Design Editor.

Memory and peripheral components automatically connect to the appropriate bus on the core. All other connections designated as required in the component's definition file are made, such as clock and interrupt connections. If the component has connections that are not required, those connections are not made automatically.

The memory map is automatically updated when you add a component to a core. It shows where the component fits into the core address space in relation to the other components.

### **Configuring Components**

Most components have dialog boxes that appear automatically when you place a component in the Design Editor. The configuration dialog box allows you to specify addresses and other parameters. These parameters are described and defined in the component data sheets available from the component vendor or on the component vendor's website. (To go to a component vendor's website, right-click on the component and select an entry under the Browse menu.)

- 1. In the Design Editor, select the desired component.

- 2. Right-click on the component and select **Configure** > **Basics** from the context menu.

- 3. Enter the desired parameters, based on data sheets provided by the vendor.

- 4. Click OK.

#### **Configuring the Pin Settings**

- 1. In the Design Editor, select the desired component.

- 2. Right-click on the component and select **Configure** > **Pins** from the context menu.

- 3. Select pins to export to the test bench.

- 4. Click OK.

Unconnected pins are not automatically connected or exported to the test bench. Pin names for pins that may be exported are displayed in bold.

Setting values for required drivers overwrites default values only if the driver is connected to the pin.

### **Deleting Components**

You can delete a component by selecting the desired component and performing one of the following actions:

- Press the Del key on your keyboard.

- Select **Edit > Delete**.

- Right-click and select **Delete** from the context menu.

- Click the **Delete** button on the toolbar.

When you delete a component with a bus, the "delete" action is propagated throughout the design. The component's bus is deleted, which then deletes all the connections associated with the bus, which then deletes all the components that had a required connection to the bus.

#### **Accessing Component Information**

From the Platform Express interface, you can access information about a component directly from the vendor's web site. For example, to access information from the ARM web site:

- 1. Select the desired ARM-based component in the Design Editor.

- 2. Right-click and select **Browse** > + **ARM926EJS Technical Refenence Manual** from the context menu.

Platform Express invokes a browser and loades the specified URL.

The exact menu choice of the context menu varies depending on the selected core.

#### Accessing the Details Window

You can also display the Details window that contains information on the selected core. The Details window displays details about the component or bus such as instance names, types, and connections.

- 1. Select the desired component in the Design Editor.

- 2. Right-click and select **Details** from the context menu.

| -                                            | Componen                                      | t Details                                                                     |

|----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|

| Name:<br>Version:<br>Path:<br>Instance Name: |                                               | le/pxLibraries/PxArm9/componentLibrary/                                       |

| Bus Interfaces:                              |                                               |                                                                               |

| Bus Typ<br>Instand<br>Connect                | nce Name:<br>pe:<br>se Name of Connected Bus: | anbaAHBData<br>anbaAHB<br>anbaAHB_1<br>a926_1<br>a926_1<br>a926_1<br>apbmst_1 |

| Bus Typ<br>Instand<br>Connect                | e Name of Connected Bus:                      | a926_1                                                                        |

| Interfa<br>Bus Typ<br>Instand                | ace Name:                                     | armInterrupt<br>armInterrupt                                                  |

|                                              | nvironment Selected: Mo<br>elected: vh        | delsim                                                                        |

| •                                            | Cia                                           | ise                                                                           |

Figure 2-4. Details window

#### **Working with Connectors**

#### **Creating Connections**

When you instantiate a component, Platform Express automatically creates all the required connections. A bus ("Bus A") can be dragged to another compatible bus ("Bus B"). This action removes "Bus A" and inserts a secondary master

connection on "Bus B." The bus interface that was previously represented by "Bus A" becomes connected to "Bus B" and is now represented by a connector.

#### **Connecting an Unconnected Component**

• Drag the component to a bus.

Platform Express automatically selects the component interface to connect to the bus, and displays the bus interface ID next to the connector.

• To change the component interface, right-click the bus interface ID and select the desired bus interface.

(This works *only* if there is more than one available, compatible bus interface. If so, an asterisk appears next to the bus interface ID. It is changed by clicking the interface ID, not the connector.)

#### **Deleting Connections**

When you delete a required connection, the component to which it belongs is automatically deleted. You can delete a connection by selecting the desired connection and performing one of the following actions:

- Press the Del key on your keyboard.

- Select Edit > Delete.

- Right-click and select **Delete** from the context menu.

- Click the **Delete** button on the toolbar.

When you delete a required connection, the component to which it belongs is deleted automatically.

#### **Working With Buses**

A *bus* refers to a path used for transmitting signals from any of several sources to any of several destinations. A *bus bridge* is a component with a master bus

interface and a slave bus interface in which signals arriving on the slave interface are translated into signals on the master interface. This allows slaves connected to the master interface to respond to signals from the master of the bus to which the slave interface is connected.

The Design Editor provides several ways of working with buses:

- Bus Views

- Automatic Bus Connections

- Changing Bus Connections

- Bus Bridges

- Multiple Bus Connections

#### **Bus Views**

The Design Editor displays the bus connections for all components in the design. It provides platform-defined views, which may include:

- All buses (default view)

- System bus only

- Interrupt bus only

- Reset bus only

- Timer bus only

You can switch between the various views using the Bus View menu in the status bar. Depending on the platform characteristics specified by the vendor in the core component's definition file, some buses may only be visible in the "all buses" view.

#### **Automatic Bus Connections**

As the component is dragged over the buses, the cursor changes, indicating where the component can or cannot be attached.

If a component is dropped while a bus is highlighted, the component attaches to that bus. If no bus is highlighted when the component is dropped, Platform Express selects a bus to connect to.

If a component can be connected to more than one available bus, Platform Express automatically connects to one of the buses. Afterwards, you can move the component to a different bus, if desired.

#### **Changing Bus Connections**

To change a component's bus connection, drag the connector (not the component) to the preferred bus.

To make connections to additional buses, drag the component to the preferred bus. If the component has additional connections available for that bus type, it remains connected to the original bus and an additional connection is made to the second bus. If the component does not have any additional connections available for that bus type, it is not moved.

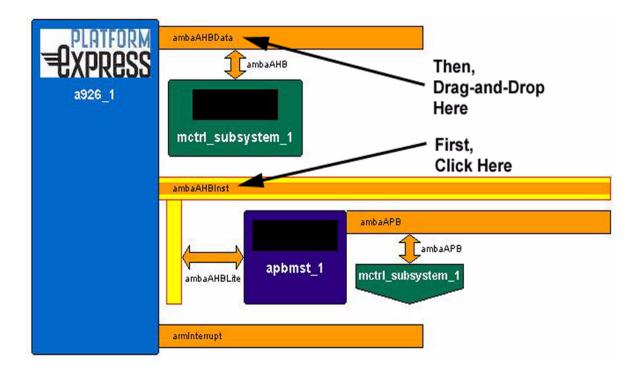

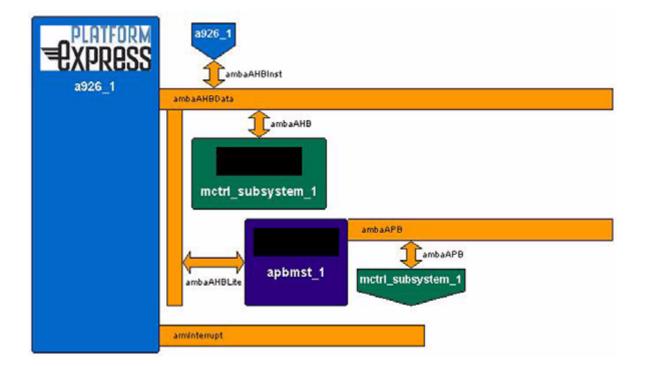

#### **Bus Bridges**

Bus bridges create a bus-to-bus connection that allows components that can only connect to one bus type to connect to a different bus type. Bus bridges are displayed perpendicular to the parent bus, with the extension parallel to the parent bus.

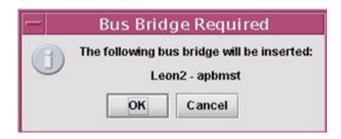

If you add a component that requires a bus bridge to connect to an existing bus, a bus bridge selection dialog box may appear, and a dialog box for configuring the bus bridge may also appear. After the bus bridge is configured, the new bus and the component appear in the Design Editor.

#### **Multiple Bus Connections**

Components with connections to multiple buses (for example, to the system and interrupt buses) are represented once for each bus type. The first representation contain all labels and logos. Subsequent representations are arrow-shaped, with the instance name only. All representations are highlighted if any of them is selected. Components with multiple connections to a single bus show all connections from a single representation.

#### **Master and Slave Components**

Bus interfaces can be masters or slaves. Unconnected master interfaces are represented as buses. Primary bus masters appear as components on the left side of the Design Editor. Secondary bus masters are displayed above the bus. Bus slave components are displayed below the bus. When the maximum number of master or slave components have been added to a bus, an error message appears.

### **Configuring Buses**