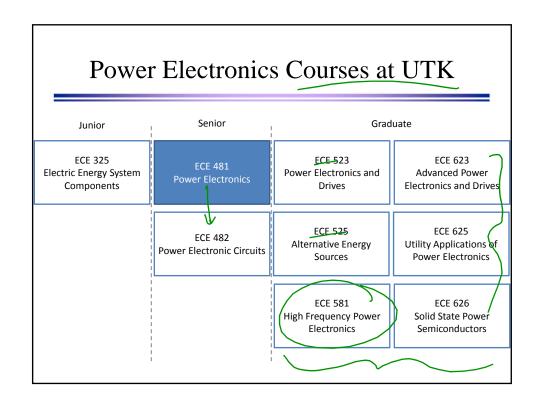

# Lecture 25: Transformer Design; Further Topics

ECE 481: Power Electronics

Prof. Daniel Costinett

Department of Electrical Engineering and Computer Science

University of Tennessee Knoxville

Fall 2013

#### Announcements

- ECE 482: Power Electronic Circuits

- http://oira.tennessee.edu/sais/ (7 students missing)

- Midterm exam:

- Available after class today

- Due anytime before 12:15pm on Wednesday, Dec  $11^{\text{th}}$

IN MK 502

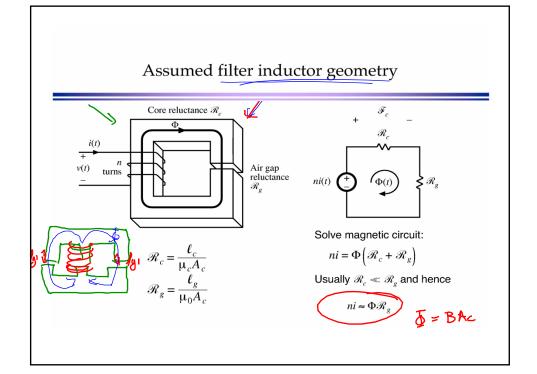

#### Filter inductor, cont.

- Negligible core loss, negligible proximity loss

- Loss dominated by dc copper loss

- ځ

- Flux density chosen simply to avoid saturation

- · Air gap is employed

- Could use core materials having high saturation flux density (and relatively high core loss), even though converter switching frequency is high

#### Chapter 14 Inductor Design

- 14.1 Filter inductor design constraints

- 14.2 A step-by-step design procedure

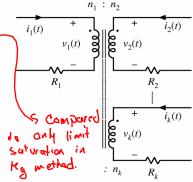

- 14.3 Multiple-winding magnetics design using the  $K_g$  method

- 14.4 Examples

- 14.5 Summary of key points

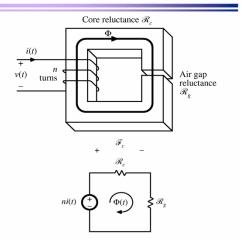

### 14.1 Filter inductor design constraints

i(t) = R

#### Objective:

Design inductor having a given inductance L, which carries worst-case current  $I_{\max}$  without saturating, and which has a given winding resistance R, or, equivalently, exhibits a worst-case copper loss of

$$P_{cu} = I_{rms}^{2} R$$

**Example**: filter inductor in CCM buck converter

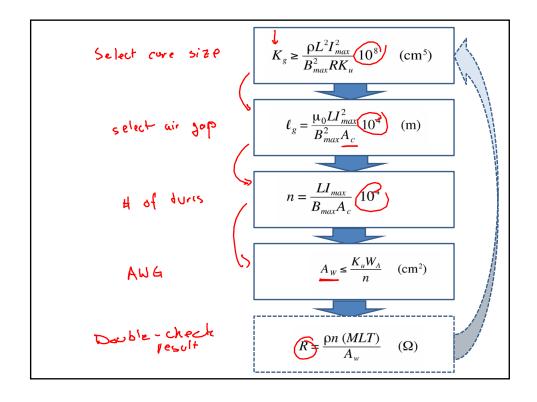

### 14.2 A step-by-step procedure

The following quantities are specified, using the units noted:

Wire resistivity  $\rho$  ( $\Omega$ -cm)

Peak winding current  $I_{max}$  (A)

Inductance L (H)

Winding resistance R ( $\Omega$ )

Winding fill factor  $K_u$ Core maximum flux density  $B_{max}$  (T)

The core dimensions are expressed in cm:

Core cross-sectional area  $A_c$  (cm<sup>2</sup>) Core window area  $W_A$  (cm<sup>2</sup>) Mean length per turn MLT (cm)

The use of centimeters rather than meters requires that appropriate factors be added to the design equations.

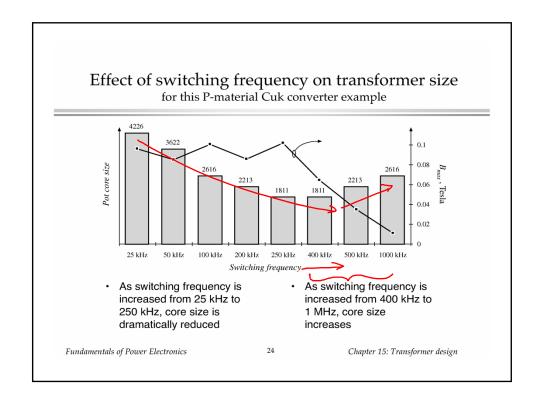

#### Chapter 15 Transformer Design

Some more advanced design issues, not considered in previous chapter:

- Inclusion of core loss

- Selection of operating <u>flux</u> density to optimize total loss

- Multiple winding design: as in the coupled-inductor case, allocate the available window area among several windings

- A transformer design procedure

- How switching frequency affects transformer size

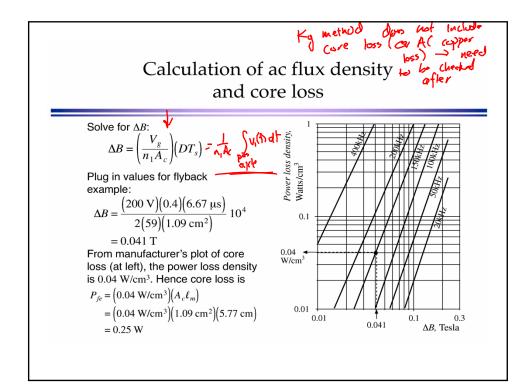

# 15.1 Transformer Design: Basic Constraints

Core loss

$$P_{fe} = K_{fe} (\Delta B)^{\beta} A_c \ell_m$$

Typical value of  $\beta$  for ferrite materials: 2.6 or 2.7

$\Delta B$  is the peak value of the ac component of B(t), *i.e.*, the peak ac flux density

So increasing  $\Delta B$  causes core loss to increase rapidly

This is the first constraint

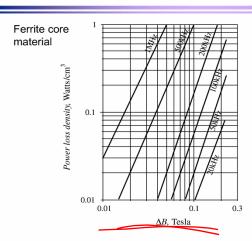

#### Total core loss: manufacturer's data

Empirical equation, at a fixed frequency:

$$P_{fe} = K_{fe} (\Delta B)^{\beta} A_c \ell_m$$

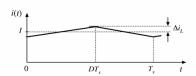

### Flux density

Constraint #2

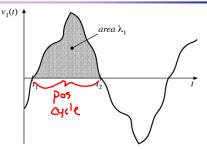

Flux density B(t) is related to the applied winding voltage according to Faraday's Law. Denote the voltseconds applied to the primary winding during the positive portion of  $v_1(t)$  as  $\lambda_1$ :

$$\lambda_1 = \int_{t_1}^{t_2} v_1(t) dt$$

This causes the flux to change from its negative peak to its positive peak. From Faraday's law, the peak value of the ac component of flux density is

$$\Delta B = \frac{\lambda_1}{2n_1 A_c}$$

To attain a given flux density, the primary turns should be chosen according to

$$n_1 = \frac{\lambda_1}{2\Delta B A_c}$$

### Copper loss

Constraint #3

- Allocate window area between windings in optimum manner, as described in previous section

- · Total copper loss is then equal to

$$P_{cu} = \frac{\rho(MLT)n_1^2 I_{tot}^2}{W_A K_u}$$

with

$$I_{tot} = \sum_{j=1}^{k} \frac{n_j}{n_1} I_j$$

Eliminate  $n_1$ , using result of previous slide:

$$P_{cu} = \left(\frac{\rho \lambda_1^2 I_{tot}^2}{4K_u}\right) \left(\frac{(MLT)}{W_A A_c^2}\right) \left(\frac{1}{\Delta B}\right)^2$$

Note that copper loss decreases rapidly as  $\Delta B$  is increased

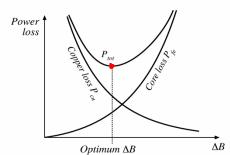

#### Total power loss

$$4. P_{tot} = P_{cu} + P_{fe}$$

There is a value of  $\Delta B$  that minimizes the total power loss

$$P_{tot} = P_{fe} + P_{cu}$$

$$P_{fe} = K_{fe} (\Delta B)^{\beta} A_c \ell_m$$

$$P_{cu} = \left(\frac{\rho \lambda_1^2 I_{tot}^2}{4K_u}\right) \left(\frac{(MLT)}{W_A A_c^2}\right) \left(\frac{1}{\Delta B}\right)^2$$

#### Total loss

Substitute optimum  $\Delta B$  into expressions for  $P_{cu}$  and  $P_{fe}$ . The total loss is:

$$P_{tot} = \left[A_c \ell_m K_{fe}\right]^{\left(\frac{2}{\beta+2}\right)} \left[\frac{\rho \lambda_1^2 I_{tot}^2}{4K_u} \frac{(MLT)}{W_A A_c^2}\right]^{\left(\frac{\beta}{\beta+2}\right)} \left[\left(\frac{\beta}{2}\right)^{-\left(\frac{\beta}{\beta+2}\right)} + \left(\frac{\beta}{2}\right)^{\left(\frac{2}{\beta+2}\right)}\right]$$

Rearrange as follows:

$$\frac{W_{A}\left(A_{c}\right)^{\left(2(\beta-1)/\beta\right)}}{(MLT)\ell_{m}^{\left(2/\beta\right)}}\left[\left(\frac{\beta}{2}\right)^{-\left(\frac{\beta}{\beta+2}\right)}+\left(\frac{\beta}{2}\right)^{\left(\frac{2}{\beta+2}\right)}\right]^{-\left(\frac{\beta+2}{\beta}\right)}=\frac{\rho\lambda_{1}^{2}I_{tot}^{2}K_{fe}^{\left(2/\beta\right)}}{4K_{u}\left(P_{tot}\right)^{\left((\beta+2)/\beta\right)}}$$

Left side: terms depend on core geometry

Right side: terms depend on specifications of the application

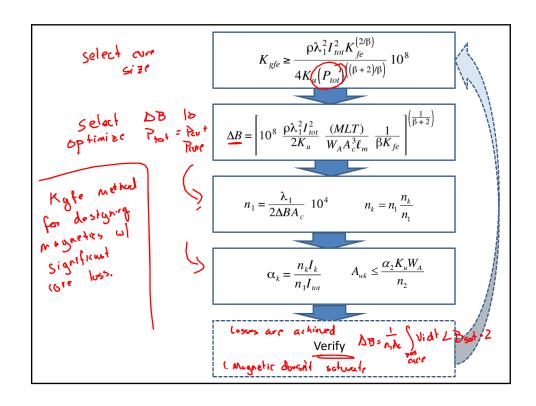

# The core geometrical constant $K_{gfe}$

Define

$$K_{gfe} = \frac{W_A \left(A_c\right)^{\left(2(\beta-1)/\beta\right)}}{(MLT)\ell_m^{\left(2/\beta\right)}} \left[ \left(\frac{\beta}{2}\right)^{-\left(\frac{\beta}{\beta+2}\right)} + \left(\frac{\beta}{2}\right)^{\left(\frac{2}{\beta+2}\right)} \right]^{-\left(\frac{\beta+2}{\beta}\right)}$$

Design procedure: select a core that satisfies

$$K_{gfe} \ge \frac{\rho \lambda_1^2 I_{tot}^2 K_{fe}^{(2/\beta)}}{4K_u (P_{tot})^{((\beta+2)/\beta)}}$$

Appendix D lists the values of  $K_{gfe}$  for common ferrite cores

$K_{g/e}$  is similar to the  $K_g$  geometrical constant used in Chapter 14:

- $K_g$  is used when  $B_{max}$  is specified

- $K_{gfe}$  is used when  $\Delta B$  is to be chosen to minimize total loss

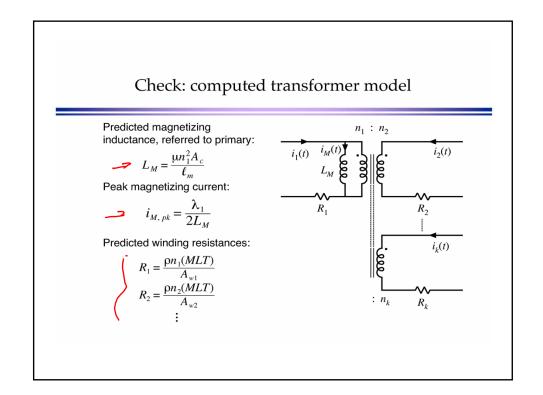

# 15.2 Step-by-step transformer design procedure

The following quantities are specified, using the units noted: Wire effective resistivity  $\rho \qquad \qquad (\Omega\text{-cm})$

Total rms winding current, ref to pri  $I_{tot}$  (A) Desired turns ratios  $n_2/n_1, n_3/n_1$ , etc.

Applied pri volt-sec  $\lambda_1$  (V-sec) Allowed total power dissipation  $P_{tot}$  (W)

Winding fill factor  $K_u$ Core loss exponent  $\beta$

Core loss coefficient  $K_{f_{\alpha}}$  (W/cm<sup>3</sup>T<sup> $\beta$ </sup>)

Other quantities and their dimensions:

Peak ac flux density

(T)

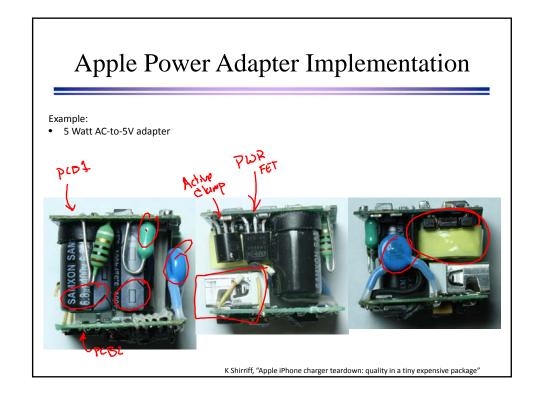

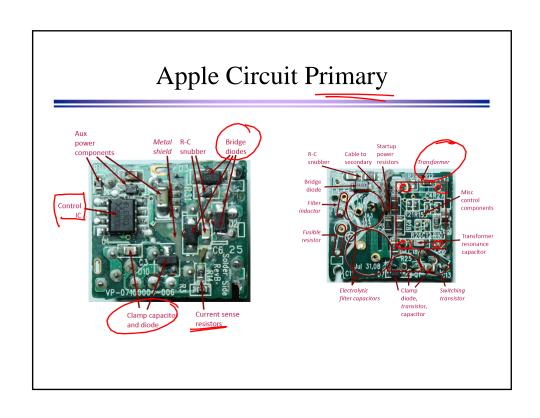

# Application of ECE481 Theory

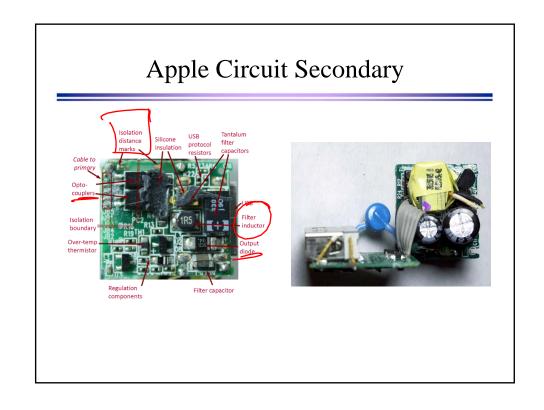

### Example: Low-Power AC Adapters

Apple "Ultracompact USB Power Adapter"

#### **Design Constraints:**

- Single converter needs power stage which can operate over wide input voltage range

- For V<sub>dc</sub> = +5 V (USB output) need very large step-down capability (M = 0.018)

- Isolation may be necessary for safety

#### Goals:

- Produce regulated DC Voltage from universal input (85 to 276 Vrms, 47-63 Hz)

- Maintain high power factor / Low EMI

- High efficiency to allow small size

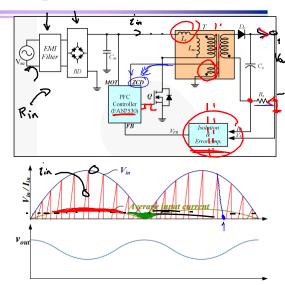

Fairchild Semi, "Design Guideline of Single-Stage Flyback AC-DC Converter Using FAN7530 for LFD Lighting"

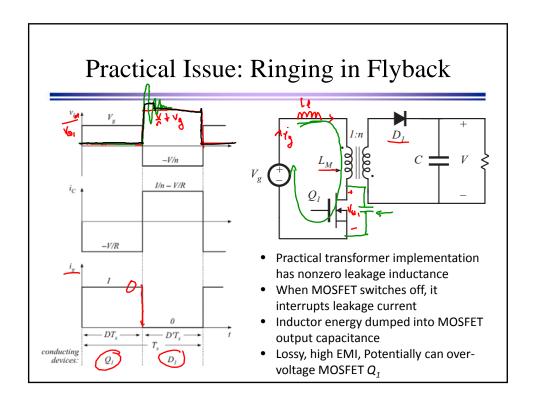

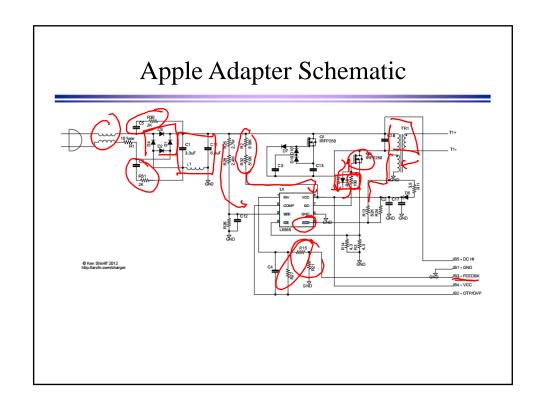

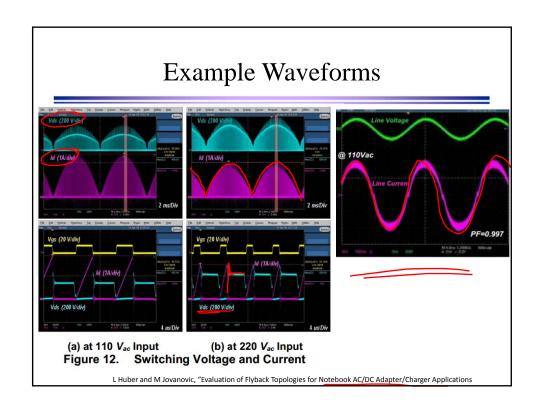

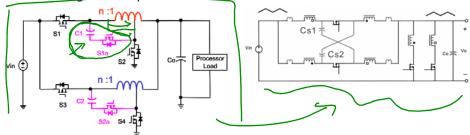

### Flyback Implementation

- Flyback selected as a simple, low part-count topology

- Used almost exclusively in Ac-to-LVDC applications at power levels less than 100W

- DCM may be used for reduced diode RR and increased f<sub>s</sub>

- Pulsating input current requires filtering

- If unity power factor is obtained, significant output ripple results

Fairchild Semi, "Design Guideline of Single-Stage Flyback AC-DC Converter Using

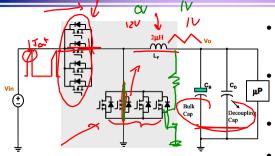

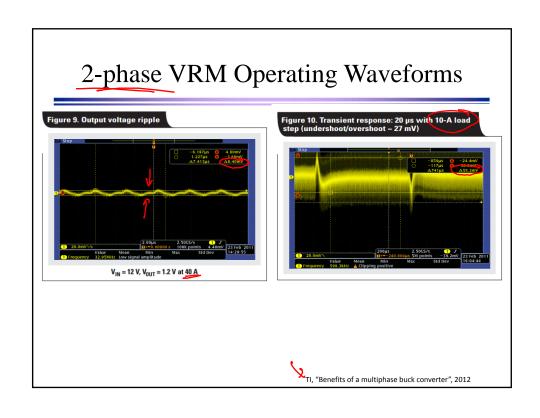

# Example 2: VRM Design

#### Goals:

- Produce tightly regulated <u>0.8-1.4 V</u> output voltage from 12 V +5%/-8%

- Maintain very strict regulation

#### **Design Constraints:**

- < 10mV ripple (pk-to-pk)</li>

- < 50mV deviation at full load current step

- 120 A/ns\_output current slew rate

- 150 A peak output current

- Regulation down to 500mA

- Voltage variation in 6.25 mV steps

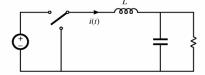

### Traditional Approach: High-Current Buck Converter

- Fig. 1.6. A single-phase buck converter for a Pentium III processor.

- Buck is simplest topology which can meet required step-down

- Multiple devices in parallel used to reduce (dominant) conduction losses

- Large inductor needed to reduce ripple

- Large output cap needed for ripple; transient hold-up

- Switching frequency increased to reduce ripple; still well-below processor speed

K Yao, "High-Frequency and High-Performance VRM Design for the Next Generations of Processors", 2004

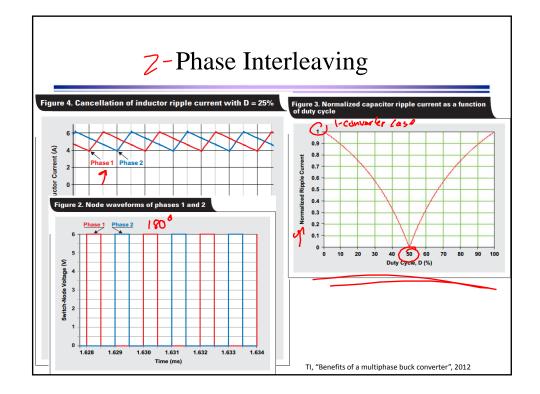

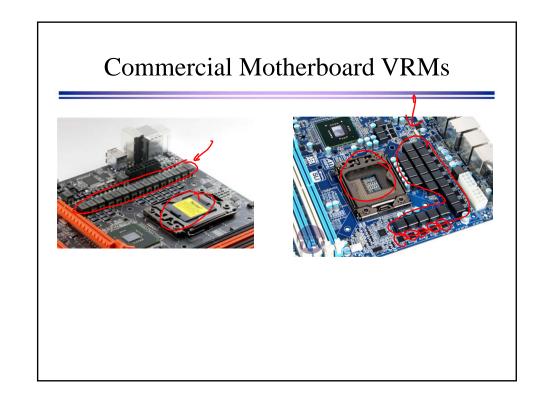

# Today's Approach: Multiphase Buck

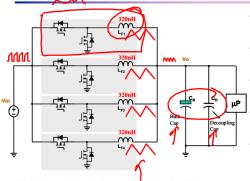

Fig. 1.7. A multiphase buck converter for a Pentium III processor.

- Multiphase to distribute the large output current

- Interleaving to cancel current ripple and to improve transient response

- 12V-input voltage bus to reduce the input bus conduction loss

- Multiphase controller with switching frequency up to 1 MHz

- Commonly, 300KHz to 500KHz switching frequency to achieve reasonable efficiency with 30V vertical trench MOSFETs

- Several electrolytic bulk capacitors in parallel to limit the transient voltage spikes; ceramics in parallel for HF

K Yao, "High-Frequency and High-Performance VRM Design for the Next Generations of Processors", 2004

### Issues:

- Small duty cycles  $(D \sim 1/12)$  cause poor device utilization

- Large size due to many phases despite high switching frequency

- $C_{out}$  limited by holdup times (large signal); further increase in  $f_s$  not beneficial

- Noneven slew rates:

$$\Delta I_{\text{max}} = \frac{12 - V_{out}}{L} \qquad \Delta I_{\text{min}} = \frac{-V_{out}}{L}$$

Balancing between phases needs to be enforced via control

Fig. 9. Multiphase tapped-inductor buck converter with an additional active

P Xu, J Wei, and F Lee, "Multiphase Coupled-Buck Converter—A Novel High Efficient 12 V Voltage Regulator Module"

Further Topics In Power Electronics

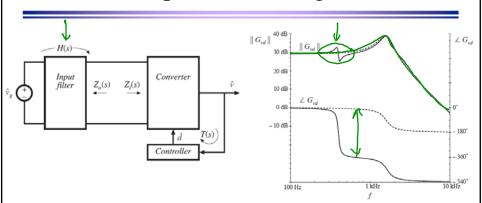

# Input Filter Design

- · Filter can seriously degrade converter control system behavior

- Use extra element theorem to derive conditions which ensure that converter dynamics are not affected by input filter

- · Must design input filter having adequate damping

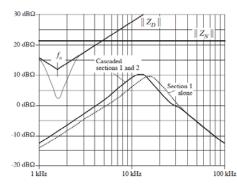

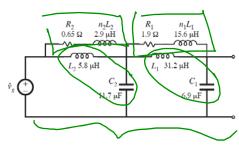

# **Damped Input Filters**

# Design criteria derived via Extra Element theorem:

Two-section damped input filter design:

$$\left\| Z(j\omega) \right\| \gg \left\| Z_N(j\omega) \right\|$$

$$\left\| Z(j\omega) \right\| \gg \left\| Z_D(j\omega) \right\|$$

Thank you for a Great Semester Good Luck with Finals!