## Lecture 9: Isolated Converters

ECE 481: Power Electronics Prof. Daniel Costinett

Department of Electrical Engineering and Computer Science

University of Tennessee Knoxville

Fall 2013

## Announcements

- Midterm exam begins at the end of class today

- Turn in Thursday, 10/3

- You may use extra sheets

## Midterm Exam #1

Fall 2013 ECE 481: Power Electronics

Instructions: This is a one-week take-home exam. It is an open-book, open-note, but absolutely no collaboration is allowed. You may not use internet resources other than the course website and contained materials. Show all work, partial credit will be given. When you have completed the exam, sign the University of Tennessee Knoxville Honor Statement below:

As a student of the University, I pledge that I have neither knowingly given nor received any inappropriate assistance in this academic work, thus affirming my own personal commitment to honor and integrity

Signature:

This exam is due at the beginning of class, 11:10am, Thursday October  $3^{\rm rd}$ . The exam contains three problems.

#### Discussion: Flyback converter

- Widely used in low power and/or high voltage applications

- · Low parts count

- . Multiple outputs are easily obtained, with minimum additional parts

- Cross regulation is inferior to buck-derived isolated converters

- · Often operated in discontinuous conduction mode

- . DCM analysis: DCM buck-boost with turns ratio

Fundamentals of Power Electronics

63

Chapter 6: Converter circuits

## 6.4. Converter evaluation and design

For a given application, which converter topology is best?

There is no ultimate converter, perfectly suited for all possible applications

Trade studies

- Rough designs of several converter topologies to meet the given specifications

- An unbiased quantitative comparison of worst-case transistor currents and voltages, transformer size, etc.

Comparison via switch stress, switch utilization, and semiconductor cost

Spreadsheet design

Fundamentals of Power Electronics

77

#### 6.4.1. Switch stress and switch utilization

- Largest single cost in a converter is usually the cost of the active semiconductor devices

- Conduction and switching losses associated with the active semiconductor devices often dominate the other sources of loss

This suggests evaluating candidate converter approaches by comparing the voltage and current stresses imposed on the active semiconductor devices.

Minimization of total switch stresses leads to reduced loss, and to minimization of the total silicon area required to realize the power devices of the converter.

Fundamentals of Power Electronics

78

Chapter 6: Converter circuits

#### Total active switch stress S

In a converter having  $\boldsymbol{k}$  active semiconductor devices, the total active switch stress  $\boldsymbol{S}$  is defined as

$$S = \sum_{j=1}^{k} V_j I_j$$

where

$V_j$  is the peak voltage applied to switch j,

$I_{j}$  is the rms current applied to switch j (peak current is also sometimes used).

In a good design, the total active switch stress is minimized.

Fundamentals of Power Electronics

79

#### Active switch utilization *U*

It is desired to minimize the total active switch stress, while maximizing the output power  $P_{load}$ .

The active switch utilization U is defined as

$$U = \frac{P_{load}}{S}$$

The active switch utilization is the converter output power obtained per unit of active switch stress. It is a converter figure-of-merit, which measures how well a converter utilizes its semiconductor devices.

Active switch utilization is less than 1 in transformer-isolated converters, and is a quantity to be maximized.

Converters having low switch utilizations require extra active silicon area, and operate with relatively low efficiency.

Active switch utilization is a function of converter operating point.

Fundamentals of Power Electronics

80

Chapter 6: Converter circuits

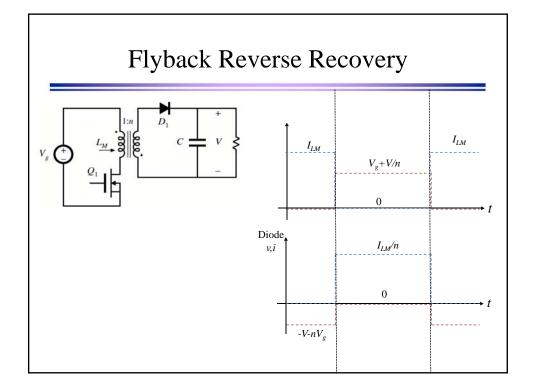

## CCM flyback example: Determination of S

During subinterval 2, the transistor blocks voltage  $V_{Ql,\rho k}$  equal to  $V_g$  plus the reflected load voltage:

$$V_{Q1,pk} = V_g + \frac{V}{n} = \frac{V_g}{D'}$$

Transistor current coincides with  $i_g(t)$ . RMS value is

$$I_{Q1,rms} = I\sqrt{D} = \frac{P_{load}}{V_g\sqrt{D}}$$

Switch stress S is

$$S = V_{Q1,pk} \, I_{Q1,rms} = \left(V_g + \frac{V}{n}\right) \left(I \, \sqrt{D}\right)$$

$V_{g} \stackrel{\longrightarrow}{\longleftarrow} L_{M} \stackrel{\longrightarrow}{\longrightarrow} C \stackrel{\longrightarrow}{\longleftarrow} V \stackrel{\longrightarrow}{\longrightarrow} I$

Fundamentals of Power Electronics

81

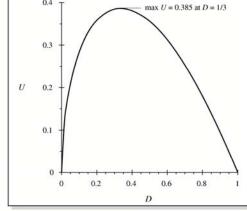

## CCM flyback example: Determination of $\boldsymbol{U}$

Express load power  $P_{load}$  in terms of V and I:

$$P_{load} = D'V\frac{I}{n}$$

Previously-derived expression for S:

$$S = V_{Q1,pk} I_{Q1,rms} = \left(V_g + \frac{V}{n}\right) \left(I \sqrt{D}\right)$$

Hence switch utilization U is

$$U = \frac{P_{load}}{S} = D' \sqrt{D}$$

Fundamentals of Power Electronics

8

Chapter 6: Converter circuits

CCM flyback model

## Flyback example: switch utilization U(D)

For given V,  $V_g$ ,  $P_{load}$ , the designer can arbitrarily choose D. The turns ratio n must then be chosen according to

$$n = \frac{V}{V_g} \frac{D'}{D}$$

Single operating point design: choose D = 1/3.

small D leads to large transistor current

large D leads to large transistor voltage

Fundamentals of Power Electronics

83

# Comparison of switch utilizations of some common converters

Table 6.1. Active switch utilizations of some common dc-dc converters, single operating point.

| Converter                                                                                | U(D)                           | max U(D)                      | $\max_{OCCUPS} U(D)$ |

|------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|----------------------|

| Buck                                                                                     | <b>√</b> D                     | 1                             | 1                    |

| Boost                                                                                    | $\frac{D'}{ID}$                | ∞                             | 0                    |

| Buck-boost, flyback, nonisolated SEPIC, isolated<br>SEPIC, nonisolated Cuk, isolated Cuk | $D' / \overline{D}$            | $\frac{2}{3\sqrt{3}} = 0.385$ | $\frac{1}{3}$        |

| Forward, $n_1 = n_2$                                                                     | $\frac{1}{2}$ / $\overline{D}$ | $\frac{1}{2\sqrt{2}} = 0.353$ | $\frac{1}{2}$        |

| Other isolated buck-derived converters (full-<br>bridge, half-bridge, push-pull)         | $\frac{\sqrt{D}}{2\sqrt{2}}$   | $\frac{1}{2\sqrt{2}} = 0.353$ | 1                    |

| Isolated boost-derived converters (full bridge,<br>push-pull)                            | $\frac{D'}{2\sqrt{1+D}}$       | $\frac{1}{2}$                 | 0                    |

Fundamentals of Power Electronics

84

Chapter 6: Converter circuits

#### Active semiconductor cost vs. switch utilization

$$\begin{pmatrix}

\text{semiconductor cost} \\

\text{per kW output power}

\end{pmatrix} = \frac{\begin{pmatrix}

\text{semiconductor device cost} \\

\text{per rated kVA}

\end{pmatrix}}{\begin{pmatrix}

\text{voltage} \\

\text{derating} \\

\text{factor}

\end{pmatrix} \begin{pmatrix}

\text{current} \\

\text{derating} \\

\text{factor}

\end{pmatrix} \begin{pmatrix}

\text{converter} \\

\text{switch} \\

\text{utilization}

\end{pmatrix}$$

(semiconductor device cost per rated kVA) = cost of device, divided by product of rated blocking voltage and rms current, in  $\$  VA. Typical values are less than 1/kVA

(voltage derating factor) and (current derating factor) are required to obtain reliable operation. Typical derating factors are 0.5 - 0.75

Typical cost of active semiconductor devices in an isolated dc-dc converter: \$1 - \$10 per kW of output power.

Fundamentals of Power Electronics

87

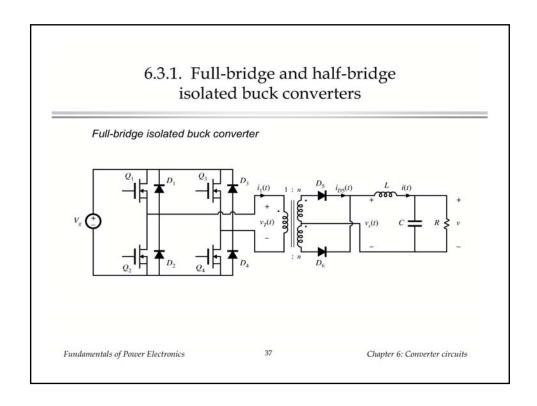

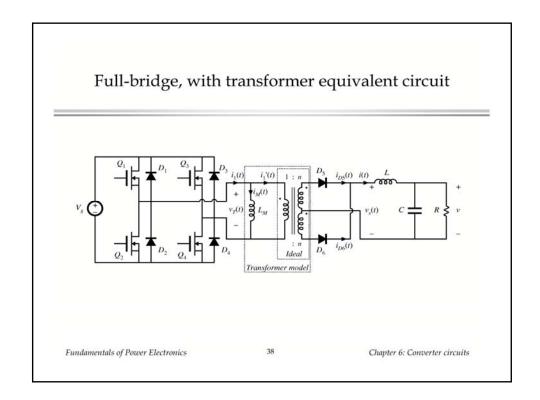

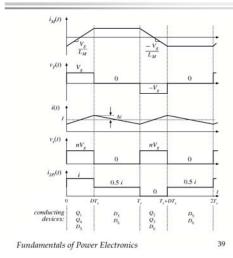

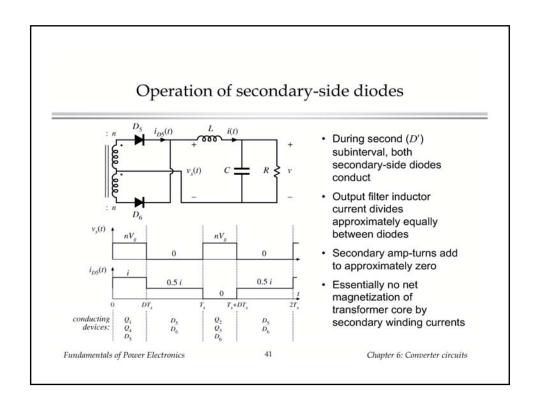

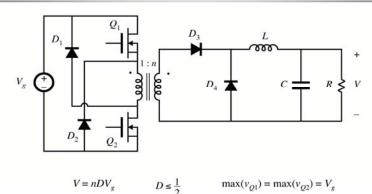

- During first switching period: transistors  $Q_1$  and  $Q_4$  conduct for time  $DT_s$ , applying volt-seconds  $V_g DT_s$  to primary winding

- During next switching period: transistors Q<sub>2</sub> and Q<sub>3</sub> conduct for time DT<sub>s</sub>, applying voltseconds -V<sub>g</sub> DT<sub>s</sub> to primary winding

- Transformer volt-second balance is obtained over two switching periods

- · Effect of nonidealities?

Chapter 6: Converter circuits

## Effect of nonidealities on transformer volt-second balance

Volt-seconds applied to primary winding during first switching period:

$(V_g - (Q_1 \text{ and } Q_4 \text{ forward voltage drops}))(Q_1 \text{ and } Q_4 \text{ conduction time})$

Volt-seconds applied to primary winding during next switching period:

$-(V_g - (Q_2 \text{ and } Q_3 \text{ forward voltage drops)})(Q_2 \text{ and } Q_3 \text{ conduction time})$

These volt-seconds never add to exactly zero.

Net volt-seconds are applied to primary winding

Magnetizing current slowly increases in magnitude

Saturation can be prevented by placing a capacitor in series with primary, or by use of current programmed mode (Chapter 12)

Fundamentals of Power Electronics

## Half-bridge isolated buck converter

- Replace transistors  $\mathcal{Q}_3$  and  $\mathcal{Q}_4$  with large capacitors

- Voltage at capacitor centerpoint is  $0.5 V_{\rm g}$

- $v_s(t)$  is reduced by a factor of two

- $M = 0.5 \ nD$

Fundamentals of Power Electronics

43

Chapter 6: Converter circuits

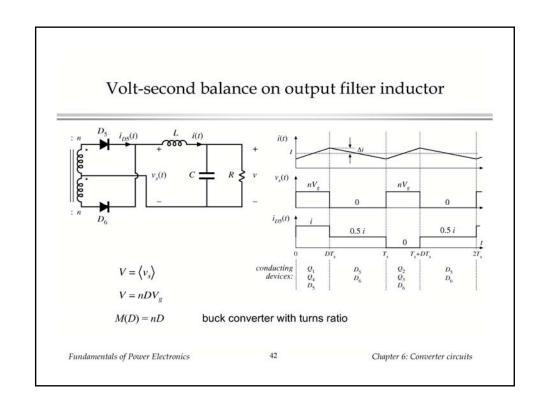

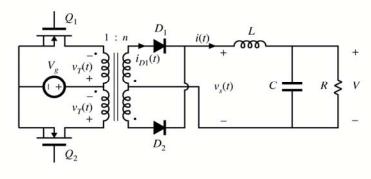

## 6.3.3. Push-pull isolated buck converter

$V = nDV_g \qquad \qquad 0 \le D \le 1$

Fundamentals of Power Electronics

56

- · Used with low-voltage inputs

- Secondary-side circuit identical to full bridge

- As in full bridge, transformer volt-second balance is obtained over two switching periods

- Effect of nonidealities on transformer volt-second balance?

- Current programmed control can be used to mitigate transformer saturation problems. Duty cycle control not recommended.

Chapter 6: Converter circuits

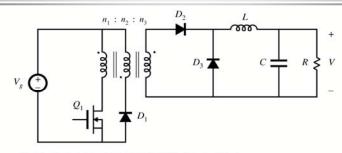

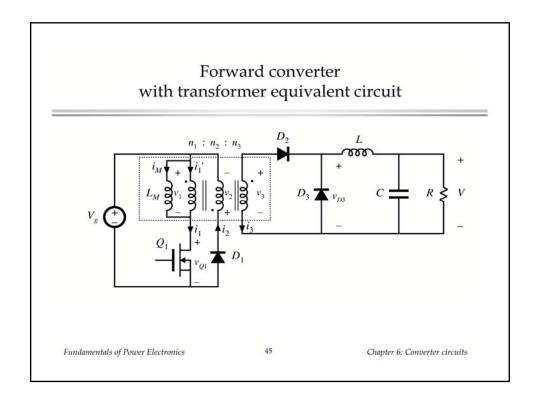

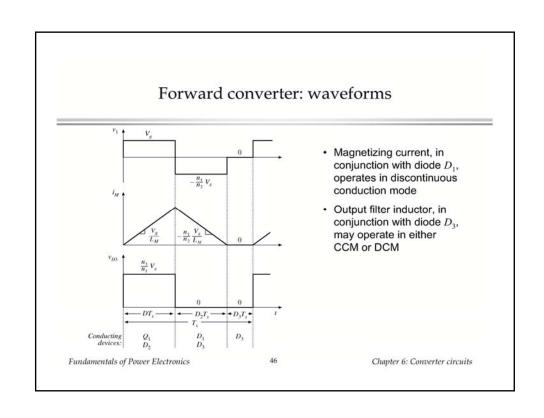

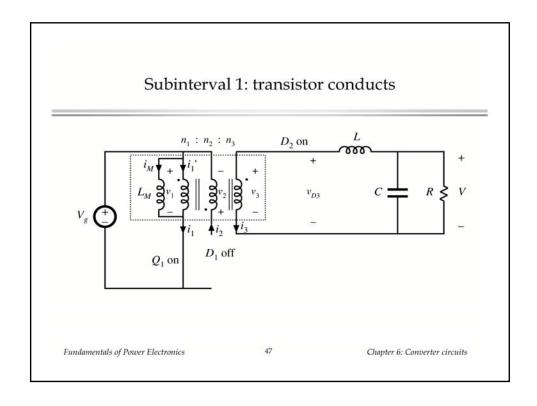

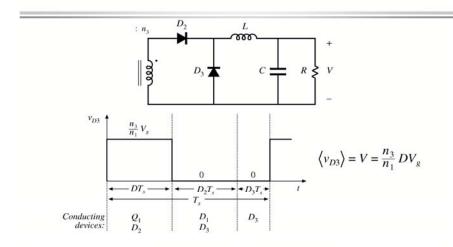

#### 6.3.2. Forward converter

- · Buck-derived transformer-isolated converter

- · Single-transistor and two-transistor versions

- · Maximum duty cycle is limited

- · Transformer is reset while transistor is off

Fundamentals of Power Electronics

4

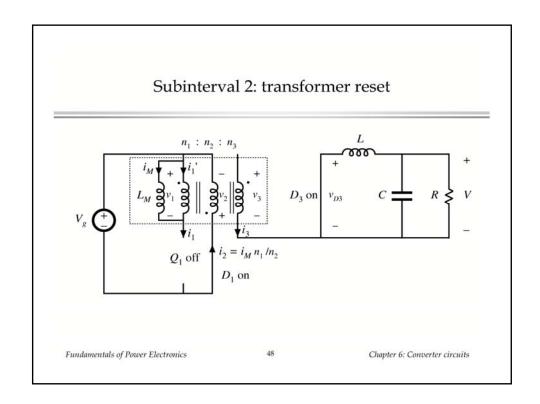

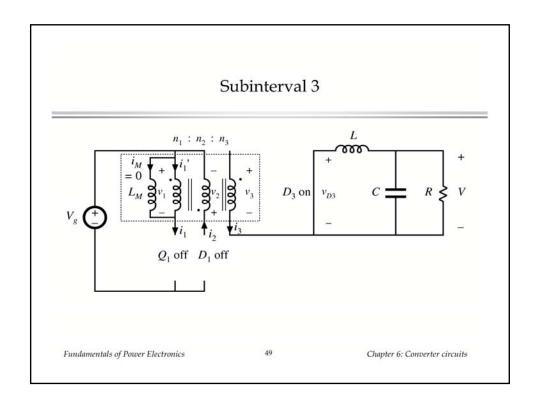

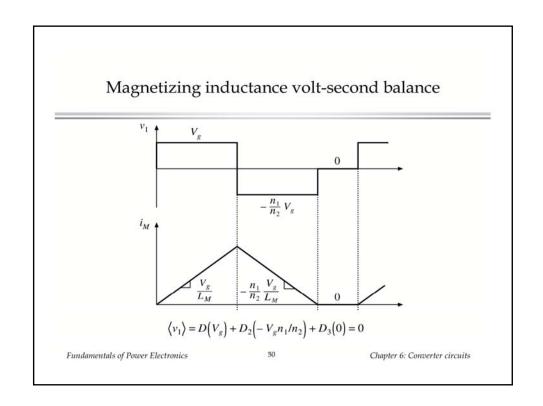

#### Transformer reset

From magnetizing current volt-second balance:

$$\left\langle v_1 \right\rangle = D \Big( V_g \Big) + D_2 \Big( - V_g n_1 / n_2 \Big) + D_3 \Big( 0 \Big) = 0$$

Solve for

$$D_2$$

:

$$D_2 = \frac{n_2}{n_1} D$$

$D_3$  cannot be negative. But  $D_3 = 1 - D - D_2$ . Hence

$$D_3=1-D-D_2\geq 0$$

$$D_3 = 1 - D\left(1 + \frac{n_2}{n_1}\right) \ge 0$$

Solve for D

$$D \le \frac{1}{1 + \frac{n_2}{n_1}}$$

for

$$n_1 = n_2$$

:  $D \le 1$

Fundamentals of Power Electronics

Chapter 6: Converter circuits

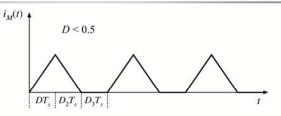

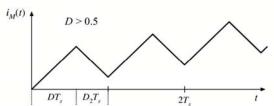

## What happens when D > 0.5

magnetizing current waveforms,

for  $n_1 = n_2$

Fundamentals of Power Electronics

52

## Conversion ratio M(D)

Fundamentals of Power Electronics

53

Chapter 6: Converter circuits

## Maximum duty cycle vs. transistor voltage stress

Maximum duty cycle limited to

$$D \le \frac{1}{1 + \frac{n_2}{n_1}}$$

which can be increased by increasing the turns ratio  $n_2 \, / \, n_J$ . But this increases the peak transistor voltage:

$$\max\left(v_{Q1}\right) = V_g\left(1 + \frac{n_1}{n_2}\right)$$

For  $n_1 = n_2$

$$D \le \frac{1}{2}$$

and  $\max(v_{Q1}) = 2V_g$

Fundamentals of Power Electronics

5

## The two-transistor forward converter

2

Fundamentals of Power Electronics

0

Chapter 6: Converter circuits

## Chapter 5. The Discontinuous Conduction Mode

- 5.1. Origin of the discontinuous conduction mode, and mode boundary

- 5.2. Analysis of the conversion ratio M(D,K)

- 5.3. Boost converter example

- 5.4. Summary of results and key points

Fundamentals of Power Electronics

Chapter 5: Discontinuous conduction mode