| <b>Active Switch Stress</b> |                             |

|-----------------------------|-----------------------------|

|                             |                             |

|                             |                             |

|                             |                             |

|                             |                             |

|                             |                             |

|                             |                             |

|                             |                             |

|                             | THE UNIVERSITY OF TENNESSEE |

|                             | KNOXVILLE                   |

| <b>Active Switch Utilization</b> |                               |

|----------------------------------|-------------------------------|

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  |                               |

|                                  | THE UNIVERSITY OF TENNESSEE T |

## **Semiconductor Proportional Cost**

(semiconductor device cost per rated kVA) = cost of device, divided by product of rated blocking voltage and rms current, in \$/kVA. Typical values are less than \$1/kVA

(voltage derating factor) and (current derating factor) are required to obtain reliable operation. Typical derating factors are 0.5 - 0.75

Typical cost of active semiconductor devices in an isolated dc-dc converter: \$1 - \$10 per kW of output power.

Fundamentals of Power Electronics

Chapter 6: Converter circuits

### **Switch Utilization Table**

Table 6.1. Active switch utilizations of some common dc-dc converters, single operating point.

| Converter                                                                                | U(D)                     | $\max U(D)$                   | $\max_{OCCUTS} U(D)$ |

|------------------------------------------------------------------------------------------|--------------------------|-------------------------------|----------------------|

| Buck                                                                                     | <b>√</b> D               | 1                             | 1                    |

| Boost                                                                                    | $\frac{D'}{ID}$          | ∞                             | 0                    |

| Buck-boost, flyback, nonisolated SEPIC, isolated<br>SEPIC, nonisolated Cuk, isolated Cuk | $D' / \!\!\!\!/ D$       | $\frac{2}{3\sqrt{3}} = 0.385$ | $\frac{1}{3}$        |

| Forward, $n_1 = n_2$                                                                     | $\frac{1}{2}$ $\sqrt{D}$ | $\frac{1}{2\sqrt{2}} = 0.353$ | $\frac{1}{2}$        |

| Other isolated buck-derived converters (full-<br>bridge, half-bridge, push-pull)         | $\frac{ID}{2I2}$         | $\frac{1}{2/2} = 0.353$       | 1                    |

| Isolated boost-derived converters (full bridge,<br>push-pull)                            | $\frac{D'}{2\sqrt{1+D}}$ | $\frac{1}{2}$                 | 0                    |

Fundamentals of Power Electronics

### **Converter Design**

- No definitive way to determine best converter topology for a given application

- Performance in power electronics depends heavily on details of implementation

- Circuit layout

- Gate driver design

- Cooling system

- Materials

- Switch stress/utilization give some direction on candidate topologies

- Active switches often dominate loss and cost of converter

## **Parameterized Design**

- To design converter independent of device implementation, consider voltage and current stresses of all elements

- In transformer isolated converters, the turns ratio is a degree of freedom for the design

- Use design equations in e.g. Excel or Matlab to examine effects of design on resulting stresses

# **Spreadsheet Design Example**

### Specifications

Maximum input voltage  $V_g$ 390 V Minimum input voltage  $V_g^s$ 260 V Output voltage V 15 V Maximum load power  $P_{load}$ 200 W Minimum load power P<sub>load</sub> 20 W Switching frequency  $f_s$ 100 kHz Maximum output ripple  $\Delta v$ 0.1 V

- · Input voltage: rectified 230 Vrms ±20%

- · Regulated output of 15 V

- · Rated load power 200 W

- · Must operate at 10% load

- Select switching frequency of 100 kHz

- Output voltage ripple ≤ 0.1V

Compare single-transistor forward and flyback converters in this application Specifications are entered at top of spreadsheet

Fundamentals of Power Electronics

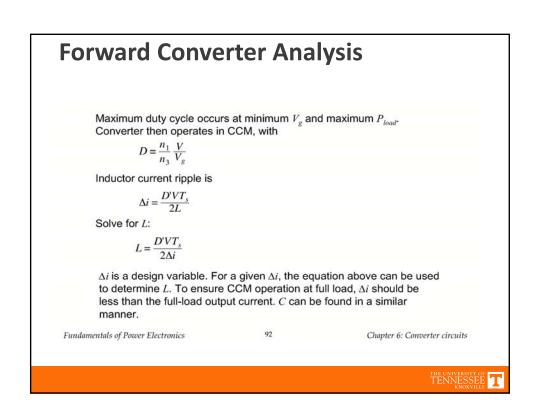

### **Forward Converter DCM Bound**

Check for DCM at light load. The solution of the buck converter operating in DCM is

$$V = \frac{n_3}{n_1} V_g \frac{2}{\sqrt{1 + \frac{4K}{D^2}}}$$

with  $K = 2L/RT$  and  $R = \frac{1}{2}$

These equations apply equally well to the forward converter, provided that all quantities are referred to the transformer secondary side.

Solve for D:

Divergence for

$$D$$

:

$$D = \frac{2\sqrt{K}}{\sqrt{\left(\frac{2n_3V_g}{n_1V} - 1\right)^2 - 1}} \quad \text{in DCM} \qquad D = \frac{n_1}{n_3} \frac{V}{V_g} \quad \text{in CCM}$$

at a given operating point, the actual duty cycle is the small of the values calculated by the CCM and DCM equations above. Minimum Doccurs at minimum  $P_{load}$  and maximum  $V_{g}$ .

Fundamentals of Power Electronics

Chapter 6: Converter circuits

### **Forward Converter Stress**

Worst-case component stresses can now be evaluated.

Peak transistor voltage is

$$\max\left(v_{Q1}\right) = V_g\left(1 + \frac{n_1}{n_2}\right)$$

RMS transistor current is

$$I_{Q1,rms} = \frac{n_3}{n_1} \sqrt{D} \; \sqrt{\; I^2 + \frac{\left(\Delta i\right)^2}{3}} \approx \frac{n_3}{n_1} \sqrt{D} \; I$$

(this neglects transformer magnetizing current)

Other component stresses can be found in a similar manner. Magnetics design is left for a later chapter.

Fundamentals of Power Electronics

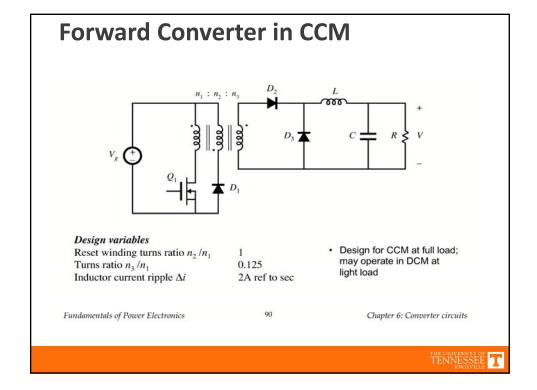

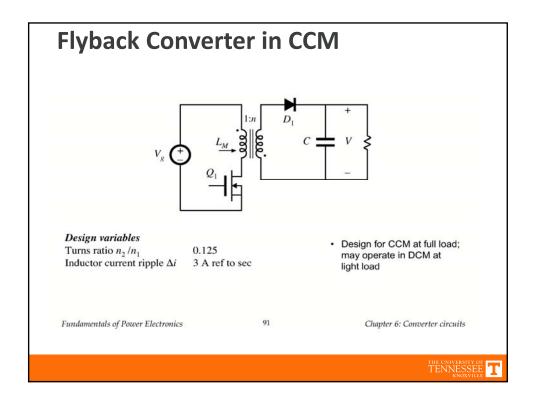

|          | Forward converter design, CCM       |                | Flyback converter design, CCM      |                               |

|----------|-------------------------------------|----------------|------------------------------------|-------------------------------|

|          | Design variables                    |                | Design variables                   |                               |

|          | Reset winding turns ratio $n_2/n_1$ | 1              | Turns ratio $n_2/n_1$              | 0.125                         |

|          | Turns ratio $n_3/n_1$               | 0.125          | Inductor current ripple $\Delta i$ | 3 A ref to sec                |

|          | Inductor current ripple $\Delta i$  | 2 A ref to sec |                                    |                               |

|          | Results                             |                | Results                            |                               |

|          | Maximum duty cycle D                | 0.462          | Maximum duty cycle D               | 0.316                         |

|          | Minimum D, at full load             | 0.308          | Minimum D, at full load            | 0.235                         |

|          | Minimum D, at minimum load          | 0.251          | Minimum D, at minimum load         | 0.179                         |

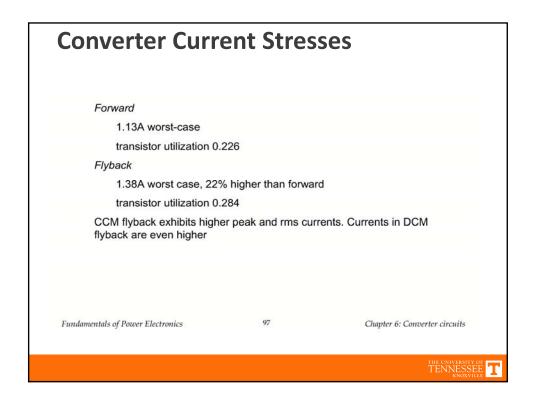

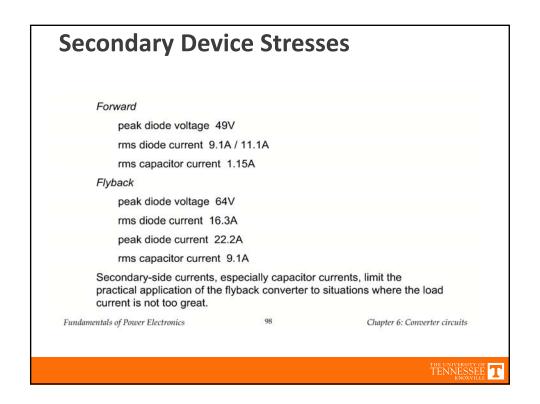

|          | Worst-case stresses                 |                | Worst-case stresses                |                               |

|          | Peak transistor voltage $v_{Q1}$    | 780 V          | Peak transistor voltage $v_{Q1}$   | 510 V                         |

|          | Rms transistor current $i_{Q1}$     | 1.13 A         | Rms transistor current iQ1         | 1.38 A                        |

|          | Transistor utilization $U$          | 0.226          | Transistor utilization $U$         | 0.284                         |

|          | Peak diode voltage v <sub>D2</sub>  | 49 V           | Peak diode voltage $v_{D1}$        | 64 V                          |

|          | Rms diode current $i_{D2}$          | 9.1 A          | Rms diode current $i_{D1}$         | 16.3 A                        |

|          | Peak diode voltage v <sub>D3</sub>  | 49 V           | Peak diode current iD1             | 22.2 A                        |

|          | Rms diode current i <sub>D3</sub>   | 11.1 A         |                                    |                               |

|          | Rms output capacitor current $i_C$  | 1.15 A         | Rms output capacitor current $i_C$ | 9.1 A                         |

| r        | tala di Danco Elastorollas          | 9              | 5                                  | Charles & Committee desired   |

| Fundamen | tals of Power Electronics           | 9              | 5                                  | Chapter 6: Converter circuits |

## **Design Comparison**

Flyback converter

Ideal peak transistor voltage: 510V

Actual peak voltage will be higher, due to ringing causes by transformer leakage inductance

An 800V or 1000V MOSFET would have an adequate design margin

Forward converter

Ideal peak transistor voltage: 780V, 53% greater than flyback

Few MOSFETs having voltage rating of over 1000 V are available —when ringing due to transformer leakage inductance is accounted for, this design will have an inadequate design margin

Fix: use two-transistor forward converter, or change reset winding turns ratio

A conclusion: reset mechanism of flyback is superior to forward

$Fundamentals\ of\ Power\ Electronics$

96

## **Chapter 6: Summary**

- Transformer-based converters often useful when extreme conversion ratios or galvanic isolation are required

- Isolated converters can be analyzed using conventional approaches, first replacing transformer by ideal transformer with magnetizing inductance

- Must ensure transformer volt-second balance, even in converters where it is not used as an energy storage element

- Selecting the best topology for a given application is an imprecise science, but active switch stress and utilization are figures-of-merit that give some insight

- Full comparison requires detailed analysis of candidate topologies