# **Design Approach**

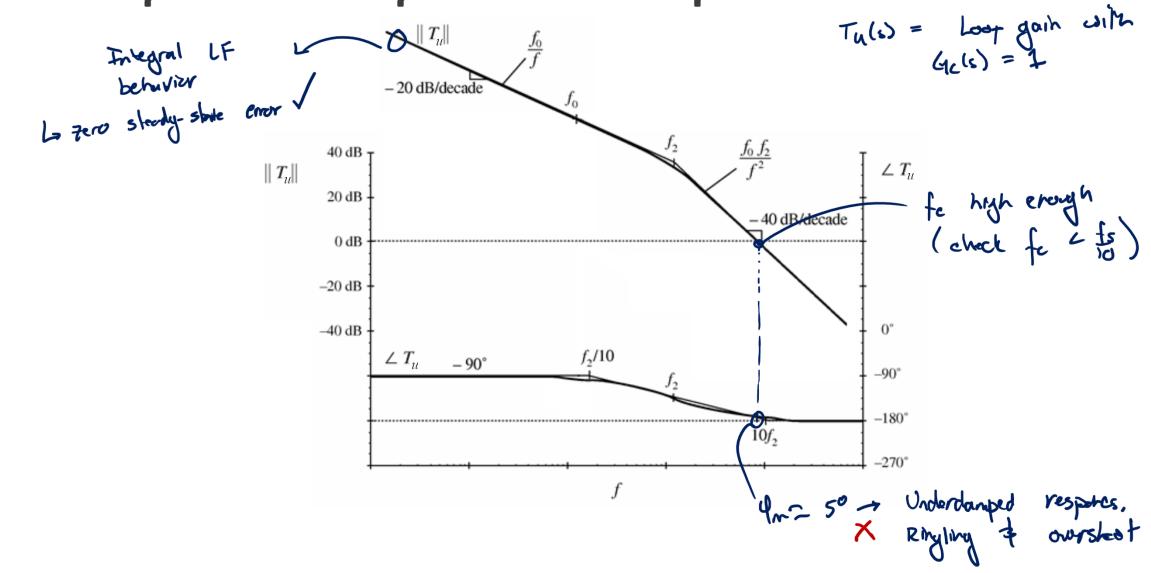

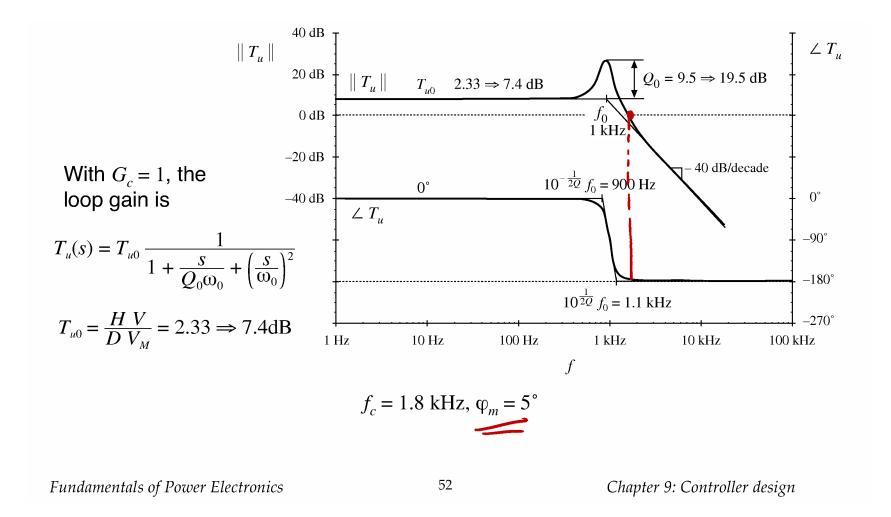

- Assume  $G_c(s) = 1$ , and plot the resulting uncompensated loop gain  $T_{ii}(s)$

- Examine uncompensated loop gain to determine the needs of the compensator  ${}^{\bullet}$

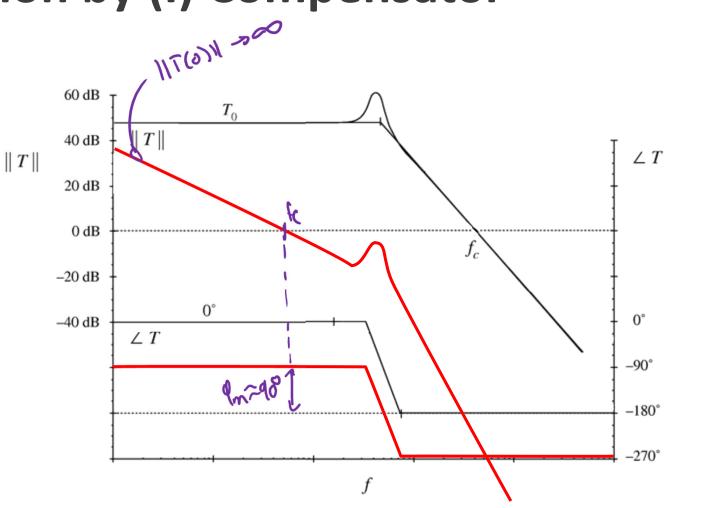

- Is low-frequency loop gain amplitude ||T(0)|| large enough to result in **low steady-state error**? La IIT(0) II ~ 00 zero stendy-sale enor

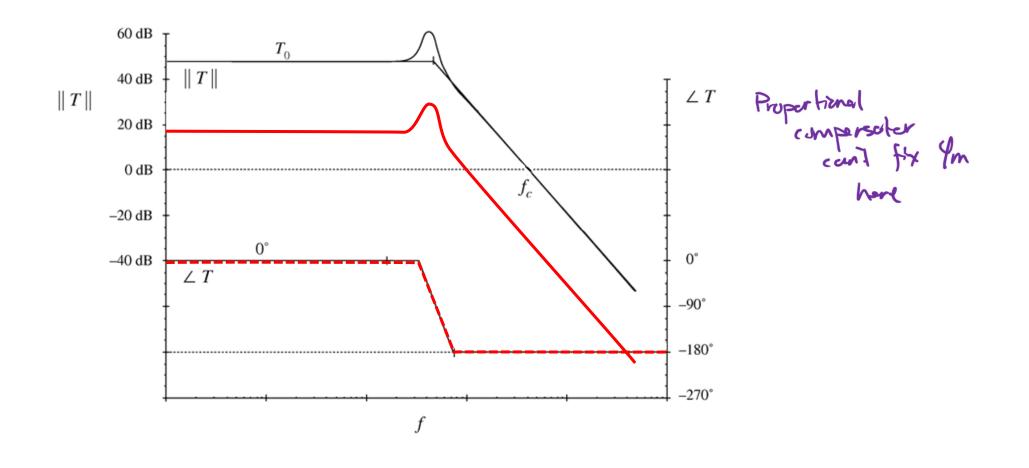

- Is  $\varphi_m$  sufficient for stability and requirements **on ringing/overshoot**?

- Is  $f_c$  high enough for a sufficiently **fast response**?

- Construct compensator to address shortcomings of  $T_{\mu}(s)$

- Use "toolbox" of compensators

$$\frac{nddittonel}{fe \lesssim fs/10} = Due to effects neglected in average model}

$$\int \frac{fe \lesssim fs/10}{||T(fcfe)||} = \frac{base}{base} = Bused on phase margin test limitations}

$$\frac{||T(f^{-}fe)||}{||T(f^{-}fe)||} = \frac{base}{base}$$$$$$

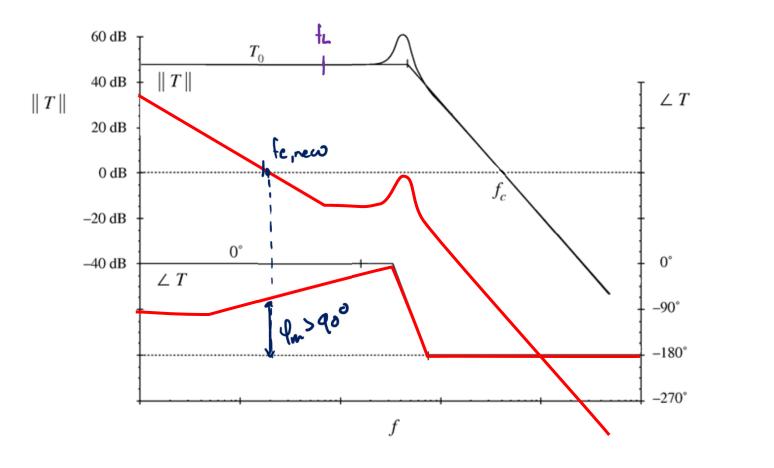

#### **Example: Uncompensated Loop Gain**

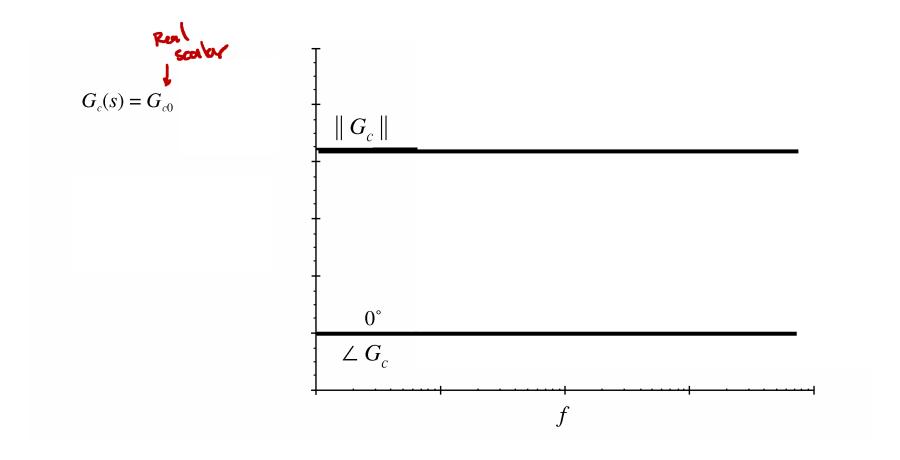

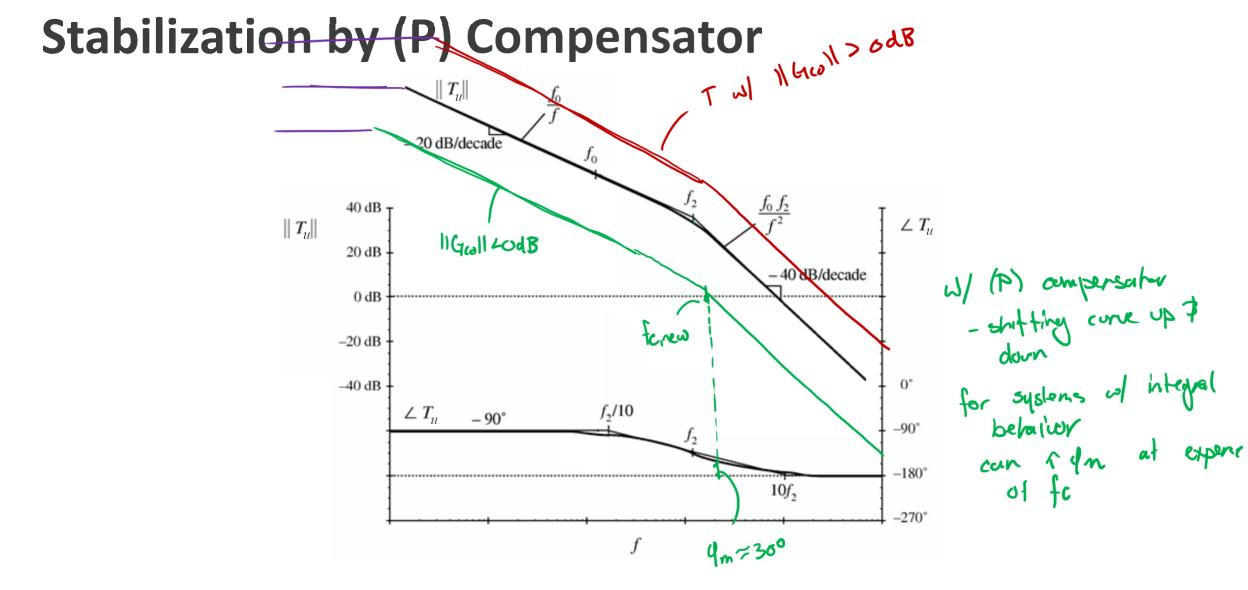

## **Proportional (P) Compensator**

#### **Another Example**

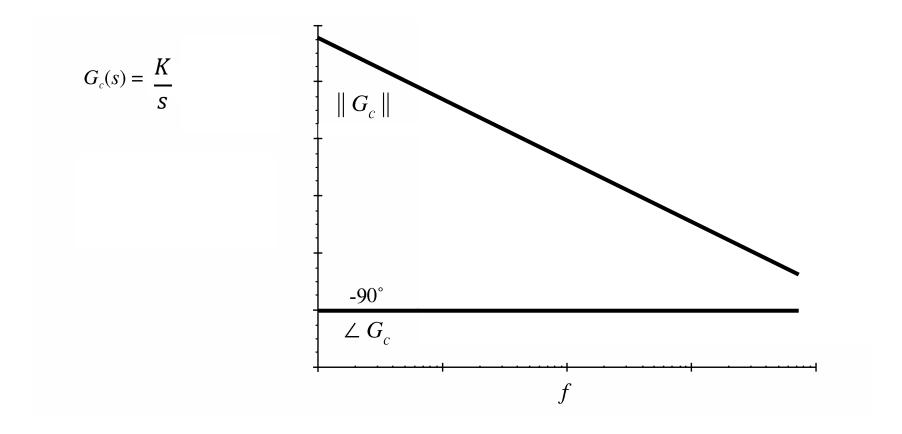

# Integral (I) Compensator

# Stabilization by (I) Compensator

•

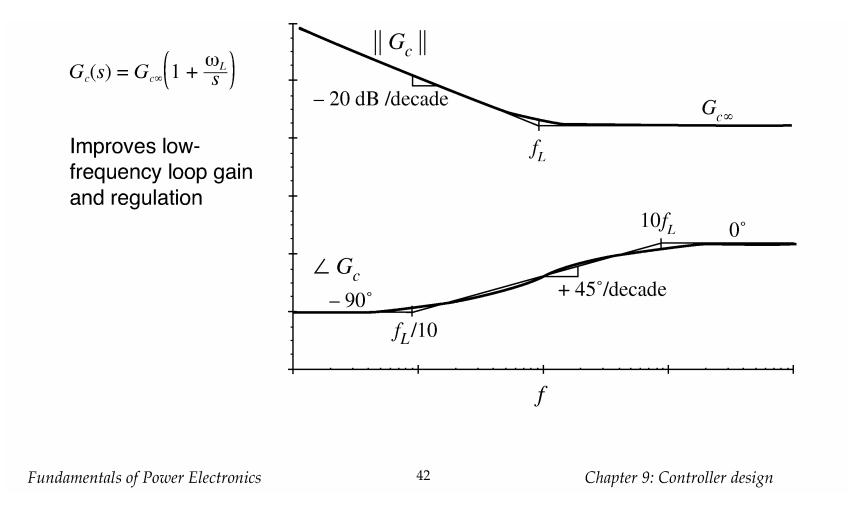

# Lag (PI) Compensator

TENNESSEE KNOXVILLE

# Stabilization by (PI) Compensator

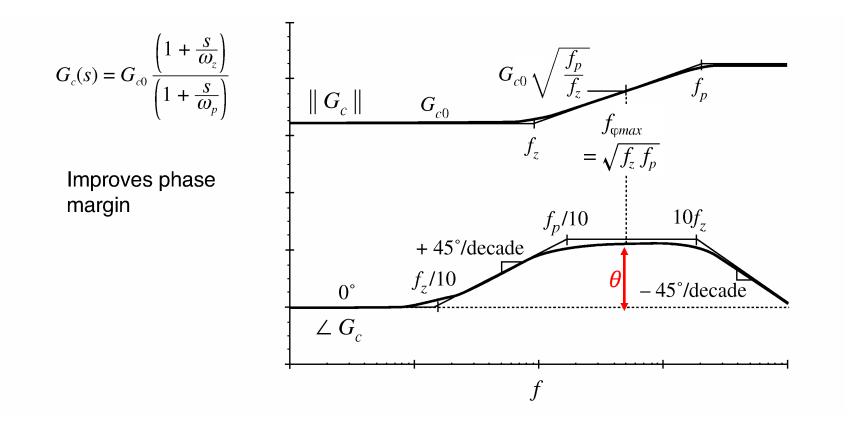

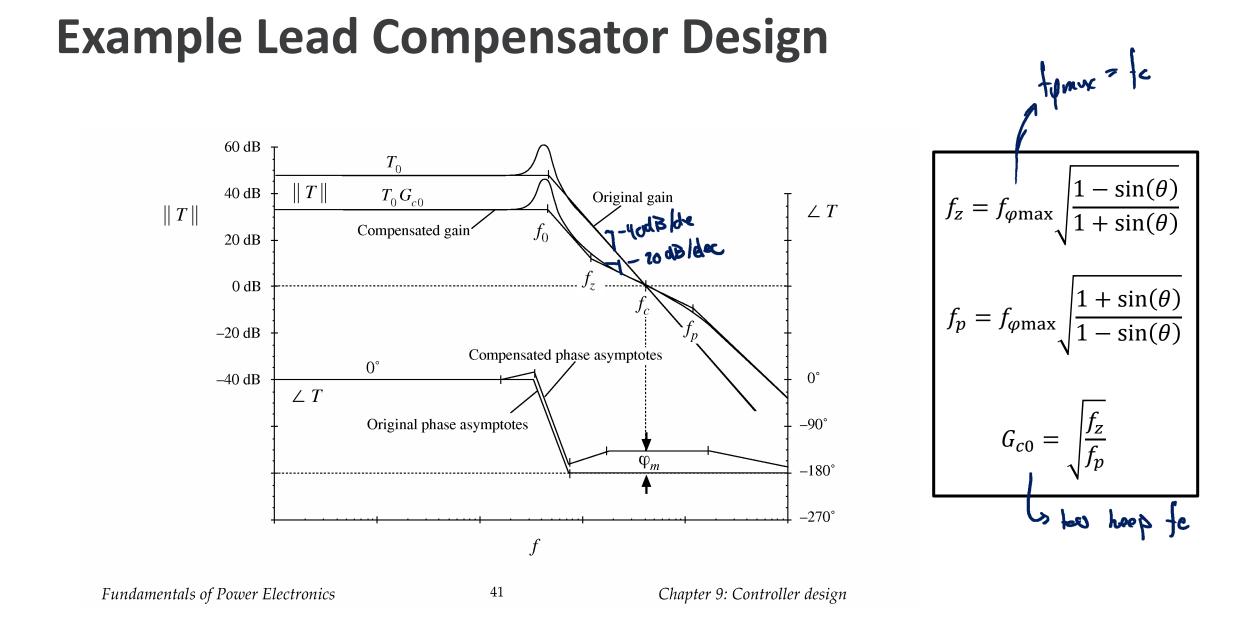

# Lead (PD) Compensator

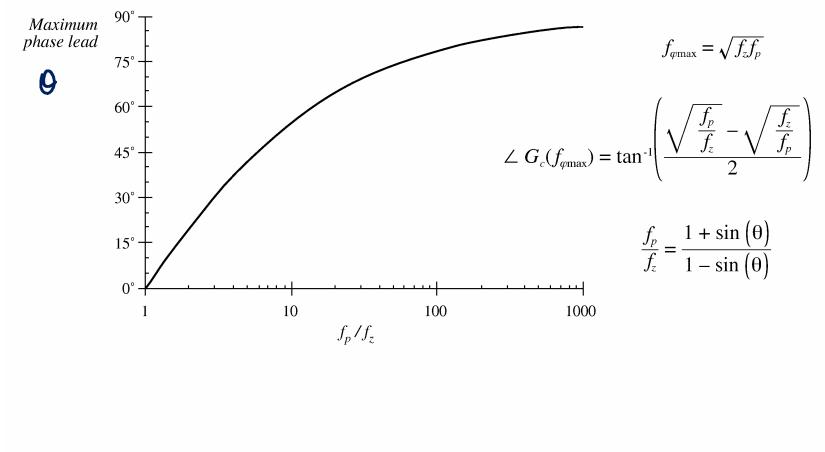

#### **Maximum Phase Lead**

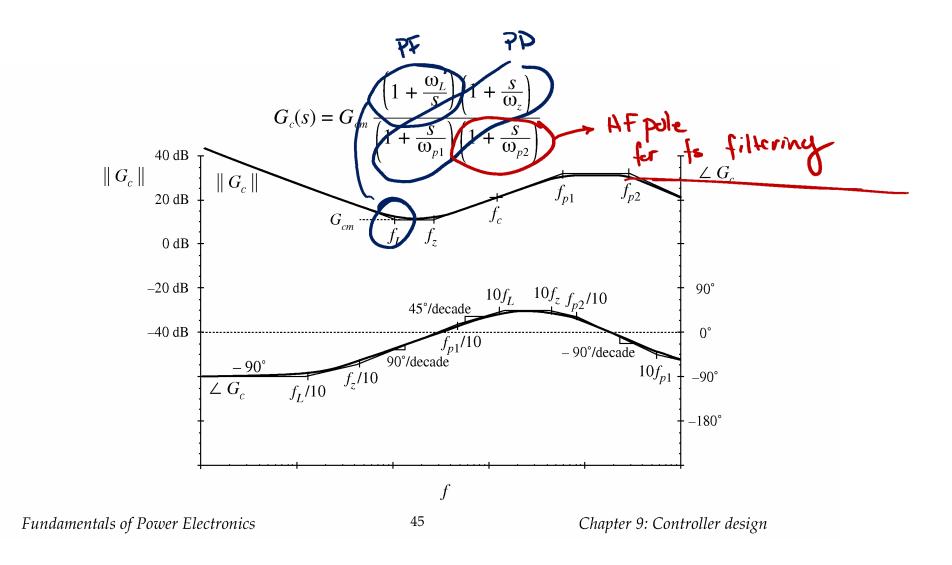

### **Combined (PID) Compensator**

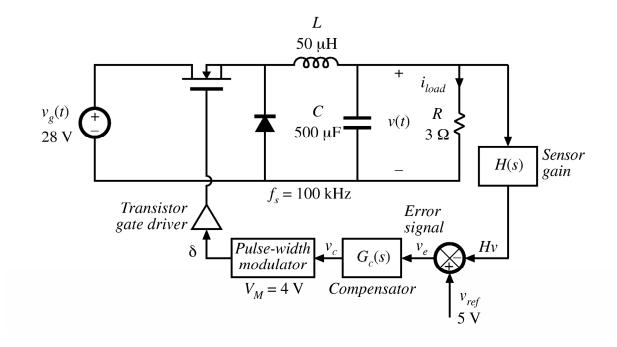

### **Example Design of Buck Compensator**

| Input voltage                      | $V_g = 28$ V                                |

|------------------------------------|---------------------------------------------|

| Output                             | $V = 15$ V, $I_{load} = 5$ A, $R = 3\Omega$ |

| Quiescent duty cycle               | D = 15/28 = 0.536                           |

| Reference voltage                  | $V_{ref} = 5 V$                             |

| Quiescent value of control voltage | $V_c = DV_M = 2.14$ V                       |

| Gain $H(s)$                        | $H = V_{ref}/V = 5/15 = 1/3$                |

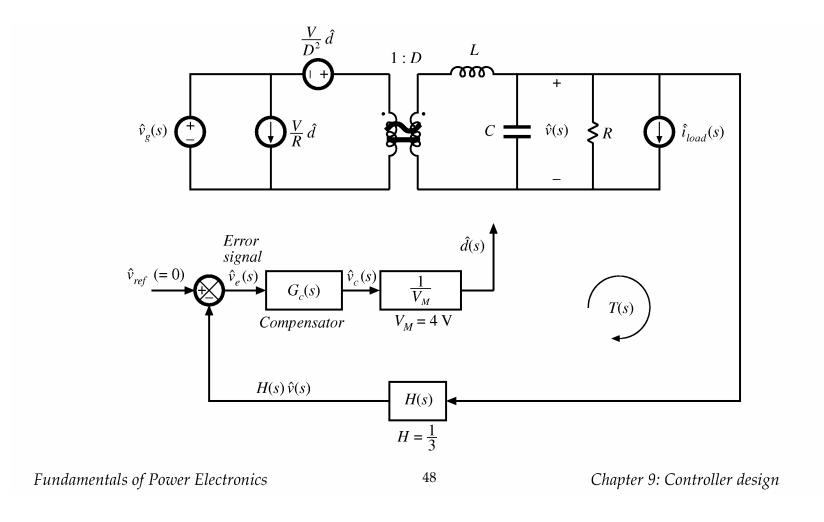

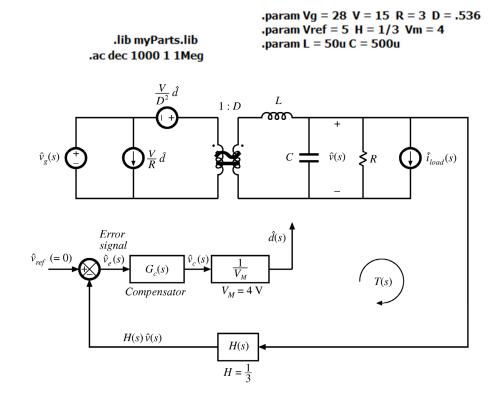

### **AC Power Stage Model**

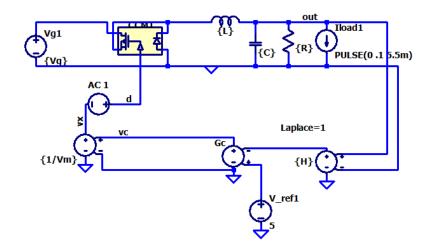

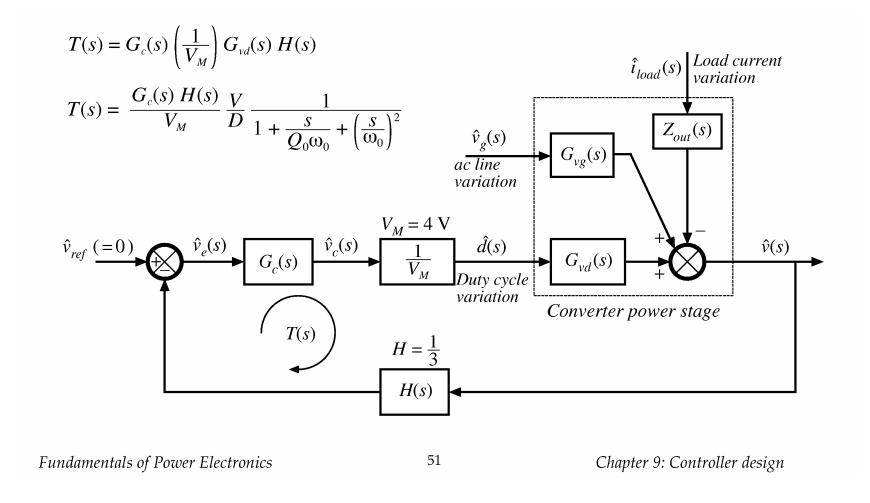

### **System Block Diagram**

## **Plotting Uncompensated Loop Gain**

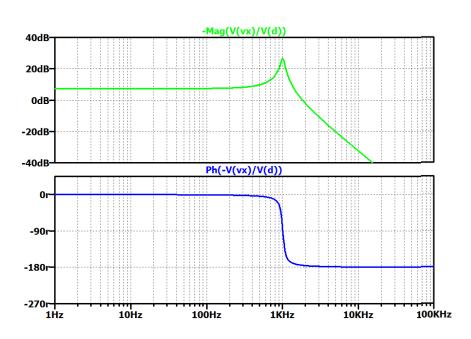

#### LTSpice Simulation – AC, Uncompensated

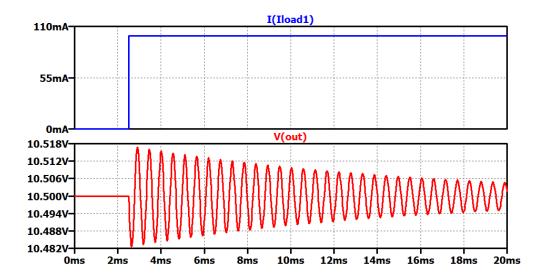

### **Transient Simulation, Uncompensated**

.param Vg = 28 V = 15 R = 3 D = .536 .param Vref = 5 H = 1/3 Vm = 4 .param L = 50u C = 500u

.ic V(out) = 15 I(L1) = 5 V(vc) = {D\*Vm}