# **Simulation Modeling**

### **Circuit Simulation**

- LTSpice

- Other tools accepted, but not supported

- Choose model type (switching, averaged, dynamic)

- Supplement analytical work rather than repeating it

- Show results which clearly demonstrate what matches and what does not with respect to experiments (i.e. ringing, slopes, etc.)

# **LTSpice Modeling Examples**

- Example files added to course materials page

- Custom model

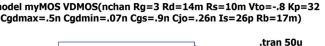

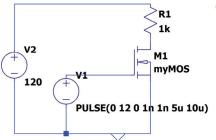

- VDMOS model

- Manufacturer Model

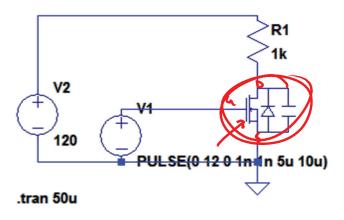

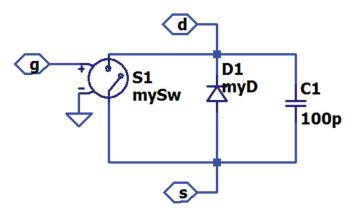

## **Custom Transistor Model**

.model myD D(n=.001) .model mySw SW(Ron=10m Roff=1G Von=1 Voff = .5 )

| VC   | OMOS        | N | Ло    | del     |  |

|------|-------------|---|-------|---------|--|

| Namo | Description |   | Units | Default |  |

| Name     | Description                                                                                                    | Units            | Default | Example |       |

|----------|----------------------------------------------------------------------------------------------------------------|------------------|---------|---------|-------|

| Vto      | Threshold voltage                                                                                              | v                | 0       | 1.0     |       |

| Кр       | Transconductance<br>parameter                                                                                  | A/V <sup>2</sup> | 1.      | .5      | .m    |

| Phi      | Surface inversion<br>potential                                                                                 | v                | 0.6     | 0.65    | +     |

| Lambda   | Channel-length<br>modulation                                                                                   | 1/V              | 0.      | 0.02    | -     |

| mtriode  | Conductance<br>multiplier in triode<br>region(allows<br>independent fit of<br>triode and<br>saturation regions | -                | 1.      | 2.      |       |

| subthres | Current(per volt<br>Vds) to switch from<br>square law to<br>exponential<br>subthreshold<br>conduction          | A/V              | 0.      | ln      | м<br> |

| BV       | Vds breakdown<br>voltage                                                                                       | v                | Infin.  | 40      |       |

| IBV      | Current at Vds=BV                                                                                              | A                | 100pA   | 1u      |       |

| NBV      | Vds breakdown<br>emission coefficient                                                                          | -                | 1.      | 10      | •     |

| Rd       | Drain ohmic<br>resistance                                                                                      | Ω                | 0.      | 1.      |       |

| Rs       | Source ohmic<br>resistance                                                                                     | Ω                | 0.      | 1.      |       |

| Rg       | Gate ohmic<br>resistance                                                                                       | Ω                | 0.      | 2.      |       |

| Rds      | Drain-source shunt<br>resistance                                                                               | Ω                | Infin.  | 10Meg   |       |

| Rb       | Body diode ohmic<br>resistance                                                                                 | Ω                | 0.      | .5      |       |

| Cio      | Zero-bias body diode                                                                                           | F                | 0.      | 1n      | 1     |

Note: any other parameters **ignored**E.g. ron = 3m Qg = 1n mfg = Infineon

http://ltwiki.org/LTspiceHelp/LTspiceHelp/M\_MOSFET.htm

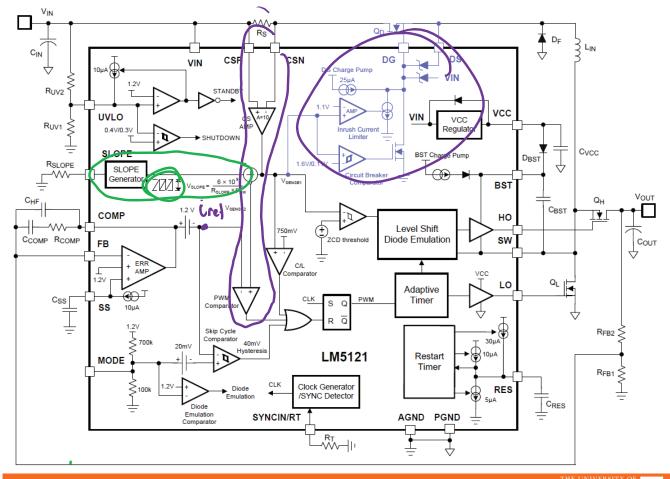

# **Manufacturer Device Model**

- Text-only netlist model of device including additional parasitics and temperature effects

- May slow or stop simulation if timestep and accuracy are not adjusted appropriately

TENNESSEE

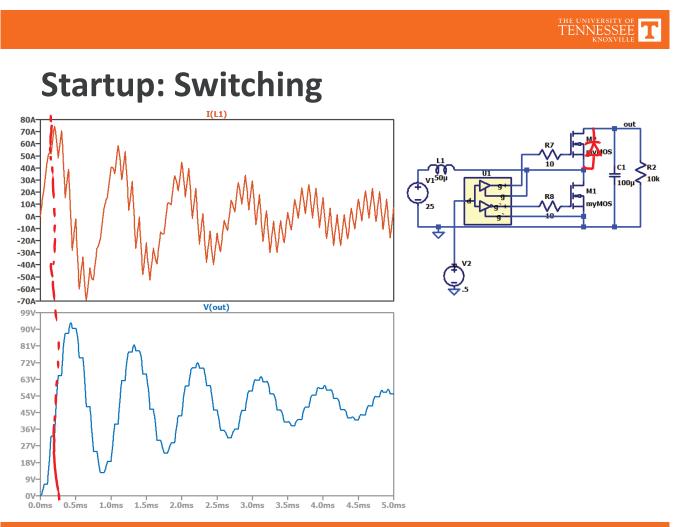

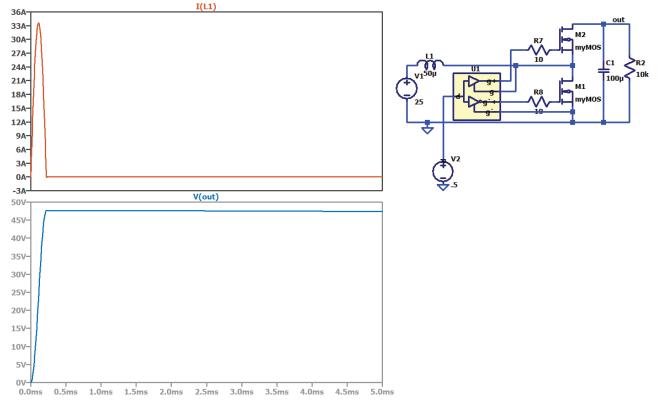

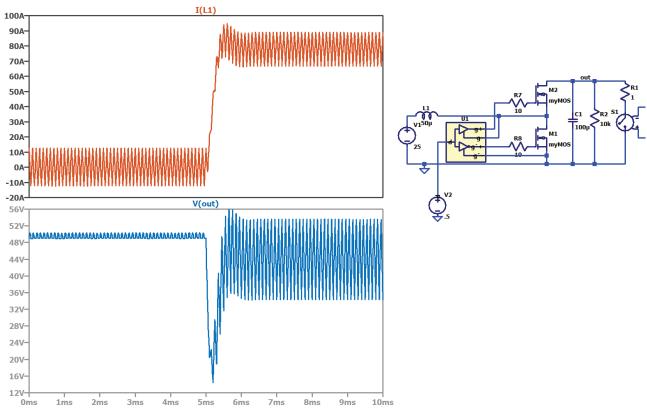

# **Full Switching Simulation**

out .ic V(out)=0 .ic I(L1)=0 .lib switch.lib M2 R7 myMOS L1 10 C1 **R**2  $\tilde{\mathcal{O}}$ U1 R V1 С M1 **R8** myMOS

.model myMOS VDMOS(Rg=1 Vto=4.5 Rd=14m Rs=10m Rb=17m Kp=30 Cgdmax=.5p Cgdmin=.05n Cgs=.2n Cjo=.03n Is=88p) .tran 1

TENNESSEE

## **Full Switching Simulation**

.model myMOS VDMOS(Rg=1 Vto=4.5 Rd=14m Rs=10m Rb=17m Kp=30 Cgdmax=.5p Cgdmin=.05n Cgs=.2n Cjo=.03n ls=88p) .tran 1 out .ic V(out)=0 .lib switch.lib Μ2 .ic I(L1)=0 **R7** Component Attribute Editor × 00 Open Symbol: E:\Program Files (x86)\LTC\LTspicelV\lib\sym\Custom\GateDi V1 This is the fourth attribute to appear on the netlist line. Attribute Value Vis. J Prefix Х InstName U1 Х GateDriver\_dt\_phase SpiceModel Value Value2 SpiceLin Spicel ine2 Cancel ΟK

# **Full Switching Model**

- Gives valuable insight into circuit operation

- Understand expected waveforms

- Identify discrepancies between predicted and experimental operation

- Slow to simulate; significant high frequency content

- Cannot perform AC analysis

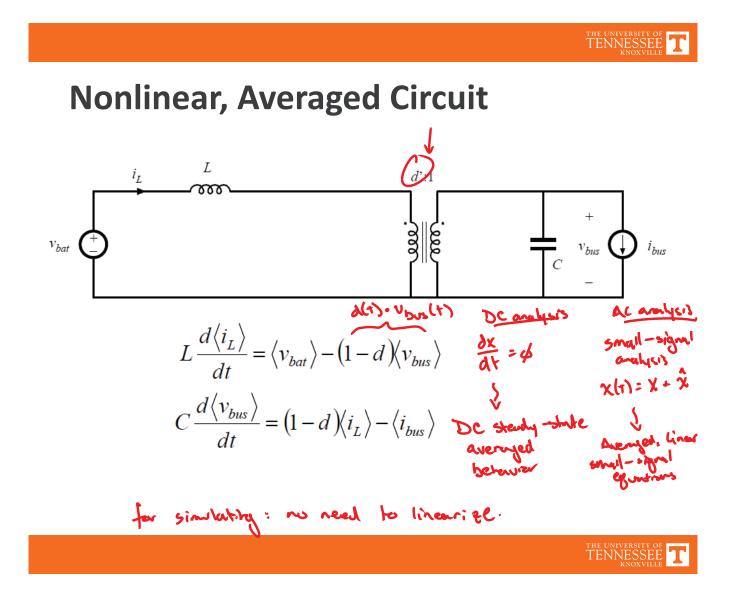

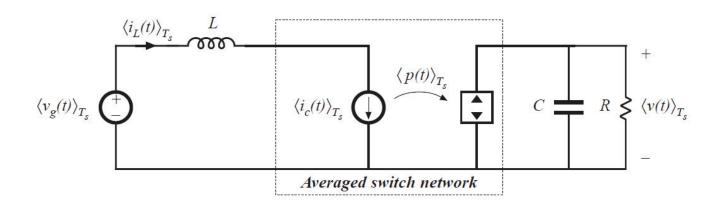

#### **Averaged Switch Modeling: Motivation**

- A *large-signal, nonlinear* model of converter is difficult for hand analysis, but well suited to simulation across a wide range of operating points

- Want an *averaged* model to speed up simulation speed

- Also allows linearization (AC analysis) for control design

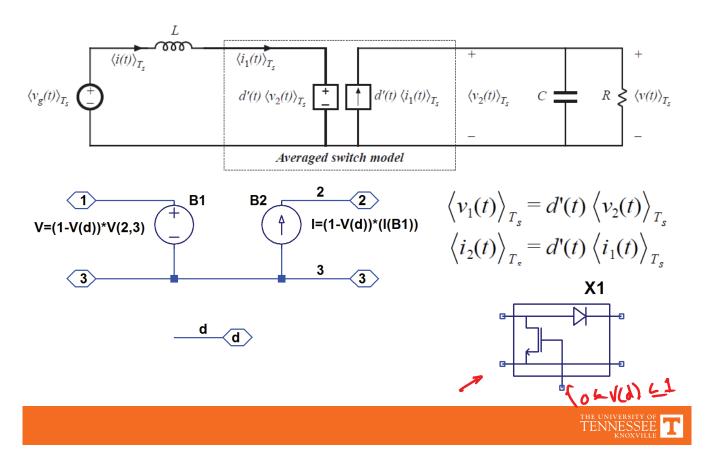

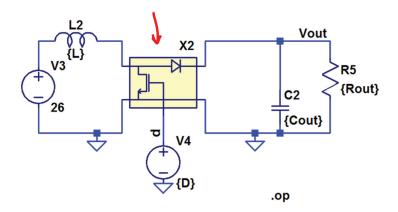

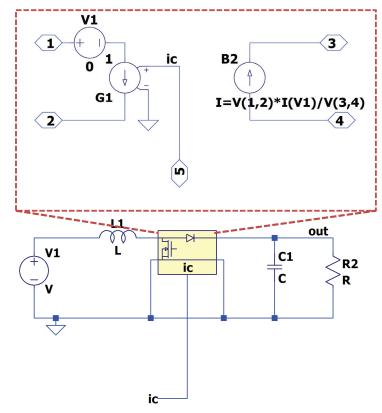

# **Implementation in LTSpice**

#### **Averaged Switch Model**

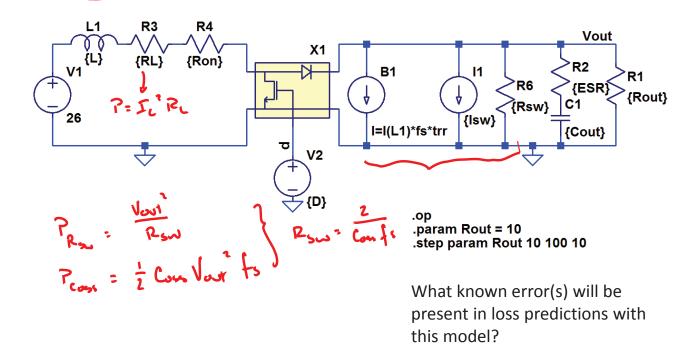

# Averaged Model With Losses

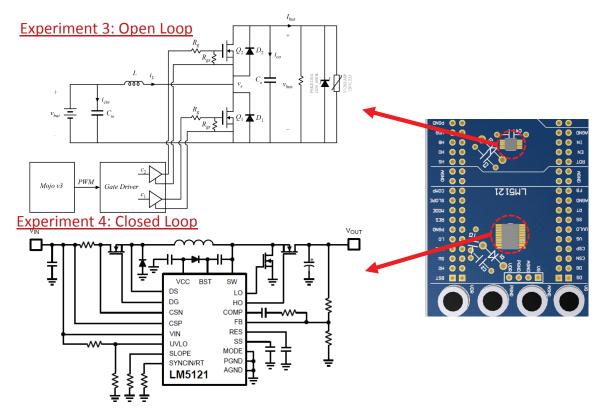

## **Experiment 4**

#### **Experiment 4: Closed-Loop Boost**

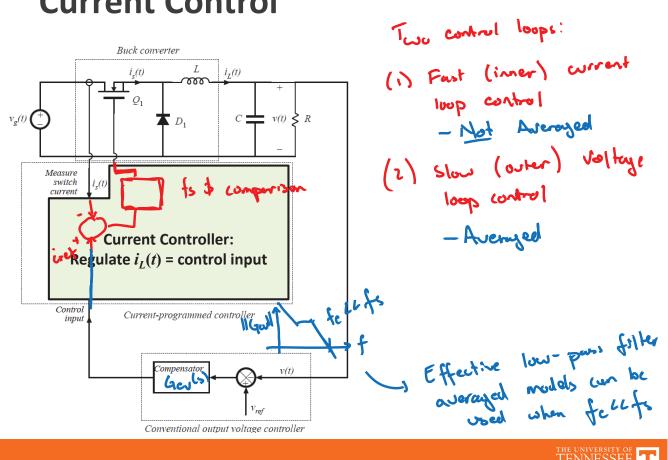

#### **Current Control**

TENNESSEE

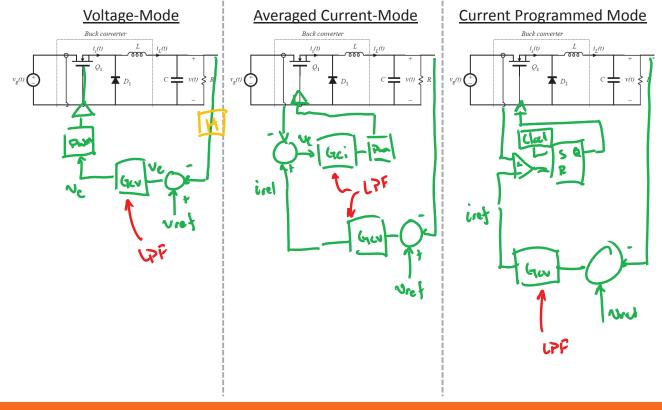

## **Averaged vs CPM**

TENNESSEE

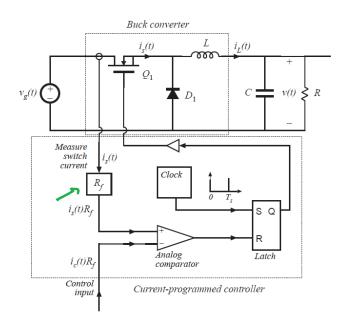

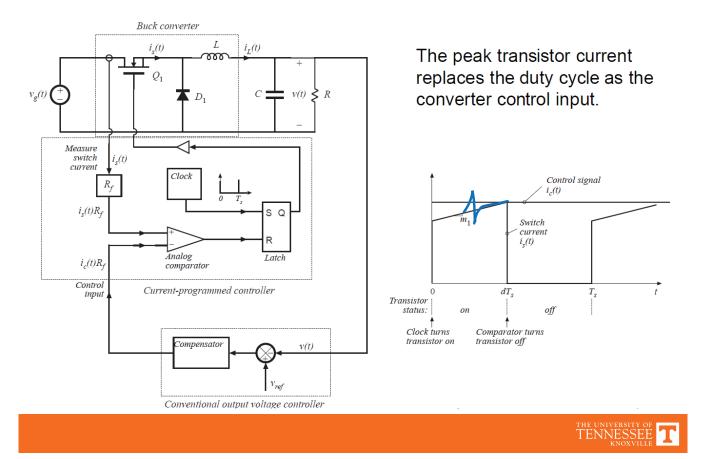

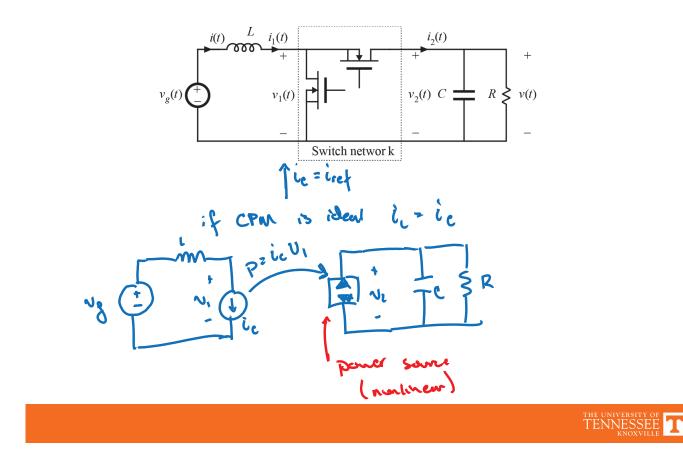

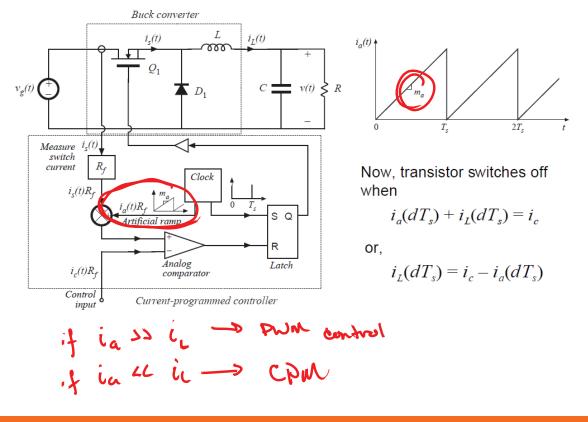

#### **Current Programmed Control (CPM)**

# **CPM Voltage Loop**

## **Current Programmed Control**

- Covered in Ch. 12 of *Fundamentals of Power Electronics*

- Advantages of current programmed control:

- Simpler dynamics —inductor pole is moved to high frequency

- Simple robust output voltage control, with large phase margin, can be obtained without use of compensator lead networks

- Transistor failures due to excessive current can be prevented simply by limiting  $i_c(t)$

- It is always necessary to sense the transistor current, to protect against overcurrent failures

- Transformer saturation problems in bridge or push-pull converters can be mitigated

- A disadvantage: susceptibility to noise

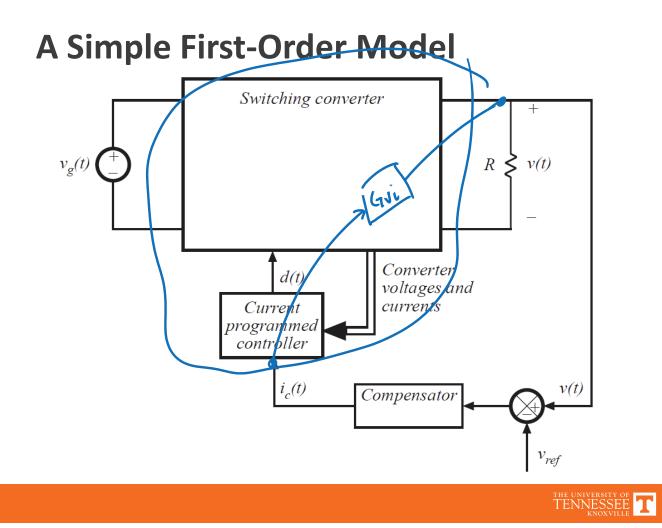

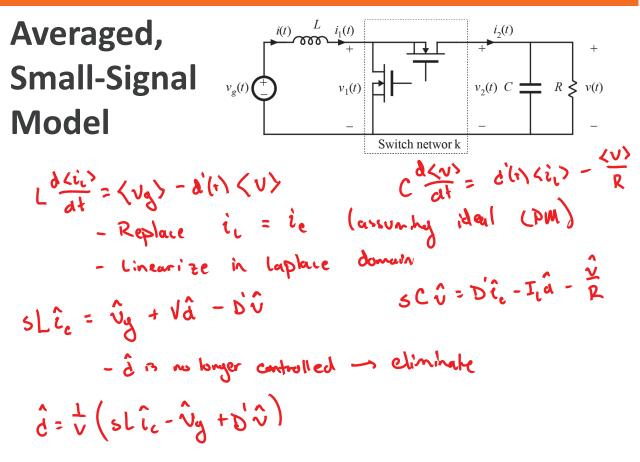

## **The First-Order Approximation**

$$\left\langle i_L(t) \right\rangle_{T_s} = i_c(t)$$

- Neglects switching ripple

- Yields physical insight and simple first-order model

- Accurate when converter operates well into CCM (so that switching ripple is small

- Accurate when artificial ramp (discussed later) is small

- Resulting small-signal relation:

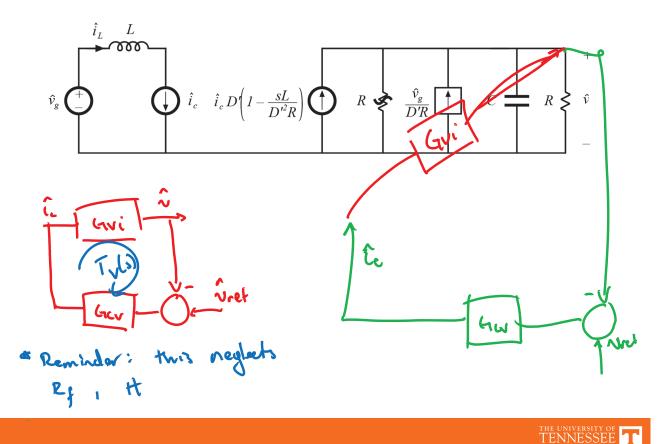

# **Averaged Modeling**

## **Large-Signal Nonlinear Model**

# **Implementation in LTSpice**

TENNESSEE KNOXVILLE

TENNESSEE T

TENNESSEE

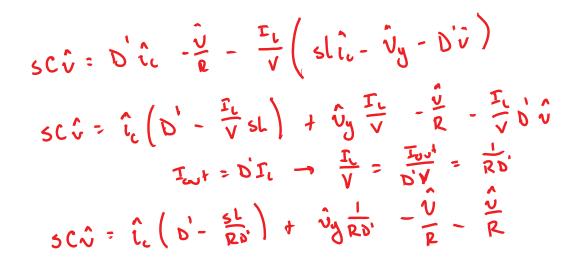

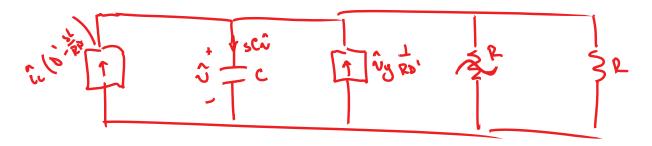

#### **Boost CCM CPM Small-Signal Model**

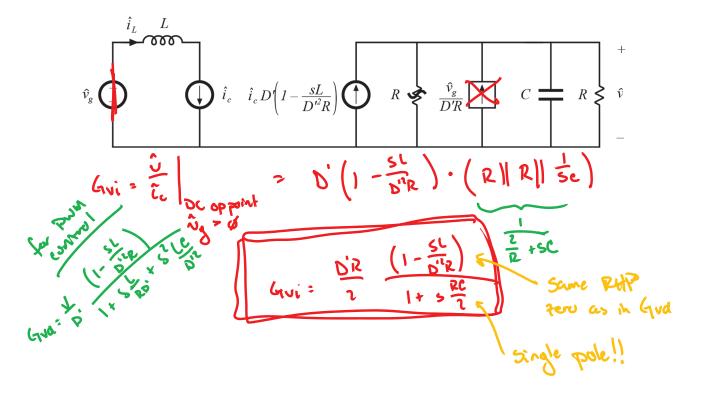

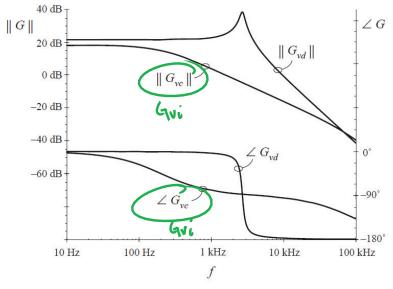

## **CPM Transfer Functions**

Fig. 12.28 Comparison of CPM control with duty-cycle control, for the control-to-output frequency response of the buck converter example.

#### **Voltage Control**

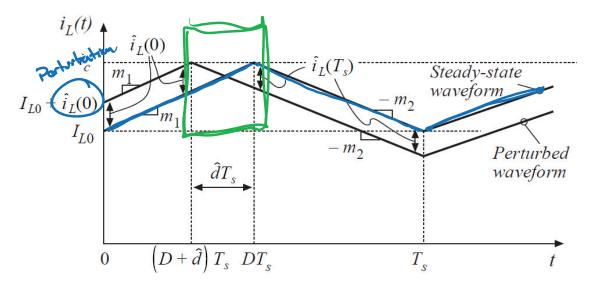

# **CPM Oscillations for D>0.5**

- The current programmed controller is inherently unstable for D > 0.5, regardless of the converter topology

- Controller can be stabilized by addition of an artificial ramp

## **Inductor Current Waveform in CCM**

| Inductor current slopes $m_1$<br>and $-m_2$ |                            |  |  |  |  |

|---------------------------------------------|----------------------------|--|--|--|--|

| buck converter                              |                            |  |  |  |  |

| $m_1 = \frac{v_g - v}{L}$                   | $-m_2 = -\frac{v}{L}$      |  |  |  |  |

| boost converter                             |                            |  |  |  |  |

| $m_1 = \frac{v_g}{L}$                       | $-m_2 = \frac{v_g - v}{L}$ |  |  |  |  |

| buck–boost converter                        |                            |  |  |  |  |

| $m_1 = \frac{v_g}{L}$                       | $-m_2 = \frac{v}{L}$       |  |  |  |  |

|                                             |                            |  |  |  |  |

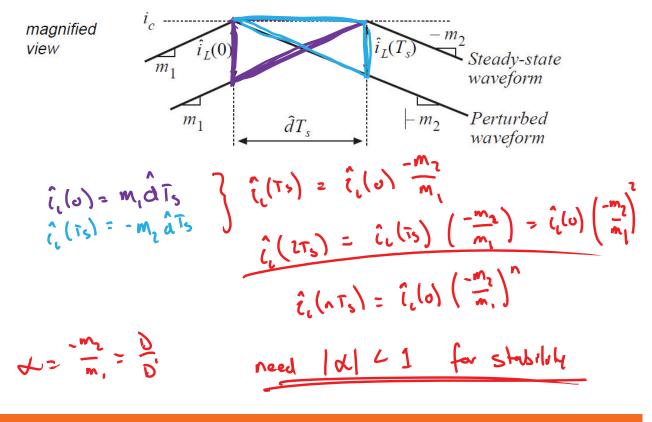

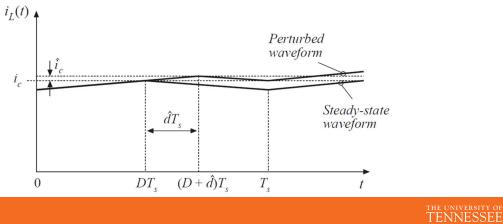

### **Introducing a Perturbation**

THE UNIVERSITY OF TENNESSEE

#### Change in Inductor Current Over $T_s$

TENNESSEE KNOXVILLE

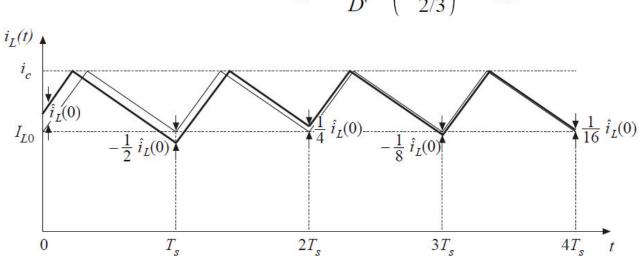

Example: Stable operation for *D*=1/3

$\alpha = -\frac{D}{D'} = \left(-\frac{1/3}{2/3}\right) = -0.5$

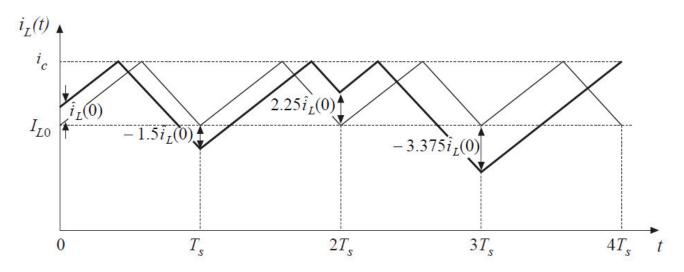

$$\alpha = -\frac{D}{D'} = \left(-\frac{0.6}{0.4}\right) = -1.5$$

# **Stabilization Through Artificial Ramp**

## **Final Value of Inductor Current**

First subinterval:

$\hat{i}_L(0) = -\hat{d}T_s \left( m_1 + m_a \right)$

Second subinterval:

$$\hat{i}_L(T_s) = -\hat{d}T_s \left(m_g - m_2\right)$$

Net change over one switching period:

$$\hat{i}_{L}(T_{s}) = \hat{i}_{L}(0) \left(-\frac{m_{2}-m_{a}}{m_{1}+m_{a}}\right)$$

After *n* switching periods:

TENNESSEE

# **Artificial Ramp: Additional Notes**

- For stability, require  $|\alpha| < 1$

- Common choices:

$$\alpha = -\frac{1 - \frac{m_a}{m_2}}{\frac{D'}{D} + \frac{m_a}{m_2}}$$

- $-m_a = 0.5 m_2$  (stable for all duty cycles)

- $-m_a = m_2$  (deadbeat)

- Artificial ramp decreases sensitivity to noise

# **More Accurate Models**

- The simple models of the previous section yield insight into the low- frequency behavior of CPM converters

- Unfortunately, they do not always predict everything that we need to know:

- Line-to-output transfer function of the buck converter

- Dynamics at frequencies approaching  $f_s$

- More accurate model accounts for nonideal operation of current mode controller built-in feedback loop

- Converter duty-cycle-controlled model, plus block diagram that accurately models equations of current mode controller

- See Section 12.3 for additional info

## More Accurate Model

- Simple model assumes  $i_L = i_c$  always

- Accounting for ripple, and artificial ramp weakens this approximation it my bandwidte of voltage loop is well below tsh then it ≈ ic apples

- Using sampled data modeling

$$\frac{\hat{i}_L}{\hat{i}_C} = \frac{1}{1 + \frac{1}{Q_s} \left(\frac{s}{2\pi f_s/2}\right) + \left(\frac{s}{2\pi f_s/2}\right)^2}$$

Where

$$Q_s = \frac{2}{\pi \left(\frac{2}{1-\alpha} - 1\right)}$$

F. Dong Tan and R. D. Middlebrook, "A Unified Model for Current Programmed Converters," IEEE Transactions on Power Electronics, vol. 10, no. 4, July 1995.

## **Note: Comparison to Datasheet**

o can be calcu  $\frac{dI_1}{dI_0} = 1 - \frac{1}{K}$

dlo

Application Information (continued)

Figure 30. Effect of Initial Perturbation when dl<sub>1</sub>/dl<sub>0</sub> < -1

een dl<sub>1</sub>/dl<sub>0</sub> and K factor is illustrated in the graphic below.

The absolute minimum value of K is 0.5. When K<0.5, the amplitude of dl<sub>1</sub> is greater than the amplitude of dl<sub>0</sub> and any initial perturbation results in sub-harmonic oscillation. If K=1, any initial perturbation will be removed in one switching cycle. This is known as one-cycle damping. When -1<dl<sub>1</sub>/dl<sub>0</sub><0, any initial perturbation will be under-damped. Any perturbation will be over-damped when 0<dl<sub>1</sub>/dl<sub>0</sub><1.

(19)

TENNESSEE

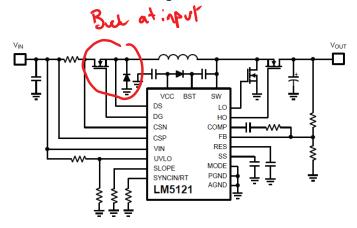

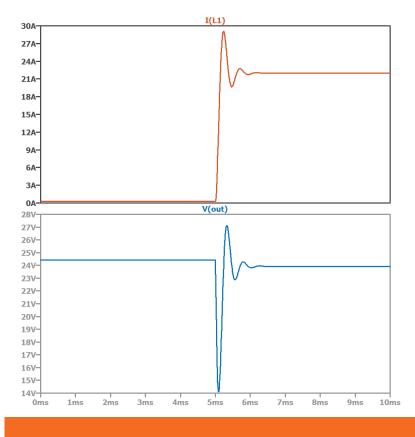

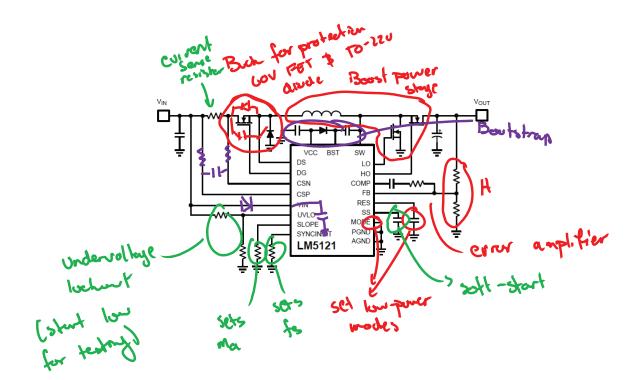

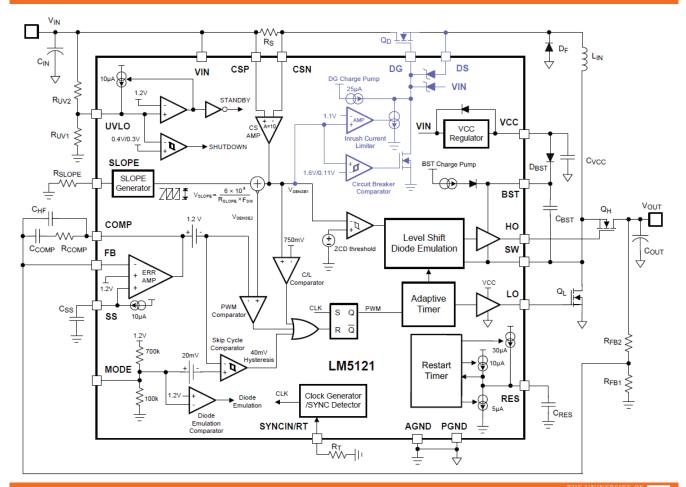

## **Application to Experiment 4**

- Complex switching controller

- Read the datasheet first

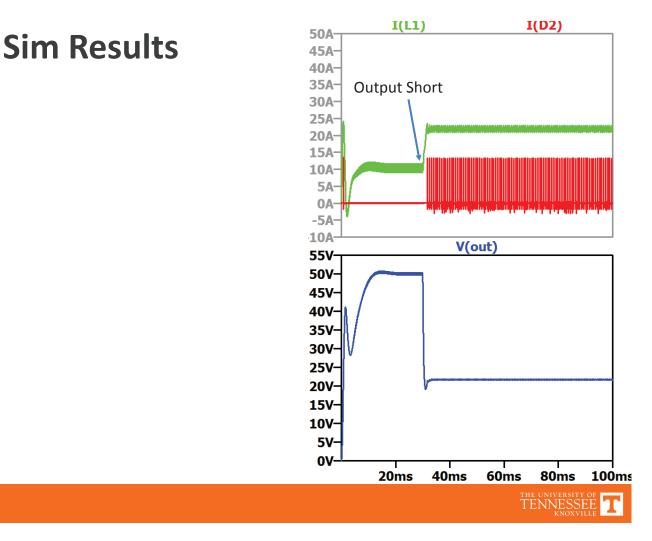

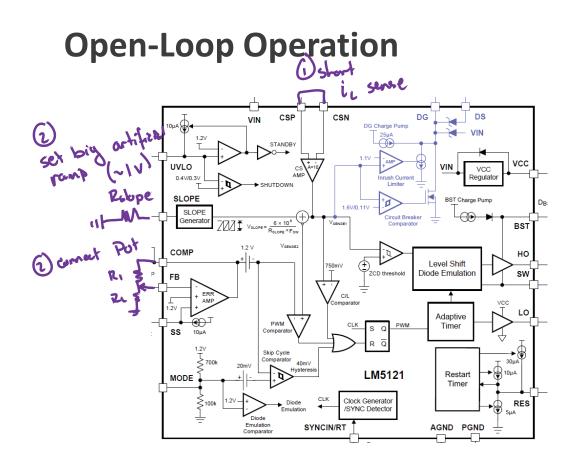

## **Startup: No Switching**

# **Short-Circuit: Switching**

# **Short-Circuit: No Switching**

## LM5121: Functionality

#### TENNESSEE KNOXVILLE

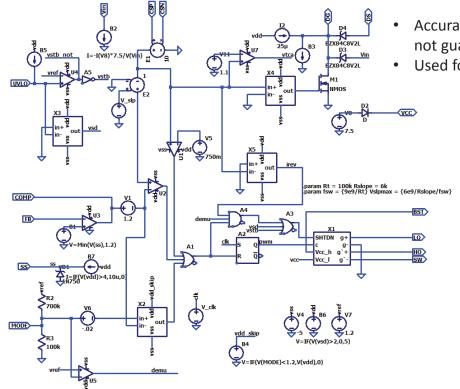

# **Internal Functional Model in LTSpice**

Accuracy/functionality not guaranteed

Used for insight only

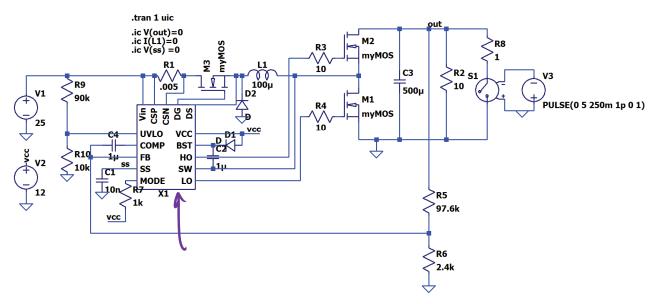

## **In-Circuit Simulation**

.model mysw sw(Von=3 Voff=2 Ron=.1 Roff = 1Meg)

.model myMOS VDMOS(Rg=1 Vto=4.5 Rd=14m Rs=10m Rb=17m Kp=30 Cgdmax=.5p Cgdmin=.05n Cgs=.2n Cjo=.03p Is=88p)

#### **A Tip: Debug Internal of Subcircuit**

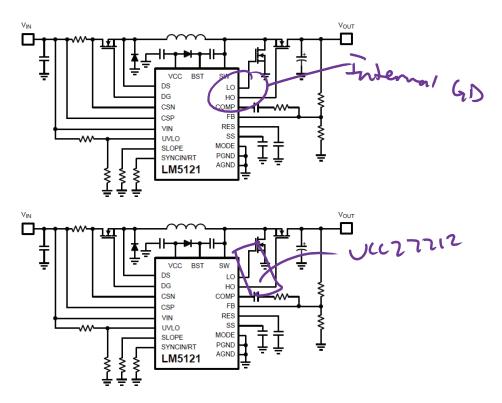

# **Experiment 4: Gate Driver Selection**

TENNESSEE KNOXVILLE

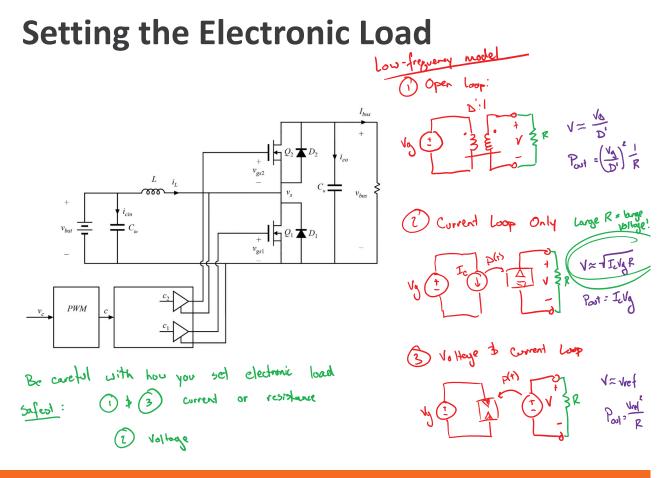

## **Experiment 4: Closing the Loop**

- Closed-loop operation in steps

- 1. Open-loop operation with LM5121 modulator

- Requires "tricking" LM5121

- 2. Closed-loop current regulation

- 3. Closed-loop voltage and current regulation

TENNESSEE KNOXVILLE