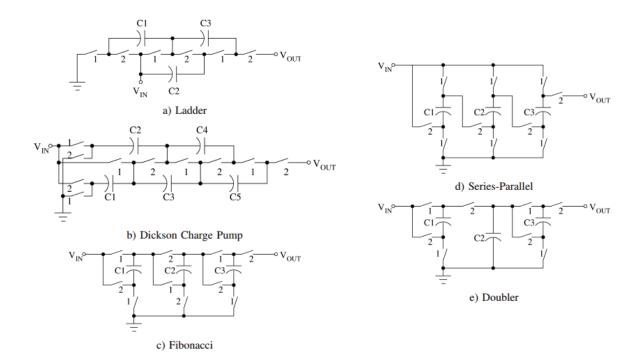

# **SC Converter Topologies**

M Seeman and S. Sanders, "Analysis and Optimization of Switched-Capacitor DC-DC Converters"

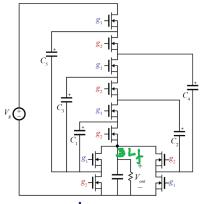

## **Dickson Converter**

### **Dickson Converter Variants**

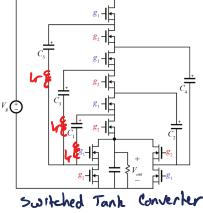

Standard Dickson (SSL / FSL)

Hybrid Dichson ul just one

Regulation

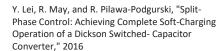

Unregulated for high? Resonant changing of all caps.

Y. Li, X. Lyu, D. Cao, S. Jiang and C. Nan, "A 98.55% Efficiency Switched-Tank Converter for Data Center Application," 2018.

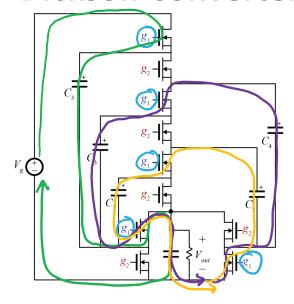

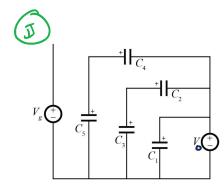

### **Dickson Subintervals**

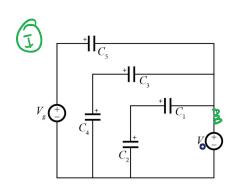

Ideal Analysis

- All cups have ~ zero ripple

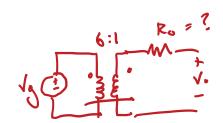

Vg = 6Vo \_ s This is a 6:1 implementation

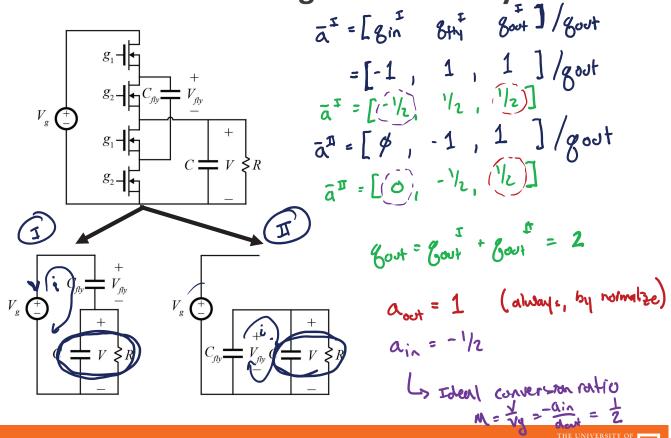

## **Charge Vector Analysis: Notation**

Finds M & Ro for arbitrary switched cap converter

- Applies cap-change balance to every capaciter in circuit 8x = Charge into capaciter x during switching subinternal I  $a_{x}^{T} = \frac{8x}{8xt}$  - normalized with vespect to Bout = Bout + Bout + ...

$$\overline{a}^{I} = \begin{bmatrix} a_{in}^{I}, & a_{ei}^{I}, & a$$

Vc1 = Voltage on C, at the end of subintensal I (assumed operation M SSL)

M. Makowski and D. Maksimovic, "Performance Limits of Switched-Capacitor DC-DC Converters," 1995 M Seeman and S. Sanders, "Analysis and Optimization of Switched-Capacitor DC-DC Converters," 2008

# **Charge Vector Analysis: Rules**

- KVL \$ KCL apply always - for all caps (ic, )= \$ in steady-stat (cap-change balance) Tis i'ci dt = \$ Gei + Bei + ... = \$ ako,  $a_{ci}^{F} + a_{ci}^{F} + \dots = \emptyset$

ex for just two subintervals,  $a_{ci}^{I} = -a_{ci}^{II}$

To find output resistance turn off Va, apply test source at output 1: A Ro To Itest

Vitest Ro = Vtest = V

2:1 Converter Charge Vector Analysis