From

| Steps Involved |

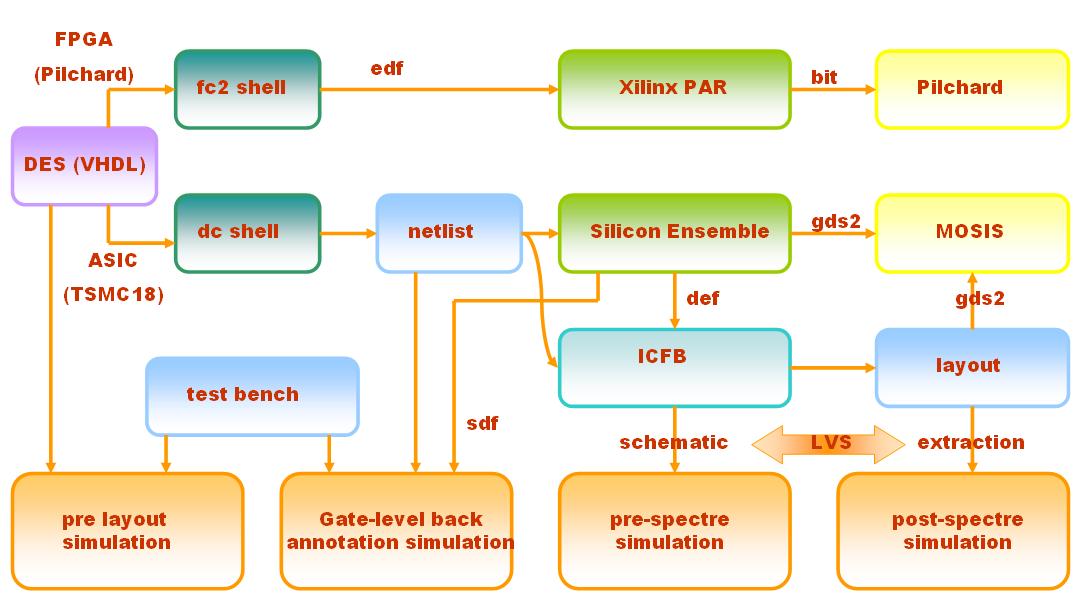

| DES module used in this project can be targeted to both ASIC as well as an FPGA. |

| The following block diagram gives the overall flow from VHDL to sending the design for fabrication |

|

|

|

Figure : VHDL to Fabrication

|

| ASIC |

| Before starting to target the DES module, pre-layout simulation is performed. The next step is to synthesize the code. Synopsys's Design compiler (dc_shell) is used to synthesize the code. Output of design compiler is a gate-level netlist .In order to test whether the netlist is correct or not , Gate-level back annotation simulation should be performed. |

| Silicon Ensemble : Next step is to get the layout. Inorder to do the layout, Cadence's Silicon ensemble can be used.tsmc18's lef file,tsmc18's netlist and the DES netlist should be given as inputs to Silicon Ensemble. Outputs from Silicon ensemble are DEF, SDF files. DEF contains the abstract view of the design and SDF is Standard Delay Format which gives the delay information between the cells and interconnects. |

| Layout : DEF file is imported into ICFB to get the DEF layout. SDF is used to do gate-level back annotation simulation. From the layout, extracted view of DES can be obtained. For bigger layouts it is not possible to do post-layout simulation. Best thing to check whether the layout has come correctly is to do LVS check. |

| Importing Netlist to get Schematic: Using ICFB , the gate level netlist can be imported to get the schematic. From the layout , the extracted view can be obtained.LVS check on these would confirm that the netlist has given the correct layout. The gate-level back annotation simulation would confirm the functionality of the block. |

| GDS2 : Once the simulations and LVS are correct, the layout can be imported as a gds2 file which can be sent for fabrication |

| FGPA |

| In the case of FPGA, we can target our design to a particular chip. Once confirming whether the pre-layout simulation works we can use FPGA compiler to synthesize the code and get an EDIF file .Using Place and Route tools of that particular vendor's FPGA we can get a bit file which can be downloaded on to the device to check the functioning. |