1. Copy the software into your home directory:

cp -r /sw/Liberator .

cd Liberator

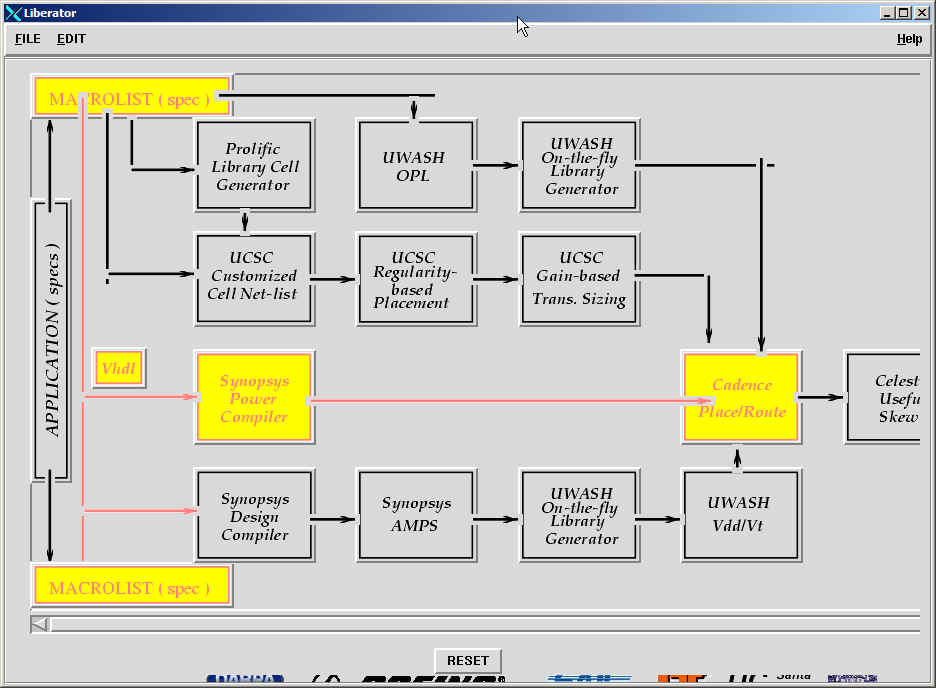

2. Start the GUI:

source ~cad/.cshrc

synopsys_tools

./team_liberator &

3. Click "RESET" to clean up the working directory

4. Generate the VHDL file:

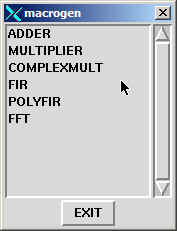

Click "MACROLIST" to see the list of available macros;

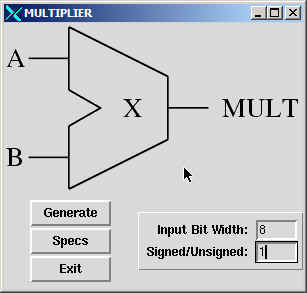

Double click the desired macro, for example "multiplier";

Input the parameters for macro (e.g. 8, 0 or 1), click "GENERATE", then "EXIT";

Click "VHDL" to see the auto-generated VHDL code

5. Optimization the design

Click "Synopsys Power Compiler",

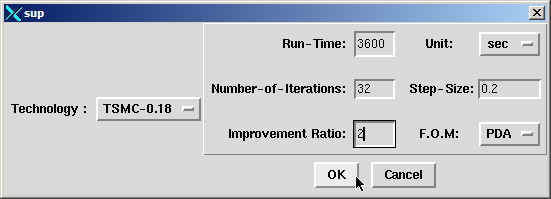

Input parameters as:

Run Time --> 3600 (or 360) Unit --> Sec (Don't choose min)

Iterations --> 32 (or 6) Step Size --> 0.2

Ratio --> 2 FOM --> PDA

Technology --> TSMC-0.18

Click "OK" to start the optimization.

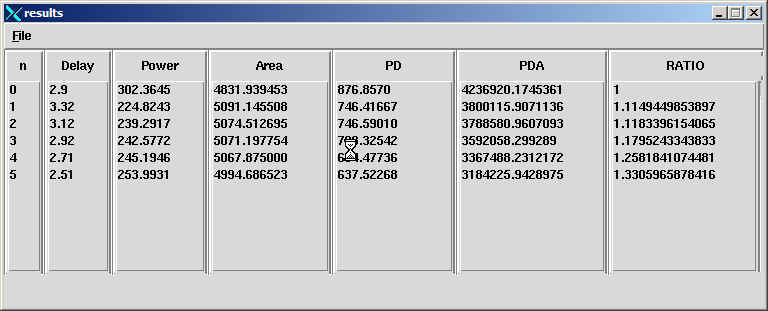

6. A dialog window appears. After about 50 (or 5) minutes, it reports the optimization finished. A result window appears.

Capture the results matrix and post on your restricted website.

Exit.

The netlist file is "MacroName_Number.v" in the current directory.

7. Use "Silicon Ensemble" to generate the auto layout (like the project in ECE 651), and export it as a DEF file.

The standard LEF file and V file are:

/sw/CDS/ARTISAN/TSMC18/aci/sc/lef/tsmc18_6lm.lef

/sw/CDS/ARTISAN/TSMC18/aci/sc/verilog/tsmc18.v

8. Use "icfb" to see the layout.

(1) Add the following 2 lines into your cds.lib file:

DEFINE tsmc18 /sw/CDS/TSMC18_Artisan/tsmc18

DEFINE tsmc18_artisan /sw/CDS/TSMC18_Artisan/tsmc18_artisan

(2) display.drf should be in your directory

(3) start "icfb".

(4) generate a new library, copy all the files under "/sw/CDS/TSMC18_Artisan/tsmc18" into the library.

(5) import the DEF file into the new library, with reference library to be "tsmc18_artisan"

(6) replace "abstract" with "layout"

(7) capture the layout

FYI: Switching Activity-SAIF (ChipTalk)